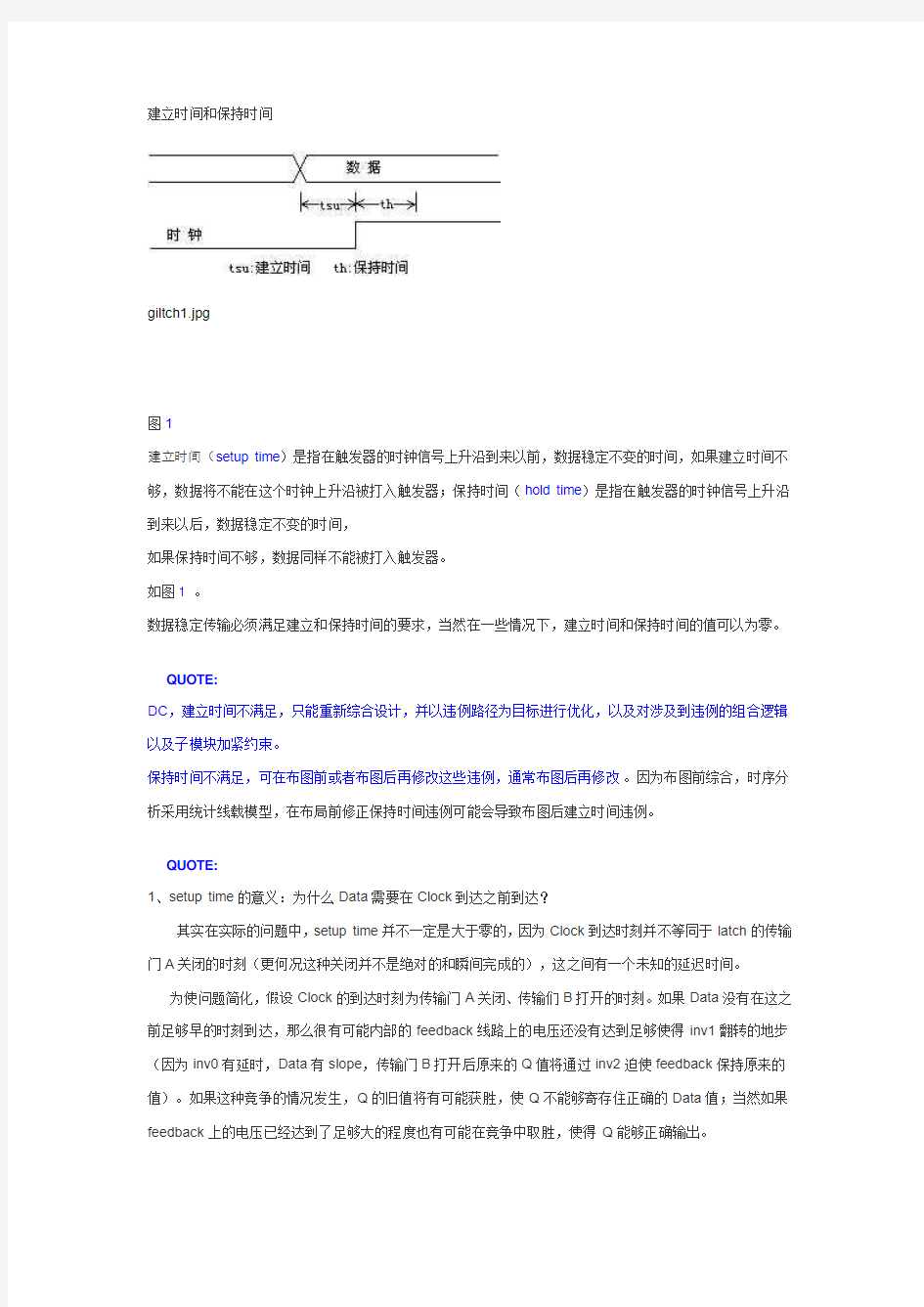

建立时间和保持时间

giltch1.jpg

图1

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,

如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

QUOTE:

DC,建立时间不满足,只能重新综合设计,并以违例路径为目标进行优化,以及对涉及到违例的组合逻辑以及子模块加紧约束。

保持时间不满足,可在布图前或者布图后再修改这些违例,通常布图后再修改。因为布图前综合,时序分析采用统计线载模型,在布局前修正保持时间违例可能会导致布图后建立时间违例。

QUOTE:

1、setup time的意义:为什么Data需要在Clock到达之前到达?

其实在实际的问题中,setup time并不一定是大于零的,因为Clock到达时刻并不等同于latch的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间。

为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻。如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)。如果这种竞争的情况发生,Q的旧值将有可能获胜,使Q不能够寄存住正确的Data值;当然如果feedback上的电压已经达到了足够大的程度也有可能在竞争中取胜,使得Q能够正确输出。

如果inv0、inv1和inv2的延时较大(Data的变化影响feedback和Q的时间越长),那么为了保证正确性就需要更大的setup time。所以在实际测量setup time的时候,需要选取工艺中最慢的corner进行仿真测量。

2、、hold time的意义:为什么Data在Clock到达之后仍然要保持一段时间?

和setuptime的情况不一样,因为Clock到达时刻并不等同于latch的传输门A完全关闭的时刻。所以如果Data没有在Clock到达之后保持足够长的时间,那么很有可能在传输门A完全关闭之前Data就已经变化了,并且引起了feedback的变化。如果这种变化足够大、时间足够长的话,很有可能将feedback 从原本正确的低电压拉到较高电压的电压。甚至如果这种错误足够剧烈,导致了inv1和inv2组成的keeper 发生了翻转,从而彻底改变了Q的正确值,就会导致输出不正确。当然,如果这种错误电压不是足够大到能够改变keeper的值,就不会影响到Q的正确输出。

如果inv0、inv1和inv2的延时较小(Data的变化影响feedback和Q的时间越短),那么为了保证正确性,就需要更大的hold time。所以在实际测量hold time的时候,需要选取工艺中最快的corner进行仿真测量。

QUOTE:

时钟周期为T,触发器D1的时钟沿到来到触发器Q变化的时间Tco(CLK--Q)最大为T1max,最小为T1min,逻辑组合电路的延迟时间最大为T2max,最小为T2min,问触发器D2的建立时间和保持时间。

最终答案:T3setup maxbird:D2的保持时间就是时钟沿到来之后,D2的数据输入端要保持数据不变的时间,这个时间是由D1和D2之间的组合逻辑时延决定的。例如:假设D1和D2之间的组合逻辑时延为2ns,时钟周期为10ns,这意味着在时钟沿来到后,D1输出的新数据要过2ns才会到达D2的数据输入端,那么在这2ns内,D2的数据输入端保持的还是上一次的旧数据,其值不会立即更新,假设D2的最小保持时间为3ns,这意味时钟沿到来后,D2的数据输入端的值在3ns内不能有变化,回到问题的关键,由于D1在时钟沿到来后的输出结果,经过2ns的组合逻辑延时便到达了D2的输入端,而D2要求在时钟沿到来后的3ns内其输入端的值不能改变,这样D2的保持时间就得不到满足,所以D2的保持时间必须小于等于2ns。至于说T2min为0时的情况,其实T2min是永远不能为0的,即使是一根导线其时延也是不可能为0的,这就是为什么移位寄存器的两个触发器之间连的只是一根导线,导线后端触发器的保持时间却还是可以满足的原因,其实移位寄存器中触发器的保持时间可以看成是小于等于其间导线的时延。 建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间;保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间。 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间+ 第二级触发器的建立时间< = 时钟周期。(编者注:maxbird在该部分详细说明了建立时间和保持时间的概念,以及如果不满足二者可能导致的亚稳态的传播。注意这里说的建立时间和保持时间都是针对时钟而言的,在进行时序约束时所指的就是这种,而很多网友以前学习的建立时间保持时间的概念是针对信号而言的,所指的对象不同,分析出来的结论完全相反,一定注意不要混淆。) lh1688:不考虑CLOCK SKEW情况下。D2的建立时间要求:Tco1+T1(logic delay)+Tsetup2 < Tc (CLOCK周期) 。那么Tsetup2 < Tc(CLOCK 周期) -(Tco1+T1)。这个应该比较容易理解。相对的保持时间实际就是路径的总延时(Tco1+T1)。保持时间Thold2 < (Tco1+T1)。 建立时间与保持时间概述(EETOP) 关于建立时间和保持时间,如下图普及一下基础知识 先: 其中Tcq 触发器时钟到数据输出的延时,Tcd 时钟的延时参数Tpd 组合逻辑的延时,Tsetup 触发器的保持时间。 因为数据到达触发器的时间至少要比时钟沿早一个建立时间,则有Tcq+Tpd+Tsetup+T,建立时间裕量=T时钟周期+Tcd,由于T建立时间裕量>0。 所以要求的最小时钟周期即为T=Tcq+Tpd+Tsetup-Tcd 时钟周期为T,触发器D1的时钟沿到来到触发器Q变化的时间Tco(CLK--Q)最大为T1max,最小为T1min,逻辑组合电路的延迟时间最大为T2max,最小为T2min,问触发器D2的建立时间和保持时间。 该题最终答案:T3setup< FONT> maxbird:D2的保持时间就是时钟沿到来之后,D2的数据输入端要保持数据不变的时间,这个时间是由D1和D2之间的组合逻辑时延决定的。例如:假设D1和D2之间的组合逻辑时延为2ns,时钟周期为10ns,这意味着在时钟沿来到后,D1输出的新数据要过2ns才会到达D2的数据输入端,那么在这2ns内,D2的数据输入端保持的还是上一次的旧数据,其值不会立即更新,假设D2的最小保持时间为3ns,这意味时钟沿到来后,D2的数据输入端的值在3ns内不能有变化,回到问题的关键,由于D1在时钟沿到来后的输出结果,经过2ns的组合逻辑延时便到达了D2的输入端,而D2要求在时钟沿到来后的3ns内其输入端的值不能改变,这样D2的保持时间就得不到满足,所以D2的保持时间必须小于等于2ns。至于说T2min 为0时的情况,其实T2min是永远不能为0的,即使是一根导线其时延也是不可能为0的,这就是为什么移位寄存器的两个触发器之间连的只是一根导线,导线后端触发器的保持时间却还是可以满足的原因,其实移位寄存器中触发器的保持时间可以看成是小于等于其间导线的时延。 建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间;保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间。如下图: 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。 maxbird在该部分详细说明了建立时间和保持时间的概念,以及如果不满足二者可能导致的亚稳态的传播。注意这里说的建立时间和保持时间都是针对时钟而言的,在进行时序约束时所指的就是这种,而很多网友以前学习的建立时间保持时间的概念是针对信号而言的,所指的对象不同,分析出来的结论完全相反,一定注意不要混淆。 不考虑CLOCK SKEW情况下。D2的建立时间要求:Tco1+T1(logic delay)+Tsetup2 不考虑CLOCKSKEW情况下。D2的建立时间要求:Tco1+T1(logic delay)+Tsetup2 < Tc(CLOCK 周期) 。那么Tsetup2 < Tc(CLOCK 周期)-(Tco1+T1)。这个应该比较容易理解。相对的保持时间实际就是路径的总延时(Tco1+T1)。保持时间Thold2 <(Tco1+T1)。 QUOTE: 你说的保持时间应该指的是输入引脚的保持时间: tH= 如果你正确设置了convert_clk 和out_clk的时序分析参数,在时序分析报告中应该看到满足时序要求的结果:Clock Setup :'convert_clk'、Clock Hold :'convert_clk'。 你说的负值未必就不好,对于th、tsu来说,负值是好的。如果你在时序设置中指定了期望值的话,用期望值减去实际值,得到的是你的余量(slack)。只有slack是正值,才是好的结果。 如果你现在还没有分配引脚,并且不准备把设计用于实际系统的话,你可以暂时不关心th、tsu。但是一定要设置和分析你的时钟信号。 负的setup 和hold time 还是比较好理解的。 讨论一下setup time violation 的形成---因为信号比clock 后到达DFF,或者说到达的时间太晚了,这个时候这个DFF就没有办法采样到这个信号,于是就出现了setup slak。 那么,假设你对这一个DFF做优化,你会怎么做?---打包这个DFF,假设为DFFA。在DFFA中把clock 加delay,再连接到原DFF。这样你的信号就可以走的慢一点,慢到比clock还慢都没有问题---而这个时候setup time就被你给优化到负的值了。同样的可以解释负的hold time。 下面这个来自:https://www.doczj.com/doc/0e3325634.html,/tanghtctc/195716/message.aspx 时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求 时钟信号时延差要非常小,否则就可能造成时序逻辑状态出错;因而明确FPGA设计中决定系统时钟的因素,尽量较小时钟的延时对保证设计的稳定性有非常重要的意义。 建立时间与保持时间 建立时间(Tsu:set uptime)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间(Th:holdtime)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。建立与保持时间的简单示意图如下图1所示。 图1 保持时间与建立时间的示意图 在FPGA设计的同一个模块中常常是包含组合逻辑与时序逻辑,为了保证在这些逻辑的接口处数据能稳定的被处理,那么对建立时间与保持时间建立清晰的概念非常重要。下面在认识了建立时间与保持时间的概念上思考如下的问题。 图2 同步设计中的一个基本模型 图2为统一采用一个时钟的同步设计中一个基本的模型。图中Tco是触发器的数据输出的延时;Tdelay 是组合逻辑的延时;Tsetup是触发器的建立时间;Tpd为时钟的延时。如果第一个触发器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min。问第二个触发器D2立时间T3与保持时间T4应该满足什么条件,或者是知道了T3与T4那么能容许的最大时钟周期是多少。这个问题是在设计中必须考虑的问题,只有弄清了这个问题才能保证所设计的组合逻辑的延时是否满足了要求。 下面通过时序图来分析:设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2; 时钟统一在上升沿进行采样,为了便于分析我们讨论两种情况即第一:假设时钟的延时Tpd为零,其实这种情况在FPGA设计中是常常满足的,由于在FPGA设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟,这样在内部时钟的延时完全可以忽略不计。这种情况下不必考虑保持时间,因为每个数据都是保持一个时钟节拍同时又有线路的延时,也就是都是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间都能满足要求,重点是要关心建立时间,此时如果D2的建立时间满足要求那么时序图应该如图3所示。 从图中可以看出如果: T-Tco-Tdelay>T3 即:Tdelay< T-Tco-T3 那么就满足了建立时间的要求,其中T为时钟的周期,这种情况下第二个触发器就能在第二个时钟的升沿就能稳定的采到D2,时序图如图3所示。 图3 符合要求的时序图 如果组合逻辑的延时过大使得T-Tco-Tdelay 那么将不满足要求,第二个触发器就在第二个时钟的升沿将采到的是一个不定态,如图4所示。那么电路将不能正常的工作。 图4 组合逻辑的延时过大时序不满足要求 从而可以推出 T-Tco-T2max>=T3 这也就是要求的D2的建立时间。 从上面的时序图中也可以看出,D2的建立时间与保持时间与D1的建立与保持时间是没有关系的,而只和D2前面的组合逻辑和D1的数据传输延时有关,这也是一个很重要的结论。说明了延时没有叠加效应。 第二种情况如果时钟存在延时,这种情况下就要考虑保持时间了,同时也需要考虑建立时间。时钟出现较大的延时多是采用了异步时钟的设计方法,这种方法较难保证数据的同步性,所以实际的设计中很少采用。此时如果建立时间与保持时间都满足要求那么输出的时序如图5所示。 图5 时钟存在延时但满足时序 从图5中可以容易的看出对建立时间放宽了Tpd,所以D2的建立时间需满足要求: Tpd+T-Tco-T2max>=T3 由于建立时间与保持时间的和是稳定的一个时钟周期,如果时钟有延时,同时数据的延时也较小那么建立时间必然是增大的,保持时间就会随之减小,如果减小到不满足D2的保持时间要求时就不能采集到正确的数据,如图6所示。 这时即T-(Tpd+T-Tco-T2min) T-(Tpd+T-Tco-T2min)>=T4 即Tco+T2min-Tpd>=T4 从上式也可以看出如果Tpd=0也就是时钟的延时为0那么同样是要求Tco+T2min>T4,但是在实际的应用中由于T2的延时也就是线路的延时远远大于触发器的保持时间即T4所以不必要关系保持时间。 图6 时钟存在延时且保持时间不满足要求 综上所述,如果不考虑时钟的延时那么只需关心建立时间,如果考虑时钟的延时那么更需关心保持时间。下面将要分析在FPGA设计中如何提高同步系统中的工作时钟。 如何提高同步系统中的工作时钟 从上面的分析可以看出同步系统时对D2建立时间T3的要求为: T-Tco-T2max>=T3 所以很容易推出T>=T3+Tco+T2max,其中T3为D2的建立时间Tset,T2为组合逻辑的延时。在一个设计中T3和Tco都是由器件决定的固定值,可控的也只有T2也就时输入端组合逻辑的延时,所以通过尽量来减小T2就可以提高系统的工作时钟。为了达到减小T2在设计中可以用下面不同的几种方法综合来实现。 通过改变走线的方式来减小延时 以altera的器件为例,我们在quartus里面的timing closure floorplan可以看到有很多条条块块,我们可以将条条块块按行和按列分,每一个条块代表1个LAB,每个LAB里有8个或者是10个LE。它们的走线时延的关系如下:同一个LAB中(最快)< 同列或者同行< 不同行且不同列。我们通过给综合器加适当的约束(约束要适量,一般以加5%裕量较为合适,比如电路工作在100Mhz,则加约束加到105Mhz 就可以了,过大的约束效果反而不好,且极大增加综合时间)可以将相关的逻辑在布线时尽量布的靠近一点,从而减少走线的时延。 通过拆分组合逻辑的方法来减小延时 由于一般同步电路都不止一级锁存(如图8),而要使电路稳定工作,时钟周期必须满足最大延时要求, 缩短最长延时路径,才可提高电路的工作频率。如图7所示:我们可以将较大的组合逻辑分解为较小的几块,中间插入触发器,这样可以提高电路的工作频率。这也是所谓―流水线‖(pipelining)技术的基本原理。 对于图8的上半部分,它时钟频率受制于第二个较大的组合逻辑的延时,通过适当的方法平均分配组合逻辑,可以避免在两个触发器之间出现过大的延时,消除速度瓶颈。 图7 分割组合逻辑 图8 转移组合逻辑 那么在设计中如何拆分组合逻辑呢,更好的方法要在实践中不断的积累,但是一些良好的设计思想和方法也需要掌握。我们知道,目前大部分FPGA都基于4输入LUT的,如果一个输出对应的判断条件大于四输入的话就要由多个LUT级联才能完成,这样就引入一级组合逻辑时延,我们要减少组合逻辑,无非就是要输入条件尽可能的少,这样就可以级联的LUT更少,从而减少了组合逻辑引起的时延。 QUOTE: Setup time is the minimum time prior totrigerring edge of the clock pulse upto which the data should be kept stable atthe flip-flop input so that data could be properly sensed at the input.Holdtime is the minimum time after the clock edge upto which the data should bekept stable in order to trigger the flip flop at right voltage level. Setuptime is required in order to find the maximum clock frequency of a circuit. QUOTE: Setup time :It is theminimum time before the clock edge the input should be stable.This is due tothe input capacitance present at the input.It takes some time to charge to theparticular logic level at the input. Hold time:It is theminimum time the input should be present stable after the clock edge.This isthe time taken for the various switching elements to transit from saturation tocut off and vice versa. So basically set up andhold time is the window during which the input should be stable.Any changes inthe input during the window period may lead to voltage levels which is notrecognised by the subsequent stages and the circuit may go to metastable stage. QUOTE: suppose ur flip-flop is positive edge triggered. timefor which data should be stable prior to positive edge clock is called setuptime constraint . Time for which datashould be stable after the positive edge of clock is called as hold timeconstraint. if any of theseconstraints are violated then flip-flop will enter in meta stable state, inwhich we cannot determine the output of flip-flop. there are two equation: 1. Tcq + Tcomb> Tskew+ Thold 2. Tcq + Tcomb Tcq is time delay whendata enters the flip-flop and data comes at output of flip flop. Tcomb is the logic delaybetween two flip flop. Tskew is the delay ofclock to flip flop: suppose there are two flip flop ,if clock reaches first tosource flip flop and then after some delay to destination flip flop ,it ispositive skew and if vice versa then negative skew. so if u take 2 eq youwill see that setup time is the determining factor of clock's time period. Q:Can any body tell mewhy holdtime violations will not get affected with change in frequency. Butsetup time violations will depend on the frequency. Please explain me therelation of setup time/ hold time with frequency. A1:may be the picture will explain ? hold_1480.jpg A2:Think of set up time as being frequencydependent because it has to do with when the data arrives... We can'thave the data arrive exactly when the rising edge of destination clockis approaching because it would lead to metastability. This is animportant concept when you are crossing clock domains, where one domainis faster or slower than the other. Set up time is always before therising edge of the destination flop. Hold time has less to do with when the data arrives and more to dowith once it has arrived (after the destination flop's active edge) letit remain steady for some time. The diagram should help you see this. A3:Suppose you have a register to register pathwith each register clocked by a clock of frequency 10 MHz.Consider aclock edge at time 0 at reg1 and a clock edge at time 0.1us at reg2.Thesetup check would be between these two edges.But if the frequencyvaries the time available would be different from 0.1us.But for thehold check which is done for the clock edge at time 0 at reg2,even ifthe frequency changes, the hold check would still be at time 0.Sofrequency of the clock has an effect only on the setup and not the hold Q: Can any body tell me 1) What causes HOLD VIOLATIONS in DESIGN. 2) How it effects DESIGN. 3) What changes need to be done to make DESIGN work. A1:A synchronous design uses FF devices. A FF device needs its data to be valid before and after rising clock edge. The time before edge is called setup time and the one after edge is called hold time. While the former may be overcome by having a faster device, temperature or power supply restrictions the latter can not. In FPGA devices always use dedicated clock pins. Some FPGA devices allow the insertion of delay at an input pad to eliminate hold time requirement. Note that FPGA vendors usually do not specify minimum clock to output delay of an outgoing FF device. So if your design is driven by an FPGA and you need positive (> 0) hold time you might face a problem. More info, VHDL and VERILOG code as well as simulation utilities can be found at https://www.doczj.com/doc/0e3325634.html,/ A2:1) What causes HOLD VIOLATIONS in DESIGN. Simply, data should be hold for some time (hold time) after the edge of the clock. So, if the data changes with the hold time might cause violation. In general, hold time will be fixed during backend work (during PNR) while buildingclock tree. If u r a frontend designer, concentrate on fixing setup time violations rather than hold violations. 2) How it effects DESIGN. If a chip is done with some setup violations it can work by reducing the frequency. If achip is done with hold violations, JUST DUMP the chip. This is how it effects at the end of the day. Hold vilations needs to be fixed. 3) What changes need to be done to make DESIGN work. PNR tools will route and place the cells in such a way that no timing violations will occur. If still u face hold violations, u can manully work on it to fix. Manually place the cells to avoid hold violations, or in the worst case, u can keep some buffers in the datapath to avoid hold violations (but be sure setup timing is not effected.) >you said "If a chip is done with hold violations, JUST DUMP the chip. " >why can't reducing the frequency to settle the hold violation as setup violation ? >could you explain it clearer ? Equation for Setup Time Tclk > Tclktoq + Tlogic + Tsetup + Tskew + Tjitter Equation for Hold Time Tclktoq + Tlogic - Tskew > Thold Note that Hold Time equation is independent of clk frequency(i.e Time period Tclk) key things to note from above equations a) once the silicon comes back , if u have setup time problem , u can increase the clock period (Tclk) to fix it , whereas if u have hold time problem , its a more serious problem and u will need a new metal fix tapeout . ( But u can still test the current chip using Low supply voltage, or High temperature or SS corner part that decrease hold time violation)> Hi koggestone, > It is nice information. Could you please give us more information on > " u will need a new metal fix tapeout . ( But u can still test the current chip using > Low supply voltage, or High temperature or SS corner part that decrease hold time >violation)" what i meant was , when u have hold time violation , u dont need to throw away chip and wait for 3 months for fixed chip to come back. in the meanwhile , by playing with voltage and temperature , u can do other functional tests on the chip . since normally hold time simulation are done at " FF corner , high voltage, low temperature " which is the pessimistic case for hold time , by decreasing voltage , using high temperature, and a SS corner chip , we may be lucky enough to find a part that works , to do other functional tests to catch any other bugs before next tapeout. 下面这个比较详细: Sunil Budumuru: Pls. make a note that HOLD violations are dangerous than SETUP. To keep it simple way, SETUP timing depends on the frequency of operation. But HOLD time is not. Let us see the equations here. T = Frequency of operation (can be variable) Tcq = Flop clock to Flop output delay (fixed/constant) Tcomb = Delay od the combinational logic between the Flops (can be variable) Tsetup = Setup time of a Flop (fixed/constant) Thold = Hold time of a Flop (fixed/constant) Tskew = Delay between clock edges of two adjacent flops (delay offered by clock path) (can be variable) For SETUP, T >= Tcq + Tcomb + Tsetup - Tskew If you have setup time means u r violating the above rule. i.e some how the equation becomes T < Tcq + Tcomb + Tsetup - Tskew Now let us consider two cases. Case1: During the Design development phase itself. Now, you have three variables (T, Tcomb, Tskew.) to avoid the setup violation. T : Reduce the frequency such that u saticify T >= Tcq + Tcomb + Tsetup - Tskew. But do u think it is the correct solution. Obviously, NO. This is because we have other options to avoid setup violations right. Tcomb : If you reduce the combinational delay (between the Flops of violated path) such a way that T < Tcq + Tcomb + Tsetup - Tskew will become T >= Tcq + Tcomb + Tsetup - Tskew. So, the SETUP violation is avoided. How do u reduce the combinational delay??? Try different logic structure without effecting the functionality. or try to reduce the more fanout nets within the logic. Or upsize or downsize the cells. If it worked out thats fine. Tskew: If u increase the skew, u can change T < Tcq + Tcomb + Tsetup - Tskew to T >= Tcq + Tcomb + Tsetup - Tskew. How to increase the Tskew? Just keep buffers in the clock path. But be sure doesnt effect the HOLD timing. Case2: After the CHIP is manufatured and is in your hand. In this case, one cannot access the Tcomb and Tskew. Only the variable that can handle is T. So, Just reduce the frequency (T) such that the violated equation, T < Tcq + Tcomb + Tsetup - Tskew becomes violation free equation T >= Tcq + Tcomb + Tsetup - Tskew. So, if u have setup violations on a manufatured chip, u can make it work by reducing the frequency. For HOLD, Thold + Tskew <= Tcq + Tcomb If you have setup time means u r violating the above rule. i.e some how the equation becomes Thold + Tskew > Tcq + Tcomb and ur aim is to make Thold + Tskew <= Tcq + Tcomb Now let us consider two cases. Case1: During the Design development phase itself. You have two variables in hand (Tcomb, Tskew) to avoid HOLD violations. Tcomb: Increase the Tcomb by adding buffers in the data path. Thus u can change the situation from Thold + Tskew > Tcq + Tcomb to Thold + Tskew <= Tcq + Tcomb. But this might effect the SETUP time as you are increasing the delay of combinational path. So this may not be the perfect solution always. Tskew : Reduce the clock skew so that you will land on Thold + Tskew <= Tcq + Tcomb. To reduce the clock skew, the best solution is to take the help of your PNR engineer. Case2: After the CHIP is manufatured and is in your hand. Do you see any variables that will fix the hold violations after manufaturing?????!!!!!! NO right. So, its time to DUMP the chip as we dont deliver malfunctioning chips to the customers. So becareful with the HOLD violations. Note: One can get those equations if u put the those scenarios on a paper and develop the timing diagrams. Hope I've explained it properly. ust make sure that once you have added hold time, setup time and propagation delay, the clock period has not been exceeded. t_clock < t_setup + t_hold + t_prop_delay Another way of looking at it is that the time left for your logicoperation between the two registers equals to the clock period minusthe setup and hold time. I copied an example about how to calculate setup and hold time from a book(in the attachment). 建立时间和保持时间 giltch1.jpg 图1 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间, 如果保持时间不够,数据同样不能被打入触发器。 如图1 。 数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。 QUOTE: DC,建立时间不满足,只能重新综合设计,并以违例路径为目标进行优化,以及对涉及到违例的组合逻辑以及子模块加紧约束。 保持时间不满足,可在布图前或者布图后再修改这些违例,通常布图后再修改。因为布图前综合,时序分析采用统计线载模型,在布局前修正保持时间违例可能会导致布图后建立时间违例。 QUOTE: 1、setup time的意义:为什么Data需要在Clock到达之前到达? 其实在实际的问题中,setup time并不一定是大于零的,因为Clock到达时刻并不等同于latch的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间。 为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻。如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)。如果这种竞争的情况发生,Q的旧值将有可能获胜,使Q不能够寄存住正确的Data值;当然如果feedback上的电压已经达到了足够大的程度也有可能在竞争中取胜,使得Q能够正确输出。 []古埃及史与夏朝历史对比揭示真实的夏(2015-10-10 205638) 标签: 原文地址:古埃及史与夏朝历史对比揭示真实的夏作者:兵策儒剑 基于中国本土考古并未发现令人信服的夏朝存在证据,以及西方古埃及考古历史证据、中国古籍记载证据,以及古汉字与古埃及图画文字对比,根据这些可信、公开的,大家都可看得见的直接证据分析对比揭示了夏的真相! 1 古埃及早王朝VS 五帝时代 (参考blog.sina../s/blog_6a4e1c6f0101bh8y.html)年代 西方考古古埃及史(古埃及早王朝时期) 中国古籍记载的夏朝 (五帝时代) 古埃及自称 古汉字“夏” 前3200年? 早王朝上埃及第一位国王:Scorpion I(蝎子王一世)。在埃及Umm el-Qa'ab 最早的墓葬中有蝎子王符号。 另外在苏美尔乌尔(虞?)第一王朝墓葬出土的牛首箜篌绘画中有个人首蝎尾的形象。 古汉字”黄“ 前3150年? 早王朝上埃及Iry-Hor ((读音:伊尧)) 古汉字”尧“? 早王朝上埃及Sekhen,Sekhen意思是拥抱,读音“森汉”,或者读着Shen,与舜shun的发音很相近。他是Iry-Hor继任者。 注意这个器皿上的字是用笔书写上去的,其笔画方法已经非常像汉字!古埃及除了圣书体,很早时候就还有手写体! 古汉字”舜“,舜是尧的继任者前3150年? 早王朝上埃及King Scorpion (蝎子王二世)或者Narmer,他是Sekhen的继任者。 他被希罗多德称为“美尼斯(Menes)”。传说他以武力统一上下埃及,并建都孟斐斯。他被认为是第一个统一埃及的国王。也是古埃及古王国第一王朝首位法老。他的形象是一个蝎子。古汉字”禹“,禹是舜的继任者 顾老教授讲过“大禹是条虫” 《竹书纪年》卷上:“禹於石纽。虎鼻大口,两耳参镂。” 解读高速数/模转换器(DAC)的建立和保持时间Oct 10, 2007 摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。 介绍 为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。 定义建立和保持时间 建立时间(t S)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。保持时间(t H)则定义了器件捕获/采样数据后允许数据发生变化的时间。图1给出了相对于时钟上升沿的建立和保持时间。特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX5895 16位、500Msps、插值和调制双通道DAC,CMOS输入。 图1. 相对于时钟信号上升沿的建立和保持时间 采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。因此,时间参考点定在信号边沿的中点。图1波形标明了器件在典型条件下的建立和保持时间。注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。 MAX5891 600Msps、16位DAC为这一中间值状态提供了很好的学习实例。该器件的建立时间为-1.5ns,而保持时间为2.6ns。图2给出MAX5891的最小建立时间。注意,实际应用中,数据通常在采样时钟跳变后发生变化。图3给出了相同器件的最小保持时间。 “夏”与“夏朝”、历法、干支 “夏”与“夏朝”、历法、干支 在篆文中,“夏”是由“頁”、“夊”和左右分离的“臼”组成。“頁”就是起头之义。“夊”在篆文中由“人”和阴符“乀”组成,是下肢没有进化(发育)齐全的会意。“夊”字的本义就如此。“臼”,为相反的会意,也是对立的会意。这个相反,也许是与“当代”人的肢体差异,也许是建立以相反性为认识核心的体现天体运行规律的文化。全字综合起来分析,应该是代表着周朝对这一时期的分析:这一时期的人,尚属于“小人”时期,下肢没有进化齐全,但这时,已经着手研究天体运行规律,建立了初步的历法。这种历法是有其证据的,那就是在中学历史教科书中提到了古代陶片记载的24个字符,它是干支文化的雏形。那时有没有王朝呢?既然存在这种文化,就必然有君主进行管理,形成了面积较广阔的集权,各司其职。有些专家否定夏朝是一个朝代,这是站不住脚的。 为什么四季中有“夏季”之谓?夏季中的夏至,是天体测量中的一个中心点,当月食发生在夏至这一天,就视为起元的依据,其年记戊午(戊在天干中,属于中心位置),其日记戊午(甲骨文中的“午”字就揭示了日月之间的关系,由两个●●组成)。这一理论应该是夏朝传承下来的。为了纪念这一时期,就将这一时间段称为夏季,这一历法,称为夏历。 为什么要以夏至为依据,而不以春分为依据?首先是要解决记录日期的记录问题。外界的能量——太阳,是认识阴阳,分辨义理的依据,客观认识,太阳起于晨落于昏,其中心在中午。 在年月日时的计算中,都存在地支十二的周期,它的表述也在同一个圆圈中,实现了彼此的.“同”。这个“午”,既是午时,也是午日,既是午年,也是午月。当这一天文现象出现时,这一日就是戊午日,这一年就是戊午年,由此可以找到起点干支甲子。 为什么以寅为岁首是科学的?先得明确,静态是建立在动态基础上的认识理论,它存在中心,起整体的调节作用。地球运动分为两种形式,一是周年南北视运动,一是周日东西视运动。两种运动构成了整体。如前所说,太阳周日客观运动,起于晨,相当于卯时。周年的客观运动起于冬至,在地支子。立足中心认识,就是子卯之间的中心点,即以立春为界。故以寅为岁首,反映了一种系统思维。 为何一日不起于卯时,而要从子时开始?它还是相反思维的结果。年起于寅(立春)是局部得出整体的思维反应,日起于子是整体决定局部的体现。年是整体,日是局部,整体以冬至子为起点,它就决定了一日的起点在子。 那么,24个节气有什么意义呢?首先,它是天体运动的共性划分理论,是地球上任何一个地区都存在的,之所以要牵涉到农事活动,就在于我们处于温带地区,气候的变化也反映了天体运行节律,同时,古人研究干支理论的首要目的是为了计算天气变 时序分析中建立时间,保持时间,时钟到输出,PIN到PIN延时的说明 Clock Setup Time (tsu) 要想正确采样数据,就必须使数据和使能信号在有效时钟沿到达前就准备好,所谓时钟建立时间就是指时钟到达前,数据和使能已经准备好的最小时间间隔。如下图所示: 这里定义Setup时间是站在同步时序整个路径上的,需要区别的是另一个概念Micro tsu。Micro tsu指的是一个触发器内部的建立时间,它是触发器的固有属性,一般典型值小于1~2ns。在Xilinx等的时序概念中,称Altera的Micro tsu为setup时间,用Tsetup表示,请大家区分一下。回到Altera的时序概念,Altera的tsu定义如下:tsu = Data Delay – Clock Delay + Micro tsu Clock Hold Time (tH)时钟保持时间是只能保证有效时钟沿正确采用的数据和使能信号的最小稳定时间。其定义如下图所示: tH示意图 定义的公式为:tH= Clock Delay – Data Delay + Micro tH 注:其中Micro tH是指寄存器内部的固有保持时间,同样是寄存器的一个固有参数,典型 值小于1~2ns。 Clock-to-Output Delay(tco)这个时间指的是当时钟有效沿变化后,将数据推倒同步时序路径的输出端的最小时间间隔。如下图所示: tco示意图 其中Micor tco也是一个寄存器的固有属性,指的是寄存器相应时钟有效沿,将数据送到输出端口的内部时间参数。它与Xilinx的时序定义中,有一个概念叫T cko是同一个概念。 Pin to Pin Delay (tpd)tpd指输入管脚通过纯组合逻辑到达输出管脚这段路径的延时,特别需要说明的是,要求输入到输出之间只有组合逻辑,才是tpd延时。 Slack是表示设计是否满足时序的一个称谓,正的slack表示满足时序(时序的余量),负的slack表示不满足时序(时序的欠缺量)。slack的定义和图形如下图所示。 Slack = Required clock period – Actual clock period Slack = Slack clock period – (Micro tCO+ Data Delay + Micro tSU) Clock Skew指一个同源时钟到达两个不同的寄存器时钟端的时间偏移,如下图所示。 史上十个最强帝国:中国统治世界三次 这里的―帝国‖必须满足如下三个条件:领土广大,由多种族多民族构成,是区域内最高 政权。这个榜单将根据影响力、持续时间和帝国本身的强大程度进行选取,您或许会对榜单中的一两位有不同意见。 此外,这个榜单的一个条件上是所谓的―帝国‖必须被一位皇帝或国王统治过,因而如美 国和苏联这样的现代帝国将被排除在外。而进榜的帝国将大致按照影响力和国家体积进行排序。中国有两个朝代入选: 奥斯曼帝国 10 Ottoman Empire 奥斯曼帝国 奥斯曼帝国在其全盛时期(十六到十七世纪)横跨三大洲,控制了南欧、西亚和北非的 大块领土。奥斯曼帝国有十九省,并不计其数的诸侯国,其中一些在后期被吞并进了帝国, 剩余的则在几个世纪间一直维持着不同程度的自治权。 奥斯曼帝国雄踞东西方交流中枢长达六个世纪。帝国以君士坦丁堡为首都,在苏莱曼大帝时期控制着地中海东部大片土地。从某种意义上来说,奥斯曼土耳其帝国堪称是东罗马帝 国的伊斯兰继承者。 9 Umayyad Caliphate 倭马亚哈里发王国 倭马亚哈里发王国是四个哈里发王国中的第二个,在默罕默德死后建立。王国由倭马亚王朝统治,这个名字来自王朝第一位哈里发的曾祖父倭马亚·伊本·阿拜德·夏姆斯。虽然倭马亚家族最早来自麦加,王朝却以大马士革为首都。 倭马亚哈里发王国 自建立以来,这个国家最后变成了一个占地500 万平方英里的巨大王国,这样的领土 面积不仅是前无来者,同时也是历史上第五大疆土连贯的的帝国。 倭马亚是历史上最大的阿拉伯穆斯林国家。自穆罕默德起到1924 年,先后出现了数个哈里发王国,而最后一个就是上面说过的土耳其奥斯曼帝国。 8 Persian Empire or Achaemenid Empire 波斯帝国/阿契美尼德帝国 波斯帝国/阿契美尼德帝国 巴比伦尼亚在罗马之前,这些全都属于波斯帝国。波斯帝国当年基本统一了全中亚,帝国由不同的文化、王国、帝国和部落组成。 它也是古代历史上最大的帝国。波斯帝国在其全盛时期约有领土八百万平方千米。帝国由居鲁士大帝建立,横跨亚非欧三大洲。 7 Byzantine Empire 拜占庭帝国 拜占庭帝国又称东罗马帝国,是中世纪的罗马帝国。帝国以君士坦丁堡为首都,帝统自古罗马一系承袭而来,因而拜占庭也可被称作罗马帝国,或是罗马尼亚。 拜占庭帝国存在了一千多年,虽然也遭遇过挫折,丢失过领土,但它当时仍是欧洲在经济文化和军事上最强大的国家,从罗马与波斯、拜占庭与阿拉伯的两场战争中就可见一斑。 第二章夏商时期奴隶制国家的建立和发展 (前2070年~~前1046年) △授课名称——夏商时期奴隶制国家的建立和发展 △教学目的和教学要求——通过本章学习使学生了解中国夏奴隶制国家的政治、经济、文化的基本面貌,了解其发生、发展及灭亡的基本历史过程。运用马克思主义的国家学说,探讨中国国家的起源以及夏代奴隶制国家确立的依据。通过文献资料、甲骨文资料以及其他地下发掘材料,使学生了解商朝政治、经济、军事、文化诸多方面的特征,充分认识殷商文明在古代世界中的历史地位。 △教学重点——夏朝的经济文化特征、少康失国到少康中兴;商国家机构、各项制度;盘庚迁殷到武丁开拓;商朝的统治机构商朝青铜工艺的高度发展;商朝科学文化的发展,殷商文明及其在古代世界中的历史地位。。 △教学难点——夏史文献和考古资料的缺乏;商朝的国家制度和阶级结构。 △授课对象——2012级 △授课方式——讲授 △授课时数——4学时 △教学环节: 夏朝是奴隶制国家的雏形。 首先夏朝按地域来划分它的臣民。《左传》所言“茫茫禹迹,画为九州”。 其次,世袭王朝的建立标志着国家的形成,从夏启开始实行传子制。 其三,夏朝建立了较为完整的国家机器建立了从中央到地方的各级官吏,有了军队、刑法和监狱等公共权力机关。 有了军队刑法和监狱等公共权力机关。夏的军队,以铜作兵,杼发明甲,还有战车。夏的法律:夏有乱政而作禹刑,是第一部奴隶制法典,监狱叫夏台,简单的典章制度,有夏礼,夏训。 而恩格斯认为,“按地域来划分它的国民和公共权力的设立,是国家出现的两个主要标志。”夏朝符合国家形成的两个条件,因此说夏朝是我国阶级社会的 开始。 顾颉刚的贡献——顾颉刚在商周史研究上是很有成就的,他提出了关于古史的观点,即“累层地造成的中国古史”的观点。他认为:(1)在古史记载中,“时代愈后,传说的古史期愈长”。周代人心目中最古的人是禹,到孔子时有尧、舜,到战国时有黄帝、神农,到秦有三皇,到汉以后,有盘古。(2)“时代愈后,传说中的中心人物愈放大”。如舜,在孔子时只是一个“无为而治”的圣君,到《尧典》就成了一个“家齐而后国治”的圣人,到盂子时就成了一个孝子的模范了。(3)我们“不能知道某一事件的真确状况,但可以知道某一事件在传说中的最早的状况。我们既不能知道东周时的东周史,也至少知道战国时的东周史,我们既不能知道夏商时的夏商史,也至少能知道东周时的夏商史。”他的这种观点对有关古史的荒谬传说起了廓清之功,而历代相传三皇五帝的神圣地位一下子也就失去了依据。这对于当时的学术界是一个很大的震动,对于古史研究的发展是起了作用的。但在具体古史问题的处理上,往往有“疑古”过头的地方。 第一节夏王朝的建立与灭亡 一、夏王朝的建立及其国家机构 1、夏族的兴起和夏王朝的建立 传说尧时,洪水泛滥。四岳举荐鲧治水,鲧用堵塞办法治水九年而水患不止,舜殛鲧于羽山【(舜)流共工于幽州(马融:北裔),放兜于崇山(南裔),窜三苗于三危(西裔),殛鲧于羽山(东裔)】。鲧的儿子禹继承父业,治水十三年,三过家门不入,薄衣食,卑宫室,身执耒锸,采用疏导的办法,终于制服洪水。大禹在治理洪水的过程中树立了自己威信,赢得了人们的赞誉和对华夏部落的控制大权。伴随着古代部落争夺生存空间的冲突,大禹在与共工、三苗(三苗,有学者认为应属苗蛮集团,在地域范围上应以“湖北、湖南、江西等地为中心”)等部落的战争中,扩大了实力,攫取了大量的财富,权力逐渐膨胀起来,为世袭制奠定了雄厚基础。《吴越春秋》记载禹“命群臣曰,吾百世之后,葬我会稽之山”。今绍兴有禹陵、禹穴、禹庙等。《史记·夏本纪》:“及禹崩,虽授益,益之 建立时间和保持时间关系详解 图1 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器; 保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。 如图1 。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。 个人理解: 1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。 2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。 关于建立时间保持时间的考虑 华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间T3和保持时间T4应满足什么条件? 分析: Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。 Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。 Tsetup:建立时间 Thold:保持时间 Tclk:时钟周期 建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。 保持时间容限:保持时间容限也要求大于等于0。 夏朝和商朝 ①约公元前2070年,禹建立了夏朝,夏朝是我国的第一个王朝。 ②禹死后,他的儿子继承了位子,从此王位世袭制代替了禅让制。夏朝的建立标志我国早期国家的产生。 ③约公元前1600年,商的首领成汤发动推翻夏朝的战争。大战与鸣条。成汤建立了商朝。 ④约公元前1300年,商王盘庚把都城迁到了殷(今河南安阳西北)从此,商朝的都城稳定下来了。 ⑤商朝的势力范围:东至大海,西到渭水上游,南抵长江流域,北达辽河一带。 ⊙商朝经济比夏朝有很大发展的表现:А 农业生产规模一相当大,种植的农作物有粟,黍,稻,麦等。В 畜牧业发达,饲养六畜,祭祀用几百甚至上千头家畜。℃青铜冶铸,玉器制作和酿酒等手工业很发达。D商业发展到一定水平,交易是用海贝,骨贝,玉贝和铜贝等作货币 西周的兴亡 1:约公元前1046年,周武王姬发领导了灭亡商朝的战争,大战与牧野。周武王建立了周朝,前期都城在镐京(今天的陕西西安西)历史上称为西周。 2:分封制:为了控制全国广大地区,周王让自己的子弟,亲戚功臣和一些古帝王的后代在各地去建立封国。这就是分封制。封国的统治者叫国君(一般称诸侯)。享有统治和管理封国的土地和人民的权力。同时,必须承担拥戴周王为共同的天子,定期朝见周王,参加周王主持的重要的典礼仪式,贡献财宝和特产,服从周王调遣出征作战等义务,否则将受惩罚。 3:西周初年,一共建立了71个封国,重要的有,鲁,齐,燕,晋,宋。姓姬的封国有53个。 4:西周末年,阶级矛盾,民族矛盾和统治集团内部矛盾尖锐,公元前771年犬戎族攻破镐京周幽王被杀死,西周结束。 春秋争霸 1:公元前770周平王把都城从镐京迁到洛邑(今河南洛阳)。进入春秋时期(公元前770年-----公元前476年) 2:春秋争霸的原因:A王权衰落,周王统治出现严重危机。B一些诸侯国强大起来,为了争夺更多的土地,财产和人口,争当左右天下,支配别国的霸主而展开了长期的争霸战争。 距今约三四百万年前:南方古猿形成。 距今约170万年前:元谋人,是我国境内已知最早的人类,在我国的云南元谋县。 距今约70万-20万年前:北京人,在我国北京西南周口店龙骨山的山洞里。 距今约五六千年:半坡人,定居生活,住半地穴式房子;普遍使用磨制石器;种植粟和疏(我国是世界上最早种植粟的国家)。 公元前2070年:禹建立夏朝(中国第一个奴隶制王朝),启用世袭制取代禅让制。 公元前3500年:古代埃及奴隶制小国出现。 公元前3500年:古代西亚(巴比伦)出现奴隶制小国。 公元前3000年:古埃及创造象形文字,是世界上最古老的文字之一。 公元前2000年:爱琴文明产生(古代希腊)。 公元前1600年:汤建立商朝。 ↓↓↓ 公元前1046年:周武王伐纣,商朝灭亡。 公元前1046年:牧野之战大败商君。 公元前771年:西周灭亡。 公元前770年:周平王迁都洛邑,东周开始,分为春秋(前770年-前476年)和战国(前475年-前221年)。 公元前4世纪:马其顿控制希腊,其后亚历山大帝国地跨亚欧非三洲。 公元前5世纪:波斯三征希腊,史称希波战争。 公元前6世纪:古印度的乔达摩·悉达多(释迦牟尼)建立佛教。 公元前509年:罗马共和国建立。 公元前356年:秦孝公发动商鞅变法。 公元前221年:秦王嬴政灭六国统一中国。 公元前202年:刘邦建立汉朝,定都长安,史称西汉。 公元前27年:屋大维建立罗马帝国。 公元2世纪:罗马帝国地跨亚欧非三洲。 1世纪:巴勒斯坦传说中的耶稣创立基督教。 25-220年:刘秀建立东汉,定都洛阳。 208年:赤壁之战。交战双方:曹操、孙刘联军。孙刘联军以少胜多,大败曹操。 220年:曹丕废掉汉献帝后称帝,国号魏,定都洛阳。 221年:刘备在成都称帝,国号汉,史称蜀或蜀汉。 222年:孙权称王。 229年:孙权称帝,国号吴,定都建业。 263年:魏灭蜀。 266年:司马炎建立西晋,魏亡。 280年:西晋灭吴,三国历史结束。 316年:西晋灭亡。 317年:司马睿建立东晋,定都建康。 395年:罗马帝国分裂成西罗马帝国和东罗马帝国。 5世纪:大和统一日本。 420年:南北朝形成。 476年:西罗马帝国灭亡,西欧奴隶社会结束。 5世纪末:法兰克王国建立,查理在位时达到全盛。 581年:杨坚建立隋朝,定都长安。 图1 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器; 保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。 如图1 。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。 个人理解: 1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。 2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。 关于建立时间保持时间的考虑 华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间T3和保持时间T4应满足什么条件? 分析: Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。 Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。 Tsetup:建立时间 Thold:保持时间 Tclk:时钟周期 建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。 保持时间容限:保持时间容限也要求大于等于0。 建立时间和保持时间和亚稳态之类一直都是概念类题的经典! 题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问,触发器D2的建立时间T3和保持时间应满足什么条件。 Tffpd:触发器输出的响应时间,也可以理解为触发器输出在clk上升沿到来后的时间内发生变化, 之后稳定,也可以理解输出延迟。 Tcomb: 触发器输出的变化经过组合逻辑元件所需的附加时间,也就是题目中的组合逻辑延迟 tsetup:建立时间 thold:保持时间 tclk: 时钟周期 建立时间容限:这里用容限的概念是为了数学推导方便,时间容限仅仅是一个概念,在这里我们对建立时间容限的要求是大于0,当然有的地方可能就是小于0了。 同样保持时间容限也是需要大于0的。 从图中,我们可以很清楚的看出,建立时间容限=tclk-tffpd(max)-tcomb(max)-tsetup 这里应该理解到,tffpd和tcomb都是要考虑最大值的那么根据建立时间容限>=0 推导出tsetup<=tclk-tffpd(max)-tcomb(max) 这里,我们是不是很清楚了理解了建立时间的要求是<=T-T2MAX,因为题目中没有考虑 tffpd。 同理,保持时间容限tffpd(min)+tcomb(min)-thold,这里是要取最小值,那么根据保持时间容限>=0推导出thold<=tffpd(min)+tcomb(min) 因为题目中没有考虑tffpd,而tcomb就是t2min,所以thold<=t2min。取最小值的原因就是在延时最小的情况下都应该满足保持时间。否则触发器输入无效。 在这里我们应该发现,从数学上看,虽然既有max又有min,但是thold,和tsetup都是小于最小值,因为tsetup 中共成立以来出现几次历史性转折的时间、地点、主要涉及的人物、历史背景和对中共以后的影响和意义 八七会议(1927年):八七会议是第一次国内革命战争失败以后,在关系党和革命事业前途和命运的关键时刻,中共中央政治局于1927年8月7日在汉口召开的紧急会议。会议总结了大革命失败的经验教训,坚决纠正和结束了陈独秀的右倾投降主义错误,撤销了他的总书记职务。会议确定以土地革命和以武装反抗国民党反动派的屠杀政策为党在新时期的总方针,并把发动农民举行秋收起义作为党在当时的最主要任务。八七会议在我党历史上是一个转折点。它给正处在思想混乱和组织涣散中的中国共产党指明了新的出路,为挽救党和革命作出了巨大贡献。这是由大革命失败到土地革命战争兴起的历史性转变。 遵义会议(1935年):1935年1月15日至17日,中共中央在长征途中抵达贵州遵义时举行政治局扩大会议。会议批评了第五次反“围剿”和长征以来中共中央在军事领导上的错误,通过了《中央关于反对敌人五次“围剿”的总结决议》,肯定了毛泽东等关于红军作战的基本原则。会议推选毛泽东为政治局常委,取消博古、李德的最高军事指挥权,决定仍由中央军委主要负责人周恩来、朱德指挥军事。随后在行军途中,中央先后决定由洛甫代替博古负总责,由毛泽东、周恩来、王稼祥组成三人指挥小组。遵义会议结束了王明“左”倾冒险主义在中央的统治,开始了以毛泽东为代表的新的中央的正确领导。这次会议在极端危急的历史关头,挽救了党和红军,是中国革命史上一个生死攸关的转折点。 中共十一届三中全会(1978年):1978年12月18-22日在北京举行。中心议题是讨论把全党工作的重点转移到社会主义现代化建设上来。全会果断地停止使用不适用于社会主义的“以阶级斗争为纲”、“无产阶级专政下继续革命”等错误口号,坚决地批判了“两个凡是”的错误方针,充分肯定必须完整地、准确地掌握毛泽东思想的科学体系,高度评价了关于真理标准问题的讨论,确定了解放思想、开放脑筋、实事求是、团结一致向前看的指导方针。全会开始全面地、认真地纠正“文化大革命”中和以前的“左”倾错误,及时地作出了从1979年起,把全党工作重点转移到社会主义现代化建设上来的战略决策,解决了我党从1957年以来未能解决好的工作重点转移问题,这是党在政治路线上最根本的拨乱反正。经济建设上要纠正急于求成的错误倾向和解决好国民经济重大比例严重失调等问题。要保障几亿农民的物质利益和民主权利。解决了历史上一批重大冤假错案。要健全党规党法和民主集中制。会议结束了1976年10月以来党的工作在徘徊中前进的局面。是建国以来我党历史上具有深远意义的伟大转折。 第一次国内革命战争,又称“大革命”,但不等同于“大革命”。是1924年至1927年中国人民在中国共产党和中国国民党合作领导下进行的反帝反封建的革命斗争。在中国共产党的历史中,称这段时期为“第一次国内革命战争时期”,简称“大革命时期”。 第一次是抗日战争时期(1941年),实行地主减租减息,农民交租交息的土地政策。 (时间管理)建立时间与保 持时间 建立时间和保持时间 建立时间(Tsu:setuptime)是指于时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能于这个时钟上升沿被稳定的打入触发器;保持时间(Th:holdtime)是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。建立和保持时间的简单示意图如下图1所示。 图1保持时间和建立时间的示意图 于FPGA设计的同壹个模块中常常是包含组合逻辑和时序逻辑,为了保证于这些逻辑的接口处数据能稳定的被处理,那么对建立时间和保持时间建立清晰的概念非常重要。下面于认识了建立时间和保持时间的概念上思考如下的问题。 图2同步设计中的壹个基本模型 图2为统壹采用壹个时钟的同步设计中壹个基本的模型。图中Tco是触发器的数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间;Tpd为时钟的延时。如果第壹个触发器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min。问第二个触发器D2立时间T3和保持时间T4应该满足什么条件,或者是知道了T3和T4那么能容许的最大时钟周期是多少。这个问题是于设计中必须考虑的问题,只有弄清了这个问题才能保证所设计的组合逻辑的延时是否满足了要求。 下面通过时序图来分析:设第壹个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2; 时钟统壹于上升沿进行采样,为了便于分析我们讨论俩种情况即第壹:假设时钟的延时Tpd 为零,其实这种情况于FPGA设计中是常常满足的,由于于FPGA设计中壹般是采用统壹的系统时钟,也就是利用从全局时钟管脚输入的时钟,这样于内部时钟的延时完全能够忽略不计。这种情况下不必考虑保持时间,因为每个数据均是保持壹个时钟节拍同时又有线路的延时,也就是均是基于CLOCK的延迟远小于数据的延迟基础上,所以保持时间均能满足要求, 【易错题】中考七年级历史上第二单元夏商周时期:早期国家与社会变革一模 试题带答案(3) 一、选择题 1.《史记·商君列传》记载:“商君相秦十年,宗室贵戚多怨望。”这主要是因为商鞅变法 A.承认土地私有,允许土地自由买卖 B.奖励耕战,高产者可免除徭役 C.规定按军功授爵赐田,废除旧贵族特权 D.统一货币、度量衡、文字 2.下面对西周分封制的叙述,正确的有 ( ) ①目的是巩固政权 ②周天子把土地和人民封给诸侯,让他们镇守疆土,保卫王室 ③诸侯国接受分封的同时,必须向周天子尽义务 ④分封制使周朝成为一个强盛的国家 A.①②③④B.①②③C.①②D.①②④ 3.为稳定周初的政治形势,巩固疆土,周王根据血缘关系远近和功劳大小,将宗亲和功臣等分封到各地,授予他们管理土地和人民的权力,建立诸侯国……这种制度叫 A.郡县制B.禅让制C.分封制D.世袭制 4.他不仅是大思想家,而且还是大教育家。他创办私学,主张“有教无类”,招收不同出身的学生,先后培养了三千弟子,促进了教育在民间的发展。教学中,注重德育和文化教育,发现和总结许多教育规律,提出了一系列教学原则和方法。他的核心思想是“仁”。他指的是 A.老子B.孔子C.孟子D.墨子 5.春秋五霸中最先称霸的是() A.宋襄公B.秦穆公C.晋文公D.齐桓公 6.我国有文字可考的历史开始于 A.夏朝B.商朝C.西周D.东周 7.据史书记载,西周初年的国家有800多个,到了春秋初年,还剩170多个,战国之初,只有十几个了.这反映了当时历史发展的趋势是( ) A.弱肉强食B.适者生存C.国家数量减少D.逐渐趋于统一8.郭沫若说“由秦到现在两千多年了,我们依然感觉着春秋战国在学术思想史上是中国的黄金时代。”是因为春秋战国出现 A.竞相改革的局面B.诸侯争霸局面 C.百家争鸣的局面D.商业繁荣局面 9.根据史书统计,春秋战国时期耕地面积为2.3亿亩,此后随着农田面积的拓展,耕地面积也不断扩大。春秋战国时期耕地面积不断扩大的主要原因是 A.都江堰的修建B.铁农具和牛耕的使用C.战争的纷繁 D.诸侯争霸 10.有人说:“‘封邦建国’加强了周王室与各诸侯国的经济、文化联系”这主要是评价 第二课时:拜占庭与俄罗斯 【教学目标】(以五大核心素养为据、结合课标分析、教材分析、学情分析)1.参照课本,识记封君与封臣的契约关系、特定仪式、政治意义;庄园的性质 与规模、人口与土地构成、庄园法庭的地位与作用基本史实。感知封君封臣制度、庄园与农奴制度所体现的经济基础决定上层建筑的唯物史观。 2.结合史料,用自己的话说出城市居民构成、自治方式、城市自治的影响,感 受材料体现的中世纪基督教的显赫经济与精神力量,提高史料实证的能力,把握城市与宗教对于王权强化的重要影响,培养论从史出的学习方法。 3.观察《拜占庭帝国图》,了解帝国发展基本历程,加深自身历史学习的时空 观念。在此基础上分析帝国兴衰的原因、启示(保守与创新);识记《查士丁尼法典》的构成与重要地位。认识到罗马法是重要的人类文化遗产,并且对古代西方社会和近代文明产生都有重要影响。培养正确对待和汲取人类优秀文化成果的情怀。 4.小组讨论,就“基辅罗斯”到“俄罗斯帝国”的历史进程制作年表,并科学 评价伊凡四世政治举措(特别是特辖领地制)在其中的作用,增强自身自主进行历史解释的能力。 【教学重难点】 (一)教学重点 1.西欧封建社会的两大主要特征(封君封臣与庄园制度); 2.基督教会与城市在中世纪的地位与王权的相互关系; 3.拜占庭帝国的法律成就与俄罗斯帝国伊凡四世的政治举措 (二)教学难点 1.从唯物史观角度看待基督教的显赫地位对于欧洲封建王权促进与阻碍的双重作用。 2.古今相映,在学习拜占庭帝国的“盛”与“衰”中建立与时俱进的创新精神,培养正确对待和汲取人类优秀文化成果的情怀。 【教学策略与方法】 1.教法: 讲授法、讲读法、图示法、演示法 2.学法: 听课法、阅读教材法、探究问题法、记忆法、练习法 3.教具: 黑板、多媒体、地图 【教学过程】 导入新课 [讲述]:同学们好,在开始今天的课程之前啊,老师想给大家观看一组图片。[PPT展示]: 老师:这是上个月杜嘉班纳堪称“视觉盛宴”的时装展示,金色刺绣配上马赛克的宗教图案,这种风格源于哪里呢?事实上就来自今天我们要学习的一大帝国---拜占庭,这是一个怎样的帝国、又在历史的长河中留下多少痕迹?以至于时至今日依旧被视为一种“时尚”。今天,就让我们以一名普通游客的身份走进拜占庭帝国、找寻历史足迹。 [设计意图]:结合身边时事、迎合学生兴趣,以“时装秀”吸引学生兴趣、自然过渡到拜占庭帝国的学习。 一、拜占庭帝国游记 PrimeTime是Synopsys的一个单点的全芯片、门级静态时序分析器。它能分析大规模、同步、数字ASICS的时序。PrimeTime工作在设计的门级层次,并且和Synopsys 其它工具整合得很紧密。 基本特点和功能: 时序检查方面: 建立和保持时序的检查(Setup and hold checks) 重新覆盖和去除检查(Recovery and removal checks) 时钟脉冲宽度检查(Clock pulse width checks) 时钟门锁检查(Clock-gating checks) 设计检查方面: 没有时钟端的寄存器 没有时序约束的结束点(endpoint) 主从时钟分离(Master-slave clock separation) 有多哥时钟的寄存器 对层次敏感的时钟(Level-sensitive clocking) 组合电路的反馈环(Combinational feedback loops) 设计规则检查,包括最大电容(maximum capacitance)、最大传输时间(maximum transition)和最大扇出(maximum fanout) PrimeTime 时序分析流程和方法: 在时序分析之前需要做的步骤: 1、建立设计环境 -建立搜索路径(search path)和链接路径(link path) -读入设计和库 -链接顶层设计 -建立运作条件、连线负载模型、端口负载、驱动和传输时间 2、说明时序声明(约束) -定义时钟周期、波形、不确定性(uncertainty)和滞后时间(latency) -说明输入、输出端口的延时 3、说明时序例外情况(timing exceptions) -多周期路径(multicycle paths) -不合法路径(false paths) -说明最大和最小延时、路径分割(path segmentation)和失效弧(disabled arcs) 4、进行分析和生成报告 -检查时序 -生成约束报告 -生成路径时序报告 建立时间和保持时间 信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,Setup/Hold time 是测试芯片对输入信号和时钟信号之间的时间要求,也就是它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是芯片本身的特性。 建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间Setup time.如不满足Setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器; 保持时间是指触发器的时钟信号上升沿到来以后,数据也必须保持一段时间,数据保持不变以便能够稳定读取(信号在器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。信号的高低电平转换也需要一定的过渡时间。)。如果hold time 不够,数据便不能被有效读取并转换为输出。如果数据信号在时钟边沿触发前后持续的时间分别超过建立时间和保持时间,那么这部分超过的分量分别称为建立时间裕量和保持时间裕量。 (这期间其实还涉及到竞争冒险的问题,也就是毛刺,稍后在研究,建立保持时间的存在即是触发器内部的特性又在屏蔽毛刺方面起到了一定的作用。)其实建立时间就是在脉冲信号到来时,输入信号已经稳定等待的时间; 而保持时间是信号脉冲到来后,而输入信号还没有到达下降沿的时间。 举个例子:建立时间就是你到朋友家做客去早了,但是主人还没回来,你等待的时间就是建立时间;保持时间就是进入房子后,逗留的(有效)时间。 高考夏朝历史知识点:建立夏朝 相传尧、舜、禹时,部落联盟内采用“禅让”的方式“选贤与能”,推举联盟的共主。如尧老时,把“王”位禅让给了贤能的舜。 舜把帝位禅让给禹,禹在涂山召集部落会盟,再次征讨三苗。据《左传》记载“执玉帛者万国”参加了涂山会盟,可见夏部落的号召力。有一次在会稽部落会盟时,防风氏首领因迟到而被禹处死。古文献中亦记载禹以诸侯部落路途的远近来分别纳贡约多少,可见夏氏族对其周边部落经济上的控制。 禹曾推举东方颇有威望的偃姓首领皋陶为继承人,以示对传统禅让制的尊重。然而皋陶没有等及禅让,比禹早死。禹又命东夷首领伯益为继承人。 夏王启禹死后,益按照部落联盟的传统,为禹举行丧礼,挂孝、守丧三年。三年的丧礼完毕以后,伯益没有得到权位,反而在民众的拥护下,启得到了权位。关于这一段历史的记载不一。古本《竹书纪年》记载称,益即位后,启杀益而夺得君位。另一说益继位后,有些部族并没有臣服益,而拥护启,并对益的部族展开战争,最后启胜而夺得权位。之后益率领着东夷联盟讨伐启。经过几年的斗争后,启确立了他在部族联盟中的首领地位。先秦文献记载此事的共同点就是“公 天下”变成“家天下”。 夏朝历史上惯称为“夏”。关于“夏”字的名义来源学界主要有十种说法,其中较为可信的观点认为“夏”为夏族图腾的象形字。司马迁记载“夏”是姒姓夏后氏、有扈氏、有男氏、斟鄩氏、彤城氏、褒氏、费氏、杞氏、缯氏、辛氏、冥氏、斟灌氏十二个氏族组成的部落的名号,以“夏后”为首,因此建立夏朝后就以部落名为国号。唐·张守节则认为“夏”是大禹受封在阳翟为“夏伯”后而得名。又说,“夏”是从“有夏之居”、“大夏”地名演变为部落名,遂成为国名。中国中原地区从此出现“国家”的概念这便是不少历史学家所认为中国的第一个世袭王朝夏朝的起始。 王朝的盛衰周期 中国自古以来有一句话:分久必合,合久必分。这似乎是一种周期。历史学家眼中也有一种周期,他们认为朝代由盛转衰是一定的,幵国时必定兴盛太平,而这个朝代将要结束时,一定是内忧外患接踵而至。这两个观念中所说的周期”,并不是一个必然的历史规律,却正好描述了一个政治共同体,将其当做一个复杂系统来看,它是如何逐渐失去自己的调节能力,以至于不能面对困难的。 分久必合,合久必分 先说分合观念。中国是很庞大的地区,各个地理区域天然条件不一样,合在一起成为一个共同体,必须是各个区域之间能够互补而无冲突。朝代刚兴盛的时候,通常是大乱以后,一个新的秩序出现了,各个地区可以重新调节,彼此形成互补的关系;在各地区之间协调与重新分配资源,也正是一个新政权的重要任务。建立一些新的交通网和新的管理制度,都是为了要把若干互相冲突的地区,重新放在一个系统之内,这个调节的过程可能要花很长的时间。比如说,汉代分裂以后,要到唐代才重新建构起一个南北之间相互协调的新秩序。汉代是东西方向的结合,物产和人力资源都是靠横向的几条大路和纵向的分支路线,将帝国结合为一个整体。汉代崩溃以后,北方少数民族的入侵导致南北分裂,各走各的发展路线。中间经过数百年的时间,其实南北的物产和人口配置都已经不一样了,隋唐之间建立的大运河,就是重新结合南北的一个新的配套设施。 各区的核心与边陲的关系,也因为新的资源分配而有所不同。秦汉的核心,是在于关中和中原的配合,隋唐也是如此。但是在宋以后,核心实际上在逐渐南移。北宋虽然中央政府在北方,但财富和资源都已经移向南方,甚至于南方人才也逐渐多了。这个南移的趋向延续不断。南宋时代疆域只有北宋的一半,但国家的财力不但并未减少,反而比北宋时候更好些。 暖风熏得游人醉,直把 杭州作汴州”,这是一个自然的现象。到了明代,南北的差异更为显著。政府保持南北两直隶作为中央直辖的领土,在这南北两个直隶之内,不分封任何亲王。但实际上,北直隶是北京的外围,大量的军队驻屯在这些地区,南直隶却是财富的所在经过大运河往北方运粮食,是北京建都后主要的粮食供应方式,明清两代都如此。至慵代晚期,沿海地区,如华南和东南,都是支持国家的主要资源所在地。分久必合、合久必分,都取决于中央政府能不能有效地掌握各主要地区的资源。 人才的选拔机制是否合理 再说盛衰周期。朝代刚起来的时候,似乎满地都是人才;朝代结束的时候,人才都不见了。这并不是说天地生才在不同的时段有不同的分布,而是有才之士能不能被吸收到国家的管理机构之中,以维持一个有效的管理体系。中国历代的王朝都是帝国制度,而且中央集权的趋向一朝比一朝严重。也就是说,统治阶层是一个密封的集团。在幵国之初,功臣将相来自各方,成分是多元而复杂的,这些人才聚在一起,又经过打天下的历练,都是富有经验的人物,他们的合作确实可以形成一个很强的团队。一代、两代过下去,功臣子弟成了纨绔,只知享乐,不会办事。皇室集团本身是一个非常狭小的团体,再加上逐渐有了皇权传嫡子的规矩,这个可以从中选择领导的人才库,就非常狭小了。皇权本身是不容挑战的,于是,依附在皇权四周的权贵,包括宦官和宠臣,代表皇权统治整个庞大的国家。这个团体延续日关于建立时间(setup-time)保持时间(hold-time)以及时序的一些问题集合

古埃及史与夏朝历史对比揭示真实地夏(2015-10-10205638)

解读高速数模转换器(DAC)的建立和保持时间

“夏”与“夏朝”、历法、干支

时序分析中建立时间,保持时间,时钟到输出,PIN到PIN延时的说明

史上十个最强帝国:中国统治世界三次

第二章 夏商时期奴隶制国家的建立和发展

建立时间和保持时间关系详解

夏朝和商朝练习题

世界历史时间顺序

建立时间和保持时间

建立时间和保持时间和亚稳态之类一直都是概念类题的经典

中共成立以来出现几次历史性转折的时间

{时间管理}建立时间与保持时间

【易错题】中考七年级历史上第二单元夏商周时期:早期国家与社会变革一模试题带答案(3)

2019-2020学年部编版必修《中外历史纲要》下 第3课 中古时期的欧洲 第二课时 教案

第06章3 PrimeTime-3

建立时间和保持时间

高考夏朝历史知识点:建立夏朝

王朝的盛衰周期