1.锁相环的基本原理和模型

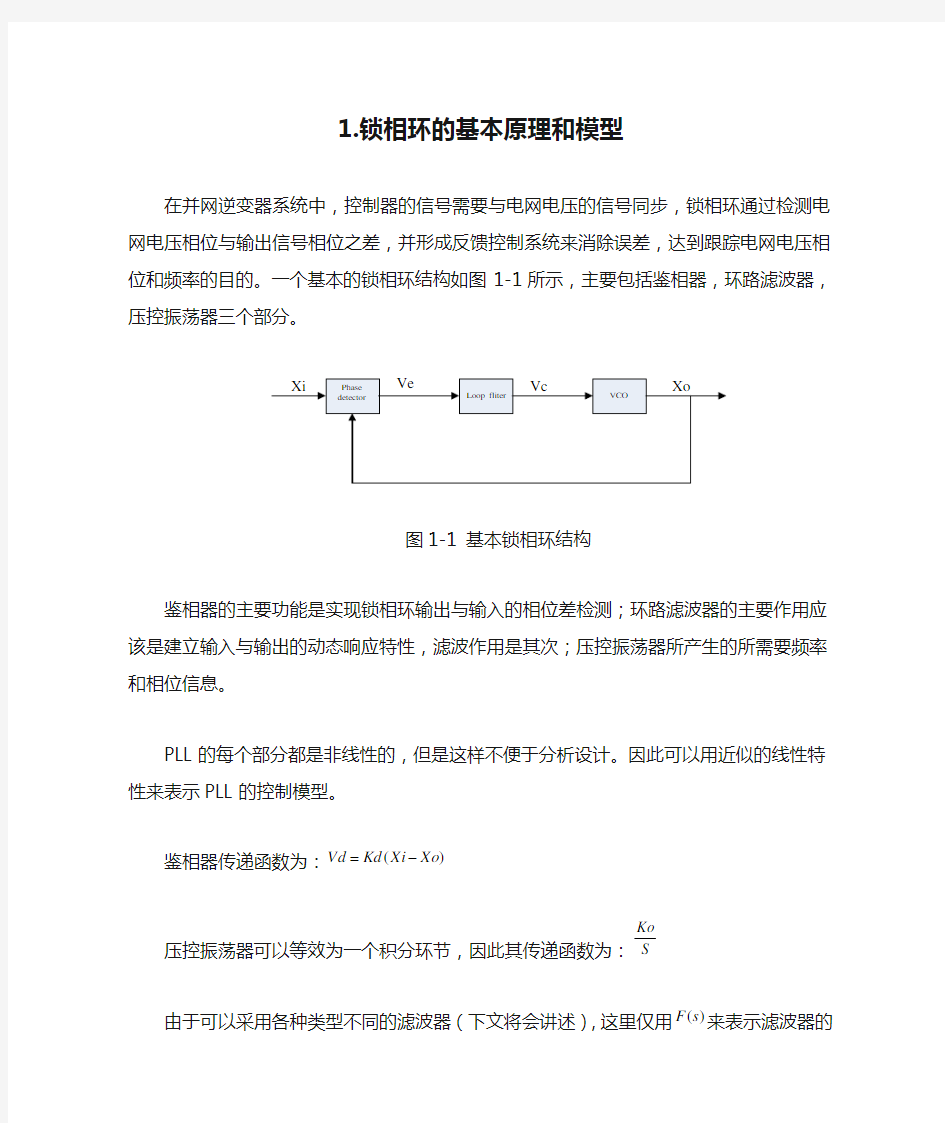

在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。

图1-1 基本锁相环结构

鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。

PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。

鉴相器传递函数为:)(Xo Xi Kd Vd -=

压控振荡器可以等效为一个积分环节,因此其传递函数为:S

Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。

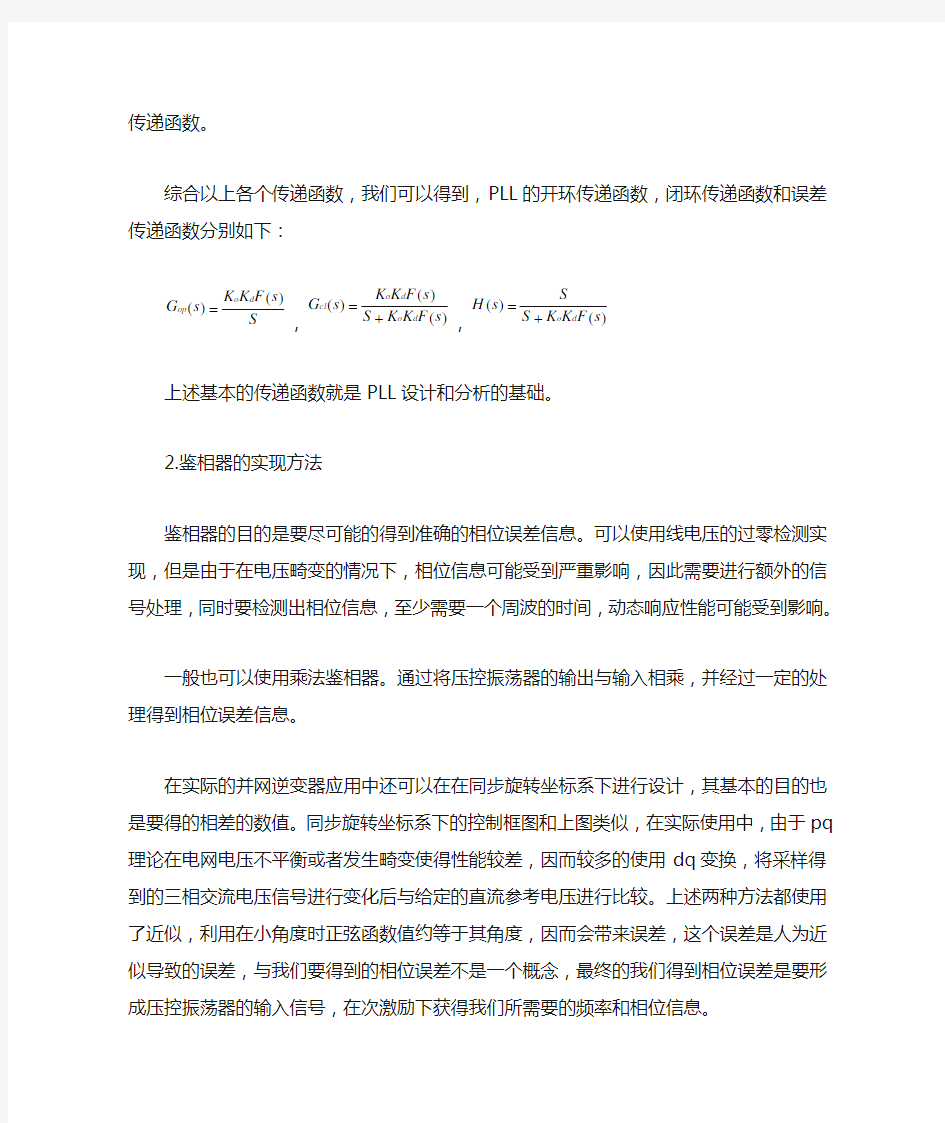

综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下:

S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,)

()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。

2.鉴相器的实现方法

鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。

一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。

在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。

2.1乘法鉴相器

乘法鉴相器是一种较为普遍的传统检相方法,其原理是基于以下数学表达式:

[])()(2

1)(*)(B A Sin B A Sin B Sin A Sin -++= 一般的可以假设PLL 的输入信号))((t t w Sin Xi i i θ+=,输出信号为))((t t w Sin Xo o o θ+=。那么根据上述等式可以得到:

))()()((2

1))()((21))

(())((t o t i t w w Sin t o t i t w t w Sin t t w Sin t t w Sin o i o i o o i i θθθθθθ-+-++++=+*+ 这个式子包括两个部分,左边部分是一个近似两倍基频的波分分量,由于经过负反馈调节后,频率相差不大,因此右边部分可以近似认为是一个低频或者直流分量,即可以近似认为PLL 输入与输出相乘以后得到的结果是:

))()((2

1t o t i Sin θθ-,更进一步的,对于较小的相角差值,我们可以近似认为:)())()((21))()((21t t o t i t o t i Sin δθθθθθ=-=-,从而得到相角差。那么要想只得到右边的直流分量,可以做个很简单的处理,将两倍基频分量用低通滤波器滤除即可。

其控制框图如图2所示:

图2 乘法鉴相器

2.2同步旋转坐标系下相位检测

同步旋转坐标变化下三相PLL 系统的控制框图如图3所示。

图3 三相PLL 系统基本框图

abc 坐标系下的系统三相电压采样值经过dq 变换后转化为同步旋转坐标下的直流电压分量d U 和q U ,相角*θ可以经过*w 积分得到,环路滤波器的作用是来获得所需要的*w 。 设系统三相电压采样值为:?????

???????+-=??????????)32cos()32cos(cos πθπθθU U U U U U sc sb sa 变换矩阵为:??

????-????????????---=****θθ

θθcos sin sin cos 232302121132C 因此有??????---=????

??????=??????**)cos()sin(θθθθU U U U U C U U sc sb sa q d ,要使得系统电压相角θ与PLL 输出相角*θ相等,即相角误差为零,实现完全跟踪,那么就有d U 为零,如果将参考电压dref U 设置为零,则可以锁定电压相角。

同样的,在相角误差很小的情况下,我们有近似关系**-≈-θθθθ)sin(,所以可得简化的模型,其控制框图如图4:

图4 三相PLL 系统简化控制框图

按照上面的分析,上图中的正弦环节可以省略。

3.滤波器的选择

滤波器是锁相环的核心部分,其性能直接决定了环路滤波器的性能。不同的环路滤波器,控制模型有不同的传递函数,具体来说就是传递函数的阶数与类型的不同,从而导致设计方法上的差异与跟踪性能不同,重点设计部分应该是环路滤波器种类的选取和参数的设计。滤波器有很多,但是我们要注意,应该保证最终的系统闭环传递函数的阶数在三阶以下,最常用的是二阶,即使是高阶也经常近似简化为二阶来进行设计,三阶以上的系统因为设计困难而很少使用。当我们确定了环路滤波器的类型和参数后,并用BODE 图分析其频率响应,验证其控制性能,例如普遍使用的表征控制器性能的参数:带宽,截止频率,阻尼系数等等,可以参考各种控制参数调节方法反复进行参数的调试以获得最佳的性能。滤波器设计应该是响应时间与跟踪精度的折中,对于高精度场合,可以让响应时间稍微长一些以获得较高的跟踪精度。对于需要实时控制的场合,可以增大其带宽来获得较快的响应时间。

在不同的阻尼比,带宽,自然频率值下,超调量,响应时间,跟踪误差都各不相同,对于参数的选取很重要。一般来说平衡无畸变的三相系统中,参数相对好设计一些。在各种非理想和故障状态下的参数调节则依据具体情况,和所希望获得的性能而决定。

3.不同类型的滤波器及PLL 闭环频率响应分析

3.1理想二阶环节(相当于一个PI 环节) 理想二阶环节的传递函数可表示为:S

K K s s i p +=+121ττ,PI 控制器相当于增加了一个位于原点的开环极点,同时也增加了一个位于S 左半平面的开环零点。极点提高系统型别,减小了稳态误差。增加的开环零点减小系统阻尼,缓和PI 控制器对系统稳定性及动态过程产生的不利影响。其频率响应如图6所示

图6 理想二阶环节频率响应

由此可以写出PLL 系统的开环和闭环传递函数分别是:)()(S K K S U s G i p op +*=

i

p i p op op cl UK S UK S UK S UK s G s G s G +++=+=2)(1)()( 将上述闭环传递函数写成二阶传递函数的标准形式:2

2

222n n n n w S w S w S w +++εε,其中i n UK w =,i

p K U K 2=ε。设V U 3112220=*=。对于典型的二阶系统,要取得较优的性能,可以取ε=0.707。有文献用n w 来衡量控制系统的带宽,对于二阶系统,这个是可取的。现在取不同的n w (取n w 分别为100,200,300,400,500),观察二阶系统的频率响应特性,如图5。

图7 不同自然频率情况下系统频率响应特性

曲线具有高频衰减特性,即低通特性。在不同的自然频率下,幅值裕量为无穷大,相角裕量都为127°,但是具有不同的谐振峰值和谐振频率,不同的穿越频率,同时在穿越频率处(幅值裕度为零的频率点),相位滞后都小于180°,系统是稳定的。

3.2无源比例积分滤波器 无源比例积分滤波器的传递函数可表示为:S

S 1211ττ++(21ττ>)。这实际上是一个超前滞后滤波器,将传递函数变形可以得到)1111(111

121212τττττττ+-+=++S S S ,与前述的PI 环节相比,在11τ较小的情况下,我们可以近似认为它是一个不完美的积分器,实际的完美积分器不容

易实现,在很多情况下,可以用上面的低通滤波器来代替。其频率响应如图8所示

图8 无源比例积分滤波器频率响应

PLL 系统的开环和闭环传递函数如下:)1111()(1

12

12τττττ+-+*=S S U s G op 1

1221121)(1)()(ττττττU

S U S U S U s G s G s G op op cl ++++=+= 3.3 RC 积分滤波器

RC 积分滤波器的传递函数为

S

τ+11,它就是一个低通滤波器。给原系统增加了一个负实零点。其频率响应如图7所示

图7 RC 积分滤波器的频率响应

PLL 系统的开环和闭环传递函数分别为:S

S U s G op τ+*=11)(

??????????U S S U ??s G s G s G op op cl τ

ττ++=+=2)(1)()( 实际使用的上述滤波器都是一阶滤波器,因此最终的都的PLL 系统闭环传递函数都是二阶系统。但是也有高阶情况的,有文献中使用了二阶butterworth 滤波器,其传递函数为:

2

022

0)(n w S w S w s H ++= 那么最终得到的PLL 系统将会是三阶系统。

由于上述系统都是二阶的,因此都可以用类似的方法的进行设计,根据实际情况所需要的性能来合理的选择参数。

以PI 环节为例,在matlab 中搭建仿真电路,仿真条件设置为:三相平衡电压源,频率为50HZ ,相电压参数为500V ,在ε=0.707,n w =100的情况下,可以得到PI 参数分别为:Kp=14,Ki=69306。仿真电路如图8:

图8 三相平衡条件下PLL仿真图输出波形如图9:

cos)

图9(a)PLL输出(wt

图9(b)PLL输出(wt)

图9(c)q轴电压波形

由上图可以看出,在三相平衡情况下,PLL输出能很好的跟踪电网电压频率和相位,并且波形没有畸变,大概半个周波的时间就能实现准确跟踪。

比较线性模型和P r o b i t 模型L o g i t模型 Document serial number【LGGKGB-LGG98YT-LGGT8CB-LGUT-

研究生考试录取相关因素的实验报告 一,研究目的 通过对南开大学国际经济研究所1999级研究生考试分数及录取情况的研究,引入录取与未录取这一虚拟变量,比较线性概率模型与Probit模型,Logit模型,预测正确率。 二,模型设定 表1,南开大学国际经济研究所1999级研究生考试分数及录取情况见数据表 定义变量SCORE:考生考试分数;Y:考生录取为1,未录取为0。 上图为样本观测值。 1.线性概率模型 根据上面资料建立模型 用Eviews得到回归结果如图: Dependent Variable: Y

Method: Least Squares Date: 12/10/10 Time: 20:38 Sample: 1 97 Included observations: 97 Variable Coefficient Std. Error t-Statistic Prob. C SCORE R-squared Mean dependent var Adjusted R-squared . dependent var . of regression Akaike info criterion Sum squared resid Schwarz criterion Log likelihood F-statistic Durbin-Watson stat Prob(F-statistic) 参数估计结果为: i Y ?+ i SCORE Se=( t= p= 预测正确率: Forecast: YF Actual: Y Forecast sample: 1 97 Included observations: 97 Root Mean Squared Error Mean Absolute Error Mean Absolute Percentage Error Theil Inequality Coefficient Bias Proportion Variance Proportion Covariance Proportion 模型 Dependent Variable: Y Method: ML - Binary Logit (Quadratic hill climbing) Date: 12/10/10 Time: 21:38 Sample: 1 97 Included observations: 97 Convergence achieved after 11 iterations Covariance matrix computed using second derivatives Variable Coefficient Std. Error z-Statistic Prob.

锁相电路(PLL)及其应用 自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的围。 目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。 一、锁相环路的基本工作原理 1.锁相环路的基本组成 锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。 图1 锁相环路的基本组成框图 将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。 在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出

控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。 2.锁相环路的捕捉与跟踪过程 当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。锁相环由失锁到锁定的过程,人们称为捕捉过程。系统能捕捉的最大频率围或最大固有频带称为捕捉带或捕捉围。 当锁相环路锁定后,由于某些原因引起输入信号或压控振荡器频率发生变化,环路可以通过自身的反馈迅速进行调节。结果是VCO 的输出频率、相位又被锁定在基准信号参数上,从而又维持了环路的锁定。这个过程人们称为环路的跟踪过程。系统能保持跟踪的最大频率围或最大固有频带称为同步带或同步围,或称锁定围。 捕捉过程与跟踪过程是锁相环路的两种不同的自动调节过程。 由此可见,自动频率控制(AFC )电路,在锁定状态下,存在着固定频差。而锁相环路控制(PLL )电路,在锁定状态下,则存在着固定相位差。虽然锁相环存在着相位差,但它和基准信号之间不存在频差,即输出频率等于输入频率.这也表明,通过锁相环来进行频率控制,可以实现无误差的频率跟踪.其效果远远优于自动频率控制电路. 3.锁相环路的基本部件 1)鉴相器(PD —Phase Detector ) 鉴相器是锁相环路中的一个关键单元电路,它负责将两路输入信号进行相位比较,将比较结果从输出端送出。 鉴相器的电路类型很多,最常用的有以下三种电路. (1)模拟乘法器鉴相器,这种鉴相器常常用于鉴相器的两路输入信号均为正弦波的锁相环电路中。 (2)异或门鉴相器,这种鉴相器适合两路输入信号均为方波信号的锁相环电路中,所以异或门鉴相器常常应用于数字电路锁相环路中。 (3)边沿触发型数字鉴相器,这种鉴相器也属于数字电路型鉴相器,对输入信号要求不严,可以是方波,也可以是矩形脉冲波.这种电路常用于高频数字锁相环路中。 图2 是异或门鉴相器的鉴相波形与鉴相特性曲线。

研究生考试录取相关因素的实验报告 一,研究目的 通过对南开大学国际经济研究所1999级研究生考试分数及录取情况的研究,引入录取与未录取这一虚拟变量,比较线性概率模型与Probit模型,Logit模型,预测正确率。 二,模型设定 表1,南开大学国际经济研究所1999级研究生考试分数及录取情况见数据表

定义变量SCORE :考生考试分数;Y :考生录取为1,未录取为0。 上图为样本观测值。 1. 线性概率模型 根据上面资料建立模型 i i i SCORE B B Y μ++=*21 用Eviews 得到回归结果如图: Dependent Variable: Y Method: Least Squares Date: 12/10/10 Time: 20:38 Sample: 1 97 Included observations: 97 Variable Coefficient Std. Error t-Statistic Prob. C -0.847407 0.159663 -5.307476 0.0000 SCORE 0.003297 0.000521 6.325970 0.0000 R-squared 0.296390 Mean dependent var 0.144330 Adjusted R-squared 0.288983 S.D. dependent var 0.353250 S.E. of regression 0.297866 Akaike info criterion 0.436060 Sum squared resid 8.428818 Schwarz criterion 0.489147 Log likelihood -19.14890 F-statistic 40.01790 Durbin-Watson stat 0.359992 Prob(F-statistic) 0.000000

锁相环及其应用 所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位 误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常 用PLL表示。 称VCO )三个部件组成闭合系统。这是一个基本环路,其各种形式均由它变化而来 PLL概念 设环路输入信号V i= V im Sin( 3 i t+ 0 i) 环路输出信号V o= V om Sin( 3 o t+ 0 o) 其中 3 o = 3 r +△ 3 o 率的自动控制系统称为锁相环路 PLL构成 由鉴相器(PD环路滤波器(LPF)压控振荡器(VCO组成的环路 通过相位反馈控制, 最终使相位保持同步, 实现了受控频率准确跟踪基准信号频锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF )和压控振荡器(简

ejt 戶心(tAejt)谋差相檯 PLL 原理 从捕捉过程一锁定 A.捕捉过程(是失锁的) 0 i — 0 i 均是随时间变化的,经相位比较产生误差相位 0 e = 0 i - 0 o ,也是变化的。 b. 0 e (t)由鉴相器产生误差电压 V d (t)= f ( 0 e )完成相位误差一电压的变换作用。 V d (t)为交流电压。 C. V d (t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由 VCO 产生 控制角频差△ 3 0,使3 0随3i 变化。 B.锁定(即相位稳定) 即 3 0= 3 r + △ 3 Omax 。 3 r 为VCO 固有振荡角频率。) 锁相基本组成和基本方程(时域) 各基本组成部件 鉴相器(PD) a. 一旦锁定0 e (t)= 0 e -(很小常数) V d (t)= V d (直流电压) b. 3 0= 3 i 输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ 3 Omax

1.锁相环的基本原理和模型 在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。 图1-1 基本锁相环结构 鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。 PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。 鉴相器传递函数为:)(Xo Xi Kd Vd -= 压控振荡器可以等效为一个积分环节,因此其传递函数为:S Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。 综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下: S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,) ()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。 2.鉴相器的实现方法 鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。 一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。 在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。 2.1乘法鉴相器

基本组成和锁相环电路 1、频率合成器电路 频率合成器组成: 频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射 信号源,发射信号源主要由锁相环和VCO 电路直接产生。如图3-4 所示。 在现在的移动通信终端中,用于射频前端上下变频的本振源(LO ),在射频电路中起着非常 重要的作用。本振源通常是由锁相环电路(Phase-Locked Loop )来实现。 2.锁相环: 它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域 3.锁相环基本原理: 锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD 或 PC):是完成相位比较的单元, 用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF): 是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的 作用 .通常由电阻、电容或电感等组成,有时也包含运算放大器。⑶压控振荡器(VCO ):振

荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。在PLL 中,压控振荡器实际上是把控制电压转换为相位。 1、压控振荡器的输出经过采集并分频; 2、和基准信号同时输入鉴相器; 3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压; 4、控制 VCO ,使它的频率改变; 5、这样经过一个很短的时间,VCO的输出就会稳定于某一期望值。 锁相环电路是一种相位负反馈系统。一个完整的锁相环电路是由晶振、鉴相器、R 分频器、N 分频器、压控振荡器(VCO )、低通滤波器(LFP)构成,并留有数据控制接口。 锁相环电路的工作原理是:在控制接口对R 分频器和N 分频器完成参数配置后。晶振产生 的参考频率( Fref)经 R 分频后输入到鉴相器,同时VCO 的输出频率( Fout)也经 N 分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式 输出,并通过 LFP 滤波,加到 VCO 的调制端,从而控制 VCO 的输出频率,使鉴相器两输入端的 输入频率相等。 锁相环电路的计算公式见公式: Fout=(N/R)Fref 由公式可见,只要合理设置数值N 和 R,就可以通过锁相环电路产生所需要的高频信号。 4.锁相环芯片 锁相环的基准频率为13MHz ,通过内部固定数字频率分频器生成5KHz 或 6.25KHz 的参考频率。 VCO 振荡频率通过IC1 内部的可编程分频器分频后,与基准频率进行相位比较,产 生误差控制信号,去控制VCO,改变VCO的振荡频率,从而使VCO输出的频率满足要求。如图 3-5 所示。 N=F VCO /F R N:分频次数 F VCO: VCO 振荡频率

什么是锁相环(PLL)工作原理及对硬件电路连接的要求锁相环是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同 步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在 比较的过程中,锁相环电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。 在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。因此,所有板卡上各自的本地80MHz 和20MHz时基的相位都是同步的,从而采样时钟也是同步的。因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。 通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线来实现的;这时,其中一块版板卡会作为主卡并且输出其内部时钟,通过RTSI线,其他从板卡就可以获得这个用于同步的时钟信号,对于基于PXI总线的产品,则通过将所有板卡的时钟于PXI内置的 10MHz背板时钟同步来实现锁相环同步的。 锁相环(PLL)的工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的 原理框图如图8-4-1所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

probit模型与logit模型 2013-03-30 16:10:17 probit模型是一种广义的线性模型。服从正态分布。 最简单的probit模型就是指被解释变量Y是一个0,1变量,事件发生地概率是依赖于解释变量,即P(Y=1)=f(X),也就是说,Y=1的概率是一个关于X的函数,其中f(.)服从标准正态分布。 若f(.)是累积分布函数,则其为Logistic模型 Logit模型(Logit model,也译作“评定模型”,“分类评定模型”,又作Logistic regression,“逻辑回归”)是离散选择法模型之一,属于多重变量分析范畴,是社会学、生物统计学、临床、数量 心理学、市场营销等统计实证分析的常用方法。 逻辑分布(Logistic distribution)公式 P(Y=1│X=x)=exp(x’β)/1+exp(x’β) 其中参数β常用极大似然估计。 Logit模型是最早的离散选择模型,也是目前应用最广的模型。Logit模型是Luce(1959)根据IIA特性首次导出的;Marschark(1960)证明了Logit模型与最大效用理论的一致性;Marley (1965)研究了模型的形式和效用非确定项的分布之间的关系,证明了极值分布可以推导出Logit 形式的模型;McFadden(1974)反过来证明了具有Logit形式的模型效用非确定项一定服从极值分布。 此后Logit模型在心理学、社会学、经济学及交通领域得到了广泛的应用,并衍生发展出了其他离散选择模型,形成了完整的离散选择模型体系,如Probit模型、NL模型(Nest Logit model)、Mixed Logit模型等。模型假设个人n对选择枝j的效用由效用确定项和随机项两部分构成:Logit模型的应用广泛性的原因主要是因为其概率表达式的显性特点,模型的求解速度快,应用方便。当模型选择集没有发生变化,而仅仅是当各变量的水平发生变化时(如出行时间发生变化),可以方便的求解各选择枝在新环境下的各选择枝的被选概率。根据Logit模型的IIA特性,选择枝的减少或者增加不影响其他各选择之间被选概率比值的大小,因此,可以直接将需要去掉的选择枝从模型中去掉,也可将新加入的选择枝添加到模型中直接用于预测。 Logit模型这种应用的方便性是其他模型所不具有的,也是模型被广泛应用的主原因之一。Logit模型的优缺点 Logit模型的优点是: (1)模型考察了对两种货币危机定义情况下发生货币危机的可能性,即利率调整引起的汇率 大幅度贬值和货币的贬值幅度超过了以往的水平的情形,而以往的模型只考虑一种情况。 (2)该模型不仅可以在样本内进行预测,还可以对样本外的数据进行预测。 (3)模型可以对预测的结果进行比较和检验,克服了以往模型只能解释货币危机的局限。 虽然Logit模型能够在一定程度上克服以往模型事后预测事前事件的缺陷,综合了FR模型中FR概率分析法和KLR模型中信号分析法的优点,但是,它只是在利率、汇率等几个主要金 融资产或经济指标的基础上预警投机冲击性货币危机,与我们所要求的一般货币危机预警还有所差异。所以仅用几个指标来定义货币危机从而判断发生货币危机的概率就会存在一定问题,外债、进出口、外汇储备、不良贷款等因素对货币危机的影响同样非常重要。 logit模型也叫Logistic模型,服从Logistic分布。 probit模型服从正态分布。 两个模型都是离散选择模型的常用模型。但logit模型简单直接,应用更广。 离散选择模型的软件很多,有limdep,elm、nlogit等。 spss18.0中能做2元和多元logit模型。 stata,sas,guass都能做logit模型。 入门级的软件是spss和elm,后者可以做多元logit和分层logit。但是elm必须购买注册号才能

锁相环基本原理 一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成,如图1, Ud = Kd (θi –θo) U F = Ud F (s ) θi θo 图1 一.鉴相器(PD ) 构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。 异或门的逻辑真值表示于表1,图2是逻辑符号图。 表1图2 从表1可知,如果输入端A 和B 分别送 2π 入占空比为50%的信号波形,则当两者 存在相位差?θ时,输出端F 的波形的 占空比与?θ有关,见图3。将F 输出波 形通过积分器平滑,则积分器输出波形 的平均值,它同样与?θ有关,这样,我 们就可以利用异或门来进行相位到电压 ?θ 的转换,构成相位检出电路。于是经积 图3 分器积分后的平均值(直流分量)为: U U=Vdd*?θ/π (1) Vcc 不同的?θ,有不同的直流分量Vd 。 ?θ与V 的关系可用图4来描述。 从图中可知,两者呈简单线形关 1/2Vcc 系: Ud = Kd *?θ (2) 1/2ππ?θ Kd 为鉴相灵敏度图4 F O o U K dt d =θV PD LPF VCO Ui Uo V A B F __F = A B + A B F B A

2. 边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。 二. 压控振荡器(VCO ) 压控振荡器是振荡频率ω0受控制电压U F (t )控制的振荡器,即是一种电压——频率变换器。VCO 的特性可以用瞬时频率ω0(t )与控制电压U F (t )之间的关系曲线来表示。未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO 的振荡频率,称为自由振荡频率ωom ,或中心频率,在VCO 线性控制范围内,其瞬时角频率可表示为: ωo (t )= ωom + K 0U F (t ) 式中,K 0——VCO 控制特性曲线的斜率,常称为VCO 的控制灵敏度,或称压控灵敏度。 三. 环路滤波器 这里仅讨论无源比例积分滤波器如图5。 其传递函数为: 1 )(1 )()()(212+++== τττs s s U s U s K i O F 式中:τ1 =R1C τ2 = R2 C 图5 四. 锁相环的相位模型及传输函数 图6 图6为锁相环的相位模型。要注意一点,锁相环是一个相位反馈系统,在环路中流通的是相位,而不是电压。因此研究锁相环的相位模型就可得环路的完整性能。 由图6可知: R1 0640 V Kd KF(s)Ko/s i o e A -+

图2:加入锁相环后的图形 图1:未加入锁相环时的图形 锁相环最基本的结构如图6.1所示。它由三个基本的部件组成:鉴相器(PD)、环路滤波器(LPF 振荡器(VCO)。 鉴相器是个相位比较装置。它把输入 信号S (t)和压控振荡器的输出信号 i Array (t)的相位进行比较,产生对应于两 S o 个信号相位差的误差电压S (t)。 e 环路滤波器的作用是滤除误差电压 (t)中的高频成分和噪声,以保证环 S e 路所要求的性能,增加系统的稳定性。

压控振荡器受控制电压S d (t)的 控制,使压控振荡器的频率向输入信 号的频率靠拢,直至消除频差而锁定。 锁相环是个相位误差控制系统。它比较输入信号和压控振荡器输出信号之间的相位差,从而产生电压来调整压控振荡器的频率,以达到与输入信号同频。在环路开始工作时,如果输入信号频率荡器频率不同,则由于两信号之间存在固有的频率差,它们之间的相位差势必一直在变化,结果出的误差电压就在一定范围内变化。在这种误差电压的控制下,压控振荡器的频率也在变化。若器的频率能够变化到与输入信号频率相等,在满足稳定性条件下就在这个频率上稳定下来。达到输入信号和压控振荡器输出信号之间的频差为零,相差不再随时间变化,误差电压为一固定值,就进入“锁定”状态。这就是锁相环工作的大致过程。 以上的分析是对频率和相位不变的输入信号而言的。如果输入信号的频率和相位在不断地变可能通过环路的作用,使压控的频率和相位不断地跟踪输入频率的变化。 锁相环具有良好的跟踪性能。若输入FM 信号时,让环路通带足够宽,使信号的调制频谱落在带这时压控振荡器的频率跟踪输入调制的变化。 对于锁相环的详细分析可参阅有关锁相技术的书籍。在此仅说明锁相环鉴频原理。可以简单控振荡器频率与输入信号频率之间的跟踪误差可以忽略。因此任何瞬时,压控振荡器的频率ωv (波的瞬时频率ωFM (t)相等。 FM 波的瞬时角频率可表示为 假设VCO 具有线性控制特性,其斜率K v (压控灵敏度)为(弧度/秒·伏),而VCO 在S d (t)=0频率为ωo ’,则当有控制电压时,VCO 的瞬时角频率为 令上两式相等,即ωv (t)≈ωFM (t),可得

锁相环的组成和工作原理#1 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡 器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1 所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入 信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电 路如图8-4-2所示。 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压 分别为: (8-4-1) (8-4-2) 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为: (8-4-3) 式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为: 即(8-4-4) 则,瞬时相位差θd为 (8-4-5)

锁相环的组成和工作原理 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。 鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: (8-4-1) (8-4-2) 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压u D为:

用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C(t)。即u C(t)为: (8-4-3) 式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为: 即(8-4-4) 则,瞬时相位差θd为 对两边求微分,可得频差的关系式为 (8-4-6) 上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,u c(t)随时间而变。 因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压u c(t)的变化而变化。该特性的表达式为 上式说明当u c(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。 8.4.2锁相环的应用 1.锁相环在调制和解调中的应用 (1)调制和解调的概念

锁相环CD4046 原理及应用 锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示。 图1 压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Ud大小决定。施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压UΨ正比于Ui和Uo两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Ud。这个平均值电压Ud朝着减小CO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。 当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。图2是CD4046的引脚排列,采用16 脚双列直插式,各引脚功能如下: 图2?1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。 ?2脚相位比较器Ⅰ的输出端。 ?3脚比较信号输入端。 ?4脚压控振荡器输出端。 ?5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。 ?6、7脚外接振荡电容。 ?8、16脚电源的负端和正端。 ?9脚压控振荡器的控制端。 ?10脚解调输出端,用于FM解调。 ?11、12脚外接振荡电阻。

全数字锁相环原理及应用 摘要:首先介绍全数字锁相环的结构,及各个模块的作用,接着讲述全数字锁相环的工作原理,然后介绍在全数字锁相环在调频和解调电路、频率合成器中的应用。 关键字:全数字锁相环数字环路鉴相器数字环路滤波器数字压控振荡器 1.前言 锁相环(PLL,Phase Locked Loop)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(ADPLL,All Digital Phase Locked Loop)与传统的模拟电路实现的PLL相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。随着通讯技术、集成电路技术的飞速发展和系统芯片的深入研究,全数字锁相环将会在其中得到更为广泛的应用。 2.全数字锁相环结构及原理 图1 数字锁相环路的基本结构 (1)数字环路鉴相器(DPD) 数字鉴相器也称采样鉴相器,是用来比较输入信号与压控振荡器输出信号的相位,它的输出电压是对应于这两个信号相位差的函数。它是锁相环路中的关键部件,数字鉴相器的形式可分为:过零采样鉴相器、触发器型数字鉴相器、超前—滞后型数字鉴相器和奈奎斯特速率取样鉴相器。 (2)数字环路滤波器(DLF) 数字环路滤波器在环路中对输入噪声起抑止作用,并且对环路的校正速度起调节作用。数字滤波器是一种专门的技术,有各种各样的结构形式和设计方法。引入数字环路滤波器和模拟锁相环路引入环路滤波器的目的一样,是作为校正网

络引入环路的。因此,合理的设计数字环路滤波器和选取合适的数字滤波器结构就能使DPLL满足预定的系统性能要求。 (3)数字压控振荡器(DCO) 数控振荡器,又称为数字钟。它在数字环路中所处的地位相当于模拟锁相环中的压控振荡器(VCO)。但是,它的输出是一个脉冲序列,而该输出脉冲序列的周期受数字环路滤波器送来的校正信号的控制。其控制特点是:前一采样时刻得到的校正信号将改变下一个采样时刻的脉冲时间位置。 全数字锁相环工作原理 全数字锁相环的基本工作过程如下: (1) 设输入信号 u i(t) 和本振信号(数字压控振荡器输出信号)u o(t) 分别是正弦和余弦信号,他们在数字鉴相器内进行比较,数字鉴相器的输出是一个与两者间的相位差成比例的电压u d(t)。 (2) 数字环路滤波器除数字鉴相器输出中的高频分量,然后把输出电压u c(t) 加到数字压控振荡器的输出端,数字压控振荡器的本振信号频率随着输入电压的变化而变化。如果两者频率不一致,则数字鉴相器的输出将产生低频变化分量,并通过低通滤波器使DCO的频率发生变化。只要环路设计恰当,则这种变化将使本振信号u o(t) 的频率与数字鉴相器输入信号u i(t) 的频率一致。 (3)最后,如果本振信号的频率和输入信号的频率完全一致,两者的相位差将保持某一个恒定值,则数字鉴相器的输出将是一个恒定直流电压(忽略高频分量),数字环路滤波器的输出也是一个直流电压,DCO的频率也将停止变化,这时,环路处于“锁定状态”。 3.全数字锁相环的特点及应用 全数字化锁相环的共同特点 (1)电路完全数字化,使用逻辑门电路和触发器电路。系统中只有“导通”和“截止”两种工作状态,受外界和电源的干扰的可能性大大减小,电路容易集成,易于制成全集成化的单片全数字锁相环路。因而系统的可靠性大大提高。 (2)全数字锁相环路还缓和甚至消除了模拟锁相环路中电压控制振荡器(VCO)的非线性以及环路中使用运算放大器和晶体管后而出现的饱和及运算放大器和鉴相器的零漂等对环路性能的影响。 (3)数字锁相环路的环路部件甚至整个环路都可以直接用微处理机来模拟而实现。 (4)全数字锁相环路中,因模拟量转变为数字量所引入的量化误差和离散控制造成的误差,只要系统设计得当,均可以被忽略。 全数字化锁相环的在实际工程中的应用 目前,全数字锁相环路(A DPLL)已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。A DPLL具有精度高、不受温度和电压影响、环路带宽和中心编程频率可调、易于构建高阶锁相环等优点。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。 全数字锁相环在调频和解调电路中的应用

锁相环工作原理 -标准化文件发布号:(9556-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII

锁相环工作原理 锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压 的相位被锁住,这就是锁相环名称的由来。 在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。因此,所有板卡上各自的本地 80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。锁相环路是一个相位反馈自动控制系统。它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。 锁相环的工作原理: 1. 压控振荡器的输出经过采集并分频; 2. 和基准信号同时输入鉴相器; 3. 鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压; 4. 控制VCO,使它的频率改变; 5. 这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。 锁相环可用来实现输出和输入两个信号之间的相位同步。当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。这时,压控振荡器按其固有频率fv进行自由振荡。当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一 个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。这时我们就称环路已被锁定。 环路的锁定状态是对输入信号的频率和相位不变而言的,若环路输入的是频率和相位不断变化的信号,而且环路能使压控振荡器的频率和相位不断地跟踪输入信号的频率和相位变化,则这时环路所处的状态称为跟踪状态。 锁相环路在锁定后,不仅能使输出信号频率与输入信号频率严格同步,而且还具有频率跟踪特性,所以它在电子技术的各个领域中都有着广泛的应用 .锁相环的基本组成: 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相 环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信 号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值, 即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。锁相环通常由鉴相器

一、MC145152(鉴相器) MC145152-2 芯片是摩托罗拉公司生产的锁相环频率合成器专用芯片。它是 MC145152-1 芯片的改进型。主要具有下列主要特征: (1)它与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出 MC。当 MC 为低电平时,双模分频器用(P+1)去除;当 MC 为高电平时,双模分频器用模数 P 去除。 (2)它有 A 计数器和 N 计数器两个计数器。它们与双模(P/(P+1))分频器提供了总分频值(NP+A)。其中,A、N 计数器可预置。N 的取值范围为 3~1023,A 的取值范围为 0~63。A 计数器计数期间,MC 为低电平;N 计数器计数(N-A)期间,MC 为高电平。 (3)它有一个参考振荡器,可外接晶体振荡器。 (4)它有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1024,1160,2048。设置方法通过改变RA0、RA1、RA2的不同电平,接下来会讲到。 (5)它有两路鉴相信号输出,其中,ФR、ФV 用来输出鉴相误差信号,LD 用来输出相位锁定信号。 MC145152-2 的供电电压为 3.0 V~9.0 V,采用 28 脚双列封装形式。MC145152-2的原理框图如图 1 所示 MC145152-2 的工作原理:参考振荡器信号经 R 分频器分频后形成 fR 信号。压控振荡器信号经双模P/(P +1)分频器分频,再经 A、N 计数器分频器后形成 fV 信号,fV=fVCO/(NP+A)。fR 信号和 fV 信号在鉴相器中鉴相,输出的误差信号(φR、φV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。当整个环路锁定后,fV=fR 且同相,fVCO=(NP+A)fV=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。原理框图如右图: 管脚描述: Pin 1频率输入 (fin) 输入到上升沿触发÷N和÷A计数器。fin通常是来自一个双模预分频器并且通过交流耦合输入。对于较大振幅的信号(标准CMOS逻辑电平)也可以直接直流耦合。其输入信号应小于30MHz,所以大于30MHz的输出一般都要用双模预分频芯片。 Pin4、5、6 参考分频地址码输入 (RA0, RA1, RA2)为参考地址码输入端,用于选择参考分频器的分频比,通过12x8ROM参考译码器和12bit÷R计数器进行编程。分频比有8种选择,其参考地址码与分频比的关系,见下表所列: