目录

一.常用逻辑电平标准 (2)

1.1 COMS电平 (3)

1.2 LVCOMS电平 (3)

2.1 TTL电平 (4)

2.2 LVTTL电平 (4)

3.1 LVDS电平 (5)

4.1 PECL(VCC=5V)/LVPECL(VCC=3.3V)电平 (5)

5.1 CML电平 (6)

6.1 VML电平 (6)

7.1 HSTL电平 (6)

7.2 SSTL电平 (7)

二.常用接口电平标准 (7)

1. RS232、RS485、RS422 (7)

2 DDR1 ,DDR2,DDR3 (8)

3 PCIE2. 0、PCIE3.0 (8)

4 USB2.0, USB3.0 (10)

5 SATA2.0, SATA3.0 (10)

6 GTX高速接口 (11)

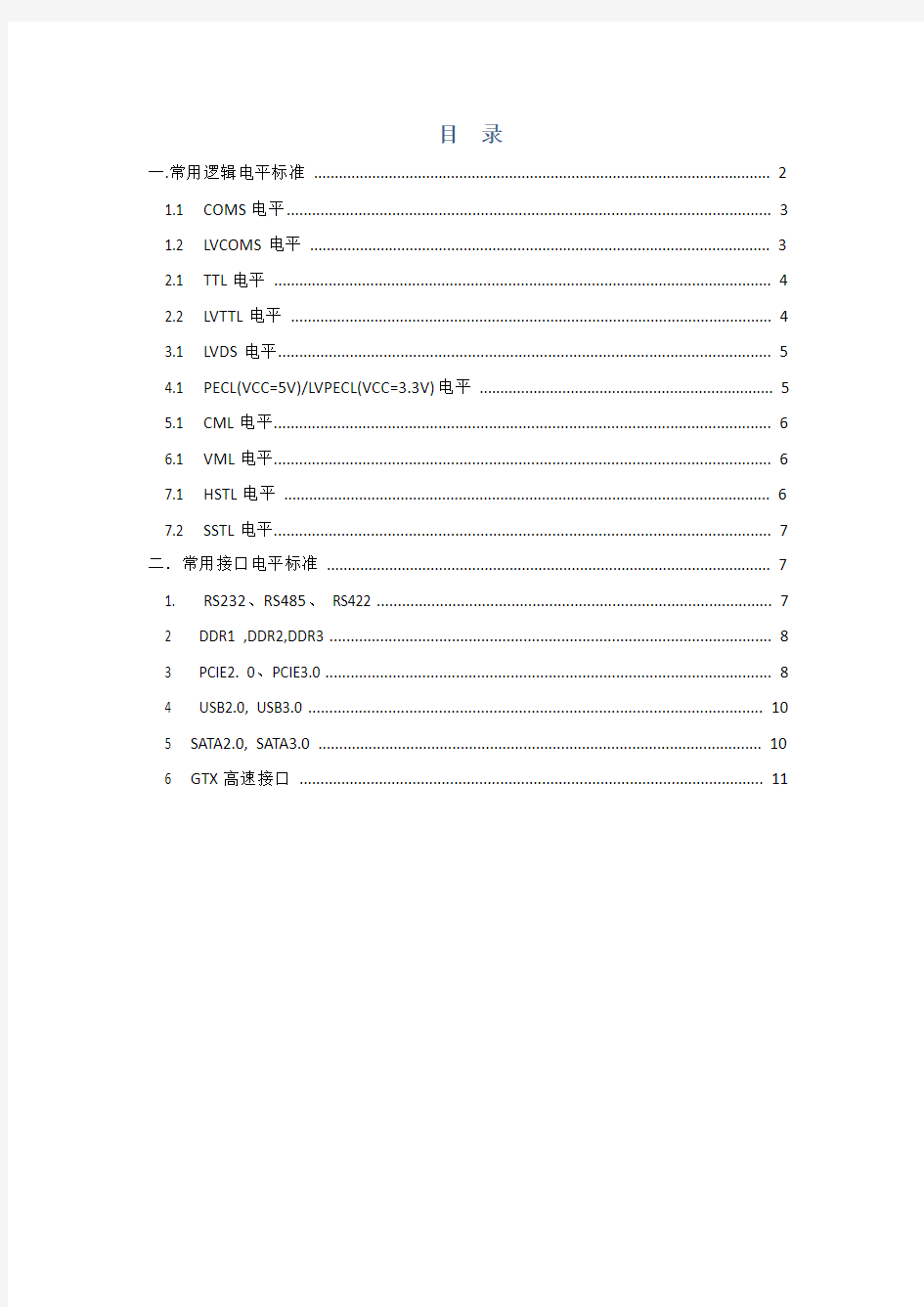

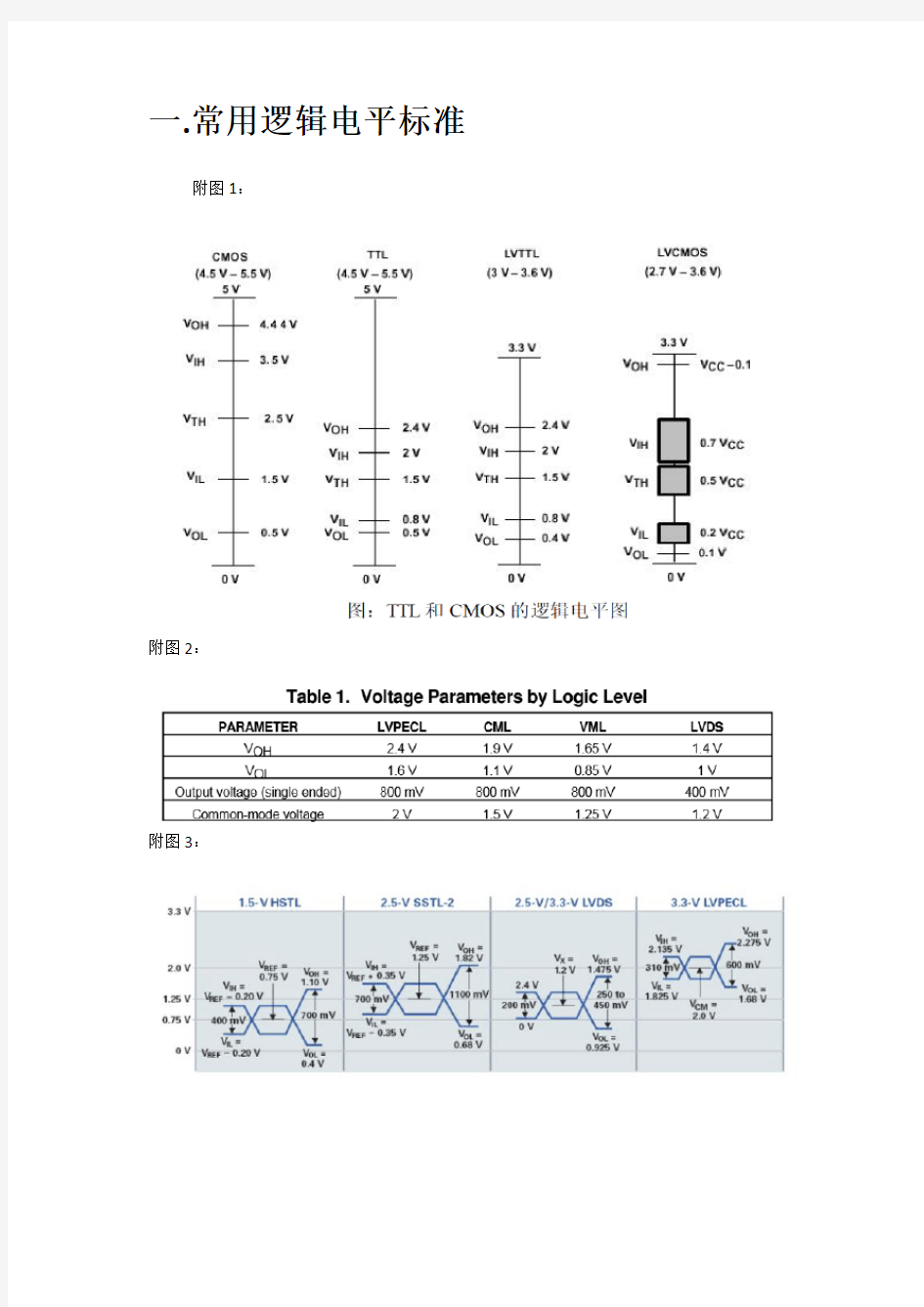

一.常用逻辑电平标准

附图1:

附图2:

附图3:

附图4:

1.1 COMS电平

1.2 LVCOMS电平

2.2 LVTTL电平

最高速率:3.125Gbps

耦合方式:

4.1 PECL(VCC=5V)/LVPECL(VCC=3.3V)电平

最高速率:LVPECL为10+Gbps

耦合方式:

最高速率:10+Gbps

耦合方式:VCC相同时CML与CML之间采用直流耦合,VCC不同时CML与CML 之间采用交流耦合

6.1 VML电平

VML电平与LVDS电平兼容,TLK2711输出是VML电平。

7.1 HSTL电平

HSTL 最主要的应用是可以用于高速存储器读可。

该标准专门针对高速内存(特别是SDRAM)接口,它可获得高达200MHz的工作频率,SSTL 主要用于DDR 存储器。和HSTL 基本相同。V¬¬CCIO=2.5V,输入为输入为

比较器结构,比较器一端接参考电平1.25V,另一端接输入信号。对参考电平要求比较高(1% 精度),HSTL 和SSTL 大多用在300M 以下.

二.常用接口电平标准

1. RS232、RS485、RS422

2 DDR1 ,DDR2,DDR3

备注

DDR4:速率1.6~3.2Gbps;I/O接口SSTL_12;VDD 1.2V;

3 PCIE2. 0、PCIE3.0

参考时钟直流规范

辅助信号直流规范

4 USB2.0, USB3.0 USB引脚定义

5 SATA2.0, SATA3.0

6 GTX高速接口

常用电平及接口电平

目录 一.常用逻辑电平标准 (3) 1.1 COMS电平 (4) 1.2 LVCOMS电平 (5) 2.1 TTL电平 (5) 2.2 LVTTL电平 (5) 3.1 LVDS电平 (6) 4.1 PECL(VCC=5V)/LVPECL(VCC=3.3V)电平 (7) 5.1 CML电平 (7) 6.1 VML电平 (7) 7.1 HSTL电平 (8) 7.2 SSTL电平 (8) 二.常用接口电平标准 (9) 1. RS232、RS485、 RS422 (9) 2 DDR1 ,DDR2,DDR3 (10) 3 PCIE2. 0、PCIE3.0 (11) 4 USB2.0, USB3.0 (13) 5 SATA2.0, SATA3.0 (14) 6 GTX高速接口 (14)

一.常用逻辑电平标准 附图1: 附图2:

附图3: 附图4: 1.1 COMS电平 电平参数条件最大值典型值最小值单位备注电源电压(VCC) 5.5 5 4.5 V 输入高压(VIH) 3.5 V 输入低压(VIL) 1.5 V 输出高压(VOH) 4.44 V 输出低压(VOL)0.5 V 共模电压(VT) 2.5 V

传输延迟时间(25-50ns) 最高速率 耦合方式 1.2 LVCOMS电平 LVCOMS电平参数条件最大值典型值最小值单位备注电源电压(VCC) 3.6 3.3 2.7 V 输入高压(VIH)0.7VCC V 输入低压(VIL) 0.2VCC V 输出高压(VOH) VCC-0.1 V 输出低压(VOL)0.1 V 共模电压(VT)0.5VCC V 最高速率 耦合方式 2.1 TTL电平 电平参数条件最大值典型值最小值单位备注电源电压(VCC) 5.5 5 4.5 V 输入高压(VIH) 2 V 输入低压(VIL) 0.8 V 输出高压(VOH) 2.4 V 输出低压(VOL)0.5 V 共模电压(VT) 1.5 V 传输延迟时间(5-10ns), 最高速率 耦合方式 2.2 LVTTL电平 电平参数条件最大值典型值最小值单位备注

玩转投影机接口连线图解 很多初级用户在看投影机文章或将投影机与其它设备进行连接时,面对众多的接口总是感到茫然。其实只要弄明白它们的用途和连/转接方法,在使用时您会觉得其也并非有登天之难。 投影机接口虽没有高档功放上那么多 但也不少 家用投影机上的常用接口 拉近点就看清楚了 一、常规视频输入端子 做为视频播放设备,投影机上输入端子(端子=接口)的数量远多于输出端子,视频端子的数量也远多于音频端子。 ●标准视频输入(RCA)

RCA是莲花插座的英文简称,RCA输入输出是最常见的音视频输入和输出接口,也被称AV接口(复合视频接口),通常都是成对的,把视频和音频信号“分开发送”,避免了因为音/视频混合干扰而导致的图像质量下降。但由于AV接口传输的仍是一种亮度/色度(Y/C)混合的视频信号,仍需显示设备对其进行亮/色分离和色度解码才能成像,这种先混合再分离的过程必然会造成色彩信号的损失,所以其目前主要被用在入门级音视频设备和应用上。 音频转RCA线 RCA转接延长头

插入示意图 白色的是音频接口和黄色的视频接口,使用时只需要将带莲花头的标准AV线缆与其它输出设备(如放像机、影碟机)上的相应接口连接起来即可。 不要小瞧了RCA,其也有做工不错的高档货 ●S端子

标准S端子 标准S端子连接线

音频复合视频S端子色差常规连接示意图 S端子(S-Video)是应用最普遍的视频接口之一,是一种视频信号专用输出接口。常见的S端子是一个5芯接口,其中两路传输视频亮度信号,两路传输色度信号,一路为公共屏蔽地线,由于省去了图像信号Y与色度信号C的综合、编码、合成以及电视机机内的输入切换、矩阵解码等步骤,可有效防止亮度、色度信号复合输出的相互串扰,提高图像的清晰度。 一般DVD或VCD、TV、PC都具备S端子输出功能,投影机可通过专用的S端子线与这些设备的相应端子连接进行视频输入。 显卡上配置的9针增强S端子,可转接色差

一些电平标准 下面总结一下各电平标准,和新手以及有需要的人共享一下^_^. 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。 TTL:Transistor-Transistor Logic 三极管结构。 Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。 因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。 LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。 3.3V LVTTL: Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。 2.5V LVTTL: Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。 更低的LVTTL不常用就先不讲了。多用在处理器等高速芯片,使用时查看芯片手册就OK了。 TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻; TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。 CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。 Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。 相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。 3.3V LVCMOS: Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。 CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。 ECL:Emitter Coupled Logic 发射极耦合逻辑电路(差分结构) Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。 速度快,驱动能力强,噪声小,很容易达到几百M的应用。但是功耗大,需要负电源。为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL。 PECL:Pseudo/Positive ECL Vcc=5V;VOH=4.12V;VOL=3.28V;VIH=3.78V;VIL=3.64V LVPELC:Low Voltage PECL

https://www.doczj.com/doc/0c8394028.html, USB接法 一、概述 因为每个USB接口能够向外设提供+5V500MA的电流,当我们在连接板载USB接口时,一定要严格按照主板的使用说明书进行安装。绝对不能出错,否则将烧毁主板或者外设。相信有不少朋友在连接前置USB插线时也发生过类似的“冒烟事件”,因此到现在我都怕一不小心把自己的U盘在别人的机器上被烧了,所以在使用U盘拷文件时,一直都使用键盘口附近后置的USB接口,因为主板集成的接口安全,不会有电源接反的可能。 今天客户打电话投诉说自己的电脑等了半个多月才修好,可把自己的移动硬盘 往上面一接,屏幕上闪了一下发现新硬件,然后移动硬盘就没有动静了,再把移动硬盘接到办公室的电脑里也不能用了。当时我一听头就嗡的一下,马上派人上门检查,结果当用我自己做的测试线接到后置的USB接口,指示灯亮,但接到前置就根本不亮。拆机一看,果真接反了。后面的事就不用说了...。 由此前置USB数据线接反的严重性大家应该都知道了,但是如何防止类似的情况发生呢,这就需要我们能够准确判别前置USB线的排列顺序,可以正确连接前置USB接线。新机器倒还可以,有使用手册,翻一翻就可以了。但是旧主板呢,拿去修理的机器呢?没有主板手册怎么办?到网上下载主板的使用手册,太浪费时间了,更何况也不一定能够找到该型号主板的接线图。不过,如果我们晓得USB接口的基本布线结构,那问题不是就迎刃而解了吗。 二、USB接口实物图 主机端: 接线图: VCC Data- Data+ GND 实物图: 设备端: 接线图: VCC GND Data-

三、市面上常见的USB接口的布线结构 这两年市面上销售的主板,板载的前置USB接口,使用的都是标准的九针USB接口,第九针是空的,比较容易判断。但是多数品牌电脑使用的都是厂家定制的主板,我们维修的时候根本没有使用说明书;还有像以前的815主板,440BX,440VX主板等,前置USB的接法非常混乱,没有一个统一的标准。当我们维修此类机器时,如何判断其接法呢? 现在,我把市面上的比较常见的主板前置USB接法进行汇总,供大家参考。(说明:■代表有插针,□代表有针位但无插针。) 1、六针双排 这种接口不常用,这种类型的USB插针排列方式见于 精英 P6STP-FL(REV:1.1)主板,用于海尔小超人766主机。其电源正和电源负为两个前置USB接口共用,因此前置的两个USB接口需要6根线与主板连接,布线如下表所示。 ■DATA1+ ■DATA1- ■VCC ■DATA2- ■DATA2+ ■GND 2、八针双排 这种接口最常见,实际上占用了十针的位置,只不过有两个针的位置是空着的,如精英的P4VXMS(REV:1.0)主板等。该主板还提供了标准的九针接法,这种作是为了方便DIY在组装电脑时连接容易。 ■VCC ■DATA- ■DATA+ □NUL ■GND ■GND □NUL ■DATA+ ■DATA- ■VCC 微星 MS-5156

几种常用逻辑电平电路的特点及应用 2007-08-13 来源: 作者: LVDS(Low Voltage Differential Signal)低电压差分信号、ECL(EmitterCoupled Logic)即射极耦合逻辑、CML电平等各种逻辑电平的特点以及接口应用。 在通用的电子器件设备中,TTL和CMOS电路的应用非常广泛。但是面对现在系统日益复杂,传输的数据量越来越大,实时性要求越来越高,传输距离越来越长的发展趋势,掌握高速数据传输的逻辑电平知识和设计能力就显得更加迫切了。 1 几种常用高速逻辑电平 1.1LVDS电平 LVDS(Low V oltage Differential Signal)即低电压差分信号,LVDS接口又称RS644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。 LVDS的典型工作原理如图1所示。最基本的LVDS器件就是LVDS驱动器和接收器。LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。LVDS 接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100 Ω的匹配电阻,并在接收器的输入端产生大约350 mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。 图1LVDS驱动器与接收器互连示意 LVDS技术在两个标准中被定义:ANSI/TIA/EIA644 (1995年11月通过)和IEEE P1596.3 (1996年3月通过)。这两个标准中都着重定义了LVDS的电特性,包括:①低摆幅(约为350 mV)。低电流驱动模式意味着可实现高速传输。ANSI/TIA/EIA644建议了655 Mb/s的最大速率和1.923 Gb/s的无失真通道上的理论极限速率。 ②低压摆幅。恒流源电流驱动,把输出电流限制到约为3.5 mA左右,使跳变期间的尖峰干扰最小,因而产生的功耗非常小。这允许集成电路密度的进一步提高,即提高了PCB板的效能,减少了成本。 ③具有相对较慢的边缘速率(dV/dt约为0.300 V/0.3 ns,即为1 V/ns),同时采用差

TTL电平和CMOS电平总结 1,TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。2,CMOS电平: 1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。 3,电平转换电路: 因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需要电平的转换 4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱动门电路。 5,TTL和COMS电路比较: 1)TTL电路是电流控制器件,而coms电路是电压控制器件。 2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。 3)COMS电路的锁定效应: COMS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。 防御措施: 1)在输入端和输出端加钳位电路,使输入和输出不超过规定电压。 2)芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。 3)在VDD和外电源之间加限流电阻,即使有大的电流也不让它进去。 4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启COMS电路得电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭COMS 电路的电源。 6,COMS电路的使用注意事项 1)COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。 2)输入端接低内阻的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。 3)当接长信号传输线时,在COMS电路端接匹配电阻。 4)当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。 5)COMS的输入电流超过1mA,就有可能烧坏COMS。 7,TTL门电路中输入端负载特性(输入端带电阻特殊情况的处理): 1)悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。 2)在门电路输入端串联10K电阻后再输入低电平,输入端出呈现的是高电平而不是低电平。因为由TTL门电路的输入端负载特性可知,只有在输入端接的串联电阻小于910欧时,它输入来的低电平信号才能被门电路识别出来,串联电阻再大的话输入端就一直呈现高电平。这个一定要注意。COMS门电路就不用考虑这些了。 8,TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出

3.5mm 插头 最常见的立体声耳机分三层,标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB接口 USB是一种常用的pc接口,他只有4根线,两根电源两根信号,故信号是串行传输的,usb接口也称为串行口, usb2.0的速度可以达到480Mbps。可以满足各种工业和民用需要.USB接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/-0.2V 也就是4.8-5.2V 。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,

否则会烧掉usb设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data- 1 USB接口定义图 USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连

接头)。 USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等, 2 所以如今有许多打印机、扫描仪、数字摄像头、数码相机、MP3播放器、MODEM等都开始使用USB做为接口模式,USB接口定义也很简单: 1 +5V 2 DATA-数据- 3 DATA+数据+ 4 GND 地 串口 主板一般都集成两个串口,可Windows却最多可提供8个串口资源供硬件设置使用(编号COM1到COM8),虽然其I/O地址不相同,但是总共只占据两个IRQ(1、3、5、7共享IRQ4,2、4、6、8共享IRQ3),平常我们常用的是COM1~COM4这四个端口。我们经常在使用中遇到这个问题——如果在COM1上安装了串口鼠标或其他外设,就不能在COM3上安装如Modem之类的其它硬件,这就是因为IRQ设置冲突而无法工作。这时玩家们可以将另外的外设安装在COM2或4。 标准的串口能够达到最高115Kbps的数据传输速度,而一些增强型串口如ESP(Enhanced Serial Port,增强型串口) 、Super

RS232、RS485、RS422电平,及常见逻辑电平标准 RS232电平或者说串口电平,有的甚至说计算机电平,所有的这些说法,指得都是计算机9针串口(RS232)的电平,采用负逻辑, -15v ~ -3v 代表1 +3v ~ +15v 代表0 RS485电平和RS422电平由于两者均采用差分传输(平衡传输)的方式,所以他们的电平方式,一般有两个引脚 A,B 发送端 AB间的电压差 +2 ~+6v 1 -2 ~-6v 0 接收端 AB间的电压差 大于+200mv 1 小于-200mv 0 定义逻辑1为B>A的状态 定义逻辑0为A>B的状态 AB之间的电压差不小于200mv 一对一的接头的情况下 RS232 可做到双向传输,全双工通讯最高传输速率 20kbps 422 只能做到单向传输,半双工通讯,最高传输速率10Mbps 485 双向传输,半双工通讯, 最高传输速率10Mbps

常见逻辑电平标准 下面总结一下各电平标准。和新手以及有需要的人共享一下^_^. 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。 TTL:Transistor-Transistor Logic 三极管结构。 Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。 因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。 LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。 3.3V LVTTL: Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。 2.5V LVTTL: Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。 更低的LVTTL不常用就先不讲了。多用在处理器等高速芯片,使用时查看芯片手册就OK了。 TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。 CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。 相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。 3.3V LVCMOS: Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。 CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

要了解逻辑电平的内容,首先要知道以下几个概念的含义: 1:输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。 2:输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。 3:输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。 4:输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。 5:阀值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平> Vih,输入低电平

Q/DKBA 深圳市华为技术有限公司技术规范 错误!未定义书签。Q/DKBA0.200.035-2000 逻辑电平接口设计规范

2000-06-20发布 2000-06-20实施深圳市华为技术有限公司发布

本规范起草单位:各业务部、研究技术管理处硬件工程室。 本规范主要起草人如下:赵光耀、钱民、蔡常天、容庆安、朱志明,方光祥、王云飞。 在规范的起草过程中,李东原、陈卫中、梅泽良、邢小昱、李德、梁军、何其慧、甘云慧等提出了很好的建议。在此,表示感谢! 本规范批准人:周代琪 本规范解释权属于华为技术有限公司研究技术管理处硬件工程室。 本规范修改记录:

目录 1、目的 5 2、范围 5 3、名词定义 5 4、引用标准和参考资料 6 5、TTL器件和CMOS器件的逻辑电平8 5.1:逻辑电平的一些概念8 5.2:常用的逻辑电平9 5.3:TTL和CMOS器件的原理和输入输出特 性9 5.4:TTL和CMOS的逻辑电平关系10 6、TTL和CMOS逻辑器件12 6.1:TTL和CMOS器件的功能分类12 6.2:TTL和MOS逻辑器件的工艺分类特点13 6.3:TTL和CMOS逻辑器件的电平分类特点13 6.4:包含特殊功能的逻辑器件14 6.5:TTL和CMOS逻辑器件的选择15 6.6:逻辑器件的使用指南15 7、TTL、CMOS器件的互连17 7.1:器件的互连总则17 7.2:5V TTL门作驱动源20 7.3:3.3V TTL/CMOS门作驱动源20 7.4:5V CMOS门作驱动源20 7.5:2.5V CMOS逻辑电平的互连20 8、EPLD和FPGA器件的逻辑电平21 8.1:概述21 8.2:各类可编程器件接口电平要求21 8.3:各类可编程器件接口电平要求21 8.3.1:EPLD/CPLD的接口电平21 8.3.2:FPGA接口电平25 9、ECL器件的原理和特点35 9.1:ECL器件的原理35 9.2:ECL电路的特性36 9.3:PECL/LVPECL器件的原理和特点37 9.4:ECL器件的互连38 9.4.1:ECL器件和TTL器件的互连38 9.4.2:ECL器件和其他器件的互连39 9.5:ECL器件的匹配方式39 9.6:ECL器件的使用举例41 9.6.1:SYS100E111的设计41 9.6.2:SY100E57的设计42 9.1:ECL电路的器件选择43 9.2:ECL器件的使用原则43

各种逻辑电平标准 在通用的电子器件设备中,TTL和CMOS电路的应用非常广泛。但是面对现在系统日益复杂,传输的数据量越来越大,实时性要求越来越高,传输距离越来越长的发展趋势,掌握高速数据传输的逻辑电平知识和设计能力就显得更加迫切了。 5V TTL和5V CMOS逻辑电平是通用的逻辑电平。·3.3V及以下的逻辑电平被称为低电压逻辑电平,常用的为LVTTL电平。·低电压的逻辑电平还有2.5V和1.8V两种。·ECL/PECL和LVDS是差分输入输出。·RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入 常用电平标准 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的LVDS、GTL、PGTL、CML、HSTL、SSTL 等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。 TTL:Transistor-Transistor Logic 三极管结构。 Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。 因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。 LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。 3.3V LVTTL: Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。 2.5V LVTTL: Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。 更低的LVTTL不常用。多用在处理器等高速芯片,使用时查看芯片手册就OK了。 TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻; TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。 CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。 Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。 相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

1.DVI接口基础知识 DVI全称为Digital Visual Interface,是1999年由Silicon Image、Intel(英特尔)、Compaq(康柏)、IBM、HP(惠普)、NEC、Fujitsu(富士通)等公司共同组成的数字显示工作组 DDWG(Digital Display Working Group)推出的接口标准,其外观是一个24针的接插件。显示设备采用DVI接口具有主要有以下两大优点: 一、速度快:DVI传输的是数字信号,数字图像信息不需经过任何转换,就会直接被传送到显示设备上,因此减少了数字→模拟→数字繁琐的转换过程,大大节省了时间,因此它的速度更快,有效消除拖影现象,而且使用DVI进行数据传输,信号没有衰减,色彩更纯净,更逼真。 二、画面清晰:计算机内部传输的是二进制的数字信号,使用VGA接口连接液晶显示器的话就需要先把信号通过显卡中的D/A(数字/模拟)转换器转变为R、G、B三原色信号和行、场同步信号,这些信号通过模拟信号线传输到液晶内部还需要相应的A/D(模拟/数字)转换器将模拟信号再一次转变成数字信号才 能在液晶上显示出图像来。在上述的D/A、A/D转换和信号传输过程中不可避免会出现信号的损失和受到干扰,导致图像出现失真甚至显示错误,而DVI接口无需进行这些转换,避免了信号的损失,使图像的清晰度和细节表现力都得到了大大提高。 区分不同DVI标准 DVI接口有多种规格,分为DVI-A、DVI-D和DVI-I,它是以Silicon Image 公司的PanalLink接口技术为基础,基于TMDS(Transition Minimized Differential Signaling,最小化传输差分信号)电子协议作为基本电气连接。TMDS是一种微分信号机制,可以将象素数据编码,并通过串行连接传递。显卡产生的数字信号由发送器按照TMDS协议编码后通过TMDS通道发送给接收器,经过*送给数字显示设备。一个DVI显示系统包括一个传送器和一个接收器。传送器是信号的来源,可以内建在显卡芯片中,也可以以附加芯片的形式出现在显卡PCB上;而接收器则是显示器上的一块电路,它可以接受数字信号,将其*并传递到数字显示电路中,通过这两者,显卡发出的信号成为显示器上的图象。 DVI-D接口

常用逻辑电平简介(转载) 逻辑电平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。 图1-1:常用逻辑系列器件 TTL:Transistor-Transistor Logic CMOS:Complementary Metal Oxide Semicondutor LVTTL:Low Voltage TTL LVCMOS:Low Voltage CMOS ECL:Emitter Coupled Logic, PECL:Pseudo/Positive Emitter Coupled Logic LVDS:Low Voltage Differential Signaling GTL:Gunning Transceiver Logic BTL:Backplane Transceiver Logic ETL:enhanced transceiver logic GTLP:Gunning Transceiver Logic Plus TI的逻辑器件系列有:74、74HC、74AC、74LVC、74LVT等 S - Schottky Logic LS - Low-Power Schottky Logic CD4000 - CMOS Logic 4000 AS - Advanced Schottky Logic 74F - Fast Logic ALS - Advanced Low-Power Schottky Logic HC/HCT - High-Speed CMOS Logic BCT - BiCMOS Technology AC/ACT - Advanced CMOS Logic FCT - Fast CMOS Technology ABT - Advanced BiCMOS Technology LVT - Low-Voltage BiCMOS Technology LVC - Low Voltage CMOS Technology LV - Low-Voltage CBT - Crossbar Technology ALVC - Advanced Low-Voltage CMOS Technology AHC/AHCT - Advanced High-Speed CMOS CBTLV - Low-Voltage Crossbar Technology ALVT - Advanced Low-Voltage BiCMOS Technology AVC - Advanced Very-Low-Voltage CMOS Logic TTL器件和CMOS器件的逻辑电平 :逻辑电平的一些概念 要了解逻辑电平的内容,首先要知道以下几个概念的含义: 1:输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。 2:输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,

计算机常见外部接口图解 插头 USB接口 串口 VGA接口 网卡(LAN)接口 并口 电脑内数据接口 IEEE1394接口 eSATA接口 Micro-USB DVI HDMI

3.5mm插头 最常见的立体声耳机分三层,也有两层的,每一层都有对应的功能,要DIY的话一定要分层。标准分布为“左右地红白”(从端部到根部依次是左声道、右声道、地线,其中左声道常用红色线皮,右声道常用白色的)。 最常见的是银白色的和铜黄色的,银色的是铜镀银,铜黄色的就是铜。由于银的稳定性和电子工程性优于铜,所以铜镀上银后可以升级使用该插头设备的用户体验。 USB接口 USB是一种常用的pc接口,他只有4根线,两根电源两根信号,故信号是串行传输的,usb接口也称为串行口,的速度可以达到480Mbps。可以满足各种工业和民用需要.USB接口的输出电压和电流是: +5V 500mA 实际上有误差,最大不能超过+/ 也就是。usb接口的4根线一般是下面这样分配的,需要注意的是千万不要把正负极弄反了,否则会烧掉usb设备或者电脑的南桥芯片:黑线:gnd 红线:vcc 绿线:data+ 白线:data-

USB接口定义颜色 一般的排列方式是:红白绿黑从左到右 定义: 红色-USB电源:标有-VCC、Power、5V、5VSB字样 白色-USB数据线:(负)-DATA-、USBD-、PD-、USBDT- 绿色-USB数据线:(正)-DATA+、USBD+、PD+、USBDT+ 黑色-地线: GND、Ground USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接头)。 USB接口是一种越来越流行的接口方式了,因为USB接口的特点很突出:速度快、兼容性好、不占中断、可以串接、支持热插拨等等,所以如今有许多打印机、扫描仪、数字摄像头、数码相机、MP3播放器、MODEM等都开始使用USB做为接口模式,USB接口定义也很简单: 1 +5V 2 DATA-数据- 3 DATA+数据+ 4 GND 地

几种常用逻辑电平电路的特点及应用 发布时间:2005-12-25 来源:应用领域:邮电 ONT face=Verdana> 引言 在通用的电子器件设备中,TTL和CMOS电路的应用非常广泛。但是面对现在系统日益复杂,传输的数据量越来越大,实时性要求越来越高,传输距离越来越长的发展趋势,掌握高速数据传输的逻辑电平知识和设计能力就显得更加迫切了。 1 几种常用高速逻辑电平 1.1LVDS电平 LVDS(Low Voltage Differential Signal)即低电压差分信号,LVDS接口又称RS644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。 LVDS的典型工作原理如图1所示。最基本的LVDS器件就是LVDS驱动器和接收器。LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100 Ω的匹配电阻,并在接收器的输入端产生大约350 mV的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。 LVDS技术在两个标准中被定义:ANSI/TIA/EIA644 (1995年11月通过)和IEEE P1596.3 (1996年3月通过)。这两个标准中都着重定义了LVDS的电特性,包括: ①低摆幅(约为350 mV)。低电流驱动模式意味着可实现高速传输。 ANSI/TIA/EIA644建议了655 Mb/s的最大速率和1.923 Gb/s的无失真通道上的理论极限速率。 ②低压摆幅。恒流源电流驱动,把输出电流限制到约为3.5 mA左右,使跳变期间的尖峰干扰最小,因而产生的功耗非常小。这允许集成电路密度的进一步提高,即提高了PCB 板的效能,减少了成本。 ③具有相对较慢的边缘速率(dV/dt约为0.300 V/0.3 ns,即为1 V/ns),同时采用差分传输形式,使其信号噪声和EMI都大为减少,同时也具有较强的抗干扰能力。 所以,LVDS具有高速、超低功耗、低噪声和低成本的优良特性。 LVDS的应用模式可以有四种形式: ①单向点对点(point to point),这是典型的应用模式。 ②双向点对点(point to point),能通过一对双绞线实现双向的半双工通信。可以由标准的LVDS的驱动器和接收器构成;但更好的办法是采用总线LVDS驱动器,即BLVDS,这是为总线两端都接负载而设计的。 ③多分支形式(multidrop),即一个驱动器连接多个接收器。当有相同的数据要传给多个负载时,可以采用这种应用形式。④多点结构(multipoint)。此时多点总线支持多个驱动器,也可以采用BLVDS驱动器。它可以提供双向的半双工通信,但是在任一时刻,

常见逻辑电平标准 下面总结一下各电平标准。和新手以及有需要的人共享一下^_^. 现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度比较高的 LVDS、GTL、PGTL、CML、HSTL、SSTL等。下面简单介绍一下各自的供电电源、电平标准以及使用注意事项。 TTL:Transistor-Transistor Logic 三极管结构。 Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。 因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。 LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。 3.3V LVTTL: Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。 2.5V LVTTL: Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。 更低的LVTTL不常用就先不讲了。多用在处理器等高速芯片,使用时查看芯片手册就OK了。TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。 CMOS:Complementary Metal Oxide Semiconductor PMOS+NMOS。 Vcc:5V;VOH>=4.45V;VOL<=0.5V;VIH>=3.5V;VIL<=1.5V。 相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。 3.3V LVCMOS: Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。 CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。 ECL:Emitter Coupled Logic 发射极耦合逻辑电路(差分结构) Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。