一·1.数据类型BIT与STD_LOGIC有什么区别。

BIT类型的取值只能是0或1,没有不定状态X,也没有高阻态。

STD_LOGIC类型可以有9种不同的值,包括U-初始值,X-不定,0-0,1-1,Z-高阻态,W-弱信号不定,L-弱信号0,H弱信号1.‘—’不可能情况。

2.信号和变量的异同。

信号是全局量,只要在结构体中已经定义,就可以在结构体中的所有地方使用,信号的赋值符号是”<=”,信号带入时可以附加延时,信号实际带入过程和带入语句的处理时分开进行的。

变量是局部量,只能在进程,子程序内部定义和使用,变量的赋值符号是“:=”,变量的赋值是立即执行的,不能附加延时。

3.VHDL语言的基本顺序语句和并行语句有哪些?

双性语句:信号带入语句

顺序语句:WHAT语句,断言语句,变量赋值语句,IF语句,CASE语句,LOOP语句,NEXT语句,EXIT语句,过程调用语句,NULL语句。

并行语句:进程(PROCESS)语句,条件带入语句,选择信号带入语句,并发过程调用语句,块语句。

4.用VHDL语言进行硬件设计的流程是什么?

1.分析实际的需求2确定芯片的功能3.用VHDL 语言描述改元件4.编译,如果有错误修改后再编译直至编译通过。5.仿真,如果仿真不符合设计要求,修改程序直至仿真通过。6.测试7.综合,8.下载到实际的芯片上。

5.基本的硬件描述语言的种类有哪些?

美国国防部开发的VHDL。

Verilog公司开发的Verilog-HDL.

日本电子工业振兴协会开发的UDL/I语言。

6.VHDL语言中包含的库的种类有哪些?库:是经编译后的数据的集合,它存放包集合定义,实体定义,构造体定义,和配置定义。库的种类:1.IEEE库,2.STD库,3.面向ASIC 的库,4.WORK库,5.用户定义库

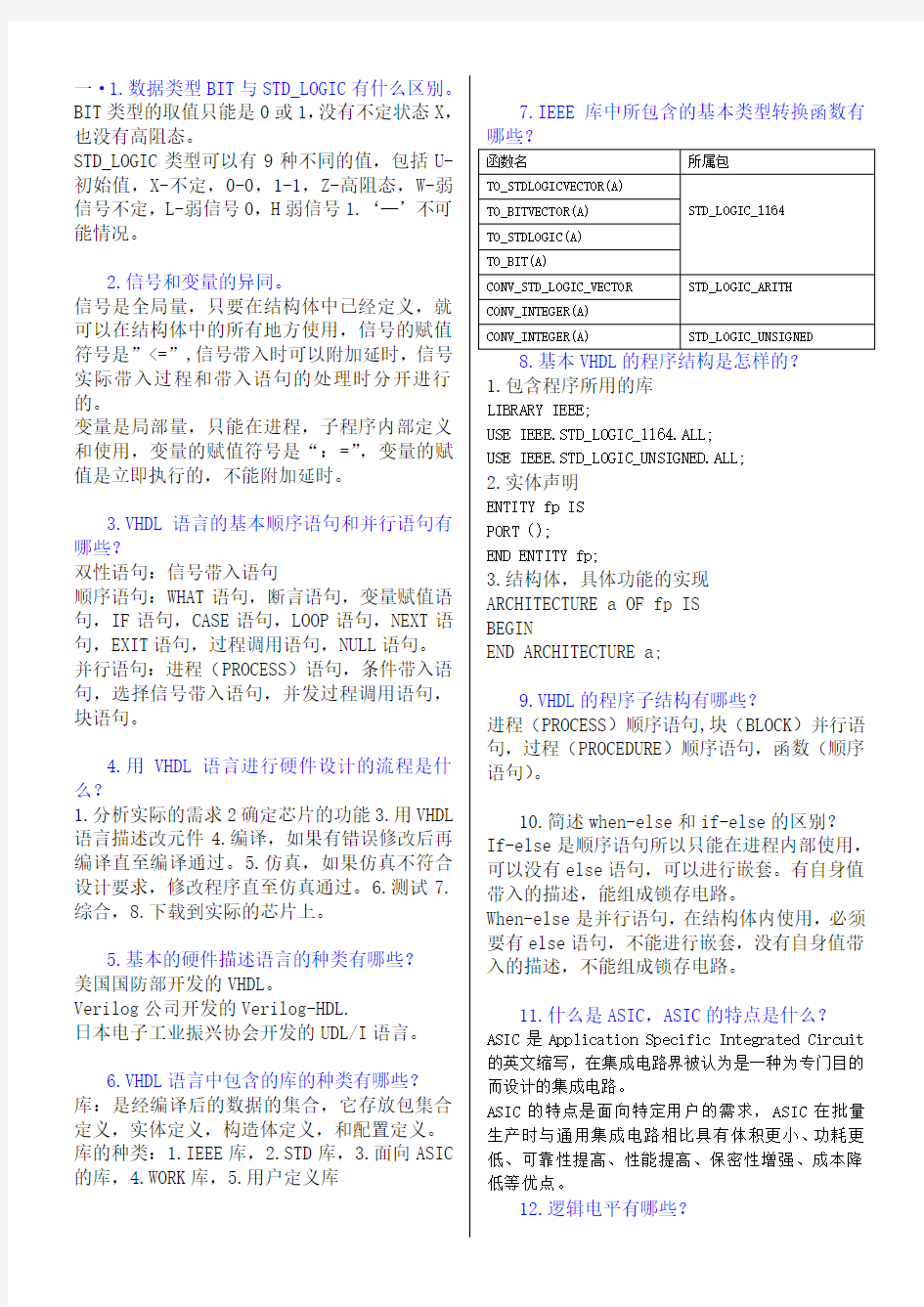

7.IEEE库中所包含的基本类型转换函数有

1.包含程序所用的库

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

2.实体声明

ENTITY fp IS

PORT();

END ENTITY fp;

3.结构体,具体功能的实现

ARCHITECTURE a OF fp IS

BEGIN

END ARCHITECTURE a;

9.VHDL的程序子结构有哪些?

进程(PROCESS)顺序语句,块(BLOCK)并行语句,过程(PROCEDURE)顺序语句,函数(顺序语句)。

10.简述when-else和if-else的区别?

If-else是顺序语句所以只能在进程内部使用,可以没有else语句,可以进行嵌套。有自身值带入的描述,能组成锁存电路。

When-else是并行语句,在结构体内使用,必须要有else语句,不能进行嵌套,没有自身值带入的描述,不能组成锁存电路。

11.什么是ASIC,ASIC的特点是什么?ASIC是Application Specific Integrated Circuit 的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

12.逻辑电平有哪些?

逻辑电平:有TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等。

·其中TTL和CMOS的逻辑电平按典型电压可分为四类:5V系列(5V TTL和5V CMOS)、3.3V 系列,2.5V系列和1.8V系列。

·5V TTL和5V CMOS逻辑电平是通用的逻辑电平。

13.TTL电平和CMOS电平可以互联吗?

数字电路中TTL电平是个电压范围,规定输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

CMOS电平在不同的电路中是0v-5v或者0v-12v。所以可以用CMOS电平驱动TTL电平器件,但是TTL 电平驱动CMOS电平器件时须加上拉电阻。

二·用VHDL语言描述给定电路,或写出给定电路的功能或输出。

三.程序改错。

四.注释程序。

五.程序同功能语句替换。

六.元件例化连接器件。

程序例子:

IF语句:(1)IF(sel=’0’)THEN

y<=’1’;

END IF;

(2)IF (sel=’0’)THEN

y<=’0’;

ELSE

y<=’1’;

END IF;

(3)IF(sel=”00”)THEN

y<=”01”;

ELSIF(sel=”01”)THEN

y<=”10”

……

ELSE

y<=”11;

END IF;

CASE语句:CASE sel IS

WHEN “00”=>y<=”00”;

WHEN “01”=>y<=”10”;

WHEN “11”=>y<=”11”;

END CASE;

FOR语句:FOR i IN 0 TO 7 LOOP

tmp:=tmpXORa(i);

END LOOP; WHILE语句:WHILE(i<8)LOOP

tmp:=tmpXORa(i);

i:=i+1;

END LOOP;

WHEN-ELSE语句(类似if-else):

q<=i0 WHEN sel=”00” ELSE

i1WHEN sel=”01” ELSE

i2WHEN sel=”10” ELSE

i3 WHEN sel=”11” ELSE

‘X’;

WITH-SELECT语句:(类似CASE语句)

WITH sel SELECT

q<=i0 WHEN “00” ,

i1 WHEN “01” ,

i2 WHEN “10” ,

i3 WHEN “11” ,

‘X’WHEN OTHERS ;

分频器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY fp IS

PORT(clk: IN STD_LOGIC;

fp1024,fp512,fp64,fp4,fp1: OUT STD_LOGIC); END ENTITY fp;

ARCHITECTURE a OF fp IS

SIGNAL buf:STD_LOGIC_VECTOR(9 DOWNTO 0); BEGIN

fp1<=buf(9);

fp4<=buf(7);

fp64<=buf(3);

fp512<=buf(0);

fp1024<=clk;

PROCESS(clk) IS

BEGIN

IF(clk'EVENT AND clk='1') THEN

IF(buf="1111111111") THEN LIBRARY IEEE;

报时电路

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY bs IS

PORT(min,sin: IN STD_LOGIC_VECTOR(7 DOWNTO 0); clk,bs512,bs1024: IN STD_LOGIC;

bsout: OUT STD_LOGIC);

END ENTITY bs;

ARCHITECTURE a OF bs IS

BEGIN

PROCESS(clk) IS

BEGIN

IF(clk'EVENT AND clk='1') THEN

IF(min="01011001") THEN

CASE sin IS

WHEN "01010000"=>bsout<=bs512;

WHEN "01010010"=>bsout<=bs512;

WHEN "01010100"=>bsout<=bs512;

WHEN "01010110"=>bsout<=bs512;

WHEN "01011000"=>bsout<=bs512;

WHEN "01011001"=>bsout<=bs1024;

WHEN OTHERS=>bsout<='0';

END CASE;

END IF;

END IF;

END PROCESS; END ARCHITECTURE a;

buf<="0000000000";

ELSE

buf<=buf+'1';

END IF;

END IF;

END PROCESS;

END ARCHITECTURE a;

元件例化

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count60 IS

PORT(clkin,en,res: IN STD_LOGIC;

bs0,bs1: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

cyout: OUT STD_LOGIC);

END ENTITY count60;

ARCHITECTURE count OF count60 IS

COMPONENT count10 IS

PORT(clk,enable,reset: IN STD_LOGIC;

b0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

cy: OUT STD_LOGIC);

END COMPONENT;

SIGNAL count4:STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL clk1,cy1:STD_LOGIC;

BEGIN

bs1<=count4;

cyout<=cy1;

u0:count10 PORT

MAP(clk=>clkin,cy=>clk1,reset=>res,enable=>en,b0=>bs0) ;

PROCESS(clk1,res,en) IS

BEGIN

IF(res='0') THEN

count4<="0000";

ELSIF (clk1'EVENT AND clk1='1') THEN

IF(en)='1' THEN

IF(count4="0110") THEN

count4<="0000";

cy1<='1';

ELSE

count4<=count4+'1';

cy1<='0';

END IF;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE count;

硬件描述语言实验附录 姓名:xxx 学号:xxx 指导教师:xxx 目录 硬件描述语言实验附录 (1) 实验1.三输入与门电路实验 (2) 实验2. 三—八译码器实验 (3) 实验3. D触发器实验 (4) 实验4. 分频器实验 (5) 实验5. 状态机实验 (8)

实验1.三输入与门电路实验 --三输入与门电路threeinput --姓名:王定 --学号:1306034248 --中北大学 LIBRARY IEEE; --调用库 USE IEEE.STD_LOGIC_1164.ALL;--库文件 -------------------------------------------------------------- ENTITY threeinput IS --定义实体名,其名称必须与VHDL文本文件名称相同PORT( A: IN STD_LOGIC; --输入端口,时钟输入 B: IN STD_LOGIC; --输入端口,个位写入使能 C: IN STD_LOGIC; --输入端口,十位写入使能 CO: OUT STD_LOGIC); --输出端口,溢出标志 END ENTITY threeinput; --结束端口定义 -------------------------------------------------------------- ARCHITECTURE RTL OF threeinput IS--定义结构体 BEGIN PROCESS(A,B,C) IS --开始,必须带上 BEGIN CO<=A AND B AND C ; END PROCESS; END ARCHITECTURE RTL; --结束结构体 表1. 三输入与门电路VHDL实验代码 图1. 三输入与门电路仿真波形图,A,B,C输入,CO输出

VHDL大总结 一、填空题 1.两种标识符 短、扩展 2.4种基本数据类型 常量、变量、信号、文件 3.常量说明格式 constant 常数名: 数据类型:=表达式; 4.三种数据变换方法? 函数转换、常数转换、类型标记 5.四种运算操作符? 逻辑、关系、算术、并置 6.如何启动进程? (1).必须包含一个显示的敏感信号变量 (2).或者包含一个wait语句 7.五种基本结构? 库(library)、包集合(package)、实体(entity)、结构体(architecture)、配置(configuration) 8.信号与变量代入? (1).<= (2).:= 9.列举可编程逻辑器件? PROM→PLA→PAL→CPLD→FPGA→EPROM→EEPROM→GAL 10.数据类型 整数、位、位矢量、符号、布尔量、时间、错误等级、标准逻辑 11.四种端口模式? IN—OUT—INOUT—BUFFER 12.三种子结构描述语句?BLOCK—PROCESS—SUBPROGRAMS

13.结构体三种描述方式 寄存器传输(RTL)--数据流、结构描述、行为描述14.标识符规则? (1).不以数字靠头 (2).下划线不连续 (3).不与保留字重复 (4).下划线前后必须有英文字母或者数字 (5).最后一个不能使用下划线(连字符) 15.扩展标识符 \12@+\ 16.赋值? (1).信号、变量可以多次赋值 (2).常量只能定义时赋值(进程内部,子函数内部)17.高阻、不定态? 'Z'------------'X' 18.进程位置? 结构体内部 19.变量位置? 进程内部---包内部----子程序内部 20.进程执行机制? 敏感信号发生跳变 21.优先级? if语句之间具有不同优先级 22.时序电路的去驱动信号? 时钟 23.时序电路在何时发生变化? 时钟信号的边沿 24.两种状态机? (1).moore-----f(现状) (2).mealy-----f(现状,输入)