Xilinx FPGA的PROM配置

作者:枪手2007年8月16号

1.建立工程,假如VHDL,UCF文件,综合,执行。

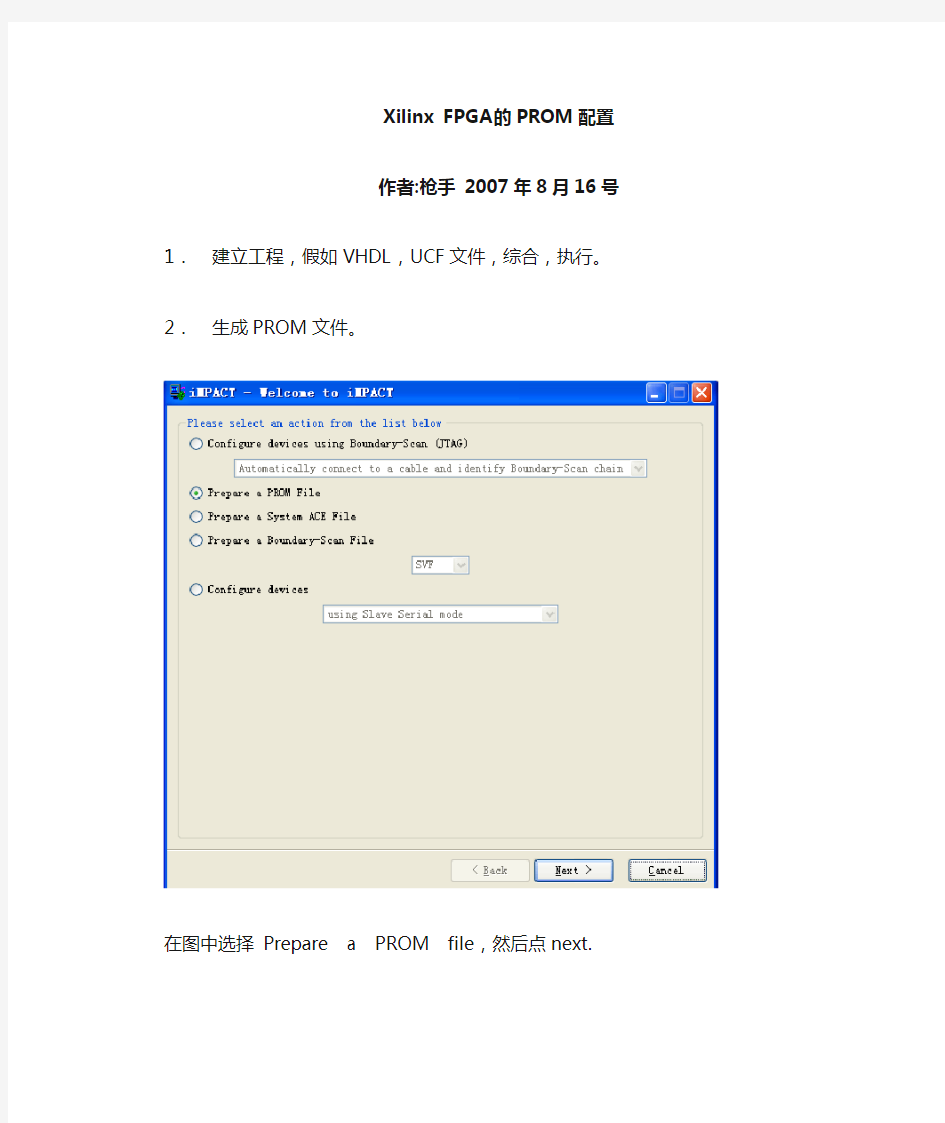

2.生成PROM文件。

在图中选择Prepare a PROM file,然后点next.

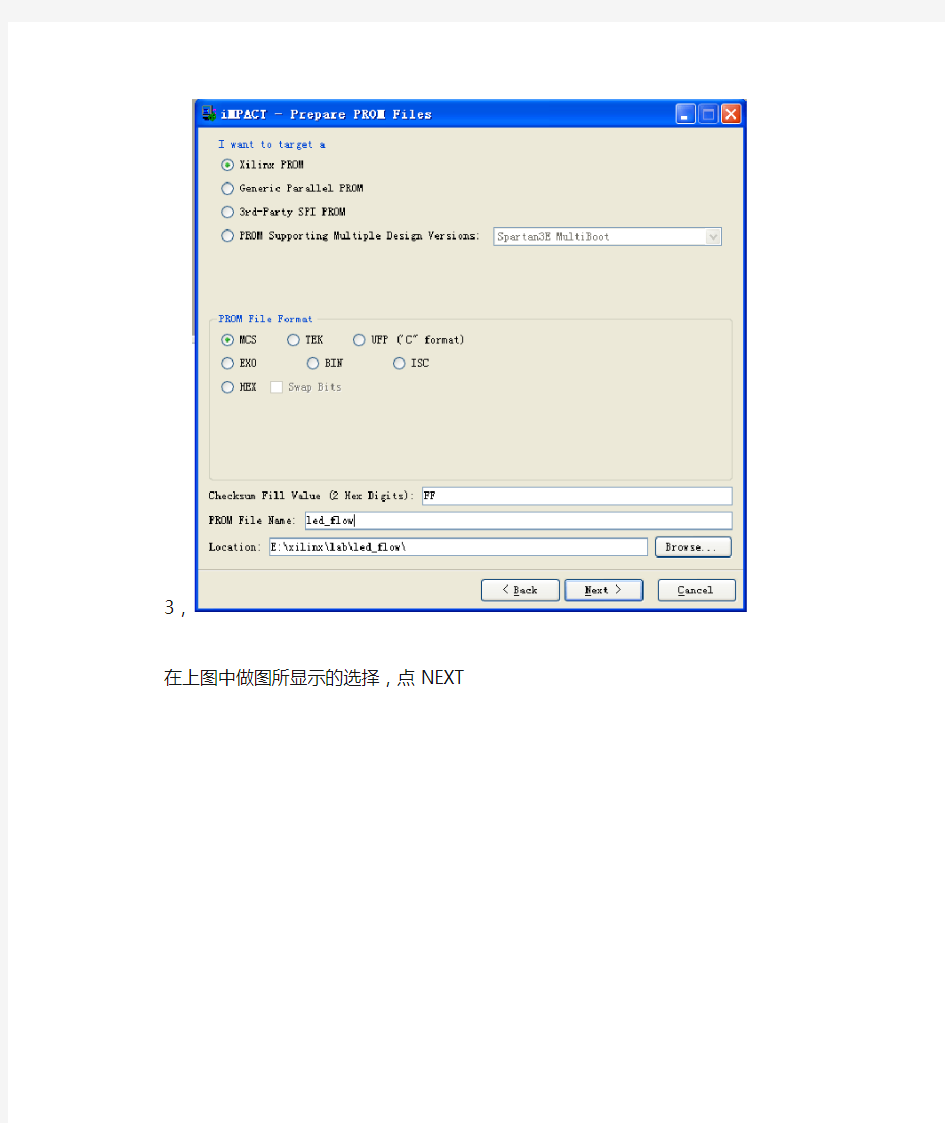

3,

在上图中做图所显示的选择,点NEXT

4

在上图中选择所用开发板上的PROM,SP3E用XCF04S,点ADD,添加到列表中。然后点next,出现file generation summary!

5.

确定是不是和所选择的一致,点finish。6.

出现上面对话框的时候,点OK。7.

在上面图中,选择bit文件。

8.

在出现上面对话框的时候,点NO。

9.然后,出现下面对话框,点OK。

10.在左边的impact modes 中,点Generate file

11.生成PROM FILE 文件成功。

12.在左边flows下,选择boundary scan。

13.点boundary scan后,出现下面界面。

14.点鼠标右键,选择initialize chain

15.出现下面下面界面。对于XC3S500E,点cancel。

16.对XCF04S,选择刚才生成的led_flow.mcs文件.

17,对第三个,点cancel.

18.上面选择后,出现下面界面,在XCF04S,点右键,出现一个菜单,选择Program.

19,点PROGRAM后,出现如下界面,按图中选择各项.

20,点OK 后,开始配置,

21.成功界面如下,然后,拨掉JTAG,关掉电源,过一会再上电.

中北大学 毕业设计开题报告学生姓名:周海芳学号:0906034202 学院、系:电子与计算机科学技术学院计算机科学与技术系 专业:计算机科学与技术 设计题目:个人博客系统的设计与实现指导教 师:元 2013年3月8日

毕业设计开题报告 1.结合毕业设计情况,根据所查阅的文献资料,撰写2000字左右的文献综述: 文献综述 一、选题的依据及意义 进入二十一世纪,以Internet为核心的现代网络积水和通信技术已经得到了飞速的发展和广泛的应用,各种网络交流互动工具也应运而生。其中以论坛、博客、社区、空间最为受广大网民朋友的欢迎,也是目前为止发展的比较成熟的信息交流工具。在网络技术逐渐渗入社会生活各个层面的今天,传统的交流方式也面临着变革,而网络博客则是一个很重要的方向。基于Web技术的网络考试系统可以借助于遍布全球的Internet 进行,因此交流既可以是本地进行,也可以是异地进行,大大拓展了沟通与交流的灵活性。博客在现如今这个飞速发展的网络时代已经成为人们不可或缺的一部分[1]。 博客,又译为网络日志、部落格或部落阁等,是一种通常由个人管理、不定期贴新的文章的。博客它经常是由简短且经常更新的帖子构成,它可以发表有关个人构思,日记,或者诗歌,散文,小说等等。博客可以是你纯粹个人的想法和心得,包括你对时事新闻、国家大事的个人看法,或者你对一日三餐、服饰打扮的精心料理等,也可以是在基于某一主题的情况下或是在某一共同领域由一群人集体创作的容。写博客是为了把自己各种各样的想法在网上表达、释放出来,把一时的想法变成观点展示给大家。而浏览博客的用户,也可以对发表观点和看法的文章进行评论,博客就是这样一个平台。 博客最初的名称是Weblog,由web和log两个单词组成,按字面意思就为网络日记,后来喜欢新名词的人把这个词的发音故意改了一下,读成we blog,由此,blog这个词被创造出来。中文意思即网志或网络日志,不过,在中国大陆有人往往也将 Blog本身和 blogger(即博客作者)均音译为“博客”。“博客”有较深的涵义:“博”为“广博”;“客”不单是“blogger”更有“好客”之意。看Blog的人都是“客”。而在,则分别音译成“部落格”(或“部落阁”)及“部落客”,认为Blog本身有社群群组的意含在,借由Blog可以将网络上网友集结成一个大博客,成为另一个具有影响力的自由媒体[2]。 二、个人博客的发展现状

标准铜排的选型指南 Final approval draft on November 22, 2020

1.目的 规范开关柜柜内用铜排的规格尺寸选择,即在铜排设计时选择合适的截面规格,以保证铜排在相应使用环境下的额定载流量。 2.适用范围 所有电工用铜和铜合金母线。 3.低压开关柜柜内铜排选择作业指导 低压开关柜柜内铜排的正常使用条件 铜排材料:符合GB/标准的TMY、THMY; 使用条件:环境温度35℃,允许温升70K; 海拔高度:< 1000m; 额定工作频率:50/60Hz。 若使用条件与上述不一致,根据铜排的具体使用条件按本指导书第4条对铜排的载流量重新校核。 系统水平主母线选择 在正常使用条件下,技术支持工程师按表1根据低压系统的额定电流选择或修改水平主母线的规格。若设计院不同意修改,技术支持工程师必须与机械设计工程师一起确认水平主母线的规格选择。 表1:水平裸铜母线额定载流量表(铜排立放,相间距单拼a=110、双拼a=110、三拼a=130)

柜内汇流母线选择 在正常项目设计中,低压开关柜柜内若干主电路连接在汇流母线上,在 任一时刻汇流母线通过的预计最大电流为连接其上的所有主电路的额定电流之和乘以额定分散系数(见表2)。汇流母线的规格按预计通过的最大电流来选择。馈线柜垂直裸铜母线的规格选择与对应的额定载流量见表3。 表2 表3 装置内其它铜母线选择 进线或联络开关的分支母线选择综合考虑系统的额定电流与开关的框架电流。当系统的额定电流大于开关的框架电流时,分支母线选择框架开关的额定电流;反之,选择系统的额定电流。其余 元器件连接母线按元器件的框架电流选择。铜排规格选择优先考虑使用K3系统中的常用铜排规格,使用不常用的铜排规格时必须得到机械分部经理的同意。装置内其它铜母线额定载流见 表4。 表4

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

毕业设计 题目:基于SSH构架的博客系统的设计和实现English title:The Design and Implementation for the blogs system based on SSH 姓名: xxxxx 学号: xxxxxxx 专业名称:计算机科学与技术 指导教师: xxxxx 二零一零年五

摘要 本文研究了当今博客系统的市场需求和种种的优势与不足,以及博客在中国发展迅速这一现状,提出了开发一个专业的博客管理系统的思想。本文对博客系统的运行机制、组成、相关可应用技术进行了深入的研究和分析,确定符合现在博客管理的需求,详细阐述了系统的总体设计和详细设计,并在此基础上,应用当前最流行的J2EE 三层结构、JSP技术、数据库等与系统开发相关的技术完成系统主要功能的实现。 本博客系统致力为广大用户提供优质的互动交流平台,实现对博客发表文章、评论、图片、好友等数据的管理,同时实现了博客内容及时、快速更新的功能,系统不仅保留了传统博客系统的功能,还加上了一些人性化的界面设计,使用户对博客的操作更为的方便。 为了满足博客信息管理系统的要求,实现系统静态与动态页面的相互分离,本系统采用了SSH构架设计,从职责上分为三层:表示层、业务逻辑层、数据持久层。其中使用Struts2作为系统的整体基础架构,负责MVC的分离,在Struts2框架的模型部分,利用Hibernate框架对持久层提供支持,业务层用Spring支持。具体做法是:用面向对象的分析方法根据需求提出一些模型,将这些模型实现为基本的Java对象,然后编写基本的DAO接口,并给出Hibernate的DAO实现,采用Hibernate架构实现的DAO类来实现Java类与数据库之间的转换和访问,最后由Spring完成业务逻辑。 关键词:表示层;业务逻辑层;数据持久层;Struts;Hibernate;Spring

Xilinx spartan3e FPGA掉电配置及应用程序引导 Xilinx公司的spartan3e开发板上面有丰富的外围器件,就存储器来说有一个16M并行flash,一个4Mbits串行flash,还又一个64M的DDR,在嵌入式开发中,一般我们可能会在FPGA中嵌入cpu软核,让C语言程序在里面运行。这就涉及到FPGA配置文件的引导,如果C语言程序太大,需要在DDR里面运行的话也涉及到应用程序的引导的问题。我刚接触到xinlinx的spartan3e开发板时,只会将FPGA配置文件(.bit)直接通过JTAG口下载到芯片里。后来编写的程序大了,如果将程序直接放到内部的RAM里面就装不下了,这时就只有将程序放到DDR里面运行,如果仅仅是调试应用程序不需要重启开发板后程序也可以运行,那么可以直接用EDK里面的XDM工具通过dow命令直接下载到DDR里面,然后就可以执行了。但是但我们的应用程序和硬件配置调试通过,达到了我们的要求以后我们就想到可不可以将让程序在板子上电时就可以自动运行呢。因为FPGA是掉电要丢失的,重新上电就必须重新配置。我们通过查找相关资料,找到了解决烧写问题的解决办法。首先是配置文件的烧写。spartan3e提供了3个掉电不丢失的外部存储器,就是上面提到的并行flash,串行flash和Flash PROM。配置文件都可以烧写到其中任何一个储存器里面。但是,在我看来,一般的配置问件都是烧写到Flash PROM里面。烧写方法有很多,可以用Xilinx公司的专门的烧写.mcs文件的工程烧写,也可以用iMPACT烧写。一般用iMPACT工具烧写,烧写过程如下: 打开iMPACT,弹出新建工程时选择Cancle,然后双击窗口左边的

毕业设计(论文)中文摘要

毕业设计(论文)外文摘要

目录 1 绪论 ......................................................... - 1 - 1.1博客概况.. (1) 1.1.1 博客的产生............................................ - 1 - 1.1.2 博客的现状............................................ - 2 - 1.2博客的发展、需求与前景 (2) 1.3本论文任务概述 (2) 1.4本论文章节安排 (3) 2 系统设计与实现 ............................................... - 3 - 2.1需求分析.. (3) 2.1.1 功能需求.............................................. - 3 - 2.1.2 项目计划安排.......................................... - 3 - 2.2系统开发环境. (4) 2.2.1开发环境简介 .......................................... - 4 - 2.2.2 Visual Studio 2008开发环境简介 ....................... - 5 - 2.2.3 SQL Server 2005数据库简介 ............................ - 5 - 2.3相关技术简介. (5) 2.3.1 C#语言简介............................................ - 5 - 2.3.2 https://www.doczj.com/doc/106311512.html, 简介.......................................... - 6 - 2.3.3 https://www.doczj.com/doc/106311512.html, 简介.......................................... - 6 - 2.3.4 Silverlight技术简介 .................................. - 7 - 2.3.5 WCF简介 .............................................. - 7 - 2.3.6 jQuery库简介 ......................................... - 8 - 2.4系统设计与实现.. (8) 2.4.1 分层架构核心思想...................................... - 8 - 2.4.2 实体介绍.............................................. - 9 - 2.4.3 数据库设计........................................... - 10 - 2.4.4 实体类的设计与实现................................... - 12 - 2.4.5 接口设计............................................. - 12 - 2.4.6 IoC 容器及依赖注入机制的设计......................... - 14 - 2.4.7 数据访问层的实现..................................... - 17 - 2.4.8 业务逻辑层的实现..................................... - 24 - 2.4.9 表示层的实现......................................... - 26 - 2.4.10 视频模块的实现...................................... - 28 - 3 系统功能演示 ................................................ - 30 - 3.1系统功能演示 (30) 3.2小结 (36)

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

1.目的 规范开关柜柜内用铜排的规格尺寸选择,即在铜排设计时选择合适的截面规格,以保证铜排在相应使用环境下的额定载流量。 2.适用范围 所有电工用铜和铜合金母线。 3.低压开关柜柜内铜排选择作业指导 3.1低压开关柜柜内铜排的正常使用条件 铜排材料:符合GB/T5585.1-2005标准的TMY、THMY; 使用条件:环境温度35℃,允许温升70K; 海拔高度:< 1000m; 额定工作频率:50/60Hz。 若使用条件与上述不一致,根据铜排的具体使用条件按本指导书第4条对铜排的载流量重新校核。 3.2系统水平主母线选择 在正常使用条件下,技术支持工程师按表1根据低压系统的额定电流选择或修改水平主母线的规格。若设计院不同意修改,技术支持工程师必须与机械设计工程师一起确认水平主母线的规格选择。 表1:水平裸铜母线额定载流量表(铜排立放,相间距单拼a=110、双拼a=110、三拼a=130)

3.3柜内汇流母线选择 在正常项目设计中,低压开关柜柜内若干主电路连接在汇流母线上,在任一时刻汇流母线通过的预计最大电流为连接其上的所有主电路的额定电流之和乘以额定分散系数(见表2)。汇流母线的规格按预计通过的最大电流来选择。馈线柜垂直裸铜母线的规格选择与对应的额定载流量见表3。 表2:额定分散系数值(引用标准GB 7251.1-2005 4.7条表1) 表3:垂直裸铜母线额定载流量表(相间距a=80)

3.4装置内其它铜母线选择 进线或联络开关的分支母线选择综合考虑系统的额定电流与开关的框架电流。当系统的额定电流大于开关的框架电流时,分支母线选择框架开关的额定电流;反之,选择系统的额定电流。其余元器件连接母线按元器件的框架电流选择。铜排规格选择优先考虑使用K3系统中的常用铜排规格,使用不常用的铜排规格时必须得到机械分部经理的同意。装置内其它铜母线额定载流见表4。 表4:装置内其它铜母线额定载流量表(设计选型)

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

毕业设计(论文)开题报告 题目名称: 个人博客网站的设计与实现 学院: 计算机科学技术学院 专业年级: 学生姓名: 班级学号: 指导教师: 二O—三年十二月二十二日

xxxx 计算机科学技术学院本科生毕业设计开题报告 开题报告内容 1. 选题经过 进入二十一世纪,以In ternet 为核心的现代网络积水和通信技术已经得到了飞速 的发展和广泛的应用,各种网络交流互动工具也应运而生。其中以论坛、博客、社区、 空间最为受广大网民朋友的欢迎,也是目前为止发展的比较成熟的信息交流工具。随 着网络技术的日渐成熟,互联网已成为日常生活工作中必不可少的工具,网络博客在 近几年更是成为各类网民不可或缺的展示自我表现自我的强大工具,其强大的功能良 好的互动性在很大程度上满足了广大网民的需求。 2. 国内外研究现状 以博客命名的起源于 1999年,2001年9.11事件,世贸大楼糟恐怖袭击,博客成 提供了最具影响力交流互动平台, 是继Email 、BBS QQ 之后新兴的第四种网络交流方 式,已经成为最强劲的互联网新兴媒体的代表。由于具有丰富的娱乐形式和自由的个 2005中国的网民数已超过 1亿人,网民数位居世界第二。其中,到去年底,中国博客 现的,早些时候博客只是一个新的网络名词并无特殊之处, 雨后春笋般冒 出来,博得越来越多网民的欢心,并在互联网上引发了一股博客热 潮。 目前国内知名的博客有:新浪博客,腾讯博客,搜狐博客,博客中国等等。 代是计算机时代,人们的工作大部分都依赖计算机。数字化的世界里,人与人的交流 也慢慢的数字化,而博客网站正适应这种人际交流方式的改变,迎合个人信息共享的 需求它就是个人信息发布的场所,是人与人沟通的一个聚集地。 3. 初步设想 在建立个人网站博客系统时,首先要解决的主要技术问题是:客户端网站导航, 对博客文章的浏览留言评论及对博客相册内容的浏览留言评论。服务器端的主要操作 专业名称 XXXX 软件方向 指导教师 XXX XX 论文题目 个人博客网站的设计与实现 开题报告日期 2013年12月22日 选题依据。(选 题经过及国内 为信息和灾难亲身体验的重要来源,从此博客正式步入主流社会的视野。博客为人们 外研究现状) 人表达方式,博客成为新新人群竞相追逐的一种时尚。 2006年4月21日,数据显示: 规模已经达到1600万,全球博客总规模突破 1亿。 第一批中文博客是在 2002年出 。就在不经意间,博客竟如 当今时

Xilinx FPGA配置的一些细节 2010年07月03日星期六 14:26 0 参考资料 (1) Xilinx: Development System Reference Guide. dev.pdf, v10.1 在Xilinx的doc目录下有。 (2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005 在Xilinx网站上有,链接 (3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007 在Xilinx网站上有,链接 注:此外xapp139和xapp151也是和配置相关的。 (4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007 (5) Tell me about the .BIT . 链接: 1 Xilinx配置过程 主要讲一下Startup Sequence。 Startup Sequence由8个状态组成. 除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。 其中默认顺序如下: 这些在ISE生成bit文件时通过属性页设定。 这几个状态的具体含义如下: Release_DONE : DONE信号变高 GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态 GTS : 激活用户IO,之前都是高阻。

知识不仅是指课本的内容,还包括社会经验、文明文化、时代精神等整体要素,才有竞争力,知识是新时代的资本,五六十年代人靠勤劳可以成事;今天的香港要抢知识,要以知识取胜 摘要 随着Internet的广泛应用 动态网页技术也应运而生 本文介绍了应用ASP动态网页技术开发博客系统的设计与实现 博客系统主要为用户提供发表文章、浏览文章等功能 用户通过Internet可以发表一些自己撰写的文章以和其他网友进行交流 博客系统主要实现了文章管理的数字化、信息化、智能化 是打破传统报刊、杂志发表文章方式的新尝试 本系统的开发设计实现采用ASP技术 系统后台使用SQL Server 2008数据库 并通过使用ODBC技术访问 本文对博客系统进行整体分析 明确了系统的可行性和用户需求;根据模块化原理 规划设计了系统功能模块;在数据库设计部分 详细说明了系统数据库的结构和数据库的完整性、安全性措施;程序设计则采用面向对象的程序设计思想 提出系统的程序设计思路 对前台与后台功能的程序实现进行了详细论述;系统测试部分

具体分析测试过程中出现的主要问题 并提出了解决方案 实现系统功能 最后 对系统作以客观、全面的评价 并对进一步改进提出了建议 关键字:博客ASP SQL Server 2008 ODBC 目录 1 系统概述 3 1.1项目背景3 1.2系统开发的意义 4 1.2.1发布想法 4 1.2.2博客的用途4 1.3 系统开发的目标 5 1.3.1任何拥有博客的人都可以做到5 1.3.2 访问博客系统的人 可以做到 5 1.4系统概述5 1.5 系统的开发方法 6 2 系统分析8 2.1 可行性分析8 2.2 需求分析8

Xilinx ISE 13.4软件使用方法 本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。 1 A 1 1.建立工程 运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示 F1软件初始状态表 选择File->New Project ,该对话框显示用向导新建工程所需的步骤。 在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。在Location 栏中选择想要存放的工程位置,如“E:\code\Xilinx\test”。顶层语言选项栏中选择“HDL”语言。设置向导最终设置效果如图F2所示 F2路径信息设置表

点击“Next”,进入芯片型号选择界面。在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。 F3芯片信息选择表 点击“Next”,出现如图F4所示工程信息汇总表格。 F4工程信息汇总表 点击“Finish”完成设置。

2新建Verilog文件 在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。 F5 在File name栏中键入verilog文件的名称,如“test”。 F6 点击“Next”,在本界面中将设置加法器的输入输出引脚数量,如图F1所示的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,因此设置结果如图F7所示。

F7 点击“Next”,出现Verilog 新建信息汇总表。 F8 点击“Finish”,完成Verilog 新建工作。 3逻辑设计 输入代码

。。。公司铜芯线及铜排选用标准 注备说明:①本表定值适用于每个接线端子连接一根导线 ②该值均取自于GB7251.1~2005 8.2.1.1章节满足于型式

试验,符合导线长期截流不超过7.3条的规定;试验导 线最小距离≤35㎡时为1m 最小距离为≥35㎡时为2m ③结合建筑电气工程验收规范GB50303~2002及北京地区 电气规程:750V铜芯BV、BVR塑料长期连续负荷允 许载流量(A)表1校正。 ④环境温度为+30℃,导线线芯最高允许温度为+65℃ ⑤建议32A是选用6m㎡导线,在特别说明的情况下采用 10m㎡ 母排: 1、执行GB5585.2~85标准 1. 1 型号:TMY 名称硬铜母线 1.2 a×b 符合GB.5581.0第6.1条表2规定 偏差符合GB5585.1第6.2条表3规定 1.3 抗拉强度:符合GB5585.2标准第5.2条表3规定 伸长率:符合GB5585.2标准第5.2条表3规定 硬度:符合GB5585.2标准第5.2条表3规定 弯曲:符合GB5585.2标准第5.3条表4规定 电阻率:符合GB5585.2标准第5.4条表5规定 直度:符合GB5585.1标准第Ⅱ章规定 2、硬铜线载流长期载流量 依据: 1. GB7251.11.2 ~2005 低压成套开关设备和控制设备

第一部分:型式试验和部分型式试验成套设备8.2.1.4 条表9 参考:2.《北京地区电气规程汇编》母线长期允许载流量表4规定 3. 建筑电气工程施工质量验收规范GB50303~2002 4. 水电部出版《高压配电装置规程》 表一:单片母线的载流量:单位:A 工作温度:25℃~40℃

毕业设计(论文)开题报告 题目名称: 个人博客网站的设计与实现 学 院: 计算机科学技术学院 专业年级: 学生姓名: 班级学号: 班 号 指导教师: 二○一三 年 十二 月 二十二 日设技术过程接地线件中安装结艺高中工况装置高资料资料试料试卷理,此,

XXXX计算机科学技术学院本科生毕业设计开题报告专业名称XXXX方向软件方向 指导教师XXX学生XX 论文题目个人博客网站的设计与实现开题报告日期2013年12月22日 开题报告内容 选题依据。(选题经过及国内外研究现状)1.选题经过 进入二十一世纪,以Internet为核心的现代网络积水和通信技术已经得到了飞 速的发展和广泛的应用,各种网络交流互动工具也应运而生。其中以论坛、博客、社区、空间最为受广大网民朋友的欢迎,也是目前为止发展的比较成熟的信息交流工具。随着网络技术的日渐成熟,互联网已成为日常生活工作中必不可少的工具,网络博客在近几年更是成为各类网民不可或缺的展示自我表现自我的强大工具,其强大的功能良好的互动性在很大程度上满足了广大网民的需求。 2.国内外研究现状 以博客命名的起源于1999年,2001年9.11事件,世贸大楼糟恐怖袭击,博客 成为信息和灾难亲身体验的重要来源,从此博客正式步入主流社会的视野。博客为人们提供了最具影响力交流互动平台,是继Email、BBS、QQ之后新兴的第四种网络交 流方式,已经成为最强劲的互联网新兴媒体的代表。由于具有丰富的娱乐形式和自由的个人表达方式,博客成为新新人群竞相追逐的一种时尚。2006年4月21日,数据 显示:2005中国的网民数已超过1亿人,网民数位居世界第二。其中,到去年底, 中国博客规模已经达到1600万,全球博客总规模突破1亿。第一批中文博客是在2002年出现的,早些时候博客只是一个新的网络名词并无特殊之处,。就在不经意间,博客竟如雨后春笋般冒出来,博得越来越多网民的欢心,并在互联网上引发了一股博客热潮。目前国内知名的博客有:新浪博客,腾讯博客,搜狐博客,博客中国等等。当今时代是计算机时代,人们的工作大部分都依赖计算机。数字化的世界里,人与人的交流也慢慢的数字化,而博客网站正适应这种人际交流方式的改变,迎合个人信息共享的需求它就是个人信息发布的场所,是人与人沟通的一个聚集地。 3.初步设想 在建立个人网站博客系统时,首先要解决的主要技术问题是:客户端网站导航,对博客文章的浏览留言评论及对博客相册内容的浏览留言评论。服务器端的主要操作 、 管 路 敷 设 技 术 通 过 管 线 敷 设 技 术 不 仅 可 以 解 决 吊 顶 层 配 置 不 规 范 高 中 资 料 试 卷 问 题 , 而 且 可 保 障 各 类 管 路 习 题 到 位 。 在 管 路 敷 设 过 程 中 , 要 加 强 看 护 关 于 管 路 高 中 资 料 试 卷 连 接 管 口 处 理 高 中 资 料 试 卷 弯 扁 度 固 定 盒 位 置 保 护 层 防 腐 跨 接 地 线 弯 曲 半 径 标 高 等 , 要 求 技 术 交 底 。 管 线 敷 设 技 术 中 包 含 线 槽 、 管 架 等 多 项 式 , 为 解 决 高 中 语 文 电 气 课 件 中 管 壁 薄 、 接 口 不 严 等 问 题 , 合 理 利 用 管 线 敷 设 技 术 。 线 缆 敷 设 原 则 : 在 分 线 盒 处 , 当 不 同 电 压 回 路 交 叉 时 , 应 采 用 金 属 隔 板 进 行 隔 开 处 理 ; 同 一 线 槽 内 , 强 电 回 路 须 同 时 切 断 习 题 电 源 , 线 缆 敷 设 完 毕 , 要 进 行 检 查 和 检 测 处 理 。 、 电 气 课 件 中 调 试 对 全 部 高 中 资 料 试 卷 电 气 设 备 , 在 安 装 过 程 中 以 及 安 装 结 束 后 进 行 高 中 资 料 试 卷 调 整 试 验 ; 通 电 检 查 所 有 设 备 高 中 资 料 试 卷 相 互 作 用 与 相 互 关 系 , 根 据 生 产 工 艺 高 中 资 料 试 卷 要 求 , 对 电 气 设 备 进 行 空 载 与 带 负 荷 下 高 中 资 料 试 卷 调 控 试 验 ; 对 设 备 进 行 调 整 使 其 在 正 常 工 况 下 与 过 度 工 作 下 都 可 以 正 常 工 作 ; 对 于 继 电 保 护 进 行 整 核 对 定 值 , 审 核 与 校 对 图 纸 , 编 写 复 杂 设 备 与 装 置 高 中 资 料 试 卷 调 试 方 案 , 编 写 重 要 设 备 高 中 资 料 试 卷 试 验 方 案 以 及 系 统 启 动 方 案 ; 对 整 套 启 动 过 程 中 高 中 资 料 试 卷 电 气 设 备 进 行 调 试 工 作 并 且 进 行 过 关 运 行 高 中 资 料 试 卷 技 术 指 导 。 对 于 调 试 过 程 中 高 中 资 料 试 卷 技 术 问 题 , 作 为 调 试 人 员 , 需 要 在 事 前 掌 握 图 纸 资 料 、 设 备 制 造 厂 家 出 具 高 中 资 料 试 卷 试 验 报 告 与 相 关 技 术 资 料 , 并 且 了 解 现 场 设 备 高 中 资 料 试 卷 布 置 情 况 与 有 关 高 中 资 料 试 卷 电 气 系 统 接 线 等 情 况 , 然 后 根 据 规 范 与 规 程 规 定 , 制 定 设 备 调 试 高 中 资 料 试 卷 方 案 。 、 电 气 设 备 调 试 高 中 资 料 试 卷 技 术 电 力 保 护 装 置 调 试 技 术 , 电 力 保 护 高 中 资 料 试 卷 配 置 技 术 是 指 机 组 在 进 行 继 电 保 护 高 中 资 料 试 卷 总 体 配 置 时 , 需 要 在 最 大 限 度 内 来 确 保 机 组 高 中 资 料 试 卷 安 全 , 并 且 尽 可 能 地 缩 小 故 障 高 中 资 料 试 卷 破 坏 范 围 , 或 者 对 某 些 异 常 高 中 资 料 试 卷 工 况 进 行 自 动 处 理 , 尤 其 要 避 免 错 误 高 中 资 料 试 卷 保 护 装 置 动 作 , 并 且 拒 绝 动 作 , 来 避 免 不 必 要 高 中 资 料 试 卷 突 然 停 机 。 因 此 , 电 力 高 中 资 料 试 卷 保 护 装 置 调 试 技 术 , 要 求 电 力 保 护 装 置 做 到 准 确 灵 活 。 对 于 差 动 保 护 装 置 高 中 资 料 试 卷 调 试 技 术 是 指 发 电 机 一 变 压 器 组 在 发 生 内 部 故 障 时 , 需 要 进 行 外 部 电 源 高 中 资 料 试 卷 切 除 从 而 采 用 高 中 资 料 试 卷 主 要 保 护 装 置 。

复位和上电复位 1 在上电时,这器件要求VCCINT在精确的上升时间内,单调的上升到标准工作电压值。 2 如果电压没满足要求,这器件就不能执行合适的上电复位。 3 上电运行的顺序:先PROM的OE/RESET保持低电平,在配置开始以前要求电源能达到它们各自的POR(上 电复位电压)门限,OE/RESET被定时释放后对稳定电源的应用有更多的余地。 4 在系统利用慢上升电源时,另外增加一个电源监控电路能被用做延时配置直到系统电源达到最小的操作 电源在OE/RESET一直为低电平。 5 当OE/RESET被释放,INIT就被上拉为高电平,允许FPGA有次序的配置。 6 如果电压低于POR门限时,PROM复位,OE/RESET再为低,直到达到POR 门限。 7 对于PROM电压正常时,只要OE/RESET=0或CE=1,复位就开始,当地址计数器复位时,CEO输出高电平,其 它的数据输出脚为高阻态。 8 XCFXXS PROM 只要求OE/RESET被释放以前,VCCINT上升到POR门限就行了。 9 XFCXXP PROM 在OE/RESET被释放以前,不但要求VCCINT上升到POR 门限,而且还要求VCCO达到被推荐的 正常工作电压。 配置 1 当JTAG配置指令在PROM里被更新时,PROM暂时给CF一个低电平,接着就给CF一个高电平。结合CF脚在外 部加了上拉电阻,此时在CF脚输出一个‘高-低-高’的脉冲个FPGA的PROGRAM 脚。此次FPGA就依次的开始 配置。 2 在CF脚外部必须加个上拉电阻,防止CF脚产生一个浮动到低电平的值而引起复位。 3 当XCFXXP的PROM存有多重设计文件时,CF脚必须连接到FPGA的PROGRAM_B脚去保证重新安放那些被选中 的设计文件(配置有效)。 4 对于XCFXXS的PROM,CF脚只是个输出,如果没有由于的功能的话,可以