第三章习题参考答案

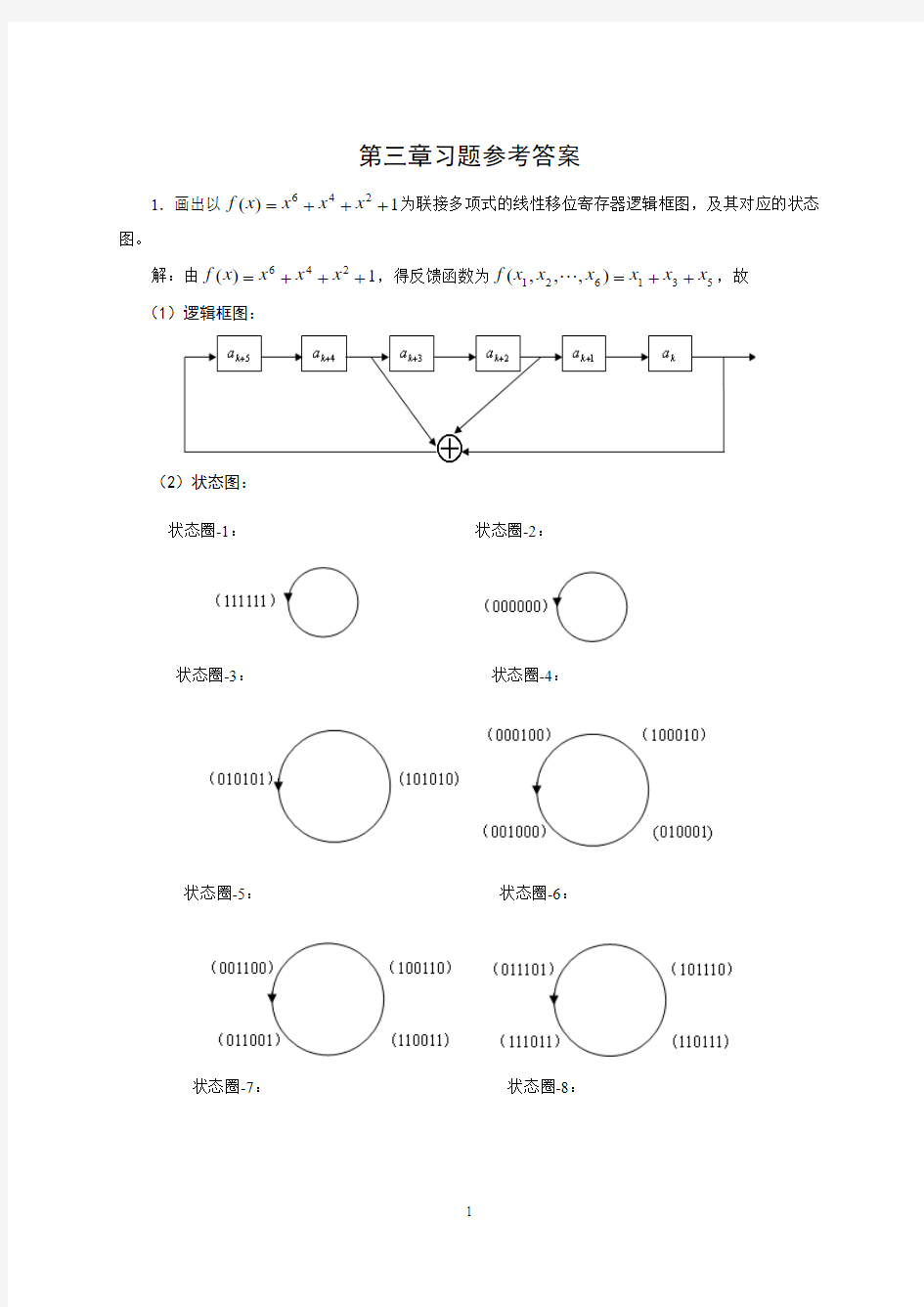

1.画出以1)(246+++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。

解:由1)(246+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++= ,故 (1)逻辑框图:

(2)状态图:

状态圈-1: 状态圈-2:

状态圈-3: 状态圈-4:

状态圈-5: 状态圈-6:

状态圈-7: 状态圈-8:

状态圈-9: 状态圈-10:

状态圈-11: 状态圈-12:

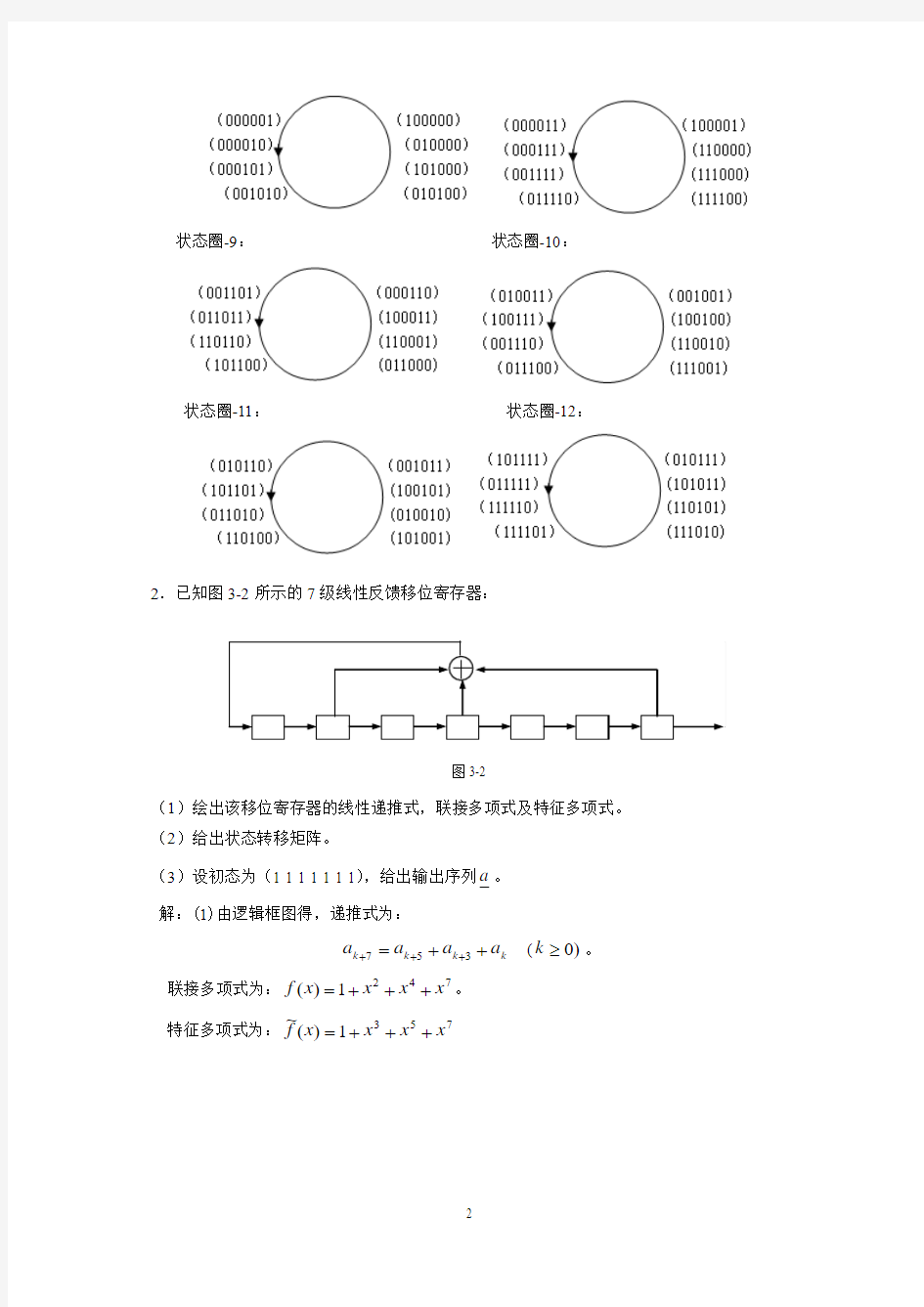

2.已知图3-2所示的7级线性反馈移位寄存器:

图3-2

(1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。

(3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为:

k k k k a a a a ++=+++357 ()0≥k 。

联接多项式为:7

4

2

1)(x x x x f +++=。

特征多项式为:7531)(~

x x x x f +++=

(2)状态转移矩阵:?

?

????

?

??

?

?

??0100000

101000000010001000100

000001000000011000000。 (3)输出序列:)111111111( =-

a 。

3.设5级线性反馈移位寄存器的联接多项式为1)(25++=x x x f ,初态为(10101)。求输出序列a 。

解:由联接多项式得,反馈函数为:41521),,,(x x x x x f += 。故以)10101

(为初态的状态转移图为:

10101

01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a

一个周期

0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n

F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n

F 2,∈?βα,令),,,(110-=n a a a α,

),,,(110-=n b b b β,有:

),,,(),,,()(1

21110∑=--==n i i n i n f f a c a a a a a T T α,

),,,(),,,()(1

21110∑=--==n

i i n i n f f b c b b b b b T T β。

)

()()

,,,(),,,()

)(,,,()

,,,()(1

211

2112211111100βαβαf f i n n

i i i n n i i n

i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑

对 2F k ∈?,

))((),,,(),,,()(1

21110ααf i n n

i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ 。

故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n

F 2上的线性变换。

5.设二元周期序列a 0≠的极小多项式为)(x f ,T 是)(x f 对应的状态转换矩阵,则S ,

ST ,…,1)(-a p ST 必两两不同。其中),,,(120-=n a a a S 。

证明:若?j i ,,1)(0-≤≠≤a p j i ,使得

j i ST ST = (不妨设 j i <)。

令 j i -=τ,则 S ST =τ

。于是,对k S ?,有 ττT S T ST ST S k k k k ===,即

k k a a =+τ ,0≥k 。

从而τ()(a p <)为序列a 的周期,与)(a p 为最小周期矛盾。故

S ,ST ,…,1)(-a p ST

必两两不同。

6.证明:若a )(f G ∈的极小多项式次数为)1(≥n ,则a ,a L ,…,a L n 1-必线性无关。 证明:由题知0≠a ,假设a ,a L ,…,a L n 1

-线性相关,则存在不全为零一组数110,,,-n c c c

使得

0)(011101110=+++==+++----a L c L c c a L c a L c a c n n n n

令:)(~x g 11

10--+++=n n x c x c c ,则)(x g 也产生序列a ,而1)(0

-≤?n x g ,与a 的极小多项式)(x f 的次数为n 矛盾,故假设不成立,因此,a ,a L ,…,a L n 1-必线性无关。

7.证明:若a )(f G ∈,n x f =?)(0,0≠a ,则a ,a L ,…,a L n 1-构成)(f G 的一组基当且仅当a 以)(x f 为极小多项式。

证明:充分性:由n x f o

=?)(知)(f G 是n 维的。又a )(f G ∈,a 以)(x f 为极小多项式,

由上题结论可知a ,a L ,…,a L n 1

-线性无关,故构成)(f G 的一组基。

必要性:设a 的极小多项式为)(x m a ,m x m a o

=?)(,则)(|)(x f x m a ,n m ≤。令:

m m m a x x c x c x c x m +++++=--112211)( ,

则0)(~=a L m a

,从而, a ,a L ,…,a L m

线性相关。而a ,a L ,…,a L

n 1

-为)(f G 的一组基,

所以1->n m ,即n m ≥,故)()(x f x m a =。即a 以)(x f 为极小多项式。

8.证明:若a )(f G ∈,n x f =?)(0

,a 以)(x f 为极小多项式,则)(f G 中每个序列均可唯

一地表成a D g )(,并且a D g )(的极小多项式为

))

(),(()(x f x g x f ,其中n x g

,D 为延迟变换。

从而)(f G 中有)(f ?个序列以)(x f 为极小多项式,其中)(f ?是次数f 0?≤,且和)(x f 互素的多 项式的个数。

证明:(1)上题结论知,)(f G b ∈?,都可由a ,a L ,…,a L n 1-为线性表出,则存在一组数110,,,-n c c c 使得:

a L c L c c a L c a L c a c

b n n n n )(011101110----+++==+++=

令:11

2210)(~--++++=n n x c x c x c c x g ,则有a D g b a L g b )()(~=?=,即)(f G b ∈?均可唯一的表示成a D g )(的形式。

(2)令:)())(),((x d x g x f =,则)()()(1x f x d x f =,)()()(1x g x d x g =,1))(),((11=x g x f 。 设a D g )(的极小多项式为)(2x f ,则只须证明))

(),(()

()()(12x g x f x f x f x f =

=。

)()()()()()()())()((11111====a D f D g a D g D f a

D g D d D f a D g D f

∴

)(1x f 为a D g )(的联接多项式,从而)(|)(12x f x f 。

又,由0)()()()()((122==a D g D d D f a D g D f 知,)()()(|)(12x g x d x f x f ,从而

)()(|)(121x g x f x f ,

而1))(),((11=x g x f ,故)(|)(21x f x f ,所以)()(12x f x f =,即 ))

(),(()

(x g x f x f 为-a D g )(的极小多

项式。

(3)当1))(),((=x f x g 时,-

a D g )(以)(x f 为极小多项式,而次数n <且与)(x f 互素的多项

式)(x g 共有)(f ?个。

9.设)(x f ][2x F ∈,0)0(≠f 。(1)证明)(f G 中任一平移等价类中序列有相同的极小多项式与周期。(2))(f G 中有相同的极小多项式的序列是否一定在同一平移等价类中?为什么?在什么条件下,序列的极小多项式相同当且仅当序列属于同一平移等价类?

证明:(1)设a )(f G ∈,a

L b t =(1)(0-≤≤a p t )是其平移等价序列,且有t k k a b +=,0≥k 。因为

k t k a p t k a p k b a a b ===++++)()(,0≥k 。

故)(|)(a p b p ,同理可证)(|)(b p a p ,所以)()(a p b p =。

设a 的极小多项式为)(x m a ,b 的极小多项式为)(x m b ,则 0)(~=a L m a

,从而 0)(0)(~)(~)(~=?===b D m a L m L a L L m b L m a

a t t a a , 即)(x m a 是

b 的联接多项式,于是)(|)(x m x m a b ,同理可证)(|)(x m x m b a 。因此)()(x m x m b a =。 (2)不一定。例如,1)(234++++=x x x x x f 是4次不可约多项式,)(f G 中非零序列都以

)(x f 为的极小多项式,但f G 中有3个周期为5的圈,显然这3个圈对应3个不同的平移等价类。

(或令 11000=a , 10111=b ,)(,f G b a ∈,但a 与b 不在同一等价类中。

) 当)(x f 是本原多项式时,序列的极小多项式相同当且仅当序列属于同一平移等价类。 10.设)(x f )()(21x f x f =,其中311)(x x x f ++=,221)(x x f +=][2x F ∈。(1)证明以0 1 1 1 1 0 0 1 0 0 0 0 1 1为一个周期段的二元序列属于)(f G 。(2)将上述序列分解成两个序列a 和b 之和,使得)(1f G a ∈,)(2f G b ∈。

证明:(1)1)()()(2

521+++==x x x x f x f x f , 令初态为=0S (01111),则)(x f 产生的

序列为: ,00110111100100

故以0 1 1 1 1 0 0 1 0 0 0 0 1 1为周期段的二元序列属于)(f G 。 (2)方法一:由1))(),((21=x f x f 知,存在1)(1=x g ,x x g =)(2,使得

)()()()(12211x f x g x f x g +=

令: ,00110111100100=c ,则

==c I c c D f D g )()(22+c D f D g )()(11,

记=a c D f D g )()(22,b =c D f D g )()(22,即有b a c +=。由引理 3.3.3 的证明过程知,

)(1f G a ∈ ,)(2f G b ∈,故a 和b 即为求:

=+=c D D a )(3 ,1101001

,b ,10,10)1(3=++=c D D 。

方法二 21f f f G G G = ,]7[1]1[11+=f G ,]2[1]1[22+=f G 。

]

14[1]7[1]2[]1[2]]

2,7)[[1,1(]]1,7)[[2,1(2]]2,1)[[1,1(]]1,1)[[2,1(221+++=+++==∴

f f f G G G

显然,周期为14的序列是由1f G 中1[7]和2f G 中1[2]唯一生成。 由 3

11)(x x x f ++=,令初态为=0S (01 1),输出序列为:

111010011100011101001。

由 221)(x x f +=,令初态为=0S (01),输出序列为: 010*******。 将上述两个输出序列异或求和有:

0111

00110111100100011001010101010101010101111010011100011101001上述序列

,1101001 =∴

-

a 。 ,10,10=-

b

11.设][)1()(22

2x F x x x f ∈++=,试问)(f G 中共有多少序列的平移等价类,每个平移等价类的周期是多少,对每个平移等价类构作出一个序列来。

解:由已知得1)(),()(,1,2,2212

1++=====x x x f x f x f m e n 令。而3)(1=f p ,故

]

6[2]3[1]1[1]

32[3

222]3[312]1[12

222

2

1

++=??-+-+=f G )(f G ∴中有4个平移等价类:一个周期为1的平移等价类; 一个周期为3的平移等价类; 两个周期为6的平移等价类。 周期为1的平移等价类中代表序列为零序列,

周期为3的平移等价类中代表序列为: ,011

两个周期为6的平移等价类中代表序列分别为: ,111001

和 ,110110。 12.求联接多项式为)1)(1()1()(4322++++++=x x x x x x x f 的线性移位寄存器的状态图f G 中的圈长和圈数。

解:令1)(2

1++=x x x f ,1)(3

2++=x x x f ,1)(43++=x x x f ,且)(),(),(321x f x f x f 两两互素,又3)(1=f p ,7)(2=f p ,15)(3=f p 。 由上题知,]6[2]3[1]1[12

1++=f G

。

对于)(2x f ,]7[1]1[12+=f G 。 对于)(3x f ,]15[1]1[13+=f G 。

]

210[6]105[4]30[6]42[2]21[1]15[4]7[1]6[2]3[1]1[1]210[6]30[6]42[2]6[2]105[3]15[3]3[1]21[1]105[1]15[1]7[1]1[1])

7[1]1[1])(30[6]6[2]15[3]3[1]15[1]1[1(])7[1]1[1])(15[1]1[1])(6[2]3[1]1[1(3

221

+++++++++=+++++++++++=++++++=++++=??=∴f f f f G G G G

f G ∴中有周期为1,3,7的圈各一个,2个周期为6的圈,周期为15,105的圈各 4

个,周期为30,210的圈各6个,周期为21的圈1个,周期为42的圈2个。

13.设a ,b 为周期序列,s ,r 为正整数。证明: (1))

()

()()(sr r s a

a

=。

(2))

()

()()(s s s b a

b a +=+。

(3)若)(mod a p r s ≡,则)

()

(s r a a =。

证明:(1)

)

(2020)

(210)

(20)()

(),,,(),,,(),,,(),,,()(rs rs rs r r r b a r s s r s a

a a a

b b b b b b a a a a k

ks ======

(2)

)

()

(20202200)

(221100)(),,,(),,,()

,,,(),,,()(s s s s s s s s s s s s b

a

b b b a a a b a b a b a b a b a b a b a +=+=+++=+++=+ (3)若)(mod a p r s ≡,则)()(N k r a kp s ∈+=

jr jr a jkp js a a a ==∴+-

)(

)

(2020)

(),,,(),,,(r r r s s s a

a a a a a a a

===∴

14.设)(x f 为n 次本原多项式,)(0f G a ∈≠,证明)

(s a

与)

12(s n a

--的极小多项式为互反多项

式。其中,*

1

2-∈n

Z s 。 证明:设γ为)(x f 的一根,因1)12,(=-n s ,1)12,(=--s s n ,故由定理3.4.4知:

)(s a 与)

12(s n

a

--都为n 级m 序列,对应的极小多项式)(x f s 和)()12(x f s n --皆为本原多项式,且s

γ和s

n

--12

γ分别为其n 次本元根。

又 s

s s

s

n n n ------=?==?121

1

212)(1γ

γγ

γ

γ,即两根互逆,从而)(x f s 和)()12(x f s n --互反,

所以)

(s a

与)

12(s n a

--的极小多项式为互反多项式。

15.求全部7级m 序列中平移等价类的个数。 解:全部7级m 序列中平移等价类的个数为:

7(21)

(21)

(127)

187

7

n n

φφφ--=

=

=。

16.用迹函数表示法表示)(f G 中序列,其中1)(4

++=x x x f 。

解:设α是在1)(~34++=

x x x f 42F 中的一个根,则

}

1,,1,,

1,,1,,1,

,1,,1,,1,0{},,,,0{][2323232333332222143210)

(~

242+++++++++++++++++===ααααααααααααααααααααααααααααα,, x f x F F

)(f G 中共有16条序列,设为)15,,1,0( =i a i ,于是有:

(1)0=β

()

() 000000),0(),0(),0(20=??=ααTr Tr Tr a

(2)1=β

()

() 001000111101011),1(),1(),1(2

1=??=ααTr Tr Tr a

(3)αβ=

()

() 010001111010110),(),(),(22=??=αααααTr Tr Tr a

(4) 1+=αβ

()

() 011001000111101),))1((,))1((),1(23=?+?++=αααααTr Tr Tr a )

(5) 2αβ=

()

() 0100011110110110),(),(),(22224=??=αααααTr Tr Tr a

(6) 12+=αβ

()

() 101011001000111),)1(()),)1(()),1((22225=?+?++=αααααTr Tr Tr a

(7) ααβ+=2

()

() 110010*********),)((),)((),(22226=?+?++=ααααααααTr Tr Tr a

(8) 12++=ααβ

(

)()

111010110010001),)1((),)1((),1(22227=?++?++++=ααααααααTr Tr Tr a

(9) 3αβ=

()

() 000111101011001),(),(),(23338=??=αααααTr Tr Tr a

(10)

13+=αβ

()

() 001111010110010),)1(())1((),1(23339=?+?++=αααααTr Tr Tr a ,

(11) ααβ+=3

()

() 010110010001111),)((),)((),(33310=?+?++=ααααααααTr Tr Tr a

(12) 13

++=ααβ

()

()

011110101100100),)1((),)1((),1(233311=?++?++++=ααααααααTr Tr Tr a (13) 2

3ααβ+=

()

() 100100011110101),)((),)((),(223232312=?+?++=ααααααααTr Tr Tr a (14) 123++=ααβ

(

)()

101100100011110),)1((),_)1((),1(223232313=?++?++++=ααααααααTr Tr Tr a

(15)

αααβ++=23

(

)()

110101100100011),)((),)((),(223232314=?++?++++=αααααααααααTr Tr Tr a

(16)12

3

+++=αααβ

()

()

111101*********),)1((),)1((),1(223232315=?+++?++++++=αααααααααααTr Tr Tr a

17.已知5级m 序列:

=a (1 1 1 1 1 0 0 0 1 1 1 0 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 1 0 0,…)

求出全部5次本原多项式。

解:{}30,3,2,131 =*

Z ,则

H H H H H H Z 151175331+++++=*

其中 {}16,8,4,2,1=H ,{}24,12,17,6,33=H ,{}20,18,10,9,55=H ,{}28,25,19,14,77=H ,

{}26,22,21,13,1111=H ,{}30,29,27,23,1515=H 。那么

),0110010011110110100001011100010()

3( =-a

),111111010000011100000101100()

5( =-

a

),1000101101011001001100001110111()

7( =-

a

),1010010001011000011011111011001()

11( =-

a

(1) 设-

a 的极小多项式为:55443322111)(x c x c x c x c x c x f +++++=,则其对应的线性递推式为:

)0(42332415≥+++=++++k a c a c a c a c a k k k k k 。

选-

a 的连续前10项:1111100011,将其代入线性递推式可得线性方程组:

?????

????=+=+=++=+++=++++1

1

00515

4543543254321c c c c c c c c c c c c c c c c 解该线性方程组得:1,0,1,0,054321=====c c c c c ,故5

311)(x x x f ++=。 (2)设)

3(-a

的极小多项式为:5

5443322121)(x c x c x c x c x c x f +++++=,则其对应的线性递

推式为:

)0(42332415≥+++=++++k a c a c a c a c a k k k k k 。

选)

3(-a

的连续前10项:1011100010,将其代入线性递推式可得线性方程组:

?????

????=+=+=++=++=+++0

1

00515

45434325321c c c c c c c c c c c c c c 解该线性方程组得:1,0,1,1,154321=====c c c c c ,53221)(x x x x x f ++++=。

(3) 设)

5(-a

的极小多项式为:55443322131)(x c x c x c x c x c x f +++++=,则其对应的线性递

推式为:

)0(42332415≥+++=++++k a c a c a c a c a k k k k k 。

选)

5(-a

的连续前10项:0010101100,将其代入线性递推式可得线性方程组:

?????

????=++=++=++=+=+0

1105324

215314231c c c c c c c c c c c c c 解该线性方程组得:1,1,1,0,154321=====c c c c c ,54331)(x x x x x f ++++=

若序列的联接多项式是本原多项式,则其特征多项式也为本原多项式,所以,所有5次本原多项式为:

5311)(x x x f ++=。 53221)(x x x x x f ++++=。

54331)(x x x x x f ++++=。 5241)(x x x f ++=。

543251)(x x x x x f ++++=。 54261)(x x x x x f ++++=。

18.设a 是一周期序列,若a 中有长为n 的游程,则a 的极小多项式的次数一定n ≥。

证明:假设-

a 的极小多项式的次数n k <。

若-

a 中有长为n 的1游程,则在k 级周期序列中至少有2个全1的状态与全1状态仅出现一次

矛盾。

若-

a 中有长为n 的0游程,则以 个

k ,00000为初态的序列只能产生零序列不能出现

),00010( 的形式,所以假设不成立。

故-

a 的极小多项式的次数一定n ≥

19.设),,,(310 a a a a =是n (1≥)级m 序列,试求数对:

),(t k k a a +,

(22,,1,0-=n k ,221-≤≤n

t ) 为)0,0(的次数。

解一:-

a 一个周期段中0和1的个数分别为12

1

--n ,12-n

则),(t k k a a +为)0,0(的总个数为12

1

21

---n c 又重复度为121

--n

∴),(t k k a a +为)0,0(的个数为

121

2

21

21

21

-=-----n n n c

解:)a (L t 和)a (L a t +都是m 序列,m 序列中0有121n --个,1有1n 2-个,

)a ,a (t k k +有(0,0)

,(0,1),(1,0),(1,1)四种情况, 设(0,0)的个数为x ,(1,1)个数为y ,则根据0,1分布知(0,1)的个数为x -121n --,(1,0)的个数为y 2

1

n --,故???-=-+-=+---1

2y 2x 1

2y x 1

n 1n 1n 可解得12x 2n -=- 即(0,0)的次数为122n --

20.用梅西算法,求产生下列有限序列的最短线性反馈移位寄存器的联接多项式。 (1)=a (1 1 1 0 1 1 1 0 0 0 1 0 1 0 1 1 0 1 0 0)。 (2)=b (1 1 1 1 0 1 1 1 1 0 )。 (1))10101101001110111000(=-

a

解:设

0,0,0,1,1,1,0,11,198********==========a a a a a a a a a a ,

0,0,1,0,1,1,0,1,0,119181716151413121110==========a a a a a a a a a a 第0

步:0,

1)(00==l x f

第1步:计算0d :0,

1000===l a d

则: 11)(11=+=l x x f

第2步:计算1d :0011=+=a a d 则: 11)()(1212==+==l l x x f x f

第3步:计算2d :0122=+=a a d 则: 11)()(2323==+==l l x

x f x f

第4步:计算3d :1233=+=a a d ,又有0=m 使13210=== 45==++==l l x x x f x f 第6步:计算5d :12455=++=a a a d ,又有3=m 使3543== 第7步:计算6d :14566=++=a a a d ,又有3=m 使36543=== 第8步:计算7d :1345677=++++=a a a a a d ,又有6=m 使476= 则: 46781)()()(x x xf x f x f +=+= 4)8,max(778=-=l l l 第9步:计算8d :1488=+=a a d ,又有6=m 使4876== 则: 3262891)()()(x x x f x x f x f ++=+= 5)9,max(889=-=l l l 第10步:计算9d :16799=++=a a a d ,又有8=m 使598= 则: 53289101)()()(x x x x x xf x f x f ++++=+= 5)10,max(9910=-=l l l 第11步:计算10d :057891010=++++=a a a a a d 则: 51)()(10115 321011==++++==l l x x x x x f x f 第12步:计算11d :0689101111=++++=a a a a a d 则: 51)()(11125 321112==++++==l l x x x x x f x f 第13步:计算12d :0791*******=++++=a a a a a d 则: 51)()(12135 321213==++++==l l x x x x x f x f 第14步:计算13d :0810********=++++=a a a a a d 则: 51)()(131********==++++==l l x x x x x f x f 第15步:计算14d :0911********=++++=a a a a a d 则: 51)()(14155 321415==++++==l l x x x x x f x f 第16步:计算15d :0101213141515=++++=a a a a a d 则: 51)()(15165 321516==++++==l l x x x x x f x f 第17步:计算16d :0111314151616=++++=a a a a a d 则: 51)()(16175 321617==++++==l l x x x x x f x f 第18步:计算17d :0914********=++++=a a a a a d 则: 51)()(17185 321718==++++==l l x x x x x f x f 第19步:计算18d :0131516171818=++++=a a a a a d 则: 51)()(18195 321819==++++==l l x x x x x f x f 第20步:计算19d :0141617181919=++++=a a a a a d 则: 51)()(19205 321920==++++==l l x x x x x f x f 因此,>++++<5,15 3 2 x x x x 就是产生此序列的最短线性移位寄存器 (2))1111011110(=- b 解:设0,1,1,1,1,0,1,11,198********==========a a a a a a a a a a , 第0步:0, 1)(00==l x f 第1步:计算0d :0,1000===l a d 则: 11)(11=+=l x x f 第2步:计算1d :0011=+=a a d 则: 11)()(1212==+==l l x x f x f 第3步:计算2d :0122=+=a a d 则: 11)()(2323==+==l l x x f x f 第4步:计算3d :0233=+=a a d 则: x x f x f +==1)()(34 134==l l 第5步:计算4d :1344=+=a a d 则: 404451)()()(x x x f x x f x f ++=+= 4)5,max(445=-=l l l 第6步:计算5d :01455=++=a a a d 则: 4561)()(x x x f x f ++== 456==l l 第7步:计算6d :12566=++=a a a d ,又有4=m 使4654== 则: 43242671)()()(x x x x x f x x f x f ++++=+= 4)7,max(667=-=l l l 第8步:计算7d :0345677=++++=a a a a a d 则: 432781)()(x x x x x f x f ++++== 478==l l 第9步:计算8d :0456788=++++=a a a a a d 则: 432891)()(x x x x x f x f ++++== 489==l l 第10步:计算9d :0567899=++++=a a a a a d 则: 4329101)()(x x x x x f x f ++++== 4910==l l 因此,>++++<4,1432x x x x 就是产生此序列的最短线性移位寄存器 21.设周期序列=a (1 1 1 1 0 1,…)的极小多项式为16 ++x x ,求a 的有理分式表示。 解: ) () ()(0x f x g x a x a i i i == ∑∞ =- 因为)(x f 为-a 的极小多项式,故6)()(00=? 5 4 1)()()(x x x a x f x g ++=?=-,故-a 的有理分式为:1 1 )(645++++=-x x x x x a 。 22.设周期序列a 的有理分式表示为:7 64324 311)(x x x x x x x x x x a +++++++++=,求序列a 及其周期。 解:5325322211)1)(1()1)(1()(x x x x x x x x x x x a +++=+++++++=-,令5 31)(x x x f ++=,为本原多项式 3112)(5=-=∴ - a p ,序列以11111为初态的序列为: 0001001011001110101001111100011 23.设),,,,,,(10110 a a a a a a p -=是周期为p 的二元周期序列,则序列 ),,,,,(210211 -----=p p p p a a a a a a 的极小多项式为)(~x m a 。 证明:设- a 的极小多项式为)(1x m ,则- a 的形式幂级数表示为有理分式: ) () (1111 1100x m x g x x a x a a x a p p p i i i = -+++= --∞ =∑ 其中1))(),((11=x m x g 记1 -- - =a b ,- b 的极小多项式为)(2x m ,则- b 的形式幂级数表示为有理分式: ) () (1221 1100 x m x g x x b x b b x b p p p i i i = -+++= --∞ =∑ 其中1))(),((22=x m x g 令1110211101)(,)(----+++=+++=p p p p x b x b b x h x a x a a x h 则: )()(~ 21x h x h = )1)(()()(, )1)(()()(222111p p x x g x m x h x x g x m x h -=-= )(~ 1)(x f x x f p =-= )()()()(~)(~)(~2 22111 x m x h x g x m x h x g =∴ )()()(~)(~2 2 11x m x g x m x g =∴ 又1))(),((11=x m x g ,1))(~),(~(11=∴x m x g )()(~2 1x m x m =∴。 即- a 与1 -- a 的极小多项式为互反多项式 24.设周期序列a 与b 的有理分式表示分别为: )() ()(x f x h x a = 及) ()()(1x f x h x b =, 其中1))(),(())(),((1==x h x f x h x f 。证明:a 与b 平移等价的充要条件是存在非负整数 1))((-≤x f p k ,使得))(mod ()()(1x f x h x h x k ≡。 解:必要性: 若- a 与- b 平移等价,则存在非负整数1)(-≤f p k ,使得)(- -=b L a k ∑-=--+=∴1 )()(k i i i k x b x a x x b ,即∑-=+=101)()()()(k i i i k x b x f x h x x f x h )(mod )()(1x f x h x x h k ≡∴ 充分性:存在非负整数1)(-≤f p k ,使得)(mod )()(1x f x h x x h k ≡则设∑∞ == )(i i i x b x g 使 得:∑-=+=+=101)()()()()()()(k i i i k k x b x f x h x x g x f x h x x f x h , 即:∑∞ =--+=0 )()(i i i k x b x a x x b )(- - =∴b L a k 即- a 与- b 平移等价。 证明:平移等价与若b a ""? ()()()()()()()()()()()()()() x f x h x x h x b x f x h x x f x h x b x a x x b x a x x b x b x f p k k k o i i i k k o i i i k k k i i i m o d :1 11111 1 ≡?+=+=?=--≤?∑∑∑-=-=-=即使得存在非负整数 “?”若存在非负整数()()使得.1-≤x f p ()()()()x f x h x h x k m o d 1≡ 则存在 ()使得,x g ()()x h x x h k ≡1+()()x f x g (1) 若()()k x g ≥?0,则 ()()()() ()()()()()()k x g x h x f x f x g x h x k ?≥+?0 1000故 ()()()(). 10 平移等价与故又b a x b x g x a x x g x b i k i i k ∑-===-∴ 移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、原理说明 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。按代码的移位方向可分为左移、右移和可逆移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同又可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图8-3-3-1所示。 其中 D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入 C为直接无条件清零端; 端,S L为左移串行输入端;S1、S0为操作模式控制端;R CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和R C端的控制作用如表8-3-3-1。 图8-3-3-1 CC40194的逻辑符号及引脚功能 表8-3-3-1 CC40194功能表 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图8-3-3-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图8-3-3-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。其状态表如表8-3-3-2所示。 表8-3-3-2 环形计数器状态表 图 8-3-3-2 环形计数器 如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。 图8-3-3-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。 8位移位寄存器的电路设计与版图实现 摘要 电子设计自动化,缩写为EDA,主要是以计算机为主要工具,而Tanner EDA则是一种在计算机windows平台上完成集成电路设计的一种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等子软件,其S-Edit以及L-Edit为常用软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,而T-Spice主要可实现电路图及版图的仿真,可以用Tanner EDA实现电路的设计布局以及版图实现等一系列完整过程。本文用Tanner EDA工具主要设计的是8位移位寄存器,移位寄存器主要是用来实现数据的并行和串行之间的转换以及对数据进行运算或专业处理的工具,主要结构构成是触发器,触发器是具有储存功能的,可以用来储存多进制代码,一般N 位寄存器就是由N个触发器构成,移位寄存器工作原理主要是数据在其脉冲的作用下实现左移或者右移的效果,输入输出的方式表现为串行及并行自由组合,本设计就是在Tanner EDA的软件平台上进行对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直至完成的结果和预期结果保持一致。 关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit 8 bits shift register circuit design and layout Abstract Electronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results. Keywords:Tanner EDA;L-Edit;Shift register,S-Edit 第三章习题参考答案 1.画出以1)(2 4 6 +++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。 解:由1)(2 46+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++=Λ,故 (1)逻辑框图: (2)状态图: 状态圈-1: 状态圈-2: 状态圈-3: 状态圈-4: 状态圈-5: 状态圈-6: 状态圈-7: 状态圈-8: 状态圈-9: 状态圈-10: 状态圈-11: 状态圈-12: 2.已知图3-2所示的7级线性反馈移位寄存器: 图3-2 (1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。 (3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为: k k k k a a a a ++=+++357 ()0≥k 。 联接多项式为:7 4 2 1)(x x x x f +++=。 特征多项式为:7531)(~ x x x x f +++= (2)状态转移矩阵:? ? ???? ? ?? ? ? ??0100000 101000000010001000100 000001000000011000000。 (3)输出序列:)111111111(ΛΛ=- a 。 3.设5级线性反馈移位寄存器的联接多项式为1)(2 5 ++=x x x f ,初态为(10101)。求输出序列a 。 解:由联接多项式得,反馈函数为:41521),,,(x x x x x f +=Λ。故以)10101(为初态的状态转移图为: 10101 01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a 44444443444444421一个周期 0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n F 2,∈?βα,令),,,(110-=n a a a Λα, ),,,(110-=n b b b Λβ,有: ),,,(),,,()(121110∑=--==n i i n i n f f a c a a a a a T T ΛΛα, ),,,(),,,()(1 21110∑=--==n i i n i n f f b c b b b b b T T ΛΛβ。 ) ()() ,,,(),,,() )(,,,() ,,,()(1 211 2112211111100βαβαf f i n n i i i n n i i n i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑ΛΛΛΛ 对 2F k ∈?, ))((),,,(),,,()(1 21110ααf i n n i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ΛΛ。 故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n F 2上的线性变换。 河南科技大学 课程设计说明书 课程名称 EDA技术与应用 题目移位寄存器的设计与实现 学院 班级 学生姓名 指导教师 日期 EDA技术课程设计任务书 班级:姓名:学号: 设计题目:移位寄存器的设计与实现 一、设计目的 进一步巩固理论知识,培养所学理论知识在实际中的应用能力;掌握EDA设计的一般方法;熟悉一种EDA软件,掌握一般EDA系统的调试方法;利用EDA软件设计一个电子技术综合问题,培养VHDL编程、书写技术报告的能力。为以后进行工程实际问题的研究打下设计基础。 二、设计任务 根据计算机组成原理中移位寄存器的相关知识,利用VHDL语言设计了三种不同的寄存器:双向移位寄存器、串入串出(SISO)移位寄存器、串入并出(SIPO)移位寄存器。 三、设计要求 (1)通过对相应文献的收集、分析以及总结,给出相应课题的背景、意义及现状研究分析。 (2)通过课题设计,掌握计算机组成原理的分析方法和设计方法。 (3)学习按要求编写课程设计报告书,能正确阐述设计和实验结果。 (4)学生应抱着严谨认真的态度积极投入到课程设计过程中,认真查阅相应文献以及实现,给出个人分析、设计以及实现。 四、设计时间安排 查找相关资料(1天)、设计并绘制系统原理图(2天)、编写VHDL程序(2天)、调试(2天)、编写设计报告(2天)和答辩(1天)。 五、主要参考文献 [1] 江国强编著. EDA技术与实用(第三版). 北京:电子工业出版社,2011. [2] 曹昕燕,周凤臣.EDA技术实验与课程设计.北京:清华大学出版社,2006.5 [3] 阎石主编.数字电子技术基础.北京:高等教育出版社,2003. [4] Mark Zwolinski. Digital System Design with VHDL.北京:电子工业出版社,2008 [5] Alan B. Marcovitz Introduction to logic Design.北京:电子工业出版社,2003 指导教师签字:年月日 实验五移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3 为并行输入端;Q 、Q 1 、Q 2 、Q 3 为并行输出端;S R 为右 移串行输入端,S L 为左移串行输入端;S 1 、S 为操作模式控制端;R C为直接无 条件清零端;CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3 ),左移 (方向由Q 3→Q ),保持及清零。 S 1、S 和R C端的控制作用如表10-1。 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态Q Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q 0Q 1 Q 2 Q 3 将依次变为0100→0010→0001→1000 →……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图10-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 图 10-2环形计数器 如果将输出Q O 与左移串行输入端S L 相连接,即可达左移循环移位。 (2)实现数据串、并行转换 实验报告 课程名称:数字电路实验第 6 次实验实验名称:移位寄存器的应用 实验时间:2012 年 5 月7 日 实验地点:组号 学号: 姓名: 指导教师:评定成绩: 《数字电路与系统设计》实验指导书 1 实验六移位寄存器应用 一、实验目的: 1.了解寄存器的基本结构。 2.掌握74LS194移位寄存器的逻辑功能。 3.学习中规模移位寄存器的应用。 二、实验仪器: 三、实验原理: 数据的存储和移动是数字信号的一种常见运作,能实现这种动作的是数据寄存器和移位寄存器,它们同计数器一样也是数字电路中不可缺少的基本逻辑器件。数据寄存器有两类结构,一类是由多个钟控D锁存器组成的,另一类是由多个钟控D触发器组成的。数据寄存器的数据的输入和输出都是并行的。移位寄存器的结构也是由多个触发器级联的,其数据不仅可以存储,还可以左移或右移。移位寄存器的数据的输入和输出都有串行和并行之分,数据的动作受公共时钟信号的控制,也就是同步工作的。 4位双向移位寄存器74LS194A为TTL双极型数字集成逻辑电路,外形为双列直插,它具有清除、左移、右移、并行送数和保持等多种功能,是一种功能比较全的中规模移位寄存器,图6-1是引脚排列图,逻辑符号如图6-2所示,74LS194A的功能表见表6-1。 《数字电路与系统设计》实验指导书 2 移位寄存器的最直接应用是数据的串/并转换,图6-3和图6-4就是简单的实例。在图6-3中M1M0=01,表示数据可以右移,首先清零端输入一个负脉冲,使Q1Q2Q3Q4=0,在单脉冲CP的作用下,右移输入端D R依次串入数据,4个CP后就可在4个输出端Q1Q2Q3Q4得到并行数据。在图6-4中首先M1M0=11,在单脉冲CP的作用下,4位数据并行输入到移存器,然后使M1M0=10,表示数据可以左移,左移输入端D L=1时,在单脉冲CP的作用下,数据依次从Q1端输出,空缺位被1(D L)填补。4个CP 后,原4位并入的数据全被移出,这时候Q1Q2Q3Q4=1111。 实验十七、移位寄存器74164的逻辑功能测 试 一、实验目的 1、掌握中规模8位移位寄存器逻辑功能。 2、认识74LS164及其引脚封装。 二、实验预习要求 1、复习有关寄存器的内容。 2、查阅74LS164及逻辑电路,熟悉其逻辑功能及引脚排 列。 三、实验设备 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、DM74LS164 四、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中锁存的代码能够在移位脉冲的作用下一次左移和右移。既能左移又能右移称为双向移位寄存器,只需要改变左、右移的控制信号可实现双向移位要求。根据移位寄存器取存信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的8位移位寄存器,型号可为74LS164,其逻辑符号及引脚排列如图所示。 其中A、B为串行输入端; CLR为异步清零端; QH—QA为输入端; CLK为移位脉冲输入端; 74164是一种串行输入、并行输出的器件,时钟高电平有效,没有时钟使能端,该器件用低电平复位 图1 74LS164的逻辑符号及引脚功能表其中QAO、QBO、QHO为在暂稳态输入条件建立之前QA、QB和QH相应的电平;QAN、QGN为在最近的时钟上升沿转换前QA或QG的电平,表示移一位。 移位寄存器应用很广,可构成移位寄存器型计数器;属虚脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换位并行数据,或把并行数据转换位串行数据等。 五、实验内容 1、测试74LS164的逻辑功能 按图所示接线,A、B、CLK分别接至逻辑电平显示输入端。QA—QH分别接至逻辑电平显示输出端。14脚接+5V电源、7脚接地。 实验十一移位寄存器及其应用 一、实验目的: 1、熟悉中规模4位双向移位寄存器的逻辑功能并掌握其使用方法; 2、熟悉移位寄存器的应用典例一——构成串行累加器和环形计数器。 二、实验原理: 1、移位寄存器是一种具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的移位寄存器称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位。根据存取信息的方式不同移位寄存器可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同, S L为左移串行输入端;S1、S0为操作模式控制端;CR为异步清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:并行送数寄存,右移(方向由Q3至Q0),左移(方向由Q0至Q3),保持及清零。S1、S0和CR 端的控制作用如表11-1所示。表11-1 2、移位寄存器的应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验主要研究移位寄存器用作环形计数器和串行累加器的线路连接及其原理。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图11-2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q3Q2Q1Q0=1000,则在时钟脉冲的作用下Q3Q2Q1Q0将依次变为0100、0010、0001、1000-----,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图11-2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 (2)串行累加器 累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。 图11-2 图11-3是由两个右向移位寄存器、一个全加器和一个进位触发器组成的串行累加器。 设开始时,被加数A=A N-1.....A O和加数B=B N-1......B O已分别存入N+1位累加数移位寄存器和加数移位寄存器。再设进位触发器D已被清零。 在第一个CP脉冲到来之前,全加器各输入、输出端的情况为:A N=A0,B N=B0,C N-1=0,S N=A0+B0+0=S0,C N=C0。 当第一个CP脉冲到来后,S0存入累加和移位寄存器的最高位,C0存入进位触发器D端,且两个移位寄存器中的内容都向右移动一位。全加器输出为S N=A1+B1+C0=S1,C N=C1。 74LS194左右移位寄存器 一、移位寄存器 在数字电路中,用来存放二进制数据或代码的电路称为寄存器。按功能 可分为:基本寄存器和移位寄存器。 移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。 二、74LS194双向移位寄存器 目前常用的集成移位寄存器种类很多,其中74LS194为四位双向移存器。 图一 74LS194移位寄存器的引脚图 以上为74LS194的引脚图,其中 D 0~D 3 :并行输入端; Q ~Q 3 :并行输出端; S 0、S 1 :操作模式控制端;:为直接无条件清零端; S R :右移串行输入端 S L :左移串行输入端; CP:时钟脉冲输入端; 表一 74LS194的模式控制和状态输出表 三、移位寄存器型计数器 利用移位寄存器可构成环形和扭环形计数器。可先使S 0=S 1 =1,并行输入预 置数值,再改变S 0和S 1 的电平,实现左移或右移状态。若把移位寄存器的输出 以一定方式反馈到串行输入D SR 端或D SL 端,就可以构成移位寄存器型计数器。 例如,将74LS194的Q 3接到D SR 端,可得到模4的环形计数器(不可自启动); 将Q 3端通过一个非门接到D SR 端,则可得到模8的扭环形计数器(不可自启动)。用一片74LS194及门电路构成一个课实现7分频或8分频器。7分频器的分 频信号由Q 2输出,同时将Q 2 、Q 3 输出通过与非门后接入D SR 端,S S 1 =10。8分频 器的分频信号由Q 3取非后输出,同时将该信号送入D SR 端,S S 1 =10。 实验五 移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用 — 实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3为并行输入端;Q 0、Q 1、Q 2、Q 3为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端;S 1、S 0 为操作模式控制端; R C 为直接无条件清零端;CP 为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3),左移(方向由Q 3→Q 0),保持及清零。 S 1、S 0和R C 端的控制作用如表10-1。 表10-1 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态 Q 0Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q Q 1 Q 2 Q 3 将依次变为0100→0010→0001 →1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数 实验四典型时序电路的功能测试与综合仿真报告 张智博 一.74LS290构成的24位计数器 方法:第一片74290的Q3与第二片的INB相连,R01,R02相连,INA,R91,R92悬空构成24位计数器。50Hz,5v方波电压源提供时钟信号,用白炽灯显示输出信号。 实验电路: 实验现象: 输出由000000变为000001,000010,000011,000100,001000,001001,001010,001011,001100,010001,010000,010010,010011,010100,011000,011001,011010,011011,011100,100000,100001,100010,100011,100100,最终又回到000000,实现一次进位。 二.74LS161构成的24位计数器 方法:运用多次置零法 用两片74LS161构成了24位计数器,两片计数器的时钟信号都由方波电压源提供,第一片芯片的Q3和第二片芯片的Q0通过与非门,构成两个74LS161的LOAD信号,第一片的CO接第二片的ENT,其他ENT和ENP接Vcc(5v)。输出接白炽灯。 电路图: 实验现象:以下为1—24的计数过程 三.74LS194构成的8位双向移位寄存器 方法:通过两片194级联,控制MA,MB 的值,来控制左右移动 实验电路由两片74LS194芯片构成。两个Ma 接在一起,两个Mb 接在一起,第一片的 Dr,第二片的Dl,分别通过开关接到Vcc(5v)上。第一片的Q3接到第二片的Dr,第二片的Q0接到第一片的Dl。8个输出端分别接白炽灯。 实验电路: 实验现象: 右移: 接通Ma,Dr后,D0到D7全部为0,白炽灯从00000000变为,,,,,,,,实现右移功能。 实验五、移位寄存器的设计 一、实验目的 设计并实现一个异步清零同步置数8位并入并出双向移位寄存器电路。 二、实验原理 在数字电路中,用来存放二进制数据或代码的电路成为寄存器。寄存器按功能可分为:基本寄存器和移位寄存器。移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。下面是一个并入串出的8位左移寄存器的VHDL描述: library ieee; use ieee.std_logic_1164.all; port(data_in: in std_logic_vector(7 downto 0); clk: in std_logic; load: in std_logic; data_out:out std_logic); end; architecture one of left8 is signal q: std_logic_vector(7 downto 0); begin process(load,clk) begin if load='1' then q<=data_in; data_out<='Z'; elsif clk'event and clk='1' then for I in 1 to 7 loop 图5-1 q(i)<=q(i-1); end loop; data_out<=q(7); end if; end process; end one; 异步清零同步置数8位并入并出双向移位寄存器电路结构图如图5-1所示。 三、实验要求 输入信号有D[0]~D[7]、DIL、DIR、S、LOAD、CLK和CLR,其中CLK接时钟,其余接拨码开关,输出信号有Q[0]~Q[7],接发光二极管。改变拨码开关的状态,观察实验结果。 实验工程项目命名为rlshift,源程序命名为rlshift8.vhd。 四、实验记录 对比较器实验结果造表,得到其真值表。 五、实验报告要求 实验七 移位寄存器及其应用 一、实验目的 1. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2. 熟悉移位寄存器的应用——环形计数器。 二、实验原理 1. 移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又有右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图 1所示。 图 1 74LS194的逻辑符号及其引脚排列 其中D 3、D 2、D 1、D 0为并行输入端, Q 3、Q 2、Q 1、Q 0为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端,S 1、S 0为操作模式控制端;CR 为直接无条件清零端;CP 为时钟脉冲输入端。74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q 3→Q 0),左移(方向由Q 0→Q 3),保持及清零。S 1、S 0和CR 端的控制作用如表 1所示。 表 1 2.移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计致器和串行累加器的线路及其原理。 (1) 环形计数器:把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图2所示,把输出端Q 0和右移串行输入端S R 相连接,设初始状态Q 3 Q 2 Q 1 Q =1000, 则在时钟脉冲作用下Q 3Q 2 Q 1 Q 将依次变为0100→0010→0001→1000→……,可见它是具 有四个有效状态的计数器,这种类型的计效器通常称为环形计数器。图2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 实验六 移位寄存器功能测试及应用 --实验报告要求 一. 实验目的(0.5分) 1. 熟悉寄存器、移位寄存器的电路结构和工作原理。 2. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 3. 熟悉移位寄存器的应用。 二. 实验电路 D0、D1 、D2 、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR 为右移串行输入端,SL 为左移串行输入端;S1、S0 为操作模式控制端;R C 为直接无条件清零端;CP 为时钟脉冲输入端。 三 图2 CC40194/74LS194 逻辑功能测试 图1 CC40194/74LS194的逻辑符号及引脚功能 图3 环形计数器 四. 实验原理(0.5分) 1.移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用。 74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。 2.移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环行计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。 (2)实现数据、并行转换器 a)串行∕并行转换器 串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出。 b)并行∕串行转换器 并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。 五. 实验内容与步骤(共1分) 1. 2.测试74LS194的逻辑功能(0.5分) (1)在实验箱上选取一个16P插座,按定位标记插好74LS194集成块。 (2)将实验挂箱上+5V直流电源接40194的16脚,地接8脚。S1、S0、SL、SR、D0、D1、D2、D3分别接至逻辑电平开关的输出插口;Q0、Q1、Q2、Q3接至发光二极管。CP端接单次脉冲源。 (3)改变不同的输入状态,逐个送入单次脉冲,观察寄存器输出状态,记录之。 a)清除:令=0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。清除后,至=1。 b)送数:令=S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=1010,加CP脉冲,观察CP=0、CP由1→0、CP=1三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。 (c)右移:清零后,令=1, S1=0 S0=1,由右移输入端S R送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。 (d)左移:先清零或予至,再令=1 S1=1,S0=0,由左移输入端S L送入二进制数码 实验六移位寄存器 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图9—1所示。 图9—1 CC40194的逻辑符号及引脚功能 其中D0、D1、D2、D3为并行输入端; Q0、Q1、Q2、Q3为并行输出端;SR为右移串行输入端,SL为左移串行输入端;S1、S0为操作模式控制端;C R为直接 无条件清零端;CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0~Q3),左移(方向由Q3~Q0),保持及清零。 S1、S0和C R端的控制作用如表9—l。 表9—l 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。(1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图9—2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表9—2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图9—2电路可以由各个输出端输出在时间上有先后顺序的脉冲。因此也可作为顺序脉冲发生器。 图9—2环形计数器表9—2 如果将输出作与左移串行输入临,相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。图9—3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位申/并行数据转换电路。 图9—3 七位串行/并行转换器 电路中S0端接高电平1,S1受Q7控制,二片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式,当Q7=0时,S1=1, S1S0=10则串行送数结束,标志着串行输入的数据已转换成并行输出了。’ 串行/并行转换的具体过程如下: 转换前,C R端加低电平,使1、2两片寄存器的内容清0,此时S1 S0=11, 实验八移位寄存器功能测试及应用 一、实验目的: 1.掌握中规模4位双向寄存器逻辑功能及使用方法。 2.熟悉移位寄存器的应用,实现数据的串行、并行转换和构成环形计数器 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS194一片。 三、预习要求及思考题 1.预习要求: 1) 复习有关寄存器有关内容。 2)熟悉74LS194逻辑功能及引脚排列。 3)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题: 1) 使寄存器清零,除采用输入低电平外,可否采用右移或左移的方法?可否使用 并行送数法?若可行,如何进行操作? 2) 环行计数器的最大优点和缺点是什么? 四、实验原理 1.位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相 同,可互换使用,其逻辑符号及引脚图如图8-1所示。 图8-1 74LS194的逻辑符号图及引脚功能图. 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端;S L为左移串行输入端;S0、S1为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和C R端的控制作用如表8-1 7.3.3移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用——实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表7-29所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图7-52 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 表 图 7-52 环形计数器 (2)实现数据串、并行转换 第一串行/并行转换器串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。图10-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。电路中S0端接高电平1,S1受Q7控制,二片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式,当Q7=0时,S1=1,有S1S0=10,则串行送数结束,标志着串行输入的数据已 图10-3 七位串行 / 并行转换器 串行/并行转换的具体过程如下: 转换前,R C端加低电平,使1、2两片寄存器的内容清0,此时S1S0=11,寄存器执行并行输入工作方式。当第一个CP脉冲到来后,寄存器的输出状态Q0~Q7为01111111,与此同时S1S0变为01,转换电路变为执行串入右移工作方式,串行输入数据由1片的S R端加入。随着CP 脉冲的依次加入,输出状态的变化可列成表10-3所示。 表10-3 由表10-3可见,右移操作七次之后,Q7变为0,S1S0又变为11,说明串行输入结束。这时,串行输入的数码已经转换成了并行输出了。 当再来一个CP脉冲时,电路又重新执行一次并行输入,为第二组串行数码转换作好了准备。 第二,并行/串行转换器,并行/串行转换器是指并行输入的数码经转换电路之后,换成串行输出。图10-4是用两片CC40194(74LS194)组成的七位并行/串行转换电路,它比图10-3多了两只与非门G1和G2,电路工作方式同样为右移。移位寄存器及其应用(精)

8位移位寄存器的电路设计与版图实现

移位寄存器 第三章答案

EDA课程设计——移位寄存器的设计与实现

实验五移位寄存器及其应用

数字电路实验6移位寄存器的应用

实验十七、移位寄存器74164的逻辑功能测 试

(整理)实验-寄存器.

74LS194左右移位寄存器

实验五移位寄存器及其应用共10页文档

计数器和移位寄存器设计仿真实验报告

实验五 移位寄存器

实验七 移位寄存器及其应用

最新实验6-移位寄存器功能测试及应用-(实验报告要求)

电子线路基础数字电路实验6 移位寄存器

移位寄存器功能测试及应用

7.3.3移位寄存器及其应用