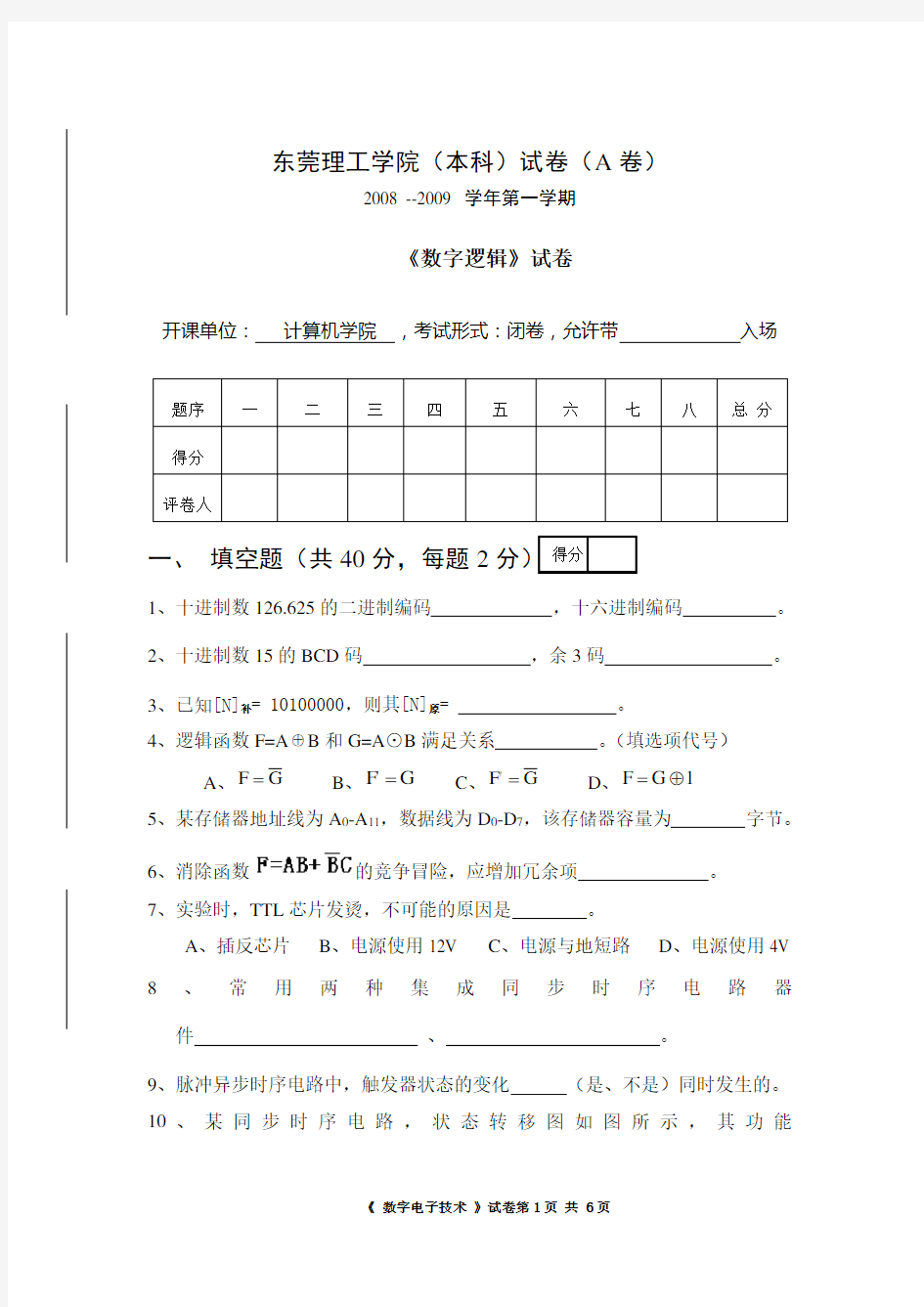

东莞理工学院(本科)试卷(A 卷)

2008 --2009 学年第一学期

《数字逻辑》试卷

开课单位: 计算机学院 ,考试形式:闭卷,允许带 入场

题序 一 二 三 四 五 六 七 八 总 分 得分 评卷人

一、 填空题(共40分,每题2

分) 1、十进制数126.625的二进制编码 ,十六进制编码 。 2、十进制数15的BCD 码 ,余3码 。 3、已知[N]补= 10100000,则其[N]原= 。

4、逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 。(填选项代号)

A 、G F =

B 、G F ='

C 、G F ='

D 、1G F ⊕=

5、某存储器地址线为A 0-A 11,数据线为D 0-D 7,该存储器容量为 字节。

6、消除函数

的竞争冒险,应增加冗余项 。

7、实验时,TTL 芯片发烫,不可能的原因是 。

A 、插反芯片

B 、电源使用12V

C 、电源与地短路

D 、电源使用4V 8

、

常

用

两

种

集

成

同

步

时

序

电

路

器

件 、 。

9、脉冲异步时序电路中,触发器状态的变化 (是、不是)同时发生的。 10、某同步时序电路,状态转移图如图所示,其功能

得分

是。

11、555定时器的功能有、、。

12、超前进位加法器与串行进位加法器相比,速度。

13、8位ADC输入满量程为10V,当输入5V电压值,数字输出量为。

14、芯片74LS32如下图所示,内含个输入端的门。

15、若要某共阴极数码管显示数字“5”,则显示代码abcdefg为。(0000000~1111111)

16、与TTL门电路相比,CMOS门电路功耗(大、小),速度(快、慢)。

17、电可擦可编程存储器是。 A.ROM B.PROM C.EPROM D.EEPROM

18、在下列电路中不是组合逻辑电路的是。

A、译码器

B、编码器

C、全加器

D、寄存器

19、触发器按结构可分为基本触发器、触发器、触

发器、触发器等。

20、与普通门电路不同,OC门在工作时需要外接和。

二、逻辑函数简化(共14分)得分

1、用代数法化简逻辑函数。

(4分)

(4分)

2、用卡诺图法简化逻辑函数。(要求画出卡诺图)(6分)

三、逻辑电路图分析(共20分)得分

1、写出F 的表达式,不需简化。(4分)

F=

2、写出F 表达式,不需简化。(4分)

3、写出C 表达式,不需简化。(4分)

F= C=

3、已知74LS161下面电路的功能如表中所示:(4分)

……………………

芯片74LS161的CO端是进位输出端,74LS161是

进制计数器,此电路

是进制计数器。

4、已知边沿JK触发器各输入端的电压波形如下,设触发器的初态为0,试画出

输出Q端对应的电压波形。(4分)

四、逻辑电路设计(共26分,每题13

1、某系二年级有四个班,该系有大、中、小三个会议室。如果全年级开会,大

得分

会议室开门,如果有两个或三个班开会,中会议室开门,如果只有一个班开会小会议室开门,没有会议三个会议室关闭。试设计产生三个会议室开门控制信号的电路,要求列出真值表,简化逻辑函数,画出电路图(提供反变量)。

2、用JK触发器设计一个“001”序列检测器,要求作出状态转换图,进行状态简化,作出最小化状态表,进行状态分配,写出输出函数表达式。

分配相邻代码的规则:(1)次态相同的现态(优先)。(2)同一现态的次态。

(3)相同输出的现态。(4)次态次数最多的分配逻辑0。

东莞理工学院(本科)试卷(A卷)参考答案

2008 --2009 学年第一学期

《数字逻辑》试卷参考答案

开课单位:计算机学院,考试形式:闭卷,允许带入场

一、填空题(每题2分,共40分)

1、1111110.101,7E.5

2、00010101,01001000

3、11100000

4、A

5、212

6、AC

7、D 8、寄存器计数器

9、不是10、具有自启动功能的五进制加法计数器

11、史密特触发器单稳态触发器多谐振荡器12、更快

13、10000000 14、4 2 或

15、1011011 16、小,慢

17、D 18、D

19、钟控、主从、边沿20、上拉电阻电源

二、逻辑函数简化(共14分)

1、

2、

三、逻辑电路图分析(共20分)

1、

2、

3、1611

4、

四、逻辑电路设计(共26分)

1、设四个班级分别为A、B、C、D,大、中、小会议室开门控制信号分别为:X,Y,Z

X=ABCD

Y=AB+AC+AD+BC+BD+CD

电路图不唯一,答案略去。

2、X为输入,Z为输出。,

由于状态分配不唯一,下面步骤的解答也非唯一,故省略答案。

东莞理工学院本科试卷(A卷)

2011 --2012 学年第2 学期

《数字电子技术》试卷及评分标准

开课单位:电子工程学院考试形式:闭卷

题序一二三四五六七八总分得分

评卷

人

一、填空题(共20分每题2分)

1. (213.8125)

10=(11010101.1101)

2

2. Y=A’+BC 的对偶式为 Y D=A’(B+C)

3.F=ABC’+AB’C+A’B+B+BC 的最简与或式是 F=AC+B

4. 在进行D/A转换时,必须将取样电压表示为最小数量单位的整数倍,这个转换过程称为量化,这个最小数量单位就是数字信号最低有效位的1所代表的数量大小。

5.下图用74160整体(异步)置零

接成的计数器是49进制计数器.

6.格雷码最基本的特性是任何相

邻的两组代码中,仅有一位数码不

同。

7.电平触发的触发器在触发脉

冲作用期间,输入信号发生多次

变化时,触发器输出状态会相应地发生多次变化。

8. CP下降沿时刻翻转的主从触发器,在CP=0期间,主触发器保持 CP 下降沿之前状态不变,而从触发器接受主触发器状态。

9.优先编码器允许同时输入两个以上的编码信号,但只对其中优先权最高的一个进行编码。

10. L(A,B,C,D)=∑m(1,4,5,6,7,9)+∑d(10,11,12,13,14,15)最简与或式为L=B+C’D

二、判断题(共10分每题2分)

1.不可重复触发单稳态触发器一旦被触发进入暂稳态以后,再加入触发脉冲也不会影响电路的工作过程,输出的暂稳态时间不变,必须在暂稳态结束以后,它才可能接受下一个触发脉冲而转入暂稳态。

2.CMOS电路的OD门、CMOS电路的三态输出门、具有互补结构的CMOS门,均能将

输出端并联使用。

3.施密特触发器属于电平触发的双稳态电路,它能把变化非常缓慢的输入波形整形成数字电路所需要的矩形脉冲。

4.凡是采用2个电平触发D触发器结构、维持阻塞结构、门电路传输延时时间结构组成的触发器,无论其逻辑功能如何,一定是边沿触发方式。

5.边沿触发的触发器的次态仅取决于CLK的下降沿(或上升沿)到来时的输入信号状态,与在此前、后输入的状态没有关系。

答: 1(√) 2(×) 3(√)4(√)5(√)

三、选择题(共15分每题3分)

1. A/D转换器量化只舍不入的方法产生的最大量化误差为 1 个最小量化单位,有舍有入的方法产生的最大量化误差为 0.5 个最小量化单位。

A. 1,0.5

B. 2,1

C. 0.5,1

D. 1,2

2.如图单稳电路v O输出脉冲宽度等于v I2从0充电

至v TH 的时间。对输入信号脉宽无限制。

A. v DD,无限制

B. v TH,要求大于电路暂稳态维持的时间。

C. v TH,无限制

D. v DD,要求大于电路暂稳态维持的时间。

3.如图由2片74HC148接成的16-4线

优先编码器,若A’10 =A’6 =A’2 =0,

其它编码输入端为1,则输出端

Z 3Z

2

Z

1

Z

为。

A. 1010

B. 0101

C. 0110

D. 0000

4.能起定时作用的电路是单稳态电

路。

A. 施密特触发器 B 单稳态电路

C 多谐振荡器 D. 译码器

5.要求JK触发器状态由0变1,其激励

输入端JK应为(1ⅹ)。

A.0ⅹ

B. 1ⅹ

C. ⅹ0

D. ⅹ1

答: 1( A ) 2( C ) 3( A ) 4( B ) 5( B )

四、分析与设计题(4小题,共55分)

1. 设计一个有三个输入、一个输出的组合逻辑电路,输入为二进制数。当输入

二进制数能被3整除(即余数为0)时,输出为1,否则,输出为0,写出最简单与或逻辑表达式,用74LS138译码器实现逻辑功能,画出电路图。(12分)

解:设输入变量为A 、B 、C,输出变量为Z 。根据逻辑功能要求,列出的电路的真值表,得到输出Z 的表达式:

'''''ABC BC A C B A F ++= (5分) Z=m 0+m 3+m 6=(m 0’m 3’m 6’)’ (3分)

电

路图(4分)

2. TTL 边沿触发器组成的电路和其输入波形见图,写出状态方程,试画出Q 端的波形,设电路初态均为0。 (12分)

解: 从图中可见,FF 为上升沿触发。

B A K B A J ⊕=⊕=',

B

A BQ A Q

B A Q K JQ Q n ⊕=⊕+?⊕=+=+222212'')(''

(5分)

波形图(7分)

3. 分析下图,要求写出输出方程、激励方程、状态方程,画出状态图,说明实

A B C Z 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

1 0 0 1 0 0 1 0

现的逻辑功能。(21分)

1J

C1

1K

1J

C1

1K

FF1FF0

CP

=1

X

&

Z

Q1

Q1Q0

Q0

解:①先求输出方程和激励方程

'

'

1

1

1

1

Q

XQ

Z

Q

X

K

J

K

J

=

⊕

=

=

=

=

(4分)

②求状态方程

(4分)

③画状态图(7分)

④逻辑功能分析。该电路是一个同步模4可逆计数器。X为加/减控制信号,X=0为加法,X=1为减法,Z为借位输出. (6分)

4.试对下图进行线路连接,使555构成多谐触发器,若R1=20KΩ,R2=80KΩ,C=0.1Μf,求振荡周期和占空比。(10分)

解:T=0.7(R

1

+ R

2

)C+0.7 R

2

C=12.6ms

(5分)

其线路连接见图(5分)

%

5.

55

160

20

80

20

2

2

1

2

1=

+

+

=

+

+

=

R

R

R

R

q

0001

10

11Q1Q0

1/0

1/0

1/11/00/0

0/0

X/Z

0/0

'

'

'

'

'

1

1

1

1

1

1

1

1

Q

Q

K

Q

J

Q

Q

Q

X

Q

K

Q

J

Q

n

n

=

+

=

⊕

⊕

=

+

=

+

+

试卷(A 卷)2009 --2010 学年第一学期《 数字电子技术

一、填空、选择(共20分,1~4小题 每空1 分,5~6小题 每空2 1.

2. 3. 用8位二进制代码(最高位表示正负,其余7位表示数值)表示下列

带符号的数:

(+24)10 原码 00011000 、反码 00011000 、补码 00011000 。 (-24)10 原码 10011000 、反码 11100111 、补码 11101000 。 4.常见的A/D 转换器有逐次逼近型和双积分型等。如果设计一个便携式仪表中使用的A/D ,应选择其中的那种类型?用在速度要求较高的工业现场控制中,应选择其中那种类型?

便携式仪表选 双积分型 ,工业现场控制选 逐次逼近型 5.74LS00是TTL 电路,CD4011是CMOS 电路,以下说法正确的是: D 。 A. 74LS00只能使用+5V 电源电压,CD4011只能使用+10V 电源电压; B. 74LS00、CD4011都只能使用+5V 电源电压;

C. CD4011只能使用+5V 电源电压,74LS00则不一定;

D. 74LS00只能使用+5V 电源电压,CD4011则不一定。

6.已知逻辑函数

根据反演规则,其反函数为

根据对偶规则,其对偶函数为

CD C B A Y(A,B,C,D)++=)(16

8102).()7.13()875.11()111.1011(E B ===码

余码38421210)10100101()01110010()11011()27(===BCD )

()(D C C B A Y ++=)

()(D C BC A Y D ++=

B A

C B

D C

A B A C B D BC A C A B A C B D D BC A C A B A C B D D BC A C A B A C B E B A C D DE B A D BC A D C A B A C B CD DE B A D BC A C B D C A B A C B CD DE

B A D B

C A C B

D C A B A C B CD Y ++++++++++++++++++++++++++++++++++++++========解:)1()()(二、用公式法化化简下列逻辑函数为最简“与或”表达式。 (共10分)

(注:能正确化简,但答案不是最简,得分减半)

三、试用一片74HC138(3-8译码器)和一片74LS20(2个四输入与非门)构建一个“一位二进制全减器”。 (共10分)

要求:1. 列出真值表2. 写出逻辑表达式3. 画出电路图。 解:真值表如

DE

B A D B

C A C B

D A C B A C B CD Y +++++++=)(ABC

C B A C B A C B A S +++=ABC

A C

B A J ++=2分

1

00

A B C

J

S

1分

四、设计一个“4输入、1输出”的组合逻辑电路,完成“大小月份”判别。设输入信号为与“1~12”相对应的4位二进制数,要求大月时输出为1,小月输出0(二月也算小月)。 要求:1. 填写真值表

2.利用卡诺图化简,并尽可能利用无关项,使其最简。

3.限用2输入端的“与非门” (禁用其它类型的逻辑门)实现之。

(共15分)

解:1. 填写真值表如下,其中四项为无关项。

2

3.

姓名: 学号: 系别: 年级专业:

( 密 封 线 内 不 答 题 ) ………………………………………密………………………………………………封………………………………………线……………………………………………………

D A D A D A D A D A D A Y =+=+=D A D A Y +=∴D

A (真值表4分)

(卡诺图化简2分,每圈1分) (表达式2分) (电路图5分,可有多种答案) (使用了其它类型的门,得2分)

五、分析图示计数器 (共15分) 1.写出驱动方程和状态方程;

2.填写状态转换表,画出状态转换图;

3.完整的说明计数器类型,并说明能否自启动; 4.设计数器初始状态为“0、0”, 画出其计数波形。

解:1. (3分)

(3分)

2. 状态转换表如右,状态转换图如下

(转换图循环内1分) (循环外1分)

3. 计数器类型:同步、六进制,能自启动。(3分,三项内容各1分) 4.计数波形如下。(2分)

?????==n n

n Q K Q Q J 202

10?????==n n Q K Q J 1

313

??

???==n

n

Q K Q J 0101n n n n

n n Q Q Q Q Q Q 0

010111=+=+n n n n n n n n n n Q Q Q Q Q Q Q Q Q Q 1

2020201210+=+=+n n n n n n Q Q Q Q Q Q 1

121212=+=+Q 01

2

Q Q (转换表1分)

(触发沿错,分减半) (最后沿错,分减半) 2

八、已知某信号发生器的电路框图如下,其输出信号的波形为倒阶梯波(如左下图)。试仿照此方法,用框图的形式设计一个能输出正阶梯波(如右下图)的信号发生器电路。

若要求输出信号的频率为1KHz ,C=1uF ,则R F 应如何取值?(共 10 分)

倒阶梯波 正阶梯波

(6分)

(4分)

Ω75113881010

1101422142213

3

6....====-x x x x x xCf x R F

期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班 姓名 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 得分 评卷人 装 订 线 内 请 勿 答 题

6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 D C B A F+ + + =B.D C B A F+ + + = D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为 _____D_____。 A.500KHz B.200KHz C.100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 装

中国石油大学(北京)远程教育学院 《数字逻辑》期末复习题 一、单项选择题 1. TTL 门电路输入端悬空时,应视为( A ) A. 高电平 B. 低电平 C. 不定 D. 高阻 2. 最小项D C B A 的逻辑相邻项是( D ) A .ABCD B .D B C A C .C D AB D .BCD A 3. 全加器中向高位的进位1+i C 为( D ) A. i i i C B A ⊕⊕ B.i i i i i C B A B A )(⊕+ C.i i i C B A ++ D.i i i B C A )(⊕ 4. 一片十六选一数据选择器,它应有( A )位地址输入变量 A. 4 B. 5 C. 10 D. 16 5. 欲对78个信息以二进制代码表示,则最少需要( B )位二进制码 A. 4 B. 7 C. 78 D. 10 6. 十进制数25用8421BCD 码表示为(B ) A.10 101 B.0010 0101 C.100101 D.10101 7. 常用的BCD 码有(C ) A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码 8. 已知Y A AB AB =++,下列结果中正确的是(C ) A:Y=A B:Y=B C:Y=A+B D: Y A B =+ 9. 下列说法不正确的是( D ) A:同一个逻辑函数的不同描述方法之间可相互转换 B:任何一个逻辑函数都可以化成最小项之和的标准形式 C:具有逻辑相邻性的两个最小项都可以合并为一项 D:任一逻辑函数的最简与或式形式是唯一的 10. 逻辑函数的真值表如下表所示,其最简与或式是(C )

A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC + 11.以下不是逻辑代数重要规则的是( D ) 。 A. 代入规则 B. 反演规则 C. 对偶规则 D. 加法规则 12.已知函数E)D (C B A F +?+=的反函数应该是( A ) 。 A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?= D. [] )E D (C B A F +?+?= 13.组合逻辑电路一般由( A )组合而成。 A 、门电路 B 、触发器 C 、计数器 D 、寄存器 14.求一个逻辑函数F 的对偶式,可将F 中的( A )。 A 、“·”换成“+”,“+”换成“·”,常数中的“0”“1”互换 B 、原变量换成反变量,反变量换成原变量 C 、变量不变 D 、常数中的“0”换成“1”,“1”换成“0” 15.逻辑函数()()()()=++++=E A D A C A B A F ( A ) 。 A. AB+AC+AD+AE B. A+BCED C. (A+BC)(A+DE) D. A+B+C+D+E 16.下列逻辑电路中,不是组合逻辑电路的有( D ) A 、译码器 B 、编码器 C 、全加器 D 、寄存器 17.逻辑表达式A+BC=( C )

数字电路与逻辑设计期末考试样题 一、TO FILL YOUR ANSWERS IN THE “( )”(1’ X 5) 1. An unused CMOS NAND gate input should be tied to logic ( ) or another input. 2. DAC can proportionally convert ( ) input to analog signal output. 512 3. A truth table for a ( ) input, 4-output combinational logic function could be stored in a 4 EPROM. 4. The RCO output of 74X163 is asserted if and only if the enable signal ( )is asserted and the counter is in state …1111?. 5. If the signed-magnitude representation is(001101)2 for one number, then it?s 8-bit two?s complement representation is()2. 二、Single selection problems: there is only one correct answer in the following questions.(2’ X 5) 1、An 8-output demultiplexer has ( ) select inputs. A. 2 B. 3 C. 4 D. 5 2、For a logical function ,which representation as follows is one and only(唯一). ( ) A. logic expression B. logic diagram C. truth table D. timing diagram 3、In general, to complete the same function, compared to a MOORE machine, the MEAL Y machine has ()。 A. more states B. fewer states C. more flip-flops D. fewer flip-flops 4、To design a “1000001” serial sequence generator by shift registers, at least needs a ( ) bit shift register. A. 2 B. 3 C. 4 D.5 5、The following logic expressions is equal, and the hazard-free one is ( ). A. F=B?C?+AC+A?B B. F=A?C?+BC+AB? C. F=A?C?+BC+AB?+A?B D. F=B?C?+AC+A?B+BC+AB?+A?C?

北京XX 大学2006——2007学年第一学期 《数字逻辑与数字系统》期末考试试题(A ) 一、选择题(每小题1分,共10分。) .卡诺图如图1所示,电路描述的逻辑表达式F=( )。 A. ∑m(1,2,4,5,9,10,13,15) B. ∑m(0,1,3,4,5,9,13,15) C. ∑m(1,2,3,4,5,8,9,14) D. ∑m(1,4,5,8,9,10,13,15) .在下列逻辑部件中,不属于组合逻辑部件的是( )。 A. 译码器 B. 锁存器 C.编码器 D.比较器 .八路数据选择器,其地址输入端(选择控制端)有( )个。 A. 8 B. 2 C. 3 D. 4 .将D 触发器转换为T 触发器,图2所示电路的虚框 )。 A. 或非门 B. 与非门 C. 异或门 D. 同或门 图2

A. 2n B. 2n C. n D. 2n-1 6.GAL 是指( )。 A.随机读写存储器 B.通用阵列逻辑 C.可编程逻辑阵列 D. 现场可编程门阵列 7.EPROM 的与阵列( ),或阵列( )。 A. 固定、固定 B. 可编程、固定 C. 固定、可编程 D. 可编程、可编程 8.在ispLSI 器件中,GRP 是指( )。 A. 通用逻辑块 B. 输出布线区 C. 输入输出单元 D.全局布线区 9. 双向数据总线可以采用( )构成。 A.三态门 B. 译码器 C.多路选择器 D.与非门 10.ASM 流程图是设计( )的一种重要工具。 A. 运算器 B. 控制器 C.计数器 D. 存储器 二、填空题(每小题2分,共20分) 1. 图3所示加法器构成代码变换电路,若输入信号B 3B 2B 1B 0为8421BCD 码,则输出端 S 3S 2S 1S 0为______________________代码。 2. 2:4译码器芯片如图4所示。欲将其改为四路分配器使用,应将使能端G 改为 ___________________,而地址输入端A 、B 作为_________________________。 3. 门电路的输入、输出高电平赋值为逻辑_________,低电平赋值为逻辑________,这种关系为负逻辑关系。 4. 组合逻辑电路的输出只与当时的________状态有关,而与电路_______的输入状态无关。 5.译码器实现___________________译码,编码器实现___________________译码。

- - 优质资料 期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷考试时间:110 分钟 XXXX 学院 ______________系级班 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F =B . C AB F += C .C A AB F += D .C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D .BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 得分 评卷人 装 订 线 内 请 勿 答 题

- 优 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 6. 与逻辑函数D C B A F +++=功能相等的表达式为___C_____。 A .D C B A F +++=D C B A F +++= .D C B A F ++= 7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。 A . 500KHz B .200KHz

期末考试试题(答案) 一、选择题(每小题2分,共20分) 1.八进制(273)8中,它的第三位数2 的位权为___B___。 A.(128)10B.(64)10C.(256)10 D.(8)10 2. 已知逻辑表达式C B C A AB F+ + =,与它功能相等的函数表达式 _____B____。 A.AB F=B.C AB F+ = C.C A AB F+ =D.C B AB F+ = 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。 A.与关系B.异或关系C.同或关系D.无法判断 5.连续异或1985个1的结果是____B_____。 A.0B.1 C.不确定D.逻辑概念错误 6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 A.D C B A F+ + + =B.D C B A F+ + + = C.D C B A F=D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 B A F & ? F B A &

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。 A. 500KHz B.200KHz C. 100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。 A. 0100100 B.1100011 C. 1011011 D.0011011 二、填空题(每小题2分,共20分) 11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。 12.N 个输入端的二进制译码器,共有___N2____个输出端。对于每一组输入代码,有____1____个输出端是有效电平。 13.给36个字符编码,至少需要____6______位二进制数。 14.存储12位二进制信息需要___12____个触发器。

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级姓名班内序号 题号一二三四五六七八总成绩 分数20 12 10 10 10 20 10 8 得分 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。) 1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳ ) 3.若对4位二进制码(B 3B 2 B 1 B )进行奇校验编码,则校验位C= B 3 ⊕B 2 ⊕B 1 ⊕B ⊕1。 (√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0i j m m =。(╳) 7. CMOS 门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。( √ ) 10.格雷BCD 码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) 11.关于函数F A C BCD AB C =++g ,下列说法中正确的有 B 。 A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD 和ACD 进行消除; C. 存在静态功能冒险,需要加冗余项ABD 和ACD 进行消除; D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G = B.0F G += C.1F G =g D.0F G =e 13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则 =?G F A 。 A.32m m + B.1 C.AB D.AB 14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。 A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。 B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。 C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。 D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。 A. 三态输出的门电路。; B. 漏极开路的CMOS 门电路; C. ECL 门电路; D. CMOS 传输门

《数字逻辑》期末考试 A 卷参考答案 、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分) 1、为了表示104个信息,需7位二进制编码[V ] 2、BCD码能表示0至15之间的任意整数[X ] 3、余3码是有权码[X ] 4、2421码是无权码[X ] 5、二值数字逻辑中变量只能取值 6、计算机主机与鼠标是并行通信 7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ] [X ] [V ] [V ] 9、上升时间和下降时间越长,器件速度越慢[V ] 10、卡诺图可用来化简任意个变量的逻辑表达式[X ] 、写出图中电路的逻辑函数表达式。(每小题5分,共10分) 1、F=A B 2、F= AB CD 2分,共20分)

1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A ° TTL 电路 (A) F = ABCD (B) F = AH ? CD - (C) F= A + B + C + D (D) F = A + B ? C + D (E) F= A BCD 4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _° (A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q. (D) BC= 1 , D= 1 5、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。 (A) AB + AC + BC (B) AB + C (A4-B) (C) AB + CAB A — O ? =1 1 Q A |— I 1 F ?- & 1 Q A B L I l — (B) 悬0 ---- 空 。— A — & Bo — Co- & B A 3 ?满足如图所示电路的输岀函数F 的表达式为丄3 B 1 o — V OF

09年数字逻辑期末试卷(A卷)试题及答案

华东师范大学期末试卷(A ) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑______ 学生姓名:___________________ 学 号:___________________ 专 业:___________________ 年级/班级:__________________ 课程性质:公共必修、公共选修、专业必修、专业选修 ………………………………………………………………………………………… 一、填空题 (20分,每空2分) 1. (34.5)10 = ( (1) 11 0100.0101 )8421BCD = ( (2) 100010.1 )2 = ( (3) 2 2.8 )16 。 2. ()Y A B C CD =++的对偶式为___(4)Y ’A C B C A D ''''''=++ 。 3. 在数字系统中,要实现线与功能可选用___(5)OC/OD 门;要实现总线结构可选用___(6)传输 门。 4. 化简F (A,B,C,D )=∑m(3,5,6,7,10)+d (0,1,2,4,8)可得 (7) F =A ’+B ’D ’ 。 5. 已知某左移寄存器,现态为011001,若空位补0,则次态为 (8)110010 。 6. 二进制数(- 10110)2的反码和补码分别为 (9)101001 和 (10)101010 。

二、选择题(20分,每题2分) 1.在下列逻辑部件中.不属于组合逻辑部件的是 D 。 A.译码器 B.编码器 C.全加器 D.寄存器 2.逻辑表达式A+BC = B 。 A.A+C B.(A+B)(A+ C) C.A+B+ABC D.B+C 3.能得出X=Y的是 C A.X+Z=Y+Z B.XZ=YZ C. X+Z=Y+Z且XZ=YZ D.以上都不能 4.为将D触发器转换为T触发器,图中所示电路的虚框内应是 _ A_。 A.同或门B.异或门 C.与非 门D.或非门 5.设A1、A2、A3为三个信号,则逻辑函数 C 能检测出这三个信号中 是否含有奇数个高电平。 A.A1A2A3 B.A1+A2+A3 C.A1⊕A2⊕A3 D.A1+A2A3 6.以下说法正确的是 C A.TTL门电路和CMOS门电路的输入端都可以悬空

华东师范大学期末试卷(B) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑________ 学生姓名:___秦宽________________ 学 号:_2013041046__________________ 专 业:____软件工程_______ 年级/班级:13级软件工程 课程性质:公共必修、公共选修、专业必修、专业选修 一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7) 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 答案:'D A + 4. 从结构上看,时序逻辑电路的基本单元是 。 答案:触发器 5. JK 触发器特征方程为 。 答案:Q K JQ ''+ 6.A/D 转换的一般步骤为:取样,保持, ,编码。 答案:量化

二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 B C

北京邮电大学2008——2009学年第一学期 《数字逻辑与数字系统》期末考试试题(A ) 考试注意事项 一、学生参加考试须带学生证或学院证明,未带者不准进入考场。学生必须按照监考教师指定座位就坐。 二、书本、参考资料、书包等物品一律放到考场指定位置。 三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。 四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。 五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。 考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分 满分 10 20 10 10 10 12 14 14 得分 阅卷 教师 一、选择题(每小题1分,共10分。) 1. )D C B (B )B A (A F ++++==( ) A . B B . A+B C . 1 D .AB 2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。 A .( 10000011)2 B .(10100100)2 C . (1010011)2 D . (11001011)2 4. 74LS85为四位二进制数据比较器。如果只进行4位数据比较,那么三个级联输入端ab 、a=b 应为( )。 A . ab 接地,a=b 接地 B . ab 接高电平,a=b 接高电平 C . ab 接高电平,a=b 接地

西 安 金 戈 技 术 学 校 2008年秋季学期期末考试数字逻辑电路试卷 注意事项 1. 考试时间:120 分钟。 2. 本卷依据2005年颁布的《技工类院校考试要求》命制。 3. 请首先按要求在试卷的规定位置填写您的姓名、准考证号和所在班级。 4. 请仔细阅读各种题目的回答要求,在规定的位置填写您的答案。 5. 不要在试卷上乱写乱画,不要在试卷上填写无关的内容。 一. 判断: 1.数字电路抗干扰能力强的原因是只传递1和0的数字信息.. ( ) 2.BCD 码就是8421BCD 码. ( ) 3.卡诺图是真值表示的另一种形式,具有唯一性. ( ) 4.二极管可组成与门电路,但不能组成或门电路. ( ) 5.三极管非门电路中的三极管主要工作在放大状态. ( ) 6.组合逻辑电路中有具有记忆功能的逻辑部件. ( ) 7.译码是编码的逆过程. ( ) 8.触发器也称为半导体存贮单元. ( ) 9.同步触发器存在空翻现象,而边沿型触发器和主从型触发器克服了空翻. 10.JK 触发器的JK 端相当KS 触发器的SR 端. ( ) 二.选择: 1.若编码器编码输出位数为4位,则最多可对( )个输入信号编码. A.4 B.6 C.16 D.32 2.16选1数据选择器其地址输入至少应有( )位. A.2 B.4 C.8 D.16 3.半加器有( ),全加器有( ) A.2个输入端,2个输出端 B.2个输入端,3个输出端 C.3个输入端,2个输出端 D.3个输入端,3个输出端 4.二极管可组成的电路( ) A.只能是与门 B.只能是或门 C.与门和或门都可以 D.非门 5.通常能实现“线与”功能的门电路是( ) A.OC 门 BTSL.门 C.TTL 与门 6.BCD 码是( ) A.二进制码 B.十进制码 C.二一十进制码 7.下列逻辑函数表示方法中,具有唯一性的是(多选)( ) A.真值表 B.逻辑表达式 C.逻辑图 D.卡诺图 8.下列选项中不属于卡诺图特点的是( ) … … ……… ……考……………生… ……… …答……………题……………不……………准……………超……………过……………此……………线…………………

数字逻辑考试题 数字逻辑考试题(一) 一、填空(共17分,每空1分) 1. (1011.11)B =( ) D =( )H 2. (16)D =( )8421BCD 码。 3. 三态门的输出有 、 、 三种状态。 6. ABC C B A Y =),,( 的最简式为Y= 。 7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。 10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。 11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。 12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。 13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。 二、选择(共10分,每题1分) 1. DE BC A Y +=的反函数为Y =( )。 A. E D C B A Y +++?= B. E D C B A Y +++?= C. )(E D C B A Y +++?= D. )(E D C B A Y +++?= 3. 十进制数25用8421BCD 码表示为( )。 A. 10101 B. 0010 0101 C. 100101 D. 10101 4. 若用1表示高电平,0表示低电平,则是( )。 A. 正逻辑 B. 负逻辑 C. 正、负逻辑 D. 任意逻辑 5. 下逻辑图的逻辑表达式为( )。 A. AC BC AB Y = B. BC AC AB Y ++= C. BC AC AB Y ++= D. BC AC AB Y = 6. 三态门的逻辑值正确是指它有( )。 A. 1个 B. 2个 C. 3个 D. 4个 9. 组合逻辑电路在电路结构上的特点下列不正确的是( )。 A. 在结构上只能由各种门电路组成 B. 电路中不包含记忆(存储)元件 C. 有输入到输出的通路 D. 有输出到输入的反馈回路 10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输 出07~Y Y 为( )。 A. 11111101 B. 10111111 C. 11110111 D. 11111111 三 、简答题(共15分,每题5分)

一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 4. 从结构上看,时序逻辑电路的基本单元是 。 5. JK 触发器特征方程为 。 二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 +U CC +U CC -U BB R R K R C R B A B C F

5. 在下列逻辑部件中,属于组合逻辑电路的是()。 A) 计数器B) 数据选择器C) 寄存器D) 触发器 6. 已知某触发器的时钟CP,异步置0端为R D,异步置1端为S D,控制输入端V i和输出Q的波形如图2所示,根据波形可判断这个触发器是()。 图2 A) 上升沿D触发器B) 下降沿D触发器 C) 下降沿T触发器D) 上升沿T触发器 7. 寄存器要存放n位二进制数码时,需要( )个触发器。 A) n B) n log C) n2D) n/2 2 8. 下面哪种不是施密特触发器的应用:( ) A) 稳定频率脉冲输出B) 波形变换C) 脉冲整形D) 脉冲鉴幅 9. 下列哪个不能用555电路构成:( ) A)施密特触发器B)单稳态触发器C)多谐振荡器D)晶体振荡器 三、简答题(15分) 1.用公式法化简逻辑函数:Y=A'BC +(A+B')C (7分)

2018~2019 数字逻辑设计期末考题 回忆 by liuxilai && 18~19年选课同学 一、简答题(6×5=30分) 1、非确定组合逻辑优化中的蕴含项、质蕴含项和实质蕴含项 2、简述SR、D、JK、D触发器的功能 3、建立时间(setup time)和保持时间的概念,并说明如何确保同步时序逻辑电路正常的工作 4、请简述摩尔机、米利机和同步米利机的概念,并说明如何将前两者转换为后者 5、状态等价的两个含义 6、状态分配的五个原则 二、组合逻辑(2×10=20分) 1、用卡诺图化简以下函数,画卡诺图,并写出蕴含项与实质蕴含项(SOP) F(A,B,C,D)=m(0,2,8,9,10,14)+d(3,4,5) 2、用QM算法化简以下函数 F(A,B,C,D)=m(0,1,2,5,6,7,8,9,10,14)+d(12) 三、时序逻辑(15×2=20) 1、用163计数器设计从1~24计数的计数器,输入为时钟信号CLK,,使能信号En,输出为进位ECO与h[4:0]。 2、使用蕴含表法化简以下状态表 四、状态机设计(30分) 1(10分)、用verilog语言,设计识别串行同步输入序列为1的同步米利机,初始状态复位时输出为0,当1的个数被3整除时输出为1. 2、(20分)米利机,当输入序列中出现011或101时,输出z0有效,序列可重叠。

1(10分)、给出以下状态图,补充完整(图中状态内的编码与输入序列无关)。 2)使用D触发器与最少的NAND与非门,根据上面的状态分配设计电路 (2分)画出二进制状态表 (8分)触发器激励输入与电路输出的卡诺图化简,并写出化简后的函数。

………密………封………线………以………内………答………题………无………效…… 电子科技大学2012 -2013学年第二学期期末考试 A 卷 课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期: 20 13 年 07 月05 日 考试时长:_120___分钟 课程成绩构成:平时 30 %,期中 30 %,实验0 %,期末 40 % 本试卷试题由___七__部分构成,共__7___页。 题号一二三四五六七八九十合计 得分 I. Fill out your answers in the blanks (3’ X 10=30’) 1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ). 2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach. 3.The RCO_L of 4-bit counter 74x169 is ( 0 or low) when counting to 0000 in decreasing order. 4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least. 5. One state transition equation is Q* = JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN = ( JQ’+KQ ). (参见课件Flip-flops Transforming Skills.ppt) 6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states. 7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101) will be the output. 8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is

广西科技大学2015—2016学年第 1 学期课程考核 试题 考核课程数字电路与数字逻辑( A 卷)考核班级软件141、142 学生数 80 印数 85 考核方式闭卷考核时间 120 分钟 1、 选择题(每题2分,共20分) 1. 数字9的BCD码是1001,那么它的余三码是( A ) A 1100 B 1001 C 0110 D 1111 2. 若输入变量A、B全为1时,输出F为1,其余情况下,F为0,那么F与AB的关系是( B ) A B C D 3. 二进制数1100转换成十六进制数是( C ) A 12H B 0AH C 0BH D 0CH 4. 逻辑表达式( C ) A B C D 5. 组合逻辑电路通常由( A )组合而成。 A 门电路 B 计数器 C 触发器 D 寄存 器 6. 时序逻辑电路中一定包含( C ) A 门电路 B 计数器 C 触发器 D 寄 存器 7. 有2个与非门构成的基本RS触发器,如果要触发器输出保持不变,则( ) A B C D 8. T触发器,如果T端为高电平,那么CP脉冲来的时候,输出Q应( ) A 为0 B 为1 C 保持不变 D 翻

转 9. 时序逻辑电路输出状态的改变( ) A 仅与该时刻输入信号的状态有关 B 仅与时序电路的原状 态有关 C 与时序电路的原状态无关 D 与A、B两项皆有关 10. 以下( B )不是解决组合逻辑电路中竞争冒险现象的方法。 A 增加冗余项 B 使用卡诺图化简 C 增加选通脉冲 D 改变设计方法 2、 使用卡诺图法化简以下逻辑函数(每题5分,共20分) 1. 2. 3. 4. 3、 问答题(每题10分,共40分) 1. 分析下图所示的组合逻辑电路。 1) 写出逻辑表达式。(4分) 2) 画出真值表。(3分) 3) 说明其逻辑功能。(3分) 2. 现有一个T触发器,请使用必要的门电路将其转换成一个JK触发器。 3. 现有5个D触发器连接如下,RST是清零信号,清零之后 5个触

数字逻辑(A) 2010 — 2011 学年第一学期 课程名称:___数字逻辑________ 学生姓名:___________________ 学号:___________________ 专业:____软件工程_______ 年级/班级:__________________ 课程性质:公共必修、公共选修、专业必修、专业选修 一二三四五六七八总分阅卷人签名 一、填空题(20分,每空2分) 1. (2010)D =()B = ()H = ()8421BCD 答案:(111 1101 1010)B= (7DA)H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A、B两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为。 答案:与逻辑 3. 逻辑函数式F=AB+AC的对偶式为,最小项表达式为 ∑ F( )。 =m 答案:) F D+ + A =∑ (C B )( A F(5,6,7) =m 2.逻辑函数D ' '+ ' + ' + =的最简与或式 ' + + CD C A AC AB D ABC F' ABD C 是。 答案:'D A+ 4. 从结构上看,时序逻辑电路的基本单元是。 答案:触发器 5. JK触发器特征方程为。 答案:Q '+ K JQ' 6.A/D转换的一般步骤为:取样,保持,,编码。 答案:量化 二、选择题(20分,每题2分)

1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 +U CC +U CC -U BB R R K R C R B A B C F