学生实验实习报告册

学年学期:2019 -2020 学年?春?秋学期

课程名称:数字电路与逻辑设计实验A

实验项目:基于FPGA的数字电子钟的设计与实现

姓名:康勇

学号:2018211580

学院和专业:计算机科学学院计算机科学与技术专业

班级:04911801

指导教师:罗一静

重庆邮电大学教务处制

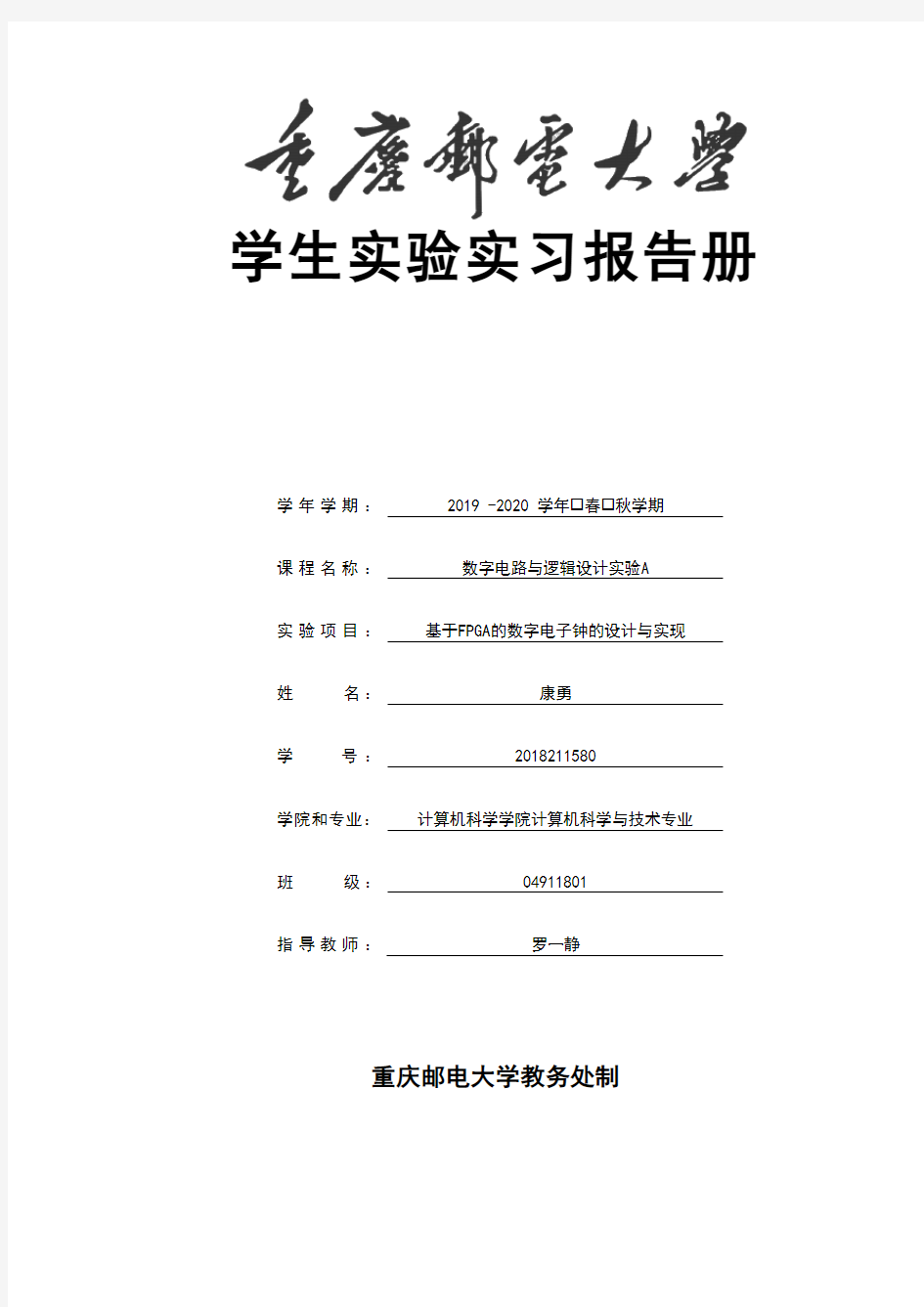

1.系统顶层模块设计

本项目分为四个模块,分别为分频模块、计时模块、数码管动态显示模块、按键消抖模块。功能包括:基本时钟功能,整点报时功能,手动校时功能,秒表功能,小数点分割时分秒功能等。

设计思路如下:

图表 1数字时钟系统顶层模块设计思路

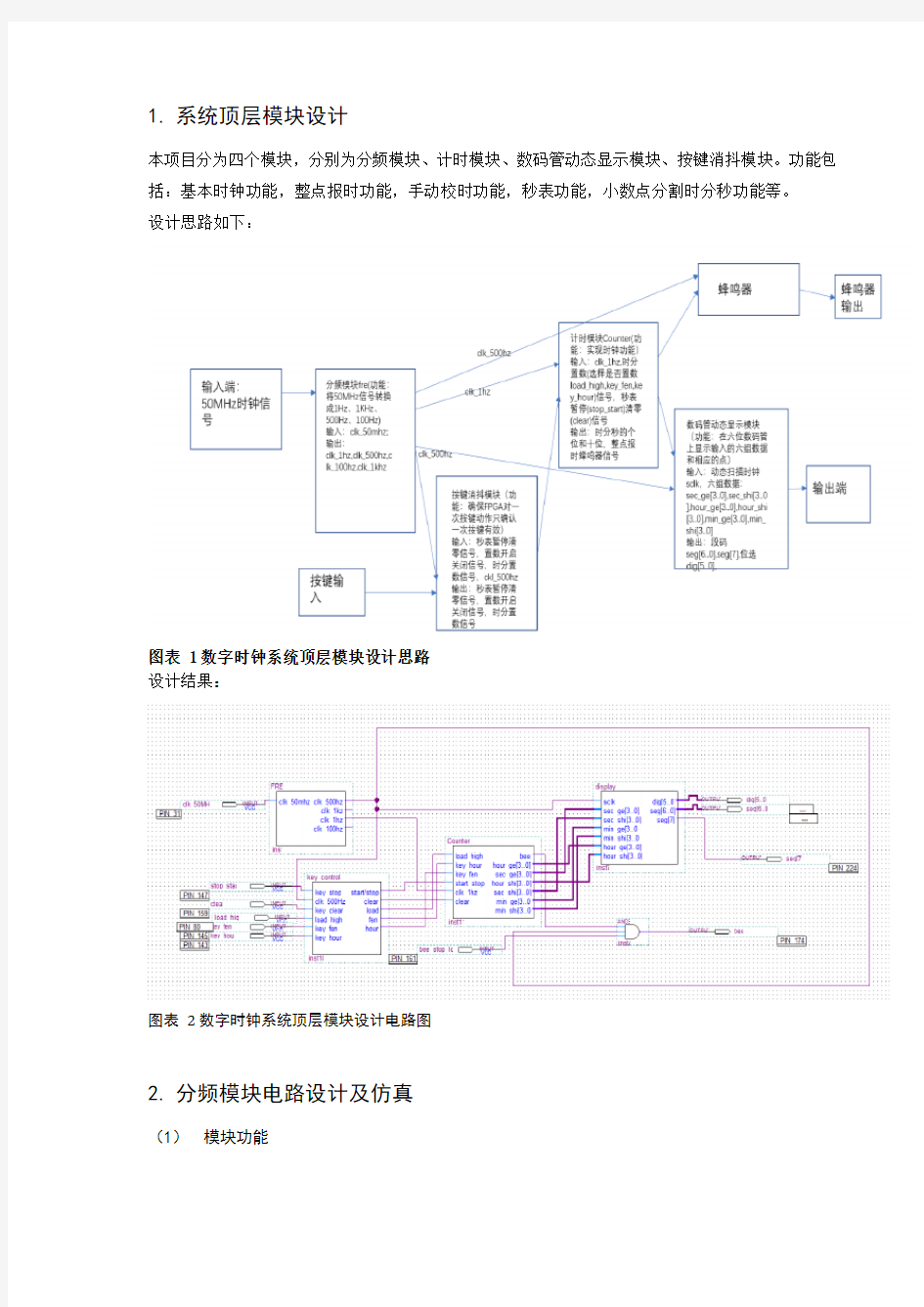

设计结果:

图表2数字时钟系统顶层模块设计电路图

2.分频模块电路设计及仿真

(1)模块功能

将输入的频率为50MHz的时钟信号利用74390通过2、5、100分频,对输入信号进行逐级分频。

(2)设计思路

图表3分频模块电路设计思路

(3)设计结果(电路)

图表4分频模块电路设计图

图表5模100电路图

(4)测试结果

图表6模100仿真图

图表7模5仿真图

图表8模2仿真图

3.计时模块设计及仿真

本模块主要功能是实现电子时钟计数功能。

图表9计时模块顶层设计电路图

3.1分、秒计时模块(模60计数)

(1)模块功能(计数、进位)

电子时钟的分钟位和秒钟位均采用模60计数;

计数功能:从0到59;

进位功能:当计数记到59的时候,输出一个进位信号。

(2)设计思路

模60计数器可以通过一个模6计数器和一个模10计数器组成,由分钟位和秒位的特性可知,可以用模10计数器为个位,模6计数器为十位。当个位到9后,向十位进一。本模块使用器件74160。

计数功能:74160是十进制同步计数器(异步清零),为实现计数功能,首先将74160的LDN 反,CLRN反,ENT,ENP接高位,再接入时钟脉冲信号CLK,即可完成下图左侧(个位)模

10计数功能;为实现下图右侧(十位)模6计数功能(有效状态为0000~0101),可利用清除端的反馈复位法实现,又因为74160为异步清零,所以当QA QB QC QD = 0110时,(将QBQC取反后连接CLRN反端)完成清0动作,即可实现模6计数。

进位:74160上升沿触发,分析可知,当个位(左侧)到9后(1001),观察可知,左侧QD 0~7时为0,8~9时为1,然后再跳到0,在其输出端取反后连接右侧的CLK端,这时左侧只有从9跳到0的时候才会产生一个上升沿信号,此信号即为进位信号;同理可分析整个计数器进位,即对右侧QC取反后输出的信号为进位信号。

(3)设计结果(电路)

图表10模60计数器电路图

(4)仿真测试

图表11模60计数器仿真测试图

3.2小时计时模块(模24计数)

(1)模块功能

电子时钟的时钟位采用模24计数;

计数功能:从0到23;

(2)设计思路

模24计数即从(0000 0000 – 0010 0011),又因为74160为异步清零,所以当计数进入暂态(0010 0100)时立即产生清零信号,即CLRN反 = (Q1C Q2B)反,如下图所示,左侧为低位,右侧为高位。

(3)设计结果(电路)

图表12模24计数器电路图

(4)仿真测试

图表13模24计数器仿真测试图

4.数码管动态显示模块

模块功能描述及设计

本模块的主要功能是通过数码管的动态扫描实现6位数码管显示计数结果,本模块由数码管选择模块counter6,位选模块dig_select,段选模块seg_select,以及译码模块decoder构成。

图表14dp模块电路图

4.1扫描模块couner6

(1)模块功能

实现000—101计数,选择6位数码管。

(2)设计思路

本模块利用双十进制异步计数器74390实现。由74390的特性可知,当1CLKB接1QA时,实现模10计数(8421BCD码)。模6计数从000—101,因为74390为异步清零且清零端高电平有效,所以当计数器进入到暂态 110 的同时立即产生清零信号至1CLR端(1CLR = 1QC1QB),即可完成模6计数

(3)设计结果(电路)

图表15模6计数器电路图

(4)仿真测试

图表16模6计数器仿真测试图

4.2位选模块dig_select

(1)模块功能

图表17位选模块原理

如上表所示,add从000-101,在实验平台上数码管依次从第一位亮到第六位。(动态显示,人眼分辨不出先后)

(2)设计思路

该模块使用二进制译码器74138实现,由74138的特性可知,当G1接高电平,G2AN反、G2BN 反接低电平时实现译码功能,输入端ABC由000—101,输出端dig[0]—dig[5],显示结果与上表所示一致。

(3)设计结果(电路)

图表18位选模块设计电路图

(4)仿真测试

图表19位选模块仿真测试结果

4.3段选模块seg_select

(1)模块功能

该模块功能是从6组输入信号(hour_shi[3..0],hour_ge[3..0],min_shi[3..0],min_ge[3..0],sec_shi[3..0],sec_ge

[3..0])中选择一组输出code[3..0],由add[2..0]控制。

(2)设计思路

该模块使用74151数据选择器完成6选1功能。

图表20段选模块原理图

74151有3条数据选择地址输入线,8条数据输出线,此模块只需用到其中6条数据输出线(D0,D1,D2,D3,D4,D5)。为实现数据选择功能,将 GN反端接地,其余端口如下图。

当add[0]add[1]add[2]为000时,即Y选择D0,输出code[0]code[1]code[2]code[3]即为sec_ge[0]sec_ge[1]sec_ge[2]sec_ge[3]。同理,依次输出sec_shi[3..0],min_ge[3..0],min_shi[3..0],hour_ge[3..0],hour_shi[3..0]。

(3)设计结果

图表21位选模块电路图

(4)仿真测试

如下图:为其设置一个初始值进行测试

图表22位选模块仿真图

4.4译码模块decoder

(1)模块功能

7448为共阴极数码管编译器,可将4位8421BCD码译为七位段码,驱动共阴数码管以十进制数形式显示数字字形。

(2)设计思路

图表23译码器设计思路

由7448功能可知,LTN反,RBIN反,BIN反均接高电平,ABCD端输入对应二进制码,OA OB OC OD OE OF OG端输出相应的0 1信号。

(3)设计结果

图表24译码器设计电路图

(4)仿真测试

图表25译码器模块仿真测试

5.其他扩展功能

5.1显示分割时分秒的点的模块dp

(1)模块功能

用两个点将时分秒分隔开来。

(2)设计思路

用于分隔时分秒只需要显示两个点(第三个和第五个点)即可,而点的亮灭由数码管的dp 决定(dp为0表示灭,dp为1表示亮)。此模块输入为add[2..0],输出为seg[7]。由前面分析可知,当add[2..0]=010或100时,seg[7]输出1,公式为seg[7]=m2+m4。此模块可利用74138完成,如下图所示。

(3)设计结果

图表26dp模块设计电路图

(4)波形仿真

图表27dp模块波形仿真

5.2 整点报时

(1)模块功能

电子时钟到整点时,蜂鸣器响。

(2)设计思路

当分钟模60计数器的8个输出端口(min_ge[3..0],min_shi[3..0])同时输出为0的时刻,蜂鸣器响1分钟。可以用一个8或门将8个输出端口连接取反后输出至蜂鸣器。

(3)设计结果

图表28整点报时模60设计图

图表29整点报时计数模块顶层电路图

(4)波形仿真

图表30整点报时波形仿真

5.3 手动校时

(1)模块功能

该模块的功能是实现时分的手动校时。

(2)设计思路

由前面的分析可知,当秒达到59后产生一个进位信号使分钟加1,当分钟达到59后产生一个进位信号使时加1。手动校时即使用两个按钮分别模拟秒的进位信号和分的进位信号。同时需要设计一个二选一的模块来启动和关闭手动校时功能。

2选1模块:如下图,s表示开关,当s为0时,选择b(置数关闭);当s为1时,选择a(置数开启)。通过计算可以得到:输出Y = ab+bs反+as。

(3)设计结果

图表31手动校时2选1设计电路图

图表32手动校时计数模块顶层设计电路图

(4)波形仿真

图表33手动校时波形仿真

5.4 秒表

(1)模块功能

此模块具有秒表功能。计数范围为00分00秒00毫秒—59分59秒99毫秒;具有开始计时、停止计时、清零及显示功能。

(2)设计思路

本项目的计数器均使用74160设计。而74160具有如下特点:①CR反(CLRN反)为0时,立即有Q3Q2Q1Q0=0000,实现异步清零功能。②CR反、LDN反、ENT接1,ENP为0时实现保持(即暂停)功能。

(3)设计结果

图表34 秒表顶层电路设计

图表35秒表模60电路图

图表36秒表模100电路图

(4)波形仿真

如下图:当清零端始终为1时,输出结果始终为0。

图表37秒表清零波形仿真

如下图:给start_stop一个脉冲信号,当start_stop为1时暂停,为0时,工作。仿真结果如下

图表38秒表暂停功能波形仿真

5.5 消抖模块

(1)模块功能

确保FPGA对一次按键动作只确认一次按键有效,消除按键抖动影响。

(2)设计思路

本模块使用D触发器(D触发器是一种延迟型触发器,不管触发的现态是0还是1,CP脉冲上升沿到来后,触发器的状态都将变成与CP脉冲上升沿到来时的D端输入值相同,相当于将数据D 存入了D触发器中。)延时后多次检测按键消抖。如下图所示,该电路为同步时序逻辑电路,一共使用了6个D触发器,由于时钟信号clk频率为500MHz,及信号经过1个D触发器延时2ms,经过6个D触发器延时12ms,满足抖动间最大10ms的要求。

信号每经过1次延时进行一次采样,只有6次采样的结果均为高,输出才为高电平,说明12ms 内信号均为高,判定按键按下。

该模块除了对按键消抖外,还要对start_stop按键进行处理,以保证单按键实现开始计时和停止计时。此处采用一个JK触发器,当按键按下,产生一次上升沿,JK触发器翻转一次,从而实现start_stop信号按键一次为高,再按一次为低。

(3)设计结果

图表39消抖模块电路设计图

图表40按键消抖模块顶层电路

5.6 频率切换

(1)模块功能

当按下频率切换拨板开关,时钟由原来1Hz变为100Hz。

(2)设计思路

用一个二选一模块来控制,当二选一开关select为1时,选择1Hz信号输入,当二选一开关select为0时,选择100Hz信号输入。二选一模块设计思路见手动校时模块。

(3)设计结果

图表41频率切换部分电路图

6.系统总体测试

7.系统设计实现过程中遇到的主要问题、解决思路和解决方案

问题1:在做整点报时的时候,波形图这些都正确,但是接到实验平台的时候,蜂鸣器不响;

解决思路:将输出信号接到蜂鸣器的同时还要给它连接一个时钟脉冲。

解决方案:如下图,其中一个输入为整点报时输入,一个为500Hz的脉冲,一个为开关控制关停。

图表43蜂鸣器

问题2:在做基本任务的时候,进位不正确。

解决思路:将真值表列出来,分析上升沿还是下降沿触发,选择哪一个输出适合作为进位输出端。

解决方案:下图为模60的进位方案。

图表44 进位

问题3:在做秒表的时候,暂停开始功能不正确(理想情况:按一下暂停,再按一下开始;问题是要一直按着才会增,不按着就暂停了)

解决思路:导致这个问题原因是按键当按下后一直是高电平,抬起后就是低电平。为了实现按一次是高电平,再按一次才是低电平,可以利用JK触发器一次翻转的特性(指一旦在CP=1期间,主触发器接收了输入激励信号,发生一次翻转后,主触发器状态就一直保持不变)实现。

解决方案:在开关之前加如图所示电路

图表45 JK触发

8.心得体会

在本次实验中,我学习到了很多知识:任意模值计数器的设计,计数器之间的进位译码器的使用,选择器的设计和利用,按键消抖的理论和解决方案,数码管结构的认识,动态扫描的原理,段选和位选电路的选择等等。也通过这次实验理解了理论课上之前没有理解的一些东西,比如为什么消抖,稳定清零,各种集成器件的原理使用。在本次实验中也发现了自己很多不足之处,比如设计进位的时候没有认真区分集成器件的区别,导致一些小错误。在设计过程中,我也感受到了亲自动手实践的乐趣,当自己正确完成基本任务和做好一个拓展任务时,能够获得成就感,并且也逐渐对数电感兴趣了。

学号:2018211580姓名:康勇座位号:C4

评分细则及测试原始数据记录