附录:Maxplus n基本操作方法

图形输入法

利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。

MAX+plusll提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。但更为重要的是,MAX+plusll还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。以传统的数字电路实验相比为例,MAX+plusIl提供原理图输入设计功能具有显著的优势:

*能进行任意层次的数字系统设计。传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计;

*对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1 ns,因此能发现一切对系统可能产生不良影响的竞争冒险现象;

通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正;

*能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件;

?通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。

?如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗;

符合现代电子设计技术规范。传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间

的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

以下将以一位全加器的设计为例详细介绍原理图输入设计方法 ,但 应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理 流程都与文本(如VHDL 文件)输入设计完全一致。

1位全加器可以用两个半加器及一个或门连接而成 ,因此需要首先一个半加 器的设计。以下将给出使用原理图输入的方法进行底层元件设计和层次化设计 的完整步骤,其主要流程与数字系统设计的一般流程基本一致

。事实上,除了

最初的输入方法稍有不同外,应用VHDL 的文本输入设计方法的流程也基本与 此相同。

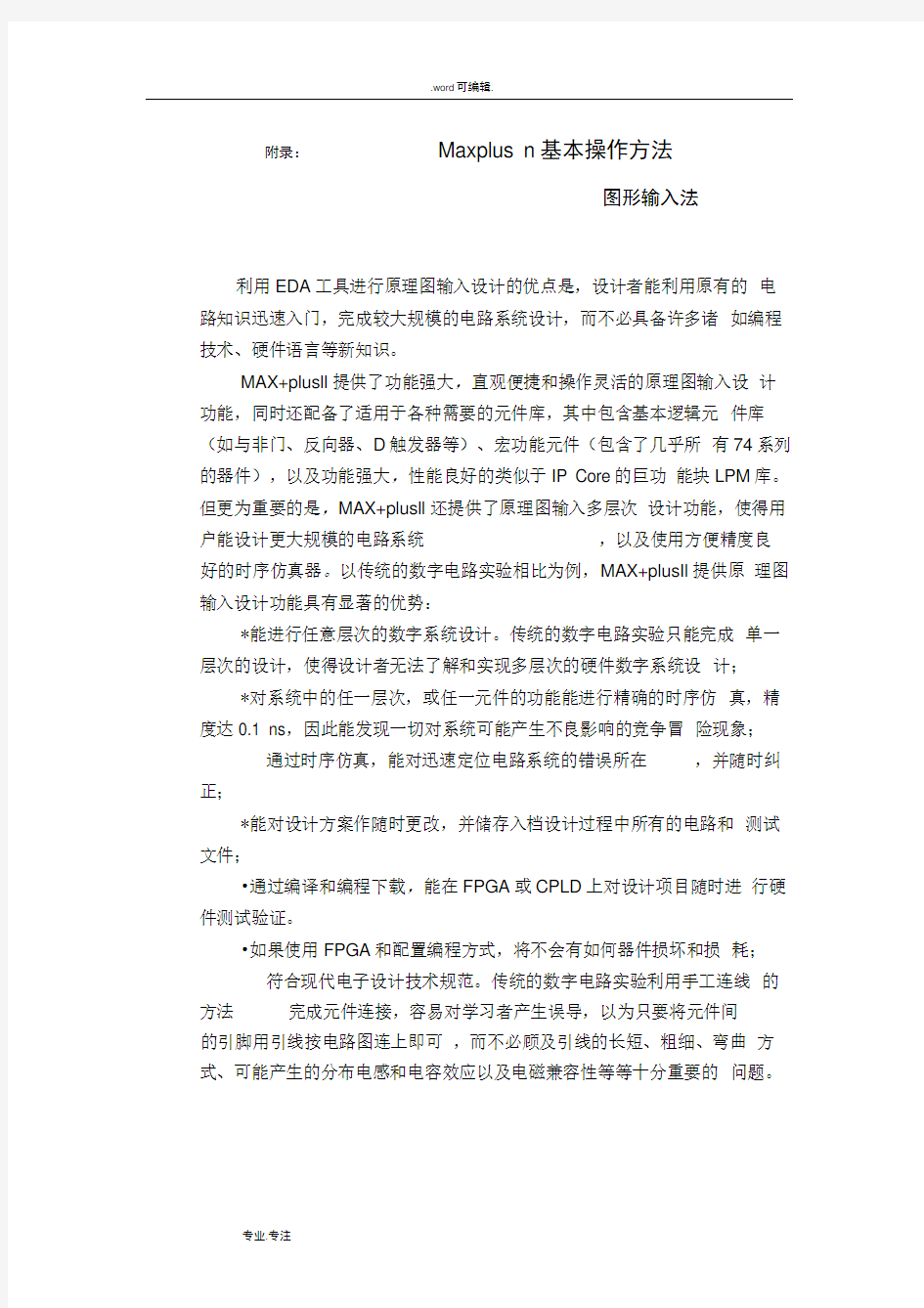

步骤1 :为本项设计建立文件夹 任何一项设计都是一项工程

(Project ),都必须首先为此工程建立

一个放置与此工程相关的所有文件的文件夹,此文件夹将被EDA 软件默 认为工作库(Work Library )。一般不同的设计项目最好放在不同的文 件夹中,注意,一个设计项目可以包含多个设计文件 ,例如数字频率

计。

图A3-1进入Max+plusll ,建立一个新的设计文件

File Type

|A1 Lux II Pile |L XXL pi OptiaiLi [2 3 rl

H

|.Odf d

3

席 Graphic tditoi tii

Symbol Ed*o? hie 广 TeMtEJtoc 广 Waveform

Editor fJe

由此可输入所需的荒件名?SDAND2 (2输入与门)、

DFF C D触发器)、GMD(地綾)、VCC. INPUT I輸/引

脚)、OWUTC输出引脚)、

基本逻辑元件库,如与门、D触友器等

宏功能元件库’如■74161、74138等

毎数可设■址功能元件库*SaLPMji^

基本逻辑元件库中的元件

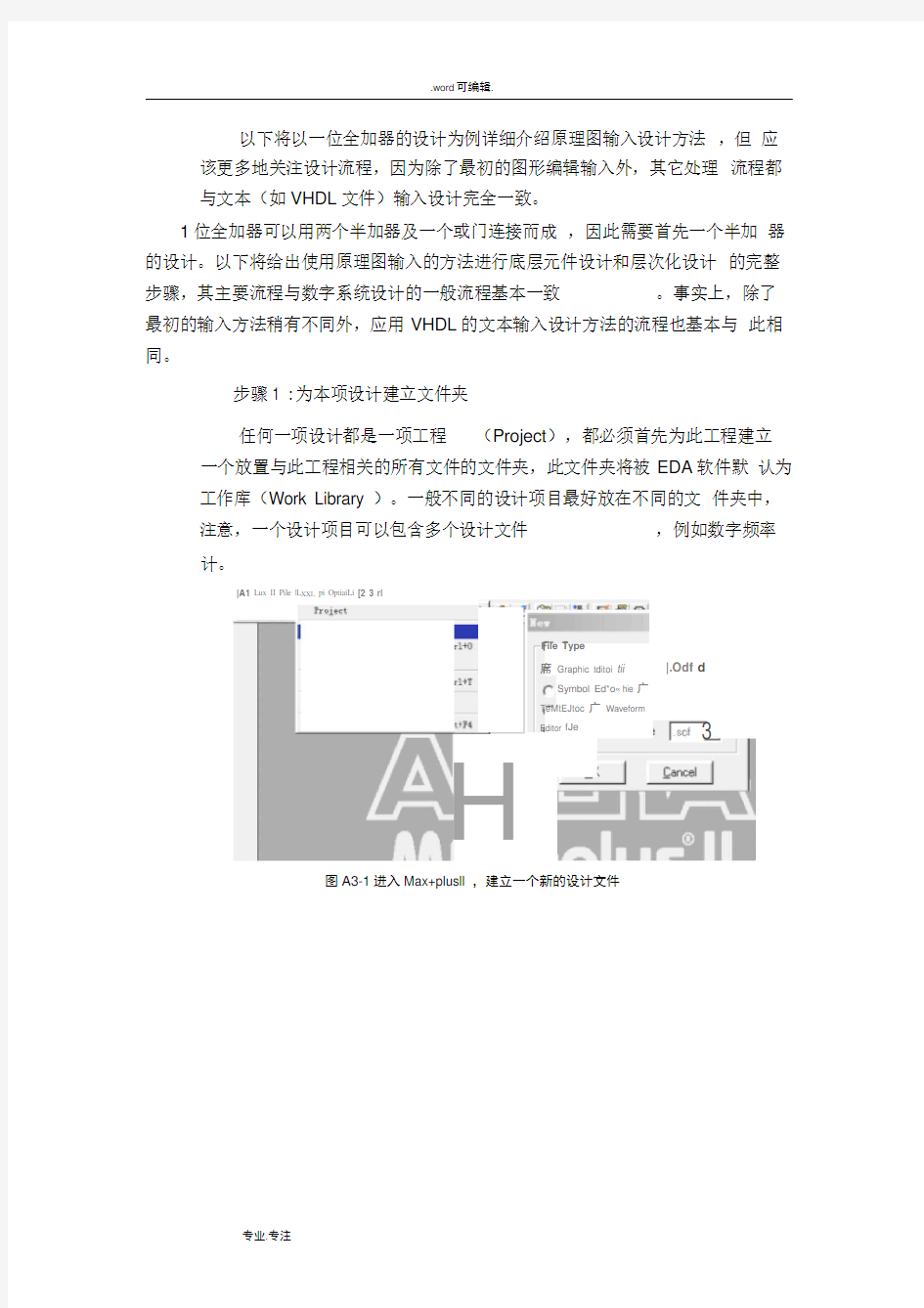

图A3-2元件输入选择窗

假设本项设计的文件夹取名为MY_PRJCT在E盘中,路径为:

E:\MY_PRJCT。文件夹不能用中文。

步骤2:输入设计项目和存盘

1、打开Mux+plusll ,选菜单File > New (图A3-1),在弹出的File Type窗中选原理图编辑输入项Graphic editor File ,按OK后将打开原理图编辑窗。

2、在原理图编辑窗中的任何一个位置上点鼠标右键,将跳出一个选

择窗,选择此窗中的输入元件项Enter Symbol,于是将跳出如图A3-2所示的输入元件选择窗。

3、用鼠标双击文件库“Symbol Libraries ”中的e:\

maxplu2\max2lib\prim 项,在Symbol Files窗中即可看到基本逻辑元件库prim中的所有元件,但也可以在Symbol Name窗中用键盘直接输入所需元件名,在按OK键,即可将元件调入原理图编辑窗中。如为了设计半加器,分别调入元件and2、not、xnor、in put和output (图A3-3)并连接好。然后用鼠标分别在in put和output的PIN-NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b、co和so。

4、点击选项File t Save As”,选出刚才为自己的工程建立的目录

E:\MY_PRJCT,将已设计好的图文件取名为:h_adder.gdf (注意后缀是.gdf),并存在此目录内。

lu-s XX K11?£(|11 V1?W Symbol M EI pi. LJt3.43.t1 kx Upt|Giis tfamdow Holp

2 < ___壁g看仓硯酶色豐國?B壘晞塚岛吧鶯亘富阿

图A3-3将所需元件全部调入原理图编辑窗

注意,原理图的文件名可以用设计者认为合适的任何英文名(VHDL 文本存盘名有特殊要求),女口adder.gdf(加法器)等。还应注意,为了将文件存入自己的E:\MY_PRJCT目录中,必须在如图A3-4的Save as窗中双

击MY_PRJCT目录,使其打开,然后键入文件名,并按OK。

韵昌Q剣工惟心飓毎?璧必圍盘篦腫苗旦笔礬霊

I

图A3-4连接好原理图并存盘

注意:原理图画好后,可以建立成一个默认的逻辑符号,Flie -> creat default symbol,则可以将用户刚刚设计的电路形成一个模块符号

h_adder 。

* IT■Ui-plu'G 1£ - ?: X

■曹■巧jgiAh ■dd.'ir — [lk_*dd.a-r. fdf ~ &rb.plkie Edi 1 ar

占PIN JhlAME

*『附…piNjiiiiE

PiN.NAK …二趣「

nA糾冋T]尸~~V PiN_hiAME

!

fl 'CO

'0 SO

禹,也ti+pix ii

□ 3 2寻

711s Ed.it Viflw Symbol A E^I^ lltilrti

Premie ct

d Qjiti. anj£ Vindcw HA-lp

JI UTiC..

V AIV..

QjtPln

Dtlete File..

B.etr i e^e---

Clcsa

S w

Save As

Cr?at & D A f?ult Synbal 肌it 5^41

Create Deftult Include Fil^-

CtrliO

Ctrl+?4

rtrliS

CtrL4I

Sjat Froj lc 匚mmrt f Lla

Save 直Cunpil老

S H£& ft. Sanulq.te

S awe, Can|pii & -S Sim-ul-kte

Archive..

Ctrl+-Sh3 ft+J

Ctrl*L

CU T1*S1M ft4L

C trl*SJi3 Et+K

Print.. . CtrL+T

Frint So-t^ip..

gierareKy

"普心n=4iril Pln^-In N

Ezit H^Hplus H 俎计F4

1 e: \myjrj c tSh_-adld.tr

2, e: \k30den >?\4iid?r \ addlcrSb

3 亡:Vcdwri 11 iif\kl0d.tn?V5eh.Vnul liSxB 电

e: \cd.vri t i ng^kLOd. Anarch VE_t P電t 呈 e

\cdiwri t i

t e: VcdiTri 11 iifi\kl0d.eTii,ii-5ch\ teS 11

亡:\cd.*Ti 11 y IklOd■匕

■obmcllAMlILJGILl g ?-: \imy_prj ct\p gl

—tawr 匚\ co

---- 1----------

F/~77^ .,,

农0…

阿「匚

图A3-5将当前设计文件设置成工程文件

步骤3:将设计项目设置成工程文件 (PROJECT )

为了使Max+plusll 能对输入的设计项目按设计者的要求进行各项处 理,必须将设计文件,如半加器h_adder.gdf ,设置成Project 。如果设计 项目由多个设计文件组成,则应该将它们的主文件,即顶层文件设置成 Project o 如果要对其中某一底层文件进行单独编译 、仿真和测试,也必

图A3-6选择最后实现本项设计的目标器件

将设计项目(如h_adder.gdf )设定为工程文件设置成Project 有两个 途径:

1、如图 A3-5 ,选择 File > Project 一 Set Project to Current File , 即将当前设计文件设置成Project 。选择此项后可以看到图A3-5所示的窗 口左上角显示出所设文件的路径。这点特别重要,此后的设计应该特别 关注此路径的指向是否正确!

2、如果设计文件未打开,可如图A3-5所示,选File > Project > Name ,然后在跳出的Project Name 窗中找到E:\MY_PRJCT 目录,在其 File 小窗中双击adder.gdf 文件,此时即选定此文件为本次设计的工程文 件(即顶层文件)了。

步骤4 :选择目标器件并编译

须首先将其设置成Projcet o

I

r

------------

Edit Chips ?

Top Dl HiBraich^. e: \nrtgp_piictxh_addei. gdf Cancel

Aylo Device...

□

K

Diffvjice Options...

MigiiaticinDBvice.,. DeviceFam^: |FLEX10K Devices:

F Show Only Fastest Speed Grades

I - l ,,4antain Current Synthesis Regardess of Device or Speed Grade Changes

为了获得与目标

器件对应的,精确的时

序仿真文件,在对文件

编译前必须选定最后

实现本设计项目的目

标器件,在

Max+plusll环境中主要

选Altera公司的FPGA

图A3-7对工程文件进行编译、综合和适配等操作或CPLD。

首先在Assign选项的下拉菜单中选择器件选择项Device,其窗口如图

A3-6所示。此窗口的Device Family是器件序列栏,应该首先在此拦中选定目标器件对应的序列名,如EPM7128S对应的是MAX7000S系列;

EPF10K10对应的是FLEX10K系列等。为了选择EPF10K10LC84-4器件,应将此栏下方标有Show only Fastest Speed Grades 的勾消去,以便显示出所有速度级别的器件。完成器件选择后,按0K键。

最后启动编译器,首先选择左上角的MAX+plusIl选项,在其下拉菜单

中选择编译器项Compiler (图A3-7),此编译器的功能包括网表文件提

取、设计文件排错、逻辑综合、逻辑分配、适配(结构综合)、时序仿真文

件提取和编程下载文件装配等。

点击Start,开始编译!如果发现有错,排除错误后再次编译

步骤5:时序仿真

接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:

1、建立波形文件。按照以上步骤2”,为此设计建立一个波形测试文件。选择File项及其New,再选择图A5-1右侧New窗中的Waveform Editer.?项,打开波形编辑窗。

2、输入信号节点。在图A3-8所示的波形编辑窗的上方选择Node 项,在下拉菜单中选择输入信号节点项Nodes from SNF。在弹出的窗口

(图A3-9)中首先点击List键,这时左窗口将列出该项设计所以信号节

点。由于设计者有时只需要观察其中部分信号的波形,因此要利用中间的

=> ”键将需要观察的信号选到右栏中,然后点击OK键即可。

M lAl+plus II - e : S?y_pr j ct\L_iidlder - [Vnti tle42 - T*?ef?r? E4i t?r]

图A3-8从SNF 文件中输入设计文件的信号节点

Q| l!TUl * rpjl UA X Jh '丄 Ik'S £,UJ>L 上丄匸“ i-iyiy

JH A 工上 ^i 1. 址 Jh h * '■ X SA

If A Vlk J

££ k BLUiM'n 口匸丄”

風育

粋 鱼理固曰凹妙 窗瓦歳 墮临ta 喲二募翠 迅

图A3-10在Options 选项中消去网格对齐 Snap to Grid 的选择(消去勾)

3、 设置波形参量。图A3-10所示的波形编辑窗中已经调入了半加器 的所有节点信号,在为编辑窗的半加器输入信号a 和b 设定必要的测试电 平之前,首先设定相关的仿真参数。如图A3-10所示,在Options 选项 中消去网格对齐Snap to Grid 的选择(消去勾),以便能够任意设置输 入电平位置,或设置输入时钟信号的周期。

4、 如图A3-11所示,设定仿真时间宽度。选择File 项及其End time 选项,在End time 选择窗中选择适当的仿真时间域,如可选34us (34 微秒),以便有足够长的观察时间。

5、 加上输入信号。现在可以为输入信号a 和b 设定测试电平了。如 图A3-12标出的那样,利用必要的功能键为a 和b 加上适当的电平,以 便仿真后能测试so 和co 输出信号。

D E a

u

胸團21I

Ref

215.6ns

I :

A|

Name:

Ref: Nam a 丽冠

I rvr*l Tirnfl- h7S Hns Eater T^d^s frea SIT

800.0ns

ii

bill]

?(01

M (D1

Lu

上i

bjii

di)

血10〕 co (0)

1JJ J

图A3-9列岀并选择需要观察的信号节点

岂 KAK4R L U .2 II Eile £diI Vie* Kcde

Utili lies

liniw Ecl :P

D.営IH.剑_為 匪1包 町|删血.禺屈园曲」 Sn&p to Grid

Start. 195.0ni£

'可刁End. |1日了.On 占

"CtrH-Shi ft+G

Name. Value :

100 Ong 2D0.Dns https://www.doczj.com/doc/3815690496.html,s 4i

U ZAT Ltbr uri at..

Color P-il^tt A .. LlCbfiEft Sa tup

aDO.Dns 900 Oni 1.C

MU+plus H Eil? 耽it 些卵 No J? As si Utili t i Qpt i

liniow Halp

I 」期.Ens

jOOOns 600.0ns 700.0ns

I

Ini' R IVR 卜 I -4PI fins

Node / GlMjpL

AyadaUe Nnde^ g Groups:

Sdected Misdes & Groqps: R Preserve EKisbrg Nodes

Fra 氏me PH .

第一章 MAX+plus II开发软件A1tera公司的MAX十plus II开发系统是一个完全集成化、易学易用的可编程逻辑设 计环境,它可以在多种平台上运行。MAX十plus是Multiple array matrix and programmable logic user system的缩写,目前已发行到了第10.1版本。它所提供的灵活性和高效性是无可比拟的,其丰富的图形界面,辅之以完整的、可即时访问的在线文档,使设计人员能够轻松、愉快地掌握和使用Max十plus II软件。 1.1MAX+plus II功能特点 1、开放的界面 Altera的工作与EDA厂家紧密结合,使MAX+plus II软件可与其它工业标准的设计输入、综合与校验工具相连接。设计人员可以使用A1tera或标准EDA设计输入工具来建立逻辑设计,使用MAX十plus II编译器(Compiler)对A1tera器件设计进行编译,并使用A1tera 或其它EDA校验工具进行器件或板级仿真。目前,Max十plus II支持与Cadence、Exemplarlogic、MentorGraphics、Synopsys、Synplicity、Viewlogic和其它公司所提供的EDA 工具的接口。 2、与结构无关 MAX十plus II系统的核心Compiler支持Altera公司的ACEX1K、FLEXl0K、FLEX 8000、FLEX 6000、Max 9000、Max 7000、Max 5000和C1assic可编程逻辑器件系列,提供了业界唯一真正与结构无关的可编程逻辑设计环境。MAX十plus II的编译器还提供了强大的逻辑综合与优化功能,使用户比较容易地将其设计集成到器件中。 3、多平台 Max十plus II软件可在基于486、奔腾PC机的Windows NT 3.51或4.0、Windows 95、Windows 98、Windows2000下运行,也可在Sun SPAC Stations,HP 9000Series 700/800和IBM RISC System/6000工作站上运行。 4、完全集成化 MAX十plus II的设计输入、编译与仿真功能全部集成在统一的开发环境下,这样可以加快动态调试,缩短开发周期。 5、丰富的设计库 MAX十plus II提供丰富的库单元供设计者调用,其中包括74系列的全部器件和多种特殊的逻辑宏功能(Macro-Function)以及新型的参数化的宏功能(Mage-Mnction)。调用库单元进行设计,可以大大减轻设计人员的工作量,也可成倍地缩短设计周期。 6、模块化工具 设计人员可以从各种设计输入、编译和仿真选项中进行选择,从而使设计环境用户化,必要时,还可根据需要添加新功能。由于MAX十plus II支持各种器件系列,设计人员不必学习新工具即可支持新结构。 7、硬件描述语言(HDL) Max + plus II软件支持各种HDL设计输入选项,包括VHDL、Verilog HDL和Altera 自己的硬件描述语言AHDL。 8、Megacore功能 Megacore功能是为复杂的系统级功能提供的,经过校验的HDL网表文件,它能使ACEX1K、FLEX10K、FLEX 8000、FLEX 6000、MAX 9000和MAX 7000器件系列实现

常用基本操作 1 常用工具栏的打开和关闭:工具栏上方点击右键进行选择 2 动态坐标的打开与关闭:在左下角坐标显示栏进行点击 3 对象捕捉内容的选择:A在对象捕捉按钮上右键点击(对象捕捉开关:F3) B 在极轴选择上可以更改极轴角度和极轴模式(绝对还是相对上一段线) 4 工具栏位置的变化:A锁定:右下角小锁;工具栏右键 B 锁定情况下的移动:Ctrl +鼠标移动 5 清楚屏幕(工具栏消失):Ctrl + 0 6 隐藏命令行:Ctrl + 9 7 模型空间和布局空间的定义:模型空间:无限大三维空间 布局空间:图纸空间,尺寸可定义的二位空间 8 鼠标左键的选择操作:A 从左上向右下:窗围 B 从右下向左上:窗交 9 鼠标中键的使用:A双击,范围缩放,在绘图区域最大化显示图形 B 按住中键不放可以移动图形 10 鼠标右键的使用:A常用命令的调用 B 绘图中Ctrl + 右键调出捕捉快捷菜单和其它快速命令 11 命令的查看:A 常规查看:鼠标移于工具栏相应按钮上查看状态栏显示 B 命令别名(缩写)的查看:工具→自定义→编辑程序参数(acad.pgp) 12 绘图中确定命令的调用:A 鼠标右键 B ESC键(强制退出命令) C Enter键 D 空格键(输入名称时,空格不为确定) 13 重复调用上一个命令: A Enter键 B 空格键 C 方向键选择 14 图形输出命令:A wmfout(矢量图) B jpgout/bmpout(位图)应先选择输出范围 15 夹点的使用:A蓝色:冷夹点 B 绿色:预备编辑夹点 C红色:可编辑夹点 D 可通过右键选择夹点的编辑类型 E 选中一个夹点之后可以通过空格键依次改变夹点编辑的命令如延伸,移动或比例缩放(应注意夹点中的比例缩放是多重缩放,同一图形可在选中夹点连续进行多次不同比例缩放)

源程序与仿真图 CNT24 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt24 is port(clk,rst:in std_logic; co:out std_logic; qh,ql :out std_logic_vector(3 downto 0)); end cnt24; architecture behave of cnt24 is signal tmpl,tmph:std_logic_vector(3 downto 0); begin process(rst,clk) begin if(rst='1') then tmpl<="0000";tmph<="0000";co<='0'; elsif(clk'event and clk='1')then if(tmpl=9)then tmpl<="0000";tmph<=tmph+1; else tmpl<=tmpl+1; if(tmph=2) then if(tmpl=3) then tmpl<="0000";tmph<="0000";co<='1'; else tmpl<=tmpl+1;co<='0'; end if; end if; end if; end if; ql<=tmpl; qh<=tmph; end process; end behave; CNT60 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt60 is port(clk,rst:in std_logic; co:out std_logic; qh,ql :out std_logic_vector(3 downto 0)); end cnt60; architecture behave of cnt60 is signal tmpl,tmph:std_logic_vector(3 downto 0); begin process(rst,clk) begin if(rst='1') then tmpl<="0000";tmph<="0000";co<='0'; elsif(clk'event and clk='1')then if(tmpl=9)then tmpl<="0000"; if(tmph=5) then tmph<="0000";co<='1'; else tmph<=tmph+1;co<='0'; end if; else tmpl<=tmpl+1; co<='0'; end if; end if; ql<=tmpl; qh<=tmph; end process; end behave; DIV1000 Library IEEE; Use IEEE.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Use IEEE.std_logic_arith.all; Entity div1000 is Port( clk: in std_logic;--from system clock(1KHz) f1hz: out std_logic);-- 1Hz output signal end div1000; architecture arch of div1000 is signal count : integer range 0 to 499;--count from 0 to 499-local si signal temp:std_logic; begin

本教程享有知识版权保护,非法传播必究。 Max+plusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,Altera是世界上最大可编程 逻辑器件的供应商之一。Max+plusⅡ界面友好,使用便捷,被誉为业界最易用易学的 EDA软件。在Max+plusⅡ上可以完成设计输入、元件适配、时序仿真和功能仿真、编程 下载整个流程,它提供了一种与结构无关的设计环境,是设计者能方便地进行设计输入、 快速处理和器件编程。 Max+plusⅡ开发系统的特点 1、开放的界面 Max+plusⅡ支持与Cadence,Exemplarlogic,Mentor Graphics,Synplicty,Viewlogic 和其它公司所提供的EDA工具接口。 2、与结构无关 Max+plusⅡ系统的核心Complier支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000和Classic可编程逻辑器件,提供了世界上唯一真正与 结构无关的可编程逻辑设计环境。 3、完全集成化 Max+plusⅡ的设计输入、处理与较验功能全部集成在统一的开发环境下,这样可以加快动 态调试、缩短开发周期。 4、丰富的设计库 Max+plusⅡ提供丰富的库单元供设计者调用,其中包括74系列的全部器件和多种特殊的 逻辑功能(Macro-Function)以及新型的参数化的兆功能(Mage-Function)。 5、模块化工具 设计人员可以从各种设计输入、处理和较验选项中进行选择从而使设计环境用户化。 6、硬件描述语言(HDL) Max+plusⅡ软件支持各种HDL设计输入选项,包括VHDL、Verilog HDL和Altera自己的 硬件描述语言AHDL。 7、Opencore特征 Max+plusⅡ软件具有开放核的特点,允许设计人员添加自己认为有价值的宏函数。 常用菜单简介 (1)MAX+PLUSⅡ菜单: MAX+plusII: Hierarchy Display___塔形显示;

C r e o动态机构仿真操 作手册 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

Creo2.0动态机构仿真操作手册 1 范围 本标准规定了Creo2.0动态机构仿真建模方法及思路。 本标准适用于公司产品结构设计选用。 2 Creo2.0机构模块简介 在进行机械设计时,建立模型后设计者往往需要通过虚拟的手段,在电脑上模拟所设计的机构,来达到在虚拟的环境中模拟现实机构运动的目的。对于提高设计效率降低成本有很大的作用。Creo Parametric 2.0中“机构”模块是专门用来进行运动仿真和动态分析的模块。 design(机械设计)和Mechanism dynamics(机械动态)两个方面的分析功能。 在装配环境下定义机构的连接方式后,单击菜单栏菜单“应用程序”→“机构”,如图1-1所示。系统进入机构模块环境,呈现图1-2所示的机构模块主界面:菜单栏增加如图所示的“机构”下拉菜单,模型树增加了如图所示“机构”一项内容,窗口上边出现如图1-3所示的工具栏图标。下拉菜单的每一个选项与工具栏每一个图标相对应。用户既可以通过菜单选择进行相关操作。也可以直接点击快捷工具栏图标进行操作。

图1-1 由装配环境进入机构环境图 图1-2 机构模块下的主界面图 图1-3 机构菜单

图1-4 模型树菜单 如图 1-4所示的“机构树”工具栏图标和图1-3中下拉菜单各选项功能解释如下: 连接轴设置:打开“连接轴设置”对话框,使用此对话框可定义零参照、再生值以及连接轴的限制设置。 凸轮:打开“凸轮从动机构连接”对话框,使用此对话框可创建新的凸轮从动机构,也可编辑或删除现有的凸轮从动机构。 3D 接触:打开“3D接触从动机构连接”对话框,使用此对话框可创建新的3D接触从动机构,也可编辑或删除现有的3D接触从动机构。

实验一MAX+plusII的基本用法 一、实验目的 掌握MAX+plusII的基本用法,了解EDA的设计流程。 二、实验步骤 建立和编辑一个VHDL或者硬件描述语言的工程文件,是数字系统或逻辑电路设计的第一步。下面以8—3译码器设计为例,叙述一下在MAX+ plusII系统中如何来完成一个工程文件的步骤,了解软件的基本使用方法。 1、建立工程目录 建立一个工程目录的主要目的是为了便于管理在系统编译、综合的过程中产生的许多临时文件和附属文件。在Windows操作系统中你想存放该工程的位置建立如:D:\max\test1\等工程目录来存放这个工程所生成的所有文件。通过Windows系统的“开始”菜单进入MAX+plusII集成环境。如图1—1所示: 图1—1 2、建立一个新文件 在图3—1点击“File”选项,如果输入的是新文件,点击子菜单中的“New”出现如 图3—2所示的对话框。在对话框内可供选择的4种编辑 方式为:Graphic Editor file为图形编辑;Symbol Editor file 为符号编辑;Text Editor file为文本编辑;Wavetorm Editor file为波形编辑。 如果用VHDL语言来编辑文件则选择文本编辑, 选取图1—2所示第三项,当该项字符被虚线框框住,并 在该项前面的圆圈中出现一个实心点时,表时该项已被选 中,点击“OK”系统将进入文本编辑状态,屏幕将会出现图1—2 如图1—3所示的编辑窗口。 图1—3

在图3—3所示的编辑窗口中输入你编写的程序,如下列的一串VHDL语句: LIBRARY IEEE USE IEEE.STD_LOGIC_1164.ALL; ENTITY T1 IS PORT( S: IN STD_LOGIC_VECTOR(7 DOWNTO 0); Y: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END T1; ARCHITECTURE A OF T1 IS BEGIN WITH S SELECT Y <= "0000" WHEN "11111110", "0001" WHEN "11111101", "0010" WHEN "11111011", "0011" WHEN "11110111", "0100" WHEN "11101111", "0101" WHEN "11011111", "0110" WHEN "10111111", "0111" WHEN "01111111", "1000" WHEN OTHERS; END A; 对程序进行保存,点击图1—1中图标第 三项,或者点击“File”菜单中的“Save”图1-4 或“Save as”会弹出Save as对话框如图1—4所示。将文件保存为t1.vhd,其所在目录 为以前所设置的工程目录。由VHDL语言的 设定,文件名必须与程序内容里的文件名 一致。 如果想对文件进行修改、编辑或一个文件 已经存在对其进行编辑、修改,可以通过“File” 菜单中的“Open”子菜单会出现如图1—5所 示的对话框选取想修改、编辑的文件进行操 作。 3、选取芯片型号 由于编译、综合结果要生成适用于写可编程器 件的文件,所以在编译以前应选定最终要下载 的芯片型号。在MAX+plusII的工具中,可以 支持的下载芯片有多种,根据所设计的逻辑电 路规模,用户可以自由地进行选择。图1—5 点击主菜单的Assign选项,再点击子菜单中的Device项得到Device对话框,如图1—6所示,利用Device Family框中的上移和下移标志,找到适用的芯片系列。在Device框中选择所需用的芯片型号,点击“OK”确定。图1—6选取的是FLEX10K10系列中的EPF10K10LC84-4。

南京信息工程大学 电子线路实验Ⅱ 课程设计报告 电子与信息工程学院 07通信工程(2)班 姓名: 学号: 2009.6.1 实验题目:用MAX+plusⅡ进行设计和仿真。

实验目的:(1)学习软件的使用方法及VHDL程序的基本语法; (2)用MAX+plusⅡ进行门电路、组合逻辑电路、触发器、 可编程逻辑器件和时序电路等的仿真。 实验内容: 一、MAX+plusⅡ软件的设计流程 1)设计输入 点击新建图标弹出如图1.1所示的新 建文件类型对话框。选取“Text Editor file”使用文本设计方法,在弹出的文本编 辑器中输入VHDL语言是设计代码并存盘, 窗口显示如图1.2. 下面以一个2输入与门的设计为例来描述 这一操作。图1.1 先输入源代码并存盘,文本编辑框效果如图 1.2所示。将此文件保存为and2.vhd。注意保存文件时一定要选择“vhd”的文件后缀,文件名必须与实体名相同。另外,保存该文件的文件夹不能用中文命令,也不能为根目录。这里是新建一个名为example的文件夹来保存and2.vhd文件的。 图1.2 当要打开已存盘的文件时则可点击左上角的,在弹出如图1.3所示Open对话框中“Show in List”栏内,选中要打开的文件类型,再选中VHDL程序所在的文件夹,,在“Files:”框内选中VHDL程序名,这时在“File Name”栏里将显示相应VHDL程序的文件名。点击“OK”按钮,就会弹出要打开的文件窗口。 2)新建一个项目 在编辑并保存VHDL程序后,准备对其编译前,一定要先将该VHDL程序所对应的文件指定为一个项目。新建一个项目的过程如下: 在主菜单中选择“File”→“Project”→“Name…”,打开如图1.4所示的项目名称选择对话框。在对话框“Directories”栏中,选择项目文件所在的

Cad常用命令及使用方法 一、绘图命令 直线:L 用法:输入命令L/回车/鼠标指定第一点/输入数值(也就是指定第二点)/回车(这时直线就画出来了)/回车(结束命令) 射线:RAY 用法:输入命令RAY/回车/鼠标指定射线起点/指定通过点/回车(结束命令) 构造线:XL 用法:输入命令XL/回车/鼠标指定构造线起点/指定通过点/回车(结束命令) 多段线:PL 用法1:同直线命令 用法2:输入命令PL/回车/指定起点/输入W(绘制带有宽度的线)/回车/指定线起点宽度/回车/指定线结束点宽度/回车/输入数值(线的长度值)/回车(结束命令) 正多边形:POL 用法:输入命令POL/回车/指定边数/回车/鼠标指定正多边形的中心点/输入选项(C外切于圆;I内接于圆)/回车/输入半径/回车(结束命令) 矩形:REC 用法1:输入命令REC/回车/鼠标指定第一角点/指定第二角点 用法2:输入命令REC/回车/输入C(绘制带有倒角的矩形)/回车/输入第一倒角值/回车/输入第二倒角值/回车/鼠标指定第一角点/指定第二角点 用法3:输入命令REC/回车/输入F(绘制带有圆角的矩形)/回车/输入圆角半径/回车/指定第一角点/指定第二角点 圆弧:A 用法:输入命令A/回车/指定圆弧起点/指定圆弧中点/指定圆弧结束点 (绘制圆弧的方法有11种,可参考绘图菜单---圆弧选项) 圆:C 用法:输入命令C/回车/鼠标指定圆心/输入半径值/回车(命令结束) (绘制圆的方法有6种,可参考绘图菜单---圆选项) 样条曲线:SPL 用法:输入命令SPL/回车/鼠标指定要绘制的范围即可/需要三下回车结束命令 椭圆:EL

1 打开图形编辑器(graphic editor),双击窗口,就可出现元件选项下拉菜单;在 c:\windows\temporary internet files 中,保存有用户自己编制的元件(实 体); c:\maxplus2\max2lib\prim中,有各类基本门电路及输入/输出端口; c:\maxplus2\max2lib\mf中,有74系列各类数字集成电路 c:\maxplus2\max2lib\mega_lpm中为可调参数库,包括参数化模块,功能 复杂的高级功能模块,如可调模值的计数器,FIFO,RAM等 c:\maxplus2\max2lib\edif中元件的功能和mf库类似 现将常用的prim和mf库中的主要元件罗列如下: c:\maxplus2\max2lib\prim and12 and2 and3 and4 and6 and8 一般与门 band12 band2 band3 band4 band6 band8 输入反向与门 = 或非门 bdir bdirc 双向端口、可控双向端口 bnand12 bnand2 bnand3 bnand4 bnand6 bnand8 输入反向与非门 = 或门 bnor12 bnor2 bnor3 bnor4 bnor6 bnor8 输入反向或非 门 = 与门 bor12 bor2 bor3 bor4 bor6 bor8 输入反向或门 = 与非门

dff dffe 带低电平置位/清零的D触发器,后者带使能端 gnd 接地 input inputc 输入端口 jkff jkffe 带低电平置位/清零的JK触发器,后者带使能端latch D锁存器 nand12 nand2 nand3 nand4 nand6 nand8 与非门nor12 nor2 nor3 nor4 nor6 nor8 或非门 not 反相器 or12 or2 or3 or4 or6 or8 或门 output outputc 输出端口 param 参量 srff srffe 带低电平置位/清零的RS触发器,后者带使能端 tff tffe 带低电平置位/清零的t触发器,后者带使能端 title 标题框 tri 三态门 vcc 正电源 xnor xor 同或、异或 c:\maxplus2\max2lib\mf

附录:Maxplus Ⅱ基本操作方法 ——图形输入法 利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。 MAX+plusII提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM 库。但更为重要的是,MAX+plusII还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。以传统的数字电路实验相比为例,MAX+plusII提供原理图输入设计功能具有显著的优势: ?能进行任意层次的数字系统设计。传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计; ?对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1ns ,因此能发现一切对系统可能产生不良影响的竞争冒险现象; ?通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正; ?能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件; ?通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。 ?如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗; ?符合现代电子设计技术规范。传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。 以下将以一位全加器的设计为例详细介绍原理图输入设计方法,但应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理流程都与文本(如VHDL文件)输入设计完全一致。

设计一般步骤 步骤1:为本项工程设计建立文件夹(自己的U盘且不是根目录); 注意:文件夹名以字母开头不能用中文,且不可带空格。 步骤2:新建设计文件并指向项目 1)菜单File=>New =>对话框中选择=>文本输入(扩展名.vhd)或原理图输入(扩展名.gdf)然后命名(以字母开头不能用中文,且不可带空格); 2)工程项目指向当前的设计文件:菜单File=>Project=>Set Project To Current File 然后选择此项; 步骤3:选择实现器件,放置原理图器件、连线 1)根据所用的实现器件型号(芯片背面)选择:菜单Assign => Device => 对话框中去掉“Show Only Fatest Speed Grades”复选框,实验室所用芯片为EP1K100QC208-3,所以,在DEVICE FAMILY 中选择ACEX1K ,DEVICE 中选择EP1K100QC208-3,选择后点击OK。 2)在原理图编辑界面,空白处右击鼠标=>选Enter Symbol 在出现的对话框中Symbol Name处输入器件代码或打开Symbol Libraries库中mf目录查找器件代码,所选择芯片出现在原理图编辑界面空白处,调整好位置和方向(Windows文档处理方法)。依此放置其他器件:输入管脚input,输出管脚output(需要重新命名:双击管脚再重命名):电源正极Vcc,电源地Gnd等。 3)鼠标左键点击连线起点,拖动到连线终点即可连接,中途改变方向需要在拐弯处松开鼠标左键一次,再拖动连线。 步骤4:编译并纠错 菜单MAX+PlusⅡ=>Compailer编译,有错误时,会出现在信息框中,纠错后再编译直到在编译信息中显示0 Error,有部分Warning不影响编译成功。 步骤5:锁定引脚(该步可省略,由EDA自动分配,但重编译后管脚号可能变动) 菜单Assign=> PIN/Location/Chip,出现的对话框中Node Name栏中直接输入管脚名或单击SEARCH按钮=>出现的对话框中单击LIST按钮=>在NAME IN Database列表中选择欲锁定的端口名,点击OK返回前一对话框。CHIP RESOURSE栏中,选PIN,在左侧下拉列表中点击黑三角选择管脚号,点击ADD按钮,重复以上过程锁定所有引脚,最后点击OK完成锁定。还可以用此步骤改变引脚号。 步骤6:建立仿真文件并设置仿真环境(自信功能正确,步骤6~8可以省去)

附录:Maxplus n基本操作方法 图形输入法 利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。 MAX+plusll提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。但更为重要的是,MAX+plusll还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。以传统的数字电路实验相比为例,MAX+plusIl提供原理图输入设计功能具有显著的优势: *能进行任意层次的数字系统设计。传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计; *对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1 ns,因此能发现一切对系统可能产生不良影响的竞争冒险现象; 通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正; *能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件; ?通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。 ?如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗; 符合现代电子设计技术规范。传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间 的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

Creo原创教程(九),接触碰撞运动仿真解析,引申模具顶针顶出件运动 今天我们来讲一下接触碰撞运动的仿真(这个恐怕是坛子里对凸轮连接最详细的教程)

之前很多人pm还有在qq群问我说做模具顶出件运动怎么做, 我直接回答用凸轮连接对设置连接,启用升离,再启用重力就可以了,这样还是有很多人不太明白,其这个东西听着很简单,里面还有很多的窍门和方法 再加上一些经验,只要你看过了本教程,再加上平时多联系,相信接触碰撞这里,一般的问题都可以解决了,我们来看一下,以前的2001版本以前方针分 析里面比较简单,简单的方针都可以做到,但是到了野火版本以后,功能提升了好多,在野火中有三种特殊的连接,可以设置特殊连接后进行各种分析, 这三种连接分别为凸轮副连接,槽连接,齿轮运动副连接,今天讲的是接触碰撞的仿真,主要用到的是凸轮的链接,所以只讲凸轮,齿轮和槽连接以后再 讲。 顶针顶出件运动仿真,其实就是在顶针头部和接触的件之间建立一个凸轮连接,有人会问,顶针和件是两个平面与平面相碰,怎么建立凸轮,在凸轮连接 时,里面有一些技巧,尤其是建立曲面和选择曲面时,技巧性比较强,相信很多高手有些时候都那凸轮连接因没有选择好曲面或是没有建立好曲面,导致 仿真多次失败。 我们先看一下凸轮的链接设置

1 “凸轮1”选项卡:定义第一个凸轮 (1)“曲面/曲线”:单击箭头选取曲线或曲面定义凸轮工作面,在选取曲面时若钩选自动 选取复选框则系统自动选取与所选曲面相邻的任何曲面,凸轮与另一凸轮相互作用的 一侧由凸轮的法线方向指示。如果选取开放的曲线或曲面,会出现一个洋红色的箭头, 从相互作用的侧开始延伸,指示凸轮的法向。 选取的曲线或边是直的,“机械设计模块”会提示选取同一主体上的点、顶点、平面实 体表面或基准平面以定义凸轮的工作面。所选的点不能在所选的线上。工作面中会出现 一个洋红色箭头,指凸轮法向。

数字电子技术综合实验 ---------MAX+PLUS II快速入门 MAX+PLUS II是Altera公司的全集成化可编程逻辑设计环境。它的界面友好,在线帮助完备,初学者也可以很快学习掌握。完成高性能的设计。另外,在进行原理图输入时,可以直接放置74系列逻辑芯片,所以对于普通爱好者来说,即使不使用Altera的可编程器件,也可以把MAX+PLUS II作为逻辑仿真工具,不用搭建硬件电路,即可对自己的设计进行调试,验证。下面以具体实例介绍MAX+PLUS II V10.0的使用。 功能 ?MAX+PLUS II的编译核心支持Altera的FLEX 10K、FLEX 8K、MAX9000、MAX7000、FLASHlogic、MAX5000、Classic系列可编程逻辑器件; ?MAX+PLUS II的设计输入、处理与校验功能一起提供了全集成化的一套可编程逻辑开发工具,可加快动态调试,缩短开发周期; ?MAX+PLUS II支持各种HDL设计输入,包括VHDL、V erilog和Altera的AHDL; ?MAX+PLUS II可与其他工业标准设计输入、综合与校验工具链接。与CAE工具的接口符合EDIF200和209、参数化模块库(LPM)、V erilog、VHDL及其它标准。 设计者可使用Altera或标准CAE设计输入工具去建立逻辑设计,使用MAX+PLUS II编译器对Altera器件设计进行编译,并使用Altera或其它CAE校验工具进行器 件或板级仿真。MAX+PLUS II支持与Synopsys、Viewlogic、Mentor Graphics、Cadence、Exemplar、Data I/O、Intergraph、Minc、OrCAD等公司提供的工具接口;

Max Plus II 操作指导 汪原 计算机与通信学院实验中心 2008年11月

前言 Maxplus II 是目前比较流行的数字系统设计软件,由Altera公司根据他们的可编程硬件产品FPGA/CPLD开发出来的集成设计平台, 该软件的功能有:逻辑电路设计、电路输入输出仿真、自动完成逻辑电路编程,并将编程代码下载到FPGA/CPLD硬件中,实现了灵活的电路设计,就可获得可靠的,且满足设计要求的逻辑器件。 注释: FPGA —— Field Programmable Gate Array,现场可编程门阵列。 CPLD —— Complex Programmable Logic Device,复杂可编程逻辑器件。 Altera公司的FPGA/CPLD有以下系列:Classic、ACEX1K、MAX5000、MAX7000、MAX9000、FLEX6000、FLEX8000、FLEX10K、FLASHLogic等。在Maxplus II的Device列表中包含了以上系列的器件。 实验任务: 1、在图形编辑区通过逻辑图设计逻辑电路,再利用波形编辑区进行逻辑功能仿真,以此验证电路的逻辑功能是否正确。 2、在文本编辑区使用VHDL硬件描述语言设计逻辑电路,再利用波形编辑区进行逻辑功能仿真,以此验证 目录 第一章Maxplus II的安装 第二章介绍Maxplus II §2.1 工作主界面 §2.2 逻辑设计编辑区 §2.3 内附逻辑函数库 §2.4 工具栏 第三章或非门NOR设计范例 §3.1 使用逻辑图设计NOR §3.2 使用VHDL设计NOR

第一章Maxplus II的安装 一、Maxplus II V10.1 安装软件包括以下文件: 二、安装流程:打开→打开→双击→进入安装 安装结束后, 在目标地址产生三个 文件夹, 进入Maxplus工作界面的图标放在Maxplus2文件夹中,你也可以从Windows开始菜单 栏上的图标进入工作界面,但要进入编辑区时却被一条信息拦阻,因为需要安装软件运行执照(License)。 三、执照(License)安装:合法的安装途径是到www . https://www.doczj.com/doc/3815690496.html,注册下载。 给同学们提供的安装软件携带了License文件,它放在补丁文件夹中。可以用两种方法安装License: 一种是将补丁 中的文件复制到 Maxplus2文件夹 中,双击Updata to 10.12文件夹内的图标和图标以激活编辑器。 另一种是从工作主界面的菜单栏,如图1-1所示,进入Options(选择)下拉菜单,选取License setup…,打开License setup对话框,如图1-2所示,由Browse找到License所在的路径,加入到License File or Server Name 输入框中,点击OK即可。

iFFF-r-F-FFF F-=. FXF —…八扌彳-FFFFF-* - F.-F- - - = *XFXF* ""'常用基本操作 1常用工具栏的打开和关闭:工具栏上方点击右键进行选择 2动态坐标的打开与关闭:在左下角坐标显示栏进行点击 3对象捕捉内容的选择:A在对象捕捉按钮上右键点击(对象捕捉开关:F3) B在极轴选择上可以更改极轴角度和极轴模式(绝对还是相对上一段线) 4工具栏位置的变化:A锁定:右下角小锁;工具栏右键 B锁定情况下的移动:Ctrl +鼠标移动 5清楚屏幕(工具栏消失):Ctrl + 0 6隐藏命令行:Ctrl + 9 7模型空间和布局空间的定义:模型空间:无限大三维空间布局空间:图纸空间,尺寸可定义的二位空间 8鼠标左键的选择操作:A从左上向右下:窗围 B从右下向左上:窗交 9鼠标中键的使用:A双击,范围缩放,在绘图区域最大化显示图形 B按住中键不放可以移动图形 10鼠标右键的使用:A常用命令的调用 B绘图中Ctrl + 右键调出捕捉快捷菜单和其它快速命令 11命令的查看:A常规查看:鼠标移于工具栏相应按钮上查看状态栏显示B命令别名(缩写)的查看:工具—自定义—编辑程序参数(acad.pgp)12绘图中确定命令的调用:A鼠标右键B ESC键(强制退出命令) C Enter键D空格键(输入名称时,空格不为确定) 13重复调用上一个命令:A Enter键B空格键C方向键选择 14图形输出命令:A wmfout (矢量图)B jpgout/bmpout (位图)应先选择输出范围 15夹点的使用:A蓝色:冷夹点B绿色:预备编辑夹点C红色:可编辑夹点D可通过右键选择夹点的编辑类型

实验一Maxplus软件的基本操作 一、实验目的 1.熟悉Maxplus软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计) 2.用逻辑图和VHDL语言设计一个异或门。 二、实验内容 1.用VHDL语言设计一个异或门 2.用Maxplus软件仿真波形图 3.设计芯片 三、实验方法 1.启动Maxplus II 2.新建一个文本编辑文件,输入异或设计的VHDL语言 3.编译。点击file→save as,保存文件名为entity名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并编译,出现0 error,0 warnings则编译通过。 4.仿真波形。点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plus II→Simulator,即可仿真出输出的波形。 5.设计芯片。点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上 (a:88,b:89,c:12),点Max+plus II→programmer→configuer,然后就可以操作试验箱,观察异或门的工作情况。 四、实验过程 异或门(XOR) 用途:异或门是一种用途广泛的门电路。典型应用是作为加法器的单元电路。

逻辑图 真值表 A B OUT 0 0 0 0 1 1 1 0 1 1 1 0 VHDL程序 数据流描述: 波形图 芯片引脚分配

MAXPLUS2基本元件库 打开图形编辑器(graphic editor),双击窗口,就可出现元件选项下拉菜单; 在c:\windows\temporary internet files 中,保存有用户自己编制的元件(实体); 在c:\maxplus2\max2lib\prim中,有各类基本门电路及输入/输出端口; c:\maxplus2\max2lib\mf中,有74系列各类数字集成电路 c:\maxplus2\max2lib\mega_lpm中为可调参数库,包括参数化模块,功能复杂的高级功能模块,如可调模值的计数器,FIFO,RAM等 c:\maxplus2\max2lib\edif中元件的功能和mf库类似 现将常用的prim和mf库中的主要元件罗列如下: c:\maxplus2\max2lib\prim and12 and2 and3 and4 and6 and8 一般与门 band12 band2 band3 band4 band6 band8 输入反向与门= 或非门 bdir bdirc 双向端口、可控双向端口 bnand12 bnand2 bnand3 bnand4 bnand6 bnand8 输入反向与非门= 或门 bnor12 bnor2 bnor3 bnor4 bnor6 bnor8 输入反向或非门= 与门 bor12 bor2 bor3 bor4 bor6 bor8 输入反向或门= 与非门 carry cascade globol exp icell mcell opndrn sclk soft wire constant 常量gnd 接地latch D锁存器 dff dffe 带低电平置位/清零的D触发器,后者带使能端 input inputc 输入端口 jkff jkffe 带低电平置位/清零的JK触发器,后者带使能端 nand12 nand2 nand3 nand4 nand6 nand8 与非门 nor12 nor2 nor3 nor4 nor6 nor8 或非门 not 反相器 or12 or2 or3 or4 or6 or8 或门 output outputc 输出端口param 参量 srff srffe 带低电平置位/清零的RS触发器,后者带使能端 tff tffe 带低电平置位/清零的t触发器,后者带使能端 title 标题框tri 三态门vcc 正电源 xnor xor 同或、异或 c:\maxplus2\max2lib\mf 161mux 16选1 * 81mux 16cudslr 16cudslr 16位计数/移位* 16dmux 16ndux 4-16 译码器* 21mux 2选1 * 2x8mux 8位2选1 * 4count 4位计数器* 74系列电路的分类: “74”指的是商用器件,“54”是军用的,它们的适用温度范围不同,军用的范围大。商用:0℃~70℃;军用:-55℃~125℃。 LS等是子系列的名称。L:低功耗H:高速S:肖特基LS:低功耗消特基ALS:先进低功耗肖特基AS:先进肖特基LS:低功耗消特基 简单门电路 7400 4nand2 7402 4nor2 7404 6not 7408 4and 7410 3nand3

Max+plusⅡ系统的操作简介 Max+plusⅡ开发工具是美国Altera公司自行设计的一种软件工具,其全称为Multiple Array Matrix and Programmable Logic User System。它具有原理图输入和文本输入(采用硬件描述语言)两种输入手段,利用该工具所配备的编辑、编译、仿真、综合、芯片编程等功能,将设计电路图或电路描述程序变成基本的逻辑单元写入到可编程的芯片中(如FPGA芯片),作成ASIC芯片。它是EDA设计中不可缺少的一种工具。 通过一个简单的二输入与门电路设计范例介绍:利用Max+plusⅡ系统 (1)如何编写VHDL程序(使用Text Editor); (2)如何编译VHDL程序(使用Compiler); (3)如何仿真验证VHDL程序(使用Waveform Editor,Simulator); (1)建立和编写一个VHDL语言的工程文件 首先启动Max+plusⅡ系统,启动后系统进入主菜单画面,在主菜单上有5个选项,分别是:Max+plusⅡ、File、Assign、Options和Help。 Max+plusⅡ系统主窗口 (a)打开文本编辑器;用鼠标点击File选项,点击子菜单中的New选项,接着屏幕会出现New的对话框。在对话框内有4种编辑方式:图形编辑、符号编辑、文本编辑和波形编辑。VHDL文件属于文本,那么应该选择文本编辑方式,点击OK按钮,屏幕上将出现一个无名的编辑窗口,则系统进入文本编辑状态。(或用鼠标点击Max+plusⅡ选项,点击子菜单中Text Editor选项.。)

打开文本编辑器 (b)在编辑窗口中进行编辑输入,输入相应的描述语句。 文本编辑窗口中编辑输入[例1] 实现2输入与门的VHDL描述 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY and2 IS PORT(a, b : IN STD_LOGIC; y: OUT STD_LOGIC); END and2; ARCHITECTURE one OF and2 IS BEGIN y<= a and b; END one;