第5章可编程逻辑器件系统设计制作训练

内容提要

在电子竞赛设计中,可编程逻辑器件作为系统的控制核心已广泛应用。本章介绍了FPGA 最小系统、FPGA最小系统配置电路等设计制作,Modelsim仿真工具使用,FPGA的最小系统板的下载,常见错误及其原因分析及编程技巧。

知识要点: FPGA最小系统、配置,仿真工具,FPGA的下载,编程错误,编程技巧。教学建议: 本章的重点是掌握FPGA最小系统的设计与制作,仿真与程序设计技巧中。建议学时数为8学时。FPGA最小系统在竞赛中可以选用成品。但FPGA作为竞赛作品中的核心部件,软件编程训练可以利用FPGA开发系统进行培训,通过对FPGA最小系统硬件的设计制作,可以使学生加深对FPGA系统的了解。仿真工具、编程技巧是训练的重点。设计制作的产品可以作为子系统或者模块保留备用。训练中要求学生完成电原理图、印制板图、装配图、实际制作、电路调试、设计总结报告。

5.1 FPGA最小系统的设计制作

5.1.1 Xilinx公司的FPGA器件

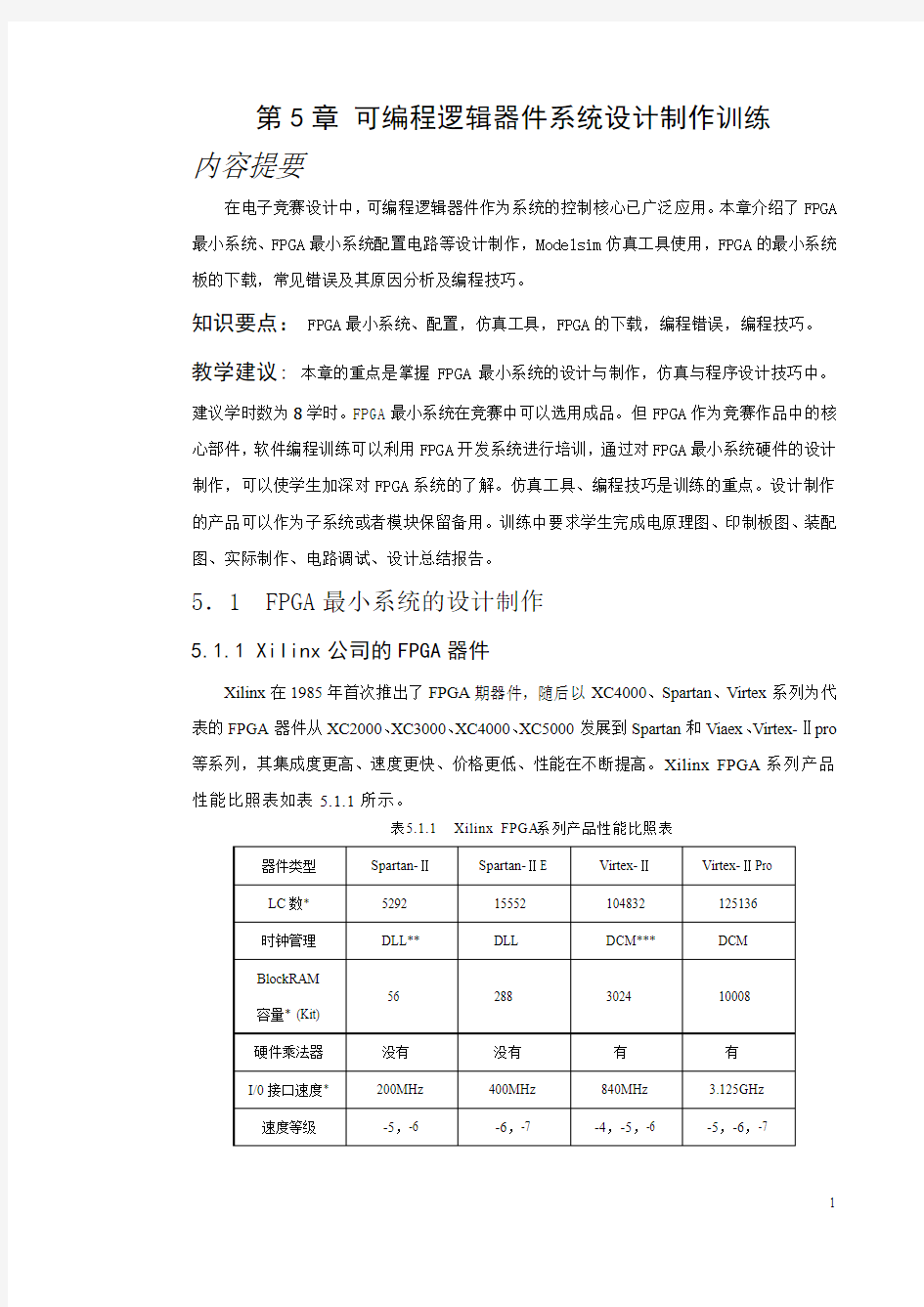

Xilinx在1985年首次推出了FPGA期器件,随后以XC4000、Spartan、Virtex系列为代表的FPGA器件从XC2000、XC3000、XC4000、XC5000发展到Spartan和Viaex、Virtex-Ⅱpro 等系列,其集成度更高、速度更快、价格更低、性能在不断提高。Xilinx FPGA系列产品性能比照表如表5.1.1所示。

表5.1.1 Xilinx FPGA系列产品性能比照表

*表中所列LC数量、BlockRAM容量、I/0接口速度均为最大值。

**DLL表示数字延迟锁相环(Delay-Locked Loop)。

***DCM表示数字时钟管理器(Digital Clock Manager)。

1. Virtex器件系列FPGA

(1)Virtex和Virtex-E系列FPGA

Xilinx推出的Virtex系列FPGA产品是Xilinx 现场可编程平台门阵列(Platform FPGA)的第一套产品。该系列器件是高速、高密度的FPGA。系统门数从5万到100万,最高时钟频率可以达到200MHz,工作电压为2.5V,采用5层金属、0.22Fm的CMOS工艺制造。主要特点是灵活的内部结构,可以兼顾速度和集成度。作为Virtex的改进型,Virtex-E采用了0.18gm、6层金属布线工艺,系统门数从5.8万门到400万门工作电压为1.8V,集成度更高,功耗更低;Virtex-E拥有先进的SelectRAM存储体系,有IMbit的片内分成式RAM和最高可达832Kbk 的片内块状RAM,可真正实现双口块RAM。存储器带宽可以达到1.66TBps。Xilinx于2001年1月正式发布了最新的Virtex-Ⅱ器件,其集成度更高,能够达到近千万系统门,在时钟管理上也采用了一些新的挂术,封装采用了BGA封装。

(2) Virtex-Ⅱ系列FPGA

Virtex-Ⅱ系列产品是Xinlinx公司在Virtex-E系列产品后推出的新型高端FPGA,该系列元件采用业界第一套数位控制阻抗技术(DCI)解决关键性的设计问题,例如高复杂度电路板布局、讯号扭曲等。Virtex-Ⅱ系列产品采用0.15μm和0.12μm混合工艺设计,内核电压为1.5V,支持多种接口标准,内部时钟频率可达420MHz。

Virtex-Ⅱ系列产品主要由CLB、IOB、BlockRAM、DCM和乘法器等组成。其中,CLB 模块用于实现FPGA的大部分逻辑功能,IOB模块用于提供封装管脚与内部逻辑之间的接口,BlockRAM用于实现FPGA内部的随机存取,DCM用于提供灵活的时钟管理,乘法器用于提高FPGA的数字运算速度。

Virtex-Ⅱ系列元件具备位元流加密功能,全面保障设计的安全性。此功能应用安全的三重数据加密标准(DES)演算法将位元流编码加密,加密演算所使用的密钥是透过IEEE 1149.1(JTAG)介面来提供,使用电池或其他恒定电源供应器将密钥储存于晶片中。加密之后的位元流可使用解密专用的密钥库(key bank)载入FPGA元件中。这项功能全面提升设计的安全性,避免设计遭人窃用,为IP供应商提供全新的商务模式。

Virtex-Ⅱ系列产品与Xilinx公司以前推出的FPGA产品相比较,其内部结构有了较大的改进,这主要包括:

①Virtex-Ⅱ内部的CLB模块含有4个Slice,从而提高了Virtex-Ⅱ系列产品的逻辑

容量和资源利用率。

②Virtex-Ⅱ内嵌专用乘法器电路,从而提高了Virtex-Ⅱ系列产品进行数字信号处理

的速度。

③Virtex-Ⅱ内嵌更大容量的BlockRAM,用于适应当前设计对大容量片内存储的要

求。

④Virtex-Ⅱ将DLL改为数字时钟管理器(DCM,Digitsl Clock Manager),从而提供

更灵活的时钟解决方案。

⑤Virtex-Ⅱ支持更多的I/O接口标准,主要包括LVTTL、LVCMOS(3.3V、2.5V、

1.8V、1.5V)、PCI(3V,33MHz/66MHz)、PCI-X、GTL、GTLP、AGP、AGP-2X、

HSTL(Ⅰ、Ⅱ、Ⅲ、Ⅳ)、SSTL3、SSTL2、LVDS(3.3V、2.5V)、LVPEFCL、LVDSEXT(3.3V、2.5V)、BLVDS、ULVDS和LDT。

⑥Virtex-Ⅱ采用数控阻抗匹配(DCI,Digitally Controlled Impedance)技术,从而减小

因阻抗匹配问题而造成的系统不稳定性。

⑦Virtex-Ⅱ内部含有更加丰富的布线资源,从而保证FPGA逻辑资源的最大利用率。

⑧Virtex-Ⅱ支持配置数据的三重加密,从而最大限度保护设计者的知识产权。(3)Virtex-ⅡPro系列FPGA

Virtex-ⅡPro系列产品采用Xilinx公司成熟的Virtex-Ⅱ架构,主要由PowerPC405处理器模块、RocketIO TM多吉比特收发器、CLB、IOB、BlockRAM、DCM和乘法器组成,其中,CLB、IOB、BlockRAM、DCM和乘法器的内部结构和使用方法与Virtex-Ⅱ系列产品完全一致。

2. Spartan器件系列FPGA

(1)SpartanⅡ器件系列

SpartanⅡ器件是以Virtex器件的结构为基础发展起来的第二代高容量的FPGA,集成度可以达到15万门,系统速度可达200MHz,能达到ASIC的性价比。SpartanⅡ器件的工作电压为2.5V,采用0.22μm/18μm CMOS工艺,6层金属连线制造。

(2)Spartan-XL器件

Spartan和Spartan-XL器件的性能指标如表5.1.2所示。

表5.1.2 Spartan和Spartan-XL器件的性能指标

(3) Spartan-ⅡE系列产品

Spartan-ⅡE系列产品主要技术参数如表5.1.3所示。

表5.1.3 Spartan-ⅡE系列产品主要技术参数

Spartan-ⅡE系列产品采用成熟的Virtex-E架构,主要由可配置逻辑模块(CLB,Configurable Logic Block)、输入输出接口模块(IOB,Input/Output Block)、BlockRAM和数字延迟锁相环(DLL,Delay-Locked Loop)组成,如图5.1.1所示。用户可编程门阵列由五个主要的可编程部分组成。

①输入输出模块(IOB)提供封装引脚和内部逻辑之间的接口;

②可配置逻辑模块(CLB)提供构造主要逻辑所需的功能(函数)部件;

③专用的每个有4096个位的块RAM存储器;

④用来补偿时钟发送延时的数字延迟锁相环(Clock DLL)和区域时钟控制;

⑤通用多级互连结构。

图5.1.1 Spartan-IIE系列FPGA功能块图表

如图5.1.1所示,其中,BlockRAM用于实现FPGA内部数据的随机存取,DLL用于FPGA 内部的时钟控制和管理。CLB用简单的路径连到所有支持和路由选择结构来形成主要的逻辑结构,用于实现FPGA的大部分逻辑功能。IOB用于提供封装管脚与内部逻辑之间的接口,位于所有逻辑单元和存储元件的周围,以便简单快速地选择信号路径来打开和关闭芯片。编程数据存放在静态存储单元中,来控制所有可编程逻辑元件和互连资源。当电源打开(POWER-UP)时数据被装载到存储单元中,如果有必要改变硬件的功能可以重新装载。下面将具体介绍每一个元件。

Spartan-ⅡE的输入输出模块如图5.1.2所示,Spartan-IIE的IOB特性化输入输出支持I/O信号标准的多样化。这些高速输入输出能支持动态存储器和总线接口的多种状态。三个IOB寄存器可做边沿触发的D触发器或是电平触发的锁存器。每一个IOB有一个被三个寄存器所共用的时钟信号(CLK)和一个每一个寄存器所独立拥有的使能时钟信号(CE)。

除了CLK和CE控制信号以外,三个寄存器共用一个置位/复位(SR)信号。对于每一个寄存器,这一信号可独立地设置成同步置位、同步复位、异步Preset或异步清零。每一个用户I/O底座都连接有可选择的上拉和下拉电阻和一个可选择的弱保持电路。在编程(设置)以前,所有的没有被编程的输出将强行进入高阻状态。下拉电阻和弱保持电路不动作,但是

计算机与信息学院 《系统硬件综合设计》 课程设计报告 学生姓名:李 学号: 1234567890 专业班级:计算机 2017 年 07 月 01日

一、实验原理及设计 本次试验我主要根据上图进行理解和编程,起先参考了5个基础实验,期间又翻阅了自己动手写cpu,并且在网上查了很多资料,下面我将对该图做出我的理解和设计: 1.pcf部分 always @(posedge Clk) begin PCPlus4F_Reg = PCPlus4F; if (BranchM&ZeroM) PCF = PCBranchM; else PCF = PCPlus4F; InstructionF_Reg = InstructionF; if (InstructionF[31:26] == 6'b000010) begin PCF = {6'h0,InstructionF[25:0]}; PCF = PCF << 2; end End assign PCPlus4F = PCF + 4; assign ImemRdAddrF = PCF; 每个时钟上升沿到来,根据上一个时钟的PCSrcM判断是否为分支指令,若是,则选择PCBranchM作为这个时钟的指令地址,否则选PCF+4作为这个指令的指令地址,另外对于J类指令,我设计了一个特定的OpCode==“000010”,即为跳转指令,因为每个指令以字节格式存储,占用,4个字节,故将后26位立即数进行位扩展后将其左移两位,效果等同于乘4,再将其赋值给PCF,这样下一跳的指令地址即为所要跳转的地址。对于这个部分,我起先是准备将其设计成一个模块的,之后由于模块接口连接时出现了无法解决的错误:输出PCF要作为Instruction Memory的输入,又要作为自身模块下一跳的输入,导致三者关联一起变化,程序报错,后来我又想到将PCF的输出改成两个,PCFout 及PCFnext,PCFout作为Instruction Memory的输入,PCFnext作为自身模块下一跳的输入,但是程序仍无法正常运行,最后我想到了在top模块中对PCF进行处理并得以实现。

单片机最小系统设计 时间:2011-05-01 22:47:54 来源:作者: 单片机最小系统设计 该单片机最小系统具有的功能: (1)具有2位LED数码管显示功能。 (2)具有八路发光二极管显示各种流水灯。 (3)可以完成各种奏乐,报警等发声音类实验。 (4)具有复位功能。 功能分析 (1)两位LED数码管显示功能,我们可以利用单片机的P0口接两个数码管来现这个功能;(2)八路发光二极管显示可以利用P1口接八个发光二极管实现这个功能; (3)各种奏乐、报警等发声功能可以采用P2.0这个引脚接一蜂鸣器来实现。 (4)利用单片机的第9脚可以设计成复位系统,我们采用按键复位;利用单片机的18、19脚可以设计成时钟电路,我们利用单片机的内部振荡方式设计的。 设计框图 硬件电路设计 根据本系统的功能,和单片机的工作条件,我们设计出下面的电路图。

元件清单的确定: 数码管:共阴极2只(分立) 电解电容:10UF的一只 30PF的电容2只 220欧的电阻9只 4.7K的电阻一只 1.2K的电阻一只 4.7K的排阻一只, 12MHZ的晶振一只 有源5V蜂名器一只 AT89S51单片机一片 常开按钮开关1只 紧锁座一只(方便芯取下来的,绿色的) 发光二极管(5MM红色)8只 万能板电路版15*17CM S8550三极管一只 4.5V电池盒一只,导线若干。七、硬件电路的焊接 按照原理图把上面的元件焊接好,详细步骤省略。 相关程序编写 针对上面的电路原理图,设计出本单片机最小系统的详细功能:(1)、第一个发光二极管点亮,同时数码管显示“1”。 (2)、第二个发光二极管点亮,同时数码管显示“2”。 (3)、依次类推到第八个发光二极管点亮,同时数码管显示“8”。以上出现的是流水灯的效果 (4)、所有的发光二极管灭了,同时数码管现实“0”。

计算机与信息学院 系统硬件综合设计》 课程设计报告 学生姓名:李 学号:1234567890 专业班级:计算机 2017 年07 月01 日

1.pcf 部分 always @(posedge Clk) begin PCPlus4F_Reg = PCPlus4F; if (BranchM&ZeroM) PCF = PCBranchM; else PCF = PCPlus4F; InstructionF_Reg = InstructionF; if (InstructionF[31:26] == 6'b000010) begin PCF = {6'h0,InstructionF[25:0]}; PCF = PCF << 2; end End assign PCPlus4F = PCF + 4; assign ImemRdAddrF = PCF; 每个时钟上升沿到来,根据上一个时钟的PCSrcM判断是否为分支指令,若是,则选择 PCBranchM作为这个时钟的指令地址,否则选PCF+4作为这个指令的指令地址,另外对于J 类指令,我设计了一个特定的OpCode=“= 000010”,即为跳转指令,因为每个指令以字节格式存储,占用,4 个字节,故将后26 位立即数进行位扩展后将其左移两位,效果等同于乘4,再将其赋值给PCF,这样下一跳的指令地址即为所要跳转的地址。对于这个部分,我起先是准备将其设计成一个模块的,之后由于模块接口连接时出现了无法解决的错误:输出PCF要作为Instruction Memory 的输入,又要作为自身模块下一跳的输入,导致三者关联一起变化,程序报错,后来我又想到将PCF的输出改成两个,PCFout 及PCFnext,PCFout 作为Instruction Memory的输入,PCFnext 作为自身模块下一跳的输入,但是程序仍无法正常运行,最后我想到了在top 模块中对PCF进行处理并得以实

单片机最小系统的设计与制作 江西冶金职业技术学院刘昆山刘星慧 【摘要】本文通过讲解单片机的工作条件,设计并制作单片机最小系统,编写单片机C语言程序,调试单片机产品,掌握单片机产品开发的基本过程。 【关键字】单片机C语言,单片机入门,单片机最小系统 一、单片机最小系统功能介绍 单片机最小系统,或者称为最小应用系统,是指用最少的元件组成的以单片机为核心元件的可以正常工作的具有特定功能的单片机系统,是单片机产品开发的核心电路。

图1单片机最小系统成品图 本制作采用单片机C语言编程,主要能完成单灯闪烁的任务,通过AT89S51单片机控制一个LED的亮与灭,实现闪烁现象。同时应具有上电复位和手动复位,并且使用单片机片内程序存储器存放用户程序。 二、知识点讲解 1、AT89S51单片机简介 AT89S51是美国ATMEL公司生产的低功耗,高性能CMOS 8位单片机,片内含4K 的可系统编程的Flash只读程序存储器,器件采用ATMEL公司的高密度、非易失性存储器技术生产,兼容标准8051指令系统及引脚。它集成的Flash程序存储器既可在线编程(ISP),也可用传统方法进行编程。 单片机的应用可以理解为是单片机芯片通过其引脚控制各种不同的外围电路,实现各种具体功能,所以要学好单片机技术,必须先了解单片机的引脚功能。AT89S51采用了40引脚的双列直插DIP封装形式,实物图如图2所示,引脚配置图如图3图4所示。

图2 AT89S51实物图图3 AT89S51引脚图 图4 AT89S52引脚图 2、引脚功能介绍 IO口灌(流进)电流大,拉(流出)电流小。

P0:漏极开路的双向IO口,使用时,当电流流出需外加上拉电阻 外部地址数据总线,可带八个TTL负载 P1:准双向口(当作输入口用时,须将IO口置1(P1=0XFF;i=P1;)),可带四个TTL负载 P1.0:T2定时计数器2的外部脉冲输入及时钟输出 P1.1:T2EX定时计数器2的捕捉、自动重装的触发输入及减法计数控制 P1.5:MOSI,主动输出从动输入引脚,用于flash(闪存)编程 P1.6:MISO, 主动输入从动输出引脚,用于flash编程 P1.7:SCK, 同步时钟,用于flash编程 ISP编程时用 P2:准双向口,可带四个TTL负载 外部地址总线高八位 P3:准双向口,可带四个TTL负载 P3.0:RXD,串行输入 P3.1:TXD,串行输出 P3.2:INT0,外部中断0输入 P3.3:INT1,外部中断1输入 P3.4:T0,定时计数器0的外部脉冲输入

XilinxFPGA引脚功能详细介绍 注:技术交流用,希望对大家有所帮助。 IO_LXXY_# 用户IO引脚 XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank号 2.IO_LXXY_ZZZ_# 多功能引脚 ZZZ代表在用户IO的基本上添加一个或多个以下功能。 Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。配置完成后,这些引脚又作为普通用户引脚。 D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。 D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。 An:O,A[25:0]为BPI模式的地址位。配置完成后,变为用户I/O口。 AW AKE:O,电源保存挂起模式的状态输出引脚。SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。除非SUSPEND模式被使能,AWAKE被用作用户I/O。 MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。 FCS_B:O,BPI flash 的片选信号。 FOE_B:O,BPI flash的输出使能信号 FWE_B:O,BPI flash 的写使用信号 LDC:O,BPI模式配置期间为低电平 HDC:O,BPI模式配置期间为高电平 CSO_B:O,在并口模式下,工具链片选信号。在SPI模式下,为SPI flsah片选信号。 IRDY1/2,TRDY1/2:O,在PCI设计中,以LogiCORE IP方式使用。 DOUT_BUSY:O,在SelectMAP模式下,BUSY表示设备状态;在位串口模式下,DOUT 提供配置数据流。 RDWR_B_VREF:I,在SelectMAP模式下,这是一个低电平有效的写使能信号;配置完成后,如果需要,RDWR_B可以在BANK2中做为Vref。 HSW APEN:I,在配置之后和配置过程中,低电平使用上拉。 INIT_B:双向,开漏,低电平表示配置内存已经被清理;保持低电平,配置被延迟;在配置过程中,低电平表示配置数据错误已经发生;配置完成后,可以用来指示POST_CRC 状态。 SCPn:I,挂起控制引脚SCP[7:0],用于挂起多引脚唤醒特性。 CMPMOSI,CMPMISO,CMPCLK:N/A,保留。 M0,M1:I,配置模式选择。M0=并口(0)或者串口(1),M1=主机(0)或者从机(1)。 CCLK:I/O,配置时钟,主模式下输出,从模式下输入。 USERCCLK:I,主模式下,可行用户配置时钟。 GCLK:I,这些引脚连接到全局时钟缓存器,在不需要时钟的时候,这些引脚可以作为常规用户引脚。 VREF_#:N/A,这些是输入临界电压引脚。当外部的临界电压不必要时,他可以作为

┊ ┊┊┊┊┊┊┊┊┊┊┊┊装┊┊┊┊┊订┊┊┊┊┊线┊┊┊┊┊┊┊┊┊┊┊┊┊ 摘要 近年来随着计算机在社会领域的渗透, 单片机的应用正在不断地走向深入,同时带动传统控制检测日新月益更新。在实时检测和自动控制的单片机应用系统中,单片机往往是作为一个核心部件来使用,仅单片机方面知识是不够的,还应根据具体硬件结构,以及针对具体应用对象特点的软件结合,以作完善。 单片机最小系统是在以51单片机为基础上扩展,使其能更方便地运用于测试系统中。本设计主要在51单片机上扩展I/O口,扩展定时器定时范围,扩展键盘显示接口并写好底层程序。 关键词最小系统,扩展,STC89C51, I/O接口 Abstract With the infiltration in the social field of the computer in recent years, the application of the one-chip computer is moving towards deepening constantly, drive tradition is it measure crescent benefit to upgrade day to control at the same time. In measuring in real time and automatically controlled one-chip computer application system, the one-chip computer often uses as a key part, only one-chip computer respect knowledge is not enough, should also follow the structure of the concrete hardware , and direct against and use the software of target’s characteristic to combine concretly, in order to do perfectly. The smallest system one chip computer is in expands at the base of MCS-51 one chip computer. Make it used more convient in the test system. this design mainly expands I/O in the take 51 on chip computer, expands the timer fixed time scope, expands the keyboard to demonstrate the connection and writes the

单片机最小系统板使用说明书WW-S-51 V1.0 作者:陈永德 版本:1.0

结论

第一章单片机最小系统板介绍 图1.1 单片机最小系统板实物图 图1.2 单片机最小系统板器件分配图 在单片机的引脚外围固定的引脚,如VCC(40),GND(20)已经正确固定到电源

和地上。X1(18),X2(19(是接晶振的引脚已经外接到11.0592MHZ和30P的电容。RST(9)是单片机的复位引脚,通过RC回路,作为单片机的上电复位。 作为P3口的第二功能端口,P3.0(10),P3.1(11)为单片机的通信引脚,和MAX232芯片连接。方便在下载程序时,只要上电复位即可完成下载的硬件操作。 另外,为了提高P0口的驱动能力,在P0口的各引脚上接了上拉电阻5.1K 到电源Vcc5V。 采用一片MAX232,为RS232与TTL电平的转换,使得可以方面使用电脑的COM口,对单片机进行程序的烧录。 在电路中总共分为四个模块:电源模块、通讯模块、人机接口模块、主控模块。 电源模块: 图1.3 电源模块电路图 通讯模块: 电脑与单片机的通讯采用了MAX232,实现RS232的电平到单片机的TTL电平转换。它的外围电路仅采用4只0.1uF的瓷片电容,作为倍升电压储存。其内部集成了两组电平转换。在此设计中只采用一组。它的连线向电脑端连接RS232端口的2,3引脚。作为数据的传输。还有一根地线(5引脚)。另一边与单片机的Rx,Tx相连。 图1.4 通信模块原理图 人机接口模块: (1)发光二极管在电路中设计了8个共阳极的发光二极管,一般作为对I/O 信号的指示,与检验作用。在发光二极管支路上连接了一个1K的排阻。

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

单片机硬件系统设 计原则 1

单片机硬件系统设计原则 一个单片机应用系统的硬件电路设计包含两部分内容:一是系统扩展,即单片机内部的功能单元,如ROM、RAM、I/O、定时器/计数器、中断系统等不能满足应用系统的要求时,必须在片外进行扩展,选择适当的芯片,设计相应的电路。二是系统的配置,即按照系统功能要求配置外围设备,如键盘、显示器、打印机、A/D、D/A转换器等,要设计合适的接口电路。 系统的扩展和配置应遵循以下原则: 1、尽可能选择典型电路,并符合单片机常规用法。为硬件系统的标准 化、模块化打下良好的基础。 2、系统扩展与外围设备的配置水平应充分满足应用系统的功能要求,并留有适当余地,以便进行二次开发。 3、硬件结构应结合应用软件方案一并考虑。硬件结构与软件方案会产生相互影响,考虑原则是:软件能实现的功能尽可能由软件实殃,以简化硬件结构。但必须注意,由软件实现的硬件功能,一般响应时间比硬件实现长,且占用CPU时间。 2

4、系统中的相关器件要尽可能做到性能匹配。如选用CMOS芯片单片机构成低功耗系统时,系统中所有芯片都应尽可能选择低功耗产品。 5、可靠性及抗干扰设计是硬件设计必不可少的一部分,它包括芯片、器件选择、去耦滤波、印刷电路板布线、通道隔离等。 6、单片机外围电路较多时,必须考虑其驱动能力。驱动能力不足时,系统工作不可靠,可经过增设线驱动器增强驱动能力或减少芯片功耗来降低总线负载。 7、尽量朝”单片”方向设计硬件系统。系统器件越多,器件之间相互干扰也越强,功耗也增大,也不可避免地降低了系统的稳定性。随着单片机片内集成的功能越来越强,真正的片上系统SoC已经能够实现,如ST公司新近推出的μPSD32××系列产品在一块芯片上集成了80C32核、大容量FLASH 存储器、SRAM、A/D、I/O、两个串口、看门狗、上电复位电路等等。单片机系统硬件抗干扰常见方法实践 影响单片机系统可靠安全运行的主要因素主要来自系统内部和外部的各种电气干扰,并受系统结构设计、元器件选择、安装、制造工艺影响。这些都构成单片机系统的干扰因素,常会导致单片机系统运行失常,轻则影响产品质量和产量,重则会导致事故,造成重大经济损失。 3

课程设计任务书 (指导教师填写) 课程设计名称电路板设计与制作学生姓名专业班级 设计题目51单片机最小系统学习板的设计与制作 一、课程设计的任务和目的 任务: 设计并制作51单片机最小系统电路板,包括电路原理图设计、版图规划与设计、系统单面电路板制作。 要求: 1)电路原理图准确、版图结构清晰、布局合理。 2)使用插针型元件,成品PCB板面布局合理,密度适当; 3)板上资源包括LED灯、数码管、蜂鸣器、按钮、串行通讯及USB接口; 4)电路板面积适中便于携带,长度15cm,宽8.5cm。 目的: 1)掌握并完成基本PCB板的设计与制作工艺; 2)学习并掌握实现单片机应用系统的软硬件设计、调试、实现的技能; 3)了解单片机最小系统的工作原理与系统开发方法,锻炼动手能力,为毕业设计做准备。 二、设计内容、技术条件和要求 1.设计并制作具有实际功能的单片机最小系统: 可选择实现的功能⑴.流水灯⑵.电子时钟⑶.数字温度计⑷.交通灯控制器; 2.根据所选电路功能,画出电路框图和原理总图。 3.根据电路所需元件及周边设备规划和设计电路板版图,描画版图。 4.根据版图生成gerber工艺文件,进行电路板制作,包括刻板,钻孔,覆铜等。 5.撰写设计总结报告。 三、时间进度安排 本课程设计共两周时间。 第一周:功能设计与理论学习 周一上午:布置设计任务;提出课程设计的目的和要求;明确对撰写总结报告、手工绘制原理图和电路板版图的要求;安排答疑、实验室开放时间。讲解印制电路板的制板流程,介绍PCB刻板机等制板设备的软硬件操作方法以及注意事项。 周一下午:讲解电路原理图与PCB版图设计方法。 周二至周五:学生查阅资料,确定设计题目;进行功能设计,在实验室完成电路原理图与PCB 版图的设计和绘制,导出电路总原理图及版图文件。期间安排两次答疑,指导学生设计。周五,交设计草图-原理图和版图供老师审阅。 第二周:电路板制作、撰写设计总结报告 周一至周四:分组在电子系统加工及评测实验室(225)操作刻板工具和设备进行电路板成品的加工和制作,成品需通过老师验收。 周五:撰写设计总结报告。 四、主要参考文献 1. 《单片机原理及应用》. 冯文旭等著. 第一版, 2008年8月. 机械工业出版社. 2. 《乐普科快速PCB制板系统操作使用流程》手册。 3. 单片机系统开发和PCB设计的相关参考教材; 指导教师签字:2018年9 月3 日

一、内容及要求 内容:设计制作一个51最小系统,用最小系统控制8个发光2极管。 要求:全部点亮,依次点亮,交换点亮;用最小系统控制蜂鸣器;用最小系统控制电机。 二、设计思路 使用AT89C51单片机时无须外扩存储器。因此,本流水灯实际上就是一个带有八个发光二极管的单片机最小应用系统,即为由发光二极管、晶振、复位、电源等电路和必要的软件组成的单个单片机。 八个发光二极管D1-D8分别接在单片机的P2.0-P2.7接口上,当给P2.0口输出“0”时,发光二极管点亮,当输出“1”时,发光二极管熄灭。可以运用输出端口指令MOV P0,A或MOV P0,#DATA,只要给累加器值或常数值,同理,接在P2.1~P2.7口的其他7个LED的点亮和熄灭的方法同LED1。因此,要实现 图2-1 主程序流程图 流水灯功能,我们只要将发光二极管LED1~LED8依次点亮、熄灭,8只LED灯便会一亮一暗的成流水灯了。在此我们还应注意一点,由于人眼的视觉暂留效应

以及单片机执行每条指令的时间很短,我们在控制二极管亮灭的时候应该延时一段时间,否则我们就看不到闪烁效果。 程序启动时跳转到键盘判断模块程序中,此程序里面包含Key1~Key5的按键情况判断,循环检测直到有按键按下的时候,程序转去相对应按键的彩灯显示的花型模块,与此同时,当按键Key6有闭合时,程序中调用延时程序程序时,给延时参数赋值上另一个值,是延时程序延时时间发生改变,以达到不同快慢节奏闪烁的彩灯。具体程序流程图2-1所示。 三、硬件设计 3.1 直流稳压电源电路 对于一个完整的电子设计来讲,首要问题就是为整个系统提供电源供电模块,电源电路的稳定可靠是系统平稳运行的前提和基础。电子设备除用电池供电外,还采用市电(交流电网)供电。通过变压、整流、滤波和稳压后,得到稳定的直流电。直流稳压电源是电子设备的重要组成部分!本项目直流稳压电源为+5V。如下图所示: 直流稳压电源的制作一般有3种制作形式,分别是分立元件构成的稳压电源、线性集成稳压电源和开关稳压电源。下图稳压电源采用的是三端集成稳压器7805构成的正5V直流电源。 图3-1 三端固定式集成稳压电源电路图 AT89C51单片机的工作电压范围:4.0V—5.5V,所以通常给单片机外接5V 直流电源。由于时间关系,此处用3节1.5V的干电池供电,在此不在赘述此稳压电源电路图原理。 3.2单片机最小系统 要使单片机工作起来,最基本的电路的构成由单片机、时钟电路、复位电路等组成。单片机最小系统如下图3-2所示。

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

2 系统硬件设计 2.1 系统总体设计结构 太阳能热水器控制器主要由温度水位数据采集模块、单片机控系统。本次设计选用的是AT89C52单片机作为核心控制器,组成热水器微控制系统。传感器采用的是单片集成两端感温电流源DS18B20温度传感器,用于检测水温,并负责将检测到的水压转换成0~5V的模拟信号,然后通过ADC0832模数转换器把检测到的温度电压信号转换成数字信号,一方面由单片机AT89C52完成最终完成太阳能热水器控制器的控制功能,另一方面通过LED显示当前温度和水位值,另外一方面与温度和水位设定值进行比较、运算,根据结果发出相应的上水、加热指令,对热水器的温度和水位进行控。 2.2 温度检测电路 温度检测部分是实现温度智能控制的重要环节,只有准确地检测出温度,才能通过软件实现辅助加热。其性能的好坏直接影响系统的性能,对于温度检测,目前比较理想的是集成温度传感器DS18B20,因此温度传感器采用是美国模拟器件公司生产的单片集成两端感温电流源DS18B20。DS18B20温度传感器是一种已经IC化的温度感测器,它会将温度转换为电流,在单片机的各种课本中经常看到。其规格如下: (1)温度每增加1℃,它会增加1μA输出电流; (2)可测量范围-55℃至125℃; (3)供电电压范围+3V至+5V。 AD590的管脚图及元件符号如2.2所示:

图2.2 DS18B20的管脚图及元件符号 DS18B20的输出电流值说明如下: 其输出电流是以绝对温度零度(-273℃)为基准,每增加1℃,它会增加1μA输出电流,因此在室温25℃时,其输出电流Iout=(273+25)=298μA。 2.2.1 DS18B20的主要特性 (1)适应电压范围更宽,电压范围:3.0~5.5V,在寄生电源方式下可由数据线供电; (2)独特的单线接口方式,DS18B20在与微处理器连接时仅需要一条口线即可实现微处理器与DS18B20的双向通讯; (3)DS18B20支持多点组网功能,多个DS18B20可以并联在唯一的三线上,实现组网多点测温; (4)DS18B20在使用中不需要任何外围元件,全部传感元件及转换电路集成在形如一只三极管的集成电路内; (5)温范围-55℃~+125℃,在-10~+85℃时精度为±0.5℃; (6)可编程的分辨率为9~12位,对应的可分辨温度分别为0.5℃、0.25℃、0.125℃和0.0625℃,可实现高精度测温; (7)在9位分辨率时最多在 93.75ms内把温度转换为数字,12位分辨率时最多在750ms内把温度值转换为数字,速度更快; (8)测量结果直接输出数字温度信号,以"一线总线"串行传送给CPU,同时可传送CRC校验码,具有极强的抗干扰纠错能力; (9)负压特性:电源极性接反时,芯片不会因发热而烧毁,但不能正常工作。 2.2.2 DS18B20工作原理 图2.3 DS18B20测温原理图 DS18B20的读写时序和测温原理与DS1820相同,只是得到的温度值的位数因分辨率不同而不同,且温度转换时的延时时间由2s 减为750ms。 DS18B20测温原

北方民族大学 电气信息工程学院总结 题目: 学生姓名: 专业: 学号:

目录目的 设计原理 硬件设计 主芯片 存储系统 电源系统 其他系统 软件设计 流程图 程序 Proteus仿真图 心得

1.目的 单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。概括的讲,一块芯片就成了一台计算机。 单片机具有体积小、功能强、应用面广等优点,目前正以前所未见的速度取代着传统电子线路构成的经典系统,蚕食着传统数字电路与模拟电路固有的领地。它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。同时,学习使用单片机了解计算机原理与结构的最佳选择。 现在,这种单片机的使用领域已十分广泛。彩电、冰箱、空调、录像机、VCD、遥控器、游戏机、电饭煲等无处不见单片机的影子,单片机早已深深地融入我们每个人的生活之中。 单片机能大大地提高这些产品的智能性,易用性及节能性等主要性能指标,给我们的生活带来舒适和方便的同时,在工农业生产上也极大地提高了生产效率和产品质量。单片机按用途大体上可分为两类,一种是通用型单片机,另一种是专用型单片机。 MCS-51单片机是美国INTEL公司于1980年推出的产品,与MCS- 48单片机相比,它的结构更先进,功能更强,在原来的基础上增加了更多的电路单元和指令,指令数达111条,MCS-51单片机可以算是相当成功的产品,一直到现在,MCS-51系列或其兼容的单片机仍是应用的主流产品,各高校及专业学校的培训教材仍与MSC-51单片机作为代表进行理论基础学习。MCS-51系列单片机主要包括8031、8051和8751等通用产品。 所谓"最小"是指可以启动单片机的必要条件,也就是说没有这个条件,就无法让单片机工作了。主要是三个方面:1、Power,指单片机工作的电源部分,VCC/GND,2、Clock,指单片机工作的时钟,单片机执行各项指令/动作,都是按照时钟这个节拍来完成的,当然是必不可少的。3、Reset,复位信号,单片机执行取指等操作都是从寄存器的某一位置开始执行的,复位信号就是告诉单片机刚开始工作时的地址在哪里,好比是个入口啦! 除了硬件设施要齐全外,要做出一个实物,还必须要有软件——c语言,c 语言是一种计算机程序设计语言。它既有高级语言的特点,又有汇编语言的特点。它可以作为系统设计语言,编写工作系统应用程序,也可以作为应用程序设计语言,编写不依赖计算机硬件的应用程序。因此,本次制作应用于c语言编写程序。2.设计任务 设计并制作一个单片机最小系统。要求设计正负5V电源给系统供电,系统具有4x4键盘阵列,6个LED显示器。用AT89S51的并行口P1接4x4矩阵键盘,以P1.0—P1.3作输入线,以P1.4—P1.7作输出线;在数码管上显示每个按键的“0—F”序号。所有口线均通过接插件与外界连接。 3.系统设置

Xilinx FPGA配置的一些细节 2010年07月03日星期六 14:26 0 参考资料 (1) Xilinx: Development System Reference Guide. dev.pdf, v10.1 在Xilinx的doc目录下有。 (2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005 在Xilinx网站上有,链接 (3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007 在Xilinx网站上有,链接 注:此外xapp139和xapp151也是和配置相关的。 (4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007 (5) Tell me about the .BIT . 链接: 1 Xilinx配置过程 主要讲一下Startup Sequence。 Startup Sequence由8个状态组成. 除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。 其中默认顺序如下: 这些在ISE生成bit文件时通过属性页设定。 这几个状态的具体含义如下: Release_DONE : DONE信号变高 GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态 GTS : 激活用户IO,之前都是高阻。

第三章系统硬件设计 3.1 孵化恒温箱的介绍 本系统使用单片机AT89C2051来实现对孵化箱温度的控制,蛋类孵化是一个复杂的生物学过程,其内部环境条件随着不同的孵化进程,发生较大的变化。孵化温度一般就认为是孵箱内部温度,孵化温度控制的原则和依据“看胎施温”是孵化温度控制的原则。孵化温度控制的影响因素孵化箱的类型、规模、密封程度、进出气孔的大小、加热系统与孵化规模的匹配程度、孵化的家禽种类、孵化箱的室温等等,每个因素的变化都会影响到孵化温度的稳定。 温度是家禽孵化的首要条件,保持合适的温度是获得较高孵化率及健雏率的前提,虽然孵化的最佳温度是37.8℃,然而在生产中还应该根据实际情况来进行温度的控制,本文就鸡种蛋孵化不同情况下的温度控制进行论述。孵化是养鸡生产中一项重要的技术环节。种蛋质量和孵化条件影响种蛋的孵化率和健雏率,而在孵化条件中,温度自始至终是禽蛋孵化中的主要矛盾,起主导作用。根据胚胎发育状况掌握好孵化温度是禽蛋孵化稳产高产的关键,即必须给胚胎提供一个最适宜的环境温度,这样才能正常完成胚胎的发育,获得较高的孵化率和健雏率。虽然在孵化中有一个最佳温度。然而在实际生产中,影响温度的因素很多。以下是鸡种蛋孵化生产中温度控制的一些基本原则。温度范围与最佳温度孵化中低于某一温度胚胎发育将被抑制。要高于某一温度,胚胎才开始发育,这一温度被称为“生理零度”,也叫临界温度,一般认为鸡的生理零度约为23.9℃,同时胚胎发育对环境温度有一定的适应能力,以鸡为例,温度在35~40.5℃之间,都会有一些种蛋孵出小鸡。在35~40.5℃之间这个温度范围内有一个最佳温度,应该环境温度保持在24~26℃,孵化箱内的最佳温度为37.8℃。环境温度对孵化有一定的影响,环境温度的高低主要影响孵化过程温度控制的精确度。在生产中一般根据不同地域、不同季节而灵活掌握。 恒温孵化和变温孵化是根据环境温度的不同而经常采用的两种孵化方式,恒温孵化与变温孵化如果操作恰当均可取得较好的效果。恒温孵化是在孵化过程中把温度控制在37.0~38.0℃之间,恒温孵化对孵化的环境要求条件较高,环境温度应该保持在22~26℃之间,并且要通风良好。变温孵化是根据孵化机类型、孵化室温度和胚胎发育日龄,给予不同的温度。如果环境温度低于20℃,则孵化温度可比最佳温度高0.5~0.7℃;如果环境温度高于30℃,则可以降低孵化温度0.2~0.6℃。表3.1为一个变温孵化方案[3]。

51单片机最小系统1.设计框图 2.硬件电路设计

3.元件清单 共阴极数码管2只(分立) 10UF电解电容2只(限压16V)30PF瓷片电容2只 220欧的电阻9只 4.7K的电阻1只 1.2K的电阻1只 4.7K的排阻1只 12MHZ的晶振1只 S8550三极管1只 单排针2排 自锁小按键1只 蜂名器1只(长音) STC89C51单片机1片 常开按钮开关1只(轻触开关)40引脚紧锁座或40引脚芯片插槽1只(前者方便单片机取下来的,但价格较贵;后者便宜,不便于拔插) 发光二极管(5MM红色)10只 电路板1张(单孔锡板,带九针串口座的焊盘) USB转串口线1根(笔记本电脑必买、台式电脑选买) USB头一个(如下一页实物图所示)双头USB线1根(两头都能插入USB 头里面) 细导线2米(单芯、铁线) 2CM铜柱8根(一头凸起,一头凹下)

104瓷片电容5片 MAX232芯片1片 串口头1个(母头、9孔式) 串口线1根(一端9孔、一端9针)****蓝色器件为台式电脑用**** 注意:有的元器件(如电阻、瓷片电容等)非常便宜,一般按10个为单位买,否则别人不卖。必备工具:万用表、电烙铁、焊锡丝、松香、吸锡器、斜口钳、镊子 相关软件:Protel 99 SE、Keil 3、单片机烧录软件 4.下载电路 STC89C52 1、电源:这当然是必不可少的了。单片机使用的是5V电源,其中正极接40引脚,负极(地)接20引脚。 2、振荡电路:单片机是一种时序电路,必须提供脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。只要买来晶振,电容,连上就可以了。 3、复位(RST,第9引脚):至于复位是何含义及为何需要复位,在单片机功能中介绍。 4、EA(31引脚):EA引脚接到正电源端。至此,一个单片机就接好,通上电,单片机就开始工作了。 5、P1口发光管电路:P1.0-P1.7(第1-8引脚)连接到8个470欧电阻驱动8个发光管。 6、单片机引脚控制连接:两排单排插连接单片机40个引脚,方便以后扩展或测试各引脚。 7、在线编程下载接口:用一个5X2(长为5的双排插)连接电源VCC、GND、P1.5(第6脚)、P1.6(第7脚)、P1.7(第8脚)和RST(第9脚),然后通过在线编程下载模块连接到电脑的并口,运行Keil编程软件可以实现在线编程和仿真,边改程序边调试电路(观看发光管的表演,当然导演就是大家自己!)