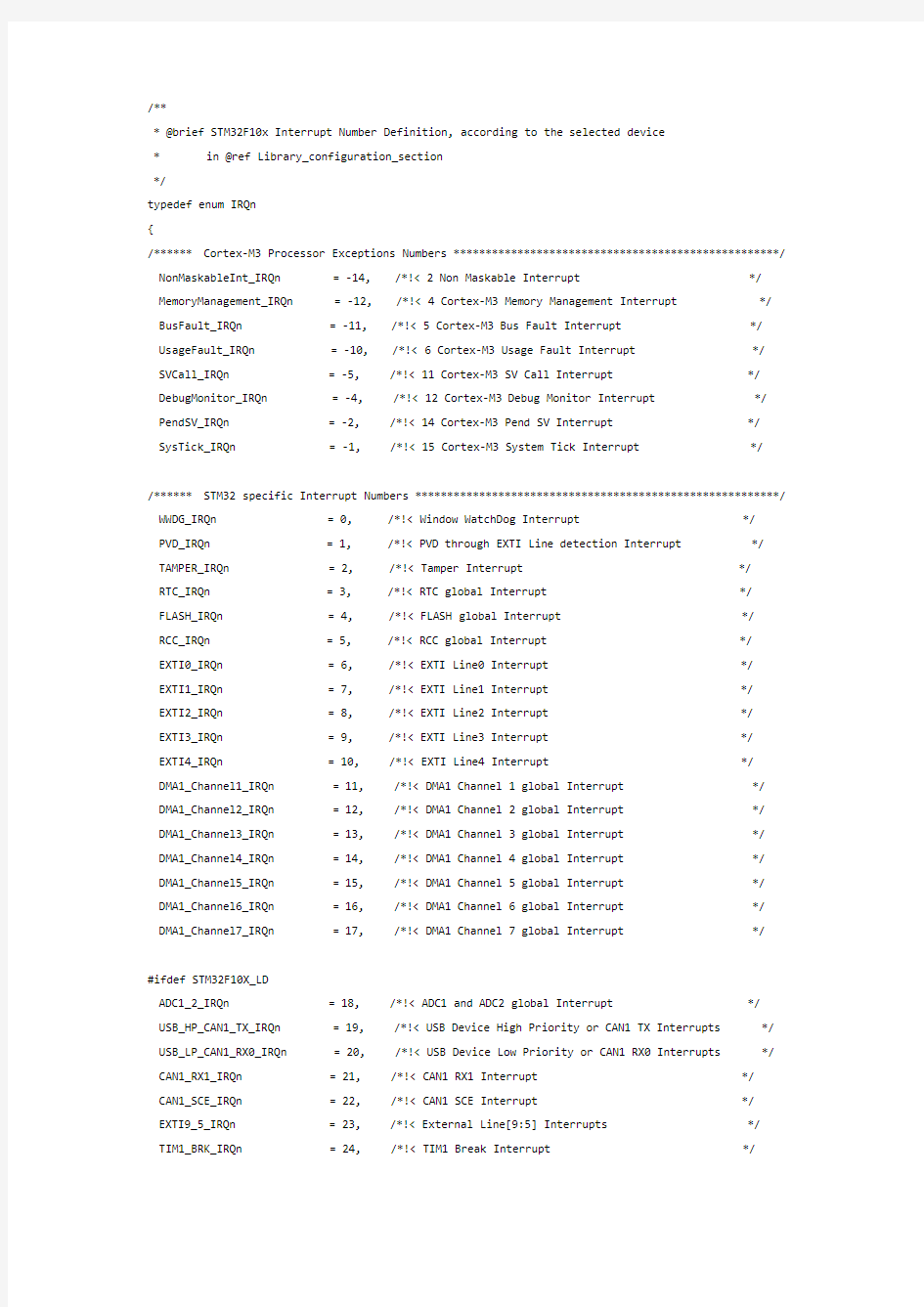

/**

*@brief STM32F10x Interrupt Number Definition,according to the selected device

*in@ref Library_configuration_section

*/

typedef enum IRQn

{

/******Cortex-M3Processor Exceptions Numbers***************************************************/ NonMaskableInt_IRQn=-14,/*!<2Non Maskable Interrupt*/ MemoryManagement_IRQn=-12,/*!<4Cortex-M3Memory Management Interrupt*/ BusFault_IRQn=-11,/*!<5Cortex-M3Bus Fault Interrupt*/ UsageFault_IRQn=-10,/*!<6Cortex-M3Usage Fault Interrupt*/ SVCall_IRQn=-5,/*!<11Cortex-M3SV Call Interrupt*/ DebugMonitor_IRQn=-4,/*!<12Cortex-M3Debug Monitor Interrupt*/ PendSV_IRQn=-2,/*!<14Cortex-M3Pend SV Interrupt*/ SysTick_IRQn=-1,/*!<15Cortex-M3System Tick Interrupt*/

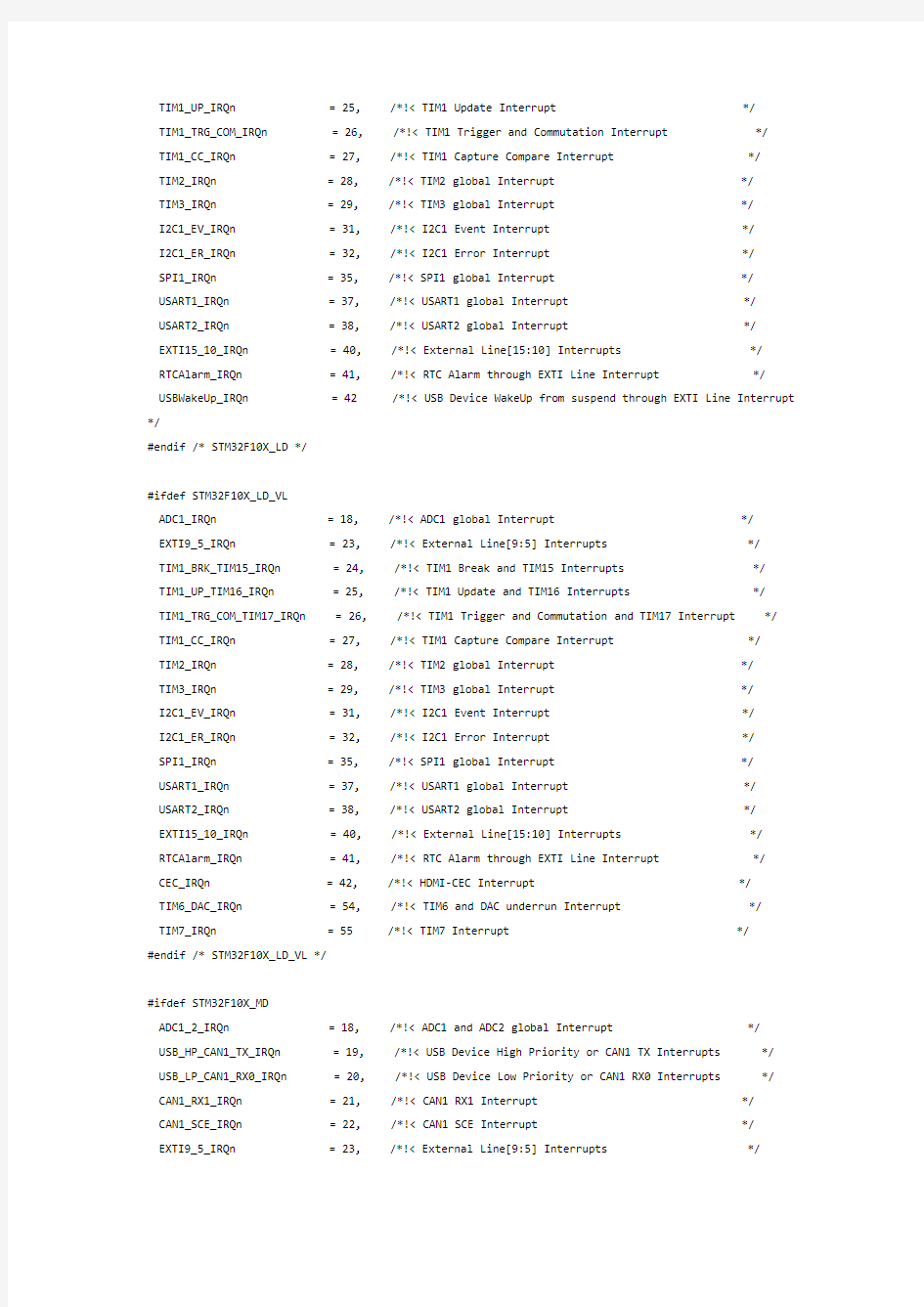

/******STM32specific Interrupt Numbers*********************************************************/ WWDG_IRQn=0,/*! #ifdef STM32F10X_LD ADC1_2_IRQn=18,/*! TIM1_TRG_COM_IRQn=26,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! SPI1_IRQn=35,/*! #endif/*STM32F10X_LD*/ #ifdef STM32F10X_LD_VL ADC1_IRQn=18,/*! EXTI9_5_IRQn=23,/*! TIM1_BRK_TIM15_IRQn=24,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! SPI1_IRQn=35,/*! TIM6_DAC_IRQn=54,/*! TIM7_IRQn=55/*! #endif/*STM32F10X_LD_VL*/ #ifdef STM32F10X_MD ADC1_2_IRQn=18,/*! CAN1_SCE_IRQn=22,/*! EXTI9_5_IRQn=23,/*! TIM1_UP_IRQn=25,/*! TIM1_TRG_COM_IRQn=26,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! TIM4_IRQn=30,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! SPI1_IRQn=35,/*! SPI2_IRQn=36,/*! #endif/*STM32F10X_MD*/ #ifdef STM32F10X_MD_VL ADC1_IRQn=18,/*! EXTI9_5_IRQn=23,/*! TIM1_BRK_TIM15_IRQn=24,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! TIM4_IRQn=30,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! SPI1_IRQn=35,/*! SPI2_IRQn=36,/*! TIM6_DAC_IRQn=54,/*! TIM7_IRQn=55/*! #endif/*STM32F10X_MD_VL*/ #ifdef STM32F10X_HD ADC1_2_IRQn=18,/*! CAN1_SCE_IRQn=22,/*! EXTI9_5_IRQn=23,/*! TIM1_BRK_IRQn=24,/*! TIM1_UP_IRQn=25,/*! TIM1_TRG_COM_IRQn=26,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! TIM4_IRQn=30,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! SPI1_IRQn=35,/*! SPI2_IRQn=36,/*! TIM8_BRK_IRQn=43,/*! TIM8_UP_IRQn=44,/*! TIM8_TRG_COM_IRQn=45,/*! TIM5_IRQn=50,/*! SPI3_IRQn=51,/*! TIM6_IRQn=54,/*! TIM7_IRQn=55,/*! DMA2_Channel1_IRQn=56,/*! #ifdef STM32F10X_HD_VL ADC1_IRQn=18,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! mapped at position60only if the MISC_REMAP bit in the AFIO_MAPR2register is set)*/ #endif/*STM32F10X_HD_VL*/ #ifdef STM32F10X_XL ADC1_2_IRQn=18,/*! CAN1_SCE_IRQn=22,/*! EXTI9_5_IRQn=23,/*! TIM1_BRK_TIM9_IRQn=24,/*! TIM1_CC_IRQn=27,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! TIM4_IRQn=30,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! SPI1_IRQn=35,/*! SPI2_IRQn=36,/*! TIM8_BRK_TIM12_IRQn=43,/*! TIM8_CC_IRQn=46,/*! TIM5_IRQn=50,/*! SPI3_IRQn=51,/*! TIM6_IRQn=54,/*! TIM7_IRQn=55,/*! DMA2_Channel1_IRQn=56,/*! #endif/*STM32F10X_XL*/ #ifdef STM32F10X_CL ADC1_2_IRQn=18,/*! CAN1_SCE_IRQn=22,/*! EXTI9_5_IRQn=23,/*! TIM1_BRK_IRQn=24,/*! TIM1_UP_IRQn=25,/*! TIM1_TRG_COM_IRQn=26,/*! TIM2_IRQn=28,/*! TIM3_IRQn=29,/*! TIM4_IRQn=30,/*! I2C1_EV_IRQn=31,/*! I2C1_ER_IRQn=32,/*! I2C2_EV_IRQn=33,/*! I2C2_ER_IRQn=34,/*! SPI1_IRQn=35,/*! SPI2_IRQn=36,/*! TIM5_IRQn=50,/*! SPI3_IRQn=51,/*! TIM6_IRQn=54,/*! TIM7_IRQn=55,/*! DMA2_Channel1_IRQn=56,/*! ETH_IRQn=61,/*! }IRQn_Type;