CRC16原理

1.基本原理

CRC校验码是基于将位串看作是系数为0或1的多项式,一个k位的数据流

可以看作是关于x的从k-1阶到0阶的k-1次多项式的系数序列。

m(x)=a0+a1x1+a2x2+??+a k?1x k?1

生成多项式G(x),规定发送方和接收方必须事先商定一个生成多项式G(x),其高位和低位必须是1。要计算m位的帧m(x)的校验和,基本思想是将校验和加在帧的末尾,使这个带校验和的帧的多项式能被G(x)除尽。

当接收方收到加有校验和的帧时,用G(x)去除它,如果有余数,则CRC校验错误,只有没有余数的校验才是正确的。

2. G(x) 应当满足以下条件:

1)生成多项式的最高位和最低位必须为1。

2)当被传送信息(CRC码)任何一位发生错误时,被生成多项式做除后应该使余数不为0。

3)不同位发生错误时,应该使余数不同。

4)对余数继续做除,应使余数循环。

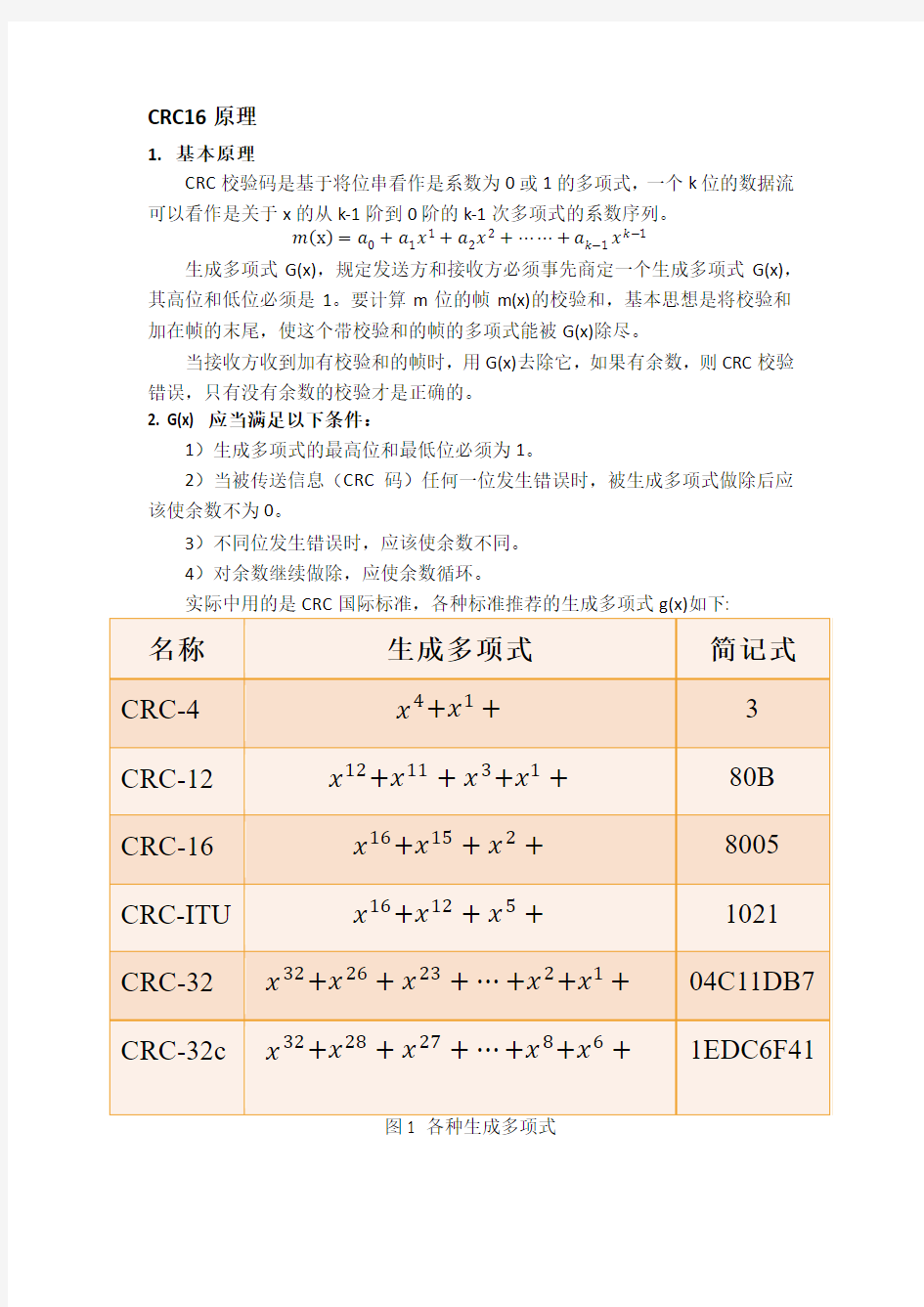

实际中用的是CRC国际标准,各种标准推荐的生成多项式g(x)如下:

2.CRC码生成方法

借助于多项式除法,其余数为校验字段。信息字段代码为: 1011001;对应m(x)=x6+x4+x3+1。假设生成多项式为:g(x)=x4+x3+1;则对应g(x)的代码为: 11001。x4m(x)=x10+x8+x7+x4 对应的代码记为:10110010000;采用多项式除法: 得余数为: 1010 (即校验字段为:1010)。

发送方:发出的传输字段为: 1 0 1 1 0 0 1(信息字段)1010(校验字段)接收方:使用相同的生成码进行校验:接收到的字段/生成码(二进制除法)如果能够除尽,则正确。

Matlab 仿真

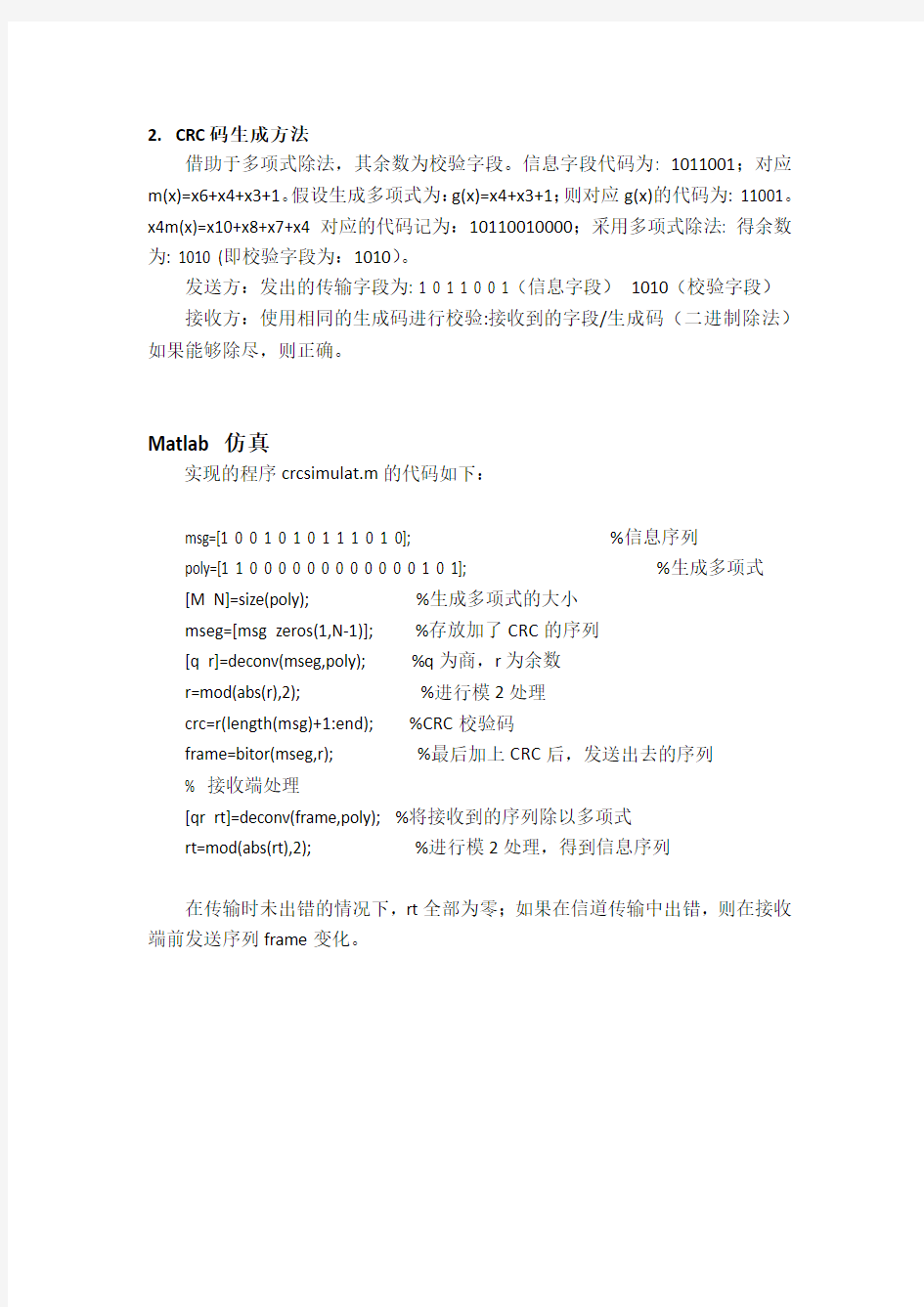

实现的程序crcsimulat.m的代码如下:

msg=[1 0 0 1 0 1 0 1 1 1 0 1 0]; %信息序列

poly=[1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1]; %生成多项式

[M N]=size(poly); %生成多项式的大小

mseg=[msg zeros(1,N-1)]; %存放加了CRC的序列

[q r]=deconv(mseg,poly); %q为商,r为余数

r=mod(abs(r),2); %进行模2处理

crc=r(length(msg)+1:end); %CRC校验码

frame=bitor(mseg,r); %最后加上CRC后,发送出去的序列

% 接收端处理

[qr rt]=deconv(frame,poly); %将接收到的序列除以多项式

rt=mod(abs(rt),2); %进行模2处理,得到信息序列

在传输时未出错的情况下,rt全部为零;如果在信道传输中出错,则在接收端前发送序列frame变化。

查表法

1. CRC16实现的步骤描述:

a. Register左移一个字节,从原始数据中读入一个新的字节;

b. 利用刚从Register中移出的字节作为下标定位table中的值;

c. 把这个值XOR到Register中;

d. 如果还有未处理的数据则返回到第一步继续执行;

e. 数据结束后,还要对这十六位数据执行b和c步骤两次,最后寄存器Register 内的值才是crc16校验码。

图2 步骤框图

2. Verilong代码流程图

其中CRCA作为第一级crc16值寄存器,Addr为取表的地址,Register为中间寄存器,data为输入的八位数据。CRC为最终CRC16输出。

下图2为流程图。

图3 查表法流程图

3. 具体的实现操作

1)生成.mig文件用于写入rom

把256个16位的table值写入到rom中方便。第一步就是用Matlab生成.mif文件。生成.mif文件的Matlab程序是crc.m

注意:在生成时,需要对16进制的数转换成十进制才能正确的生成,生成时是以十六进制形式写入的。

2)开辟片内ROM

开辟一个250*16大小的一个片内ROM,用于存取.mif文件。每个地址就对应于一个16位的值。地址为8位,输出数据是16位的。

图4 开辟的rom

3) 分析时序

下图为程序工作的时序分析图

图5 程序工作时序分析图

由于是循环的操作,所以需要3个clk处理一个8位数据。最后还要对得到的crc16a做处理。

注意:查表法的待测数据的位数需要是8的倍数,在待测数据结束后需要对crc16a做两次的移位异或操作。

4) 程序的使用

输入端口有时钟clk,复位reset_n,结束标志endB,使能en,八位数据输入data。

输出端口有十六位crc16码,输出标志位flagup。

三个clk输入一个data,data结束后给一个clk的endB的高电平。在flagup为高时,可以取得crc16码。

图6 Crc16校验器的封装

注意:三个clk输入才输入一个data,data结束后给一个clk的endB的高电平。在flagup 为高时,才可以取得crc16码。

附:程序已注释

直接法

1.直接按比特计算的实现方法

计算过程(信息字段代码为: 1011001,多项式代码为: 11001)

a. 待测数据后面扩展R=4个比特0,变成10110010000;

b. 寄存器初始化置0;

c. 先在寄存器中移入数据1011;

d. 寄存器左移一位,并且右边移入下一位数据1。这样最高位1移出,由于最高位是1,要用除数11001来进行XOR,最高位肯定XOR得0,所以不用管它,只要用低4位0110来进行XOR就可以,即1001对寄存器进行XOR,寄存器中得到1111,即第一次XOR后的结果(相当于是数据10110与生成项11001进行了一次XOR,并把最高位0消掉了),若移出的最高位是0,则寄存器继续左移一位。重复上述过程,直到处理完所有的比特。最后寄存器中的就是整个计算后的余数,即CRC值。

2. Verilog 的实现

CRC -16校验码的生成多项式为g(x)=x 6+x 5+x2+。最高位为16次方,这里用16位移位寄存器来实现,根据多项式设置异或抽头的位置即可。这部分代码如下:assign crc_enc[0]=crc_reg[15]^x;

assign crc_enc[1]=crc_reg[0];

assign crc_enc[2]=crc_reg[1]^crc_reg[15]^x;

assign crc_enc[14:3]=crc_reg[13:2];

assign crc_enc[15]=crc_reg[15]^crc_reg[14]^x;

把程序封装好后得到如图所示

图7 直接法Verilog 实现

程序说明

Clk输入时钟;reset复位端口低电平有效;x为1位数据输入端口;en 使能端口,数据发送结束的同时置低电平后可以取到最后的crc16码;crc_reg为16位的crc16码实时输出。

仿真图如下:

图8 功能仿真

附录

1.FPGA片内rom的开辟

1)打开QuertusⅡ,新建bdf文件。

2)双击空白处,可得到下图,选择红色框。

3)选择红色框内,点Next.

4) 在下面的对话框,选择红色处,并命名为xx(rom)。

5)在下图对话框可以设置位宽和长度,设置好后点Next。

6)下图的红色框的选项选择是否需要下一个时钟输出,这里我们不选。

7)选择我们创建的.mif文件,后面的不用改变,可以直接Finish。