虽然很艰辛,出了大堆问题,但总算一一解决了,即使是别人提供现成的IP核和testbench,说起来容易,但是做起来难,版本差别,软件设置,总有这些问题在困扰一穷二白的初学者,并阻挡前进的步伐,现在总结一下我做altera triple speed Ethernet这个IP核生成和编译仿真的全过程:(附操作图片)

1、生成IP core:

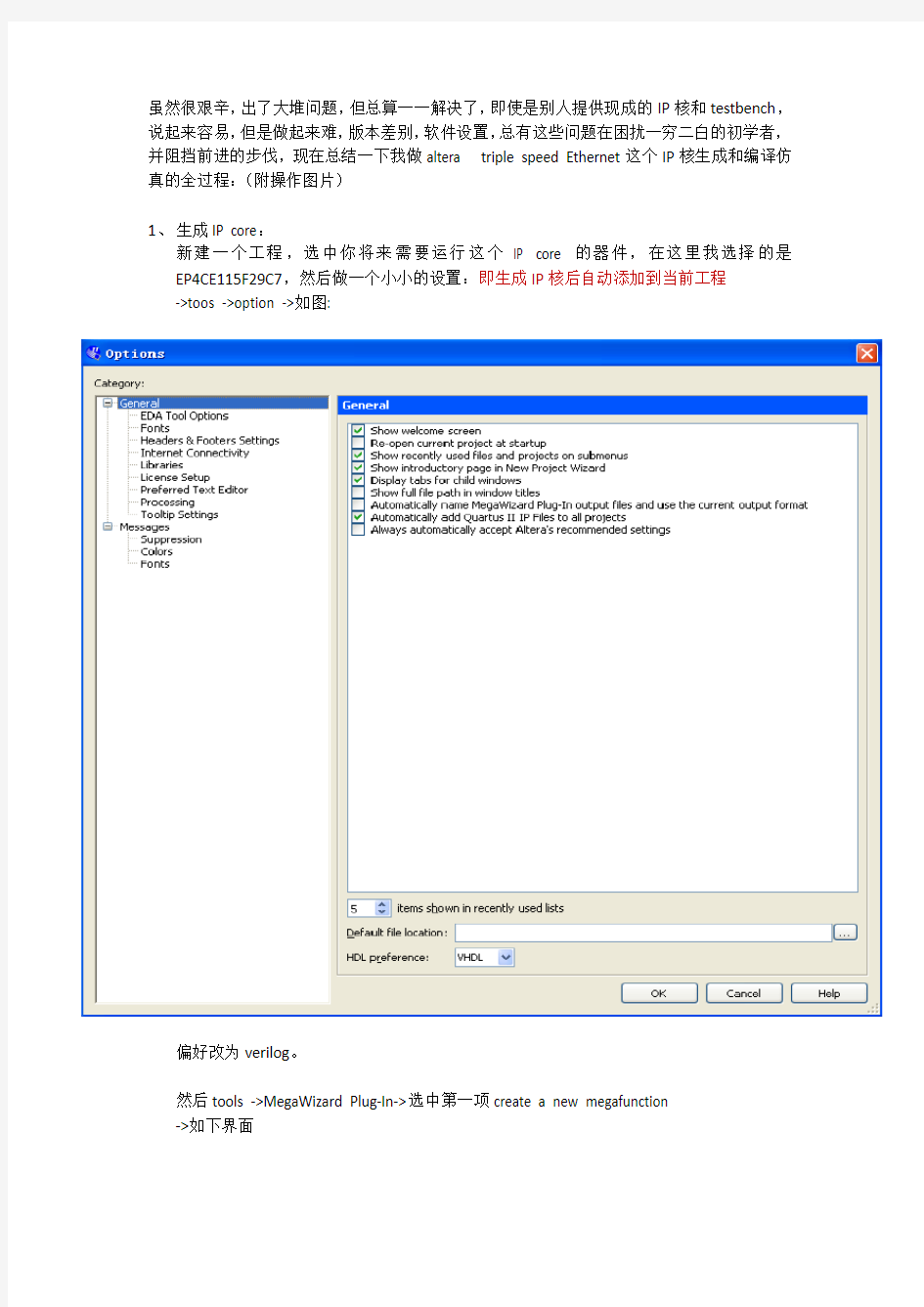

新建一个工程,选中你将来需要运行这个IP core 的器件,在这里我选择的是EP4CE115F29C7,然后做一个小小的设置:即生成IP核后自动添加到当前工程

->toos ->option ->如图:

偏好改为verilog。

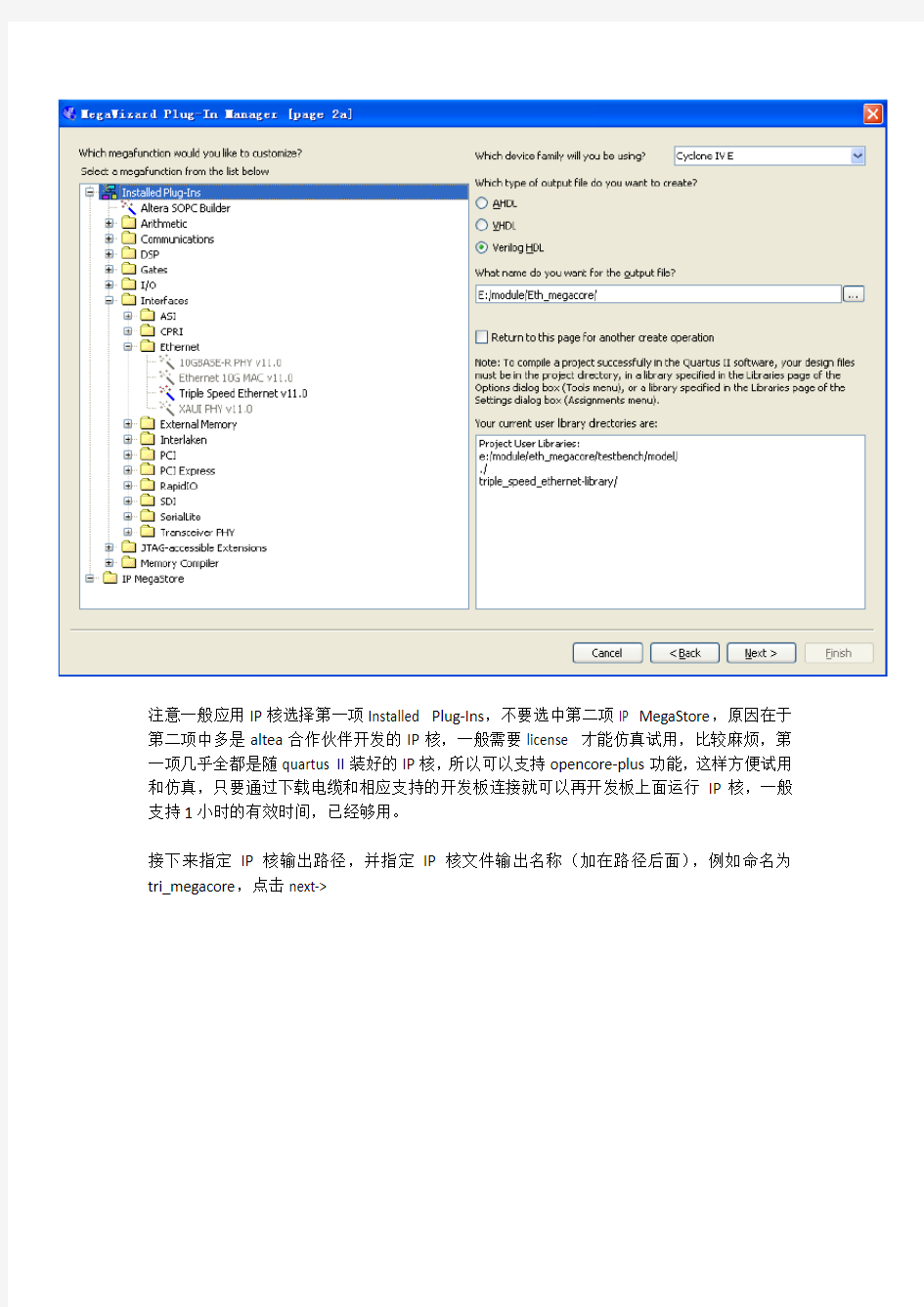

然后tools ->MegaWizard Plug-In->选中第一项create a new megafunction

->如下界面

注意一般应用IP核选择第一项Installed Plug-Ins,不要选中第二项IP MegaStore,原因在于第二项中多是altea合作伙伴开发的IP核,一般需要license 才能仿真试用,比较麻烦,第一项几乎全都是随quartus II装好的IP核,所以可以支持opencore-plus功能,这样方便试用和仿真,只要通过下载电缆和相应支持的开发板连接就可以再开发板上面运行IP核,一般支持1小时的有效时间,已经够用。

接下来指定IP核输出路径,并指定IP核文件输出名称(加在路径后面),例如命名为tri_megacore,点击next->

如图是我的设置,因FPGA内部MAC与PHY连接接口选用RGMII,故选用该设置,使用内部FIFO,点击next->

一般按照默认设置既可,因仿真或者设计需要,另外选中第二项、第四项(包括64-bit counter)、第七项,同时选中包含MDIO module,将时钟分频改为50,MAC使用125MHz时钟,分频50得到2.5MHz时钟,极为MDIO的工作时钟。

点击next->

内部FIFO设置,2048是深度(根据前段设计的数据吞吐量来定,当然一般定得大些比较好了)、8bit是位宽,这个FIFO的选择也决定avalon-ST总线的位宽。

点击next->

选中生成simulation model (仿真用)和netlist 点击next->

接下来IP core生成成功了,准备进行编译工作。

2、编译IP core:

第一次编译IP核建议在quartusII中进行,而不要再第三方的工具中进行,因为altera 自己的IP,自己的工具支持得最好,并且智能化程度很高,

首先工程窗口中点击files ,右击tri_megacore.qip,

编译之前注意以下事项:

即仿真工具选择为none ,原因在于quartus II在编译过程不支持第三方的工具。

编译一般木有啥问题。

接下来在开始调用modelsim SE6.5仿真之前,先编译好IP核需要的仿真库和器件库,

这一步比较重要,其中仿真工具的选择和路径指定、器件选择、仿真库的输出路径设置很关键,以后步骤还可能会用到。

编译完成后可以去改路径看看生成了什么东东:

不错,你看到就是自动生成的仿真需要用的所有仿真库文件。

然后在modelsim安装路径中找到modelsim.ini这个文件,去掉只读属性,并在library一栏加入:altera_lnsim_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/altera_lnsim_ver altera_mf_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/altera_mf_ver

altera_ver = D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/verilog_libs/altera_ver cycloneive_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/cycloneive_ver

lpm_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/lpm_ver

sgate_ver=D:/Altera/quartus/eda/sim_lib/modelsim/verilog_libs/sgate_ver

注意路径用正斜杠,不要用windows下面的反斜杠,因为这是modelsim的读路径要求!否则modelsim 找不到库文件,做这个的目的在于把这些库作为modelsim的默认库,以后都可以启动就直接调用。

OK,可以开始准备仿真了!!!

3、仿真IP core:

-assignment->settings->如下图:

选择好仿真工具为modelsim,大部分默认,点击More NativeLink Settings按钮,设置用户已编译仿真库位置,如下图:

在setting中选择刚刚输出编译好的仿真库的路径-tool ->option->

开启功能仿真过程:

第一次功能仿真几乎肯定是不成功的,错误如下:

在E:\module\Eth_megacore\testbench\model下面找到这些文件

这些就是传说中的仿真模型simulation model !也就是说仿真没有能够成功加载仿真模型,肯定无法成功了!

在modelsim中点击compile ,出现下面窗口:

选择E:\module\Eth_megacore\testbench\model中所有文件(除timing开头的那些,那些是做时序仿真用的),编译到work库中去,然后查看仿真脚本文件transcript,可以看出

刚才编译的脚本语句为:

vlog -reportprogress 300 -work work

E:/module/Eth_megacore/testbench/model/top_mdio_slave.v

E:/module/Eth_megacore/testbench/model/ethgen2.v

E:/module/Eth_megacore/testbench/model/ethgen.v

E:/module/Eth_megacore/testbench/model/ethmon2.v

E:/module/Eth_megacore/testbench/model/ethmon.v

E:/module/Eth_megacore/testbench/model/loopback_adapter.v

E:/module/Eth_megacore/testbench/model/loopback_adapter_fifo.v

E:/module/Eth_megacore/testbench/model/mdio_reg.v

E:/module/Eth_megacore/testbench/model/mdio_slave.v

把这些语句全部复制到do文件中去

粘贴的位置不能错,错了就无法启动功能仿真了!

OK!终于看到仿真波形了:

注意testbench采用了loopback技术,即自发自收,即如果能够收到和自己发送的相同数据的话,那么这个IP的功能就实现了,从图中看出RGMII接口的输入和输出数据均为1010,故整个的基本收发功能是正确的!

查看脚本,也可以证实这一点:

西安理工大学 研究生课程论文/研究报告 课程名称:EDA技术与ASIC设计 课程代号:050112 任课教师:高勇 报告题目:CPLD器件简介 完成日期:2011 年8 月31 日学科:微电子学与固体电子学 学号:1008090513 姓名:杨宗凯

CPLD器件简介 早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可按除只读存贮器(EPROM)和电可擦除只读存贮器(EEPROM)三种。由于结构的限制,它们只能完成简单的数字逻辑功能。其后,出现了结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),它能够完成各种数字逻辑功能。典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与—或”表达式来描述,所以,PLD能以乘积和的形式完成大量的组合逻辑功能。这一阶段的产品主要有PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。还有一类结构更为灵活的逻辑器件是可编程逻辑阵列(PLA),它也由一个与”平面和一个“或”平面构成,但是这两个平面的连接关系是可编程的。PLA器件既有现场可编程的,也有掩膜可编程的。在PAL的基础上,又发展了一种通用阵列逻辑GAL(Generic Array Logic),如GAL16V8,GAL22V10等。它采用了EEPROM工艺,实现了电可擦除、电可改写,其输出结构是可编程的逻辑宏单元,因而它的设计具有很强的灵活性,至今仍有许多人使用。这些早期的PLD器件的一个共同特点是可以实现速度特性较好的逻辑功能,但其过于简单的结构也使它们只能实现规模较小的电路。 20世纪80年代中期,Altera和Xilinx分别推出了类似于PAL结构的扩展型CPLD(Complex Programmable Logic Dvice)和与标准门阵列类似的FPGA(Field Programmable Gate Array),它们都具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。这两种器件兼容了PLD和通用门阵列的优点,可实现较大规模的电路,编程也很灵活。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。 FPGA(现场可编程门阵列)与CPLD(复杂可编程逻辑器件)都是可编程逻辑器件,它们是在PAL,GAL等逻辑器件的基础之上发展起来的。同以往的PAL,GAL等相比较,FPGA/CPLD的规模比较大,它可以替代几十甚至几千块通用IC芯片。这样的FPGA/CPLD实际上就是一个子系统部件。这种芯片受到世界范围内电子工程设计人员的广泛关注和普遍欢迎。经过了十几年的发展,许多公司都开发出了多种可编程逻辑器件。比较典型的就是Xilinx公司的FPGA器件系列和Altera公司的CPLD器件系列,它们开发较早,占有了较大的PLD市场。 FPGA,CPLD和其它类型PLD的结构各有其特点和长处,但概括起来,它们是由三大部分组成的: 1.可编程内部连线。为各逻辑块之间,以及逻辑块和I/O单元之间提供互连网络,实现信号连线。 2.逻辑块。包括实现乘积项的与阵列、乘积项分配和逻辑宏单元等,用于实现各种逻辑功能。 3. I/O单元。用于实现信号从器件输出,以及为输入信号提供输入通道。通常具有输入、输出和双向I/O模式。连线资源:由各种长度的连线线段组成,其中也有一些可编程的连接开关,它们用于逻辑块之间、逻辑块与输入/输出块之间的连接。 对用户而言,CPLD与FPGA的内部结构稍有不同,但用法一样,所以多数情况下,不加以区分。FPGA/CPLD芯片都是特殊的ASIC芯片,它们除了具有ASIC的特点之外,还具有以下几个优点:(1)随着VISI(Very Large Scale IC,超大规模集成电路)工艺的不断提高单一芯片内部可以容纳上百万个晶体管,FP2GA/CPLD芯片的规模也越来越大,其单片逻辑门数已达到上百万门,它所能实现的功能也越来越强,同时也可以实现系统集成。(2)FPGA/CPLD芯片在出厂之前都做过百分之百的测试,不需要设计人员承担投片风险和费用,设计人员只需在自己的实验室里就可以通过相关的软硬件环境来完成芯片的最终功能设计。 (3)用户可以反复地编程、擦除、使用或者在外围电路不动的情况下用不同软件就可实现不同的功能。FPGA/CPLD软件包中有各种输入工具和仿真工具,及版图设计工具和编程器等全线产品,电路设计人员在很短的时间内就可完成电路的输入、编译、优化、仿真,直至最后芯片的制作。当电路有少量改动时,更能显示出FPGA/CPLD的优势。电路设计人员使用FPGA/CPLD进行电路设计时,不需要具备专门的IC(集成电路)深层次的知识,FPGA/CPLD软件易学易用,可以使设计人员更能集中精力进行电路设计,快速将产品推向市场。 Altera公司的CPLD有Classic系列和MAX系列。MAX系列产品是采用的乘积项阵列结构,分为:

ALTERA - EPCS 型号工作电压 存储器容 量 编程类型封装类型温度等级备注 EPCS1 2.7-3.6 V 1 Mbit ISP SOIC8 -40℃~ 85℃ FPGA配置器件 ——串行系列 EPCS4 2.7-3.6 V 4 Mbit ISP SOIC8 -40℃~85℃ EPCS16 2.7-3.6 V 16 Mbit ISP SOIC8, SOIC16 -40℃~ 85℃ EPCS64 2.7-3.6 V 64 Mbit ISP SOIC16 -40℃~85℃ EPCS128 2.7-3.6 V 128 Mbit ISP SOIC16 -40℃~85℃ ALTERA - MAX Ⅱ 型号V CCINT逻辑元 UFM Size (bits) 等效宏单元典 型值 t PD1 (ns) MAX I/O ISP EPM240 3.3V/2.5V 240 8,192 192 4.7 80 YES EPM240G 1.8V 240 8,192 192 4.7 80 YES EPM570 3.3V/2.5V 570 8,192 440 5.4 160 YES EPM570G 1.8V 570 8,192 440 5.4 160 YES EPM1270 3.3V/2.5V 1,270 8,192 980 6.2 212 YES EPM2210 3.3V/2.5V 2,210 8,192 1,700 7.0 272 YES ALTERA - MAX 3000A 型号 工作电压门数宏单元逻辑阵列模块MAX I/O ISP 备注EPM3032A 3.3V 600 32 2 34 YES EPM3064A 3.3V 1,250 64 4 34 / 66 YES EPM3128A 3.3V 2,500 128 8 80 / 96 / 98 YES EPM3256A 3.3V 5,000 256 16 116 / 158 / 161 YES EPM3512A 3.3V 10,000 512 32 172 / 208 YES

Altera、Xilinx、Actel Altera作为世界老牌可编程逻辑器件的厂家,是可编程逻辑器件的发明者,开发软件 MAX+PLUSII和QuartusII。Altera 的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone,CycloneII;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix,StratixII等,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。 * Cyclone(飓风):Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列,是目前主流产品,其配置芯片也改 用全新的产品。 简评:Altera最成功的器件之一,性价比不错,是一种适合中低端应用的通用FPGA,推荐使用。 * CycloneII:Cyclone的下一代产品,2005年开始推出,90nm工艺,1.2v内核供电,属于低成本FPGA,性能和Cyclone相当,提供了硬件乘法器单元 简评:刚刚推出的新一代低成本FPGA,目前市场零售还不容易买到,估计从2005年年底开始,将逐步取代Cyclone器件,成为Altera在中低FPGA市场中的主力产品。 * Stratix :altera大规模高端FPGA,2002年中期推出,0.13um工艺,1.5v内核供电。集成硬件乘加器,芯片内部结构比Altera以前的产品有很大变化。 简评:Startix芯片在2002年的推出,改变了Altera在FPGA市场上的被动局面。该 芯片适合高端应用。随着2005年新一代StratixII器件的推出,将被StratixII逐渐取代。 * StratixII: Stratix的下一代产品,2004年中期推出,90nm工艺,1.2v内核供电,大 容量高性能FPGA。 简评:性能超越Stratix,是未来几年中,Altera在高端FPGA市场中的主力产品。 *StrtratixV为altera目前的高端产品,采用28-nm工艺,提供了28G的收发器件,适合高端的FPGA产品开发 Xilinx是FPGA的发明者,拥有世界一半以上的市场,提供90%的高端65nmFPGA产品,开发软件为ISE。Xilinx的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Spartan系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Virtex系列,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。 * Spartan-3/3L: 新一代FPGA产品,结构与VirtexII类似,全球第一款90nm工艺FPGA,1.2v内核,于2003年开始陆续推出。 简评:成本低廉,总体性能指标不是很优秀,适合低成本应用场合,是Xilinx未来几年在低端FPGA市场上的主要产品,目前市场上中低容量型号很容易购买到,大容量相对少 一些。 * Spartan-3E:基于Spartan-3/3L,对性能和成本进一步优化 * Spartan-6:xilinx最新推出的低成本FPGA

芯片了解: 一、Xilinx 的主流FPGA 分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Spartan 系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Virtex 系列,用户可以根据自己实际应用要求进行选择。 在性能可以满足的情况下,优先选择低成本器件。 1.spartan —3 Spartan-3系列FPGA 【15】 是为那些需要大容量、低价格电子应用的用户而设计的。该系统的8种FPGA 密度从5万到500万门。Spartan-3系列是在Spartan-IIE 成功的基础上通过增加逻辑资源、增加内部RAM 容量、增加I/O 引脚数量、增加时钟管理功能以及增加总体性能来实现的,很多增强的功能都来自于Virtex-II 技术。这些结合了先进处理技术的改进,使得Spartan-3的性价比超出以前所能达到的水平。也为可编程逻辑器件提供了新的标准。由于异常的低价,Spartan-3可广泛地应用于各种电子设计,包括军工航天、宽带接入、家庭网络、投影电视、数字电视。Spartan-3还是替代ASIC 的更佳选择。不同于通常的ASIC ,FPGA 减少了初期成本并缩短了开发周期。同时,FPGA 的可编程性也使得它能在不需要考虑硬件更改的情况下进行设计升级,这是ASIC 不能做到的。 Spartan-3系列FPGA 产品的主要技术参数指标如表2.1所示。 表2.1 Spartan-3系列FPGA 技术参数 Spartan-3系列FPGA 结构包括5个基本的可编程功能单元:(1)可配置逻辑块(CLB )。该模块包括基于RAM 的查找表(LUT)。除了作为存储器外,CLB 还能通过编程实现很多的逻辑功能。 (2)输入/输出模块(IOB )。该模块控制I/O 引脚和内部逻辑单元之间的数据流动,每一个IOB 支持双向三态的数据流动,支持23种差分信号标准(其中有6种高性能差分标准)。输入/输出模块还包括了双数据速率寄存器(Double Data-Rate,DDR ),数控电阻(Digitally controlled Impedance, DCI )提供自动的片内终端,大大简化了电路板的设计。 (3)Block RAM 模块。该模块提供了18Kbit 的双口数据存储。 (4)乘法器模块。该模块提供了18位的二进制数据乘法。 (5)数字时钟管理模块(Digital Clock Manager,DCM)。该模块提供了自校准、全数字的解决方案,可以提供分布式的、延时的、合成频率的、分频的以及移相的时钟信号。 下为Spartan-3系列结构图 。 器件名称 逻辑单元 系统门密度 CLB 阵列 CLB 总 数 最大用户I/O 最大差分I/O 分布式RAM 容量/bit BlockR AM 容 量/bit XC3S50 1728 50K 16×12 192 124 56 12K 72K XC3S200 4320 50K 24×20 480 173 76 30K 216K XC3S400 8064 50K 32×28 896 264 116 56K 288K XC3S1000 17280 1M 48×40 1920 391 175 120K 432K XC3S1500 29952 1.5M 64×52 3328 487 221 208K 567K XC3S2000 46080 2M 80×64 5120 565 270 320K 720K XC3S4000 62208 4M 96×72 6912 712 312 432K 1728K XC3S5000 74880 5M 104×80 8320 784 344 520K 1872K

ETL-002 Altera Cyclone III 系列FPGA开发板简介 概述 ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述 主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。开发板同时支持AS模式下载和JTAG模式下载。程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。 丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。这些接口主要包括: PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上 PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上 VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。开发板自带了动态彩条显示的功能 双串口接口:可以与任何的串口设备相接。开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。开发板自带的演示程序实时地显示分钟和秒钟的信息。 4位LED灯:用于指示状态。开发板自带了跑马灯实验。 4位按键开关:可用于复位等作用。 4位拨码开关:可用于电路的选择作用

FPGA系统设计与应用

https://www.doczj.com/doc/584561476.html, https://www.doczj.com/doc/584561476.html,

华清远见

内容大纲

Altera的FPGA体系结构简介 Altera的FPGA选型策略 嵌入式逻辑分析工具SignalTAPII的使用 基于CPLD的FPGA配置方法

v v v v

华清远见

FPGA技术的发展历史和动向

电子器件:存储器、处理器和逻辑器件 v 存储器器件保存随机信息(电子数据表或数据库的 内容); v 处理器执行软件指令,以便完成各种任务(运行数 据处理程序或视频游戏); v 逻辑器件可以提供特殊功能(器件之间的通信和系 统必须执行的其它所有功能)。降低了成本、提高 了可靠性、缩小了物理尺寸

华清远见

逻辑器件分类

逻辑器件分成两类: v 固定的或定制的

固定的或定制的逻辑器件通常称为专用芯片 (ASIC)。ASIC是为了满足特定的用途而设计的芯 片,例如MP3解码芯片等。其优点是通过固化的逻 辑功能和大规模的工业化生产,降低了芯片的成 本,同时提高了产品的可靠性。

v 可编程的或可变的

华清远见

FPGA技术概念

v CPLD (Complex Programmable Logic Device) v FPGA (Field Programmable Gate Array) v 硬核:ARM、MIPS、POWERPC v 软核:Nios/NiosII v SOC: 片上系统 v SOPC:可编程片上系统 v IP核:知识产权

目录 1 设计准则 (1) 2 模块功能摘要 (1) 3 参考资料 (1) 4 基本原理 (1) 4.1 硬件连接 (2) 4.2 操作过程 (3) 4.3 数据转换 (4) 4.4 在线升级 (5) 4.4.1 硬件要求 (6) 4.4.2 软件要求 (6) 4.4.3具体过程 (6) 5 技术指标 (7) 6 电原理图 (7) 7 PCB图.................................................................................................... 错误!未定义书签。 8 结构图..................................................................................................... 错误!未定义书签。 9 输入、输出接口及性能参数................................................................. 错误!未定义书签。 10 软件 (7) 11 元器件说明..................................................................................... 错误!未定义书签。 12 可编程器件说明............................................................................. 错误!未定义书签。 13 可信性设计说明............................................................................. 错误!未定义书签。 14 电源和接地..................................................................................... 错误!未定义书签。 15 成本预计 (7) 16 背景资料 (7) 16.1.1 性能 (8) 16.1.2 特点 (8) 17 使用、调试、维护说明 (8) 17.1 调试环境................................................................................. 错误!未定义书签。 17.2 调试方法................................................................................. 错误!未定义书签。 17.3 故障解决方法 (8) 18 经验教训 (8) 19 应用示例 (9) 19.1 FPGA在线更改配置 (9) 19.2电缆下载 (10) 19.3 应用示例之源程序 (10)

1.从好用来说,肯定是Xilinx的好用,不过Altera的便宜 Altera的FPGA的短线资源经常不够用,经常要占用LE来充当布线资源〔这也是什么原因Altera的FPGA能够廉价的缘故,资源少些所以廉价〕,然而假如你是高手,也能把他的性能发挥得很好。 另外确实是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,假如你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,如此你的RAM资源就少了一半,假如你的应用对片内双口RAM的需求很重要,用Altera的就划不来。 2.Xilinx与Altera FPGA比较系列之一逻辑资源速度 一开始没想到那个比较会得到大伙的关注,纯粹是出于自己的兴趣。两个厂商都会宣称自己某一方面比对方好,到底是谁的更好呢?这确信是个仁者见仁,智者见智的问题。最近这段时间比较忙,项目到了比较关键的阶段,加上其他一些杂七杂八的情况,很难有比较完整的时间坐下来完成报告,直到今天才差不多把一些文档整理完。在整理的过程中,越来越觉得很难比较两者之间的速度,因为相关的因素实在太多了。软件的好坏,器件本身的延迟,设计等等对最优的速度都有着相当大的妨碍。做速度比较用的滤波器很难代表其他的设计,确实是抛砖引玉,盼望能够和大伙一起讨论FPGA的速度那个问题。在整理过程中,发明了许多很有趣的情况,比如StratixIII和StratixII的速度区别等。为此,作者做了一些简单的实验,盼望能够找到合理的解释,来分析出现这些现象的缘故。 编译之前的考虑 依照作者自己的一些经验,作者把常用的一些开关打开了,以便更好的优化速度。另外,有一些选项作者拿不准是否两个软件都有相似的开关,就没有打开。 为了使得比较更加合理,作者尽可能选择门数和IO速度都比较接近的FPGA。 Xilinx采纳ISE9.1ServicePack1版本,Altera采纳Quartus7.1ServicePa ck1版本, Xilinx:

NiosⅡ 目录 综述 分类 特点 开发环境 结 编辑本段综述 Nios Ⅱ嵌入式处理器是ALTERA公司推出的采用哈佛结构、具有32位 指令集的第二代片上可编程的软核处理器, 其最大优势和特点是模块化的硬件 结构, 以及由此带来的灵活性和可裁减性。相对于传统的处理器, Nios Ⅱ系统 可以在设计阶段根据实际的需求来增减外设的数量和种类。设计者可以使用ALTERA 提供的开发工具SOPC Builder, 在PL D器件上创建软硬件开发的 基础平台, 也即用SOPC Builder创建软核CPU和参数化的接口总线Avalon。在此基础上, 可以很快地将硬件系统(包括处理器、存储器、外设接口和用户 逻辑电路)与常规软件集成在单一可编程芯片中。而且, SOPC Builder还提供 了标准的接口方式,以便用户将自己的外围电路做成Nios Ⅱ软核可以添加的 外设模块。这种设计方式, 更加方便了各类系统的调试。 编辑本段分类 Nios II系列包括3种产品,分别是:Nios II/f(快速)——最高的系统性能,中等FPGA使用量;Nios II/s(标准)——高性能,低FPGA使用量;Nios II/e(经济)——低性能,最低的FPGA使用量。这3种产品具有32位处 理器的基本结构单元——32位指令大小,32位数据和地址路径,32位通用 寄存器和32个外部中断源;使用同样的指令集架构(ISA),100%二进制 代码兼容,设计者可以根据系统需求的变化更改CPU,选择满足性能和成本 的最佳方案,而不会影响已有的软件投入。 编辑本段特点 Nios II系列支持使用专用指令。专用指令是用户增加的硬件模块,它增 加了算术逻辑单元(ALU)。用户能为系统中使用的每个Nios II处理器创建 多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和本身Nios II指令相同,能够从多达两个源寄存器取值, 可选择将结果写回目标寄存器。同时,Nios II系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必 支付根本不使用的硅片功能。Nios II系列能够满足任何应用32位嵌入式微处理器的需要,客户可以将第一代Nios处理器设计移植到某种Nios II处理

简谈Altera和Xilinx的FPGA区别 大家好,又到了每日学习的时间了,最近有很多人再问我学习FPGA到底是选择Altera的还是xilinx的呢,于是我就苦口婆心的说了一大堆,中心思想大概就是,学习FPGA一定要学习FPGA的设计思想以及设计原理,不要纠结于单一的实验平台或者操作软件,因为你想在这个行业越走越高的话,广度和深度都是要有所了解的,初期学习的时候尤其注重动手,选择一款操作平台以及操作软件是为了让你更好的去动手做,而不是让你在这款软件或者实验平台去做文章,因为不懂原理的话,换个环境你同样是什么都不明白。尤其是现在的科技公司产品更新升级换代还比较快,要学会去掌握最核心的知识点才是王道。下面,就我自己接触,咱们就来简单聊聊Altera和Xilinx的FPGA 区别,欢迎大家一起交流,三人行,必有我师,共同学习,共同进步。对于Altera和Xilinx 的FPGA,本人认为可以分为两个方面去比较一下,基本逻辑资源和内部基本架构。从目前企业中做开发使用的广泛性来说,Xilinx占得比重确实是大一些,但是从其他方面来说,比如价格,相对而言Altera的便宜些。对于两者的特点,Xilinx的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较满的时候。而Altera的FPGA 的短线资源经常不够用,经常要占用LE来充当布线资源,这也是为什么Altera的FPGA 可以便宜的原因,资源少些当然便宜,但是如果你是高手,也能把他的性能发挥得很好。另外就是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用Altera的就划不来。下面咱们就从我刚才说的基本逻辑资源和内部基本架构这两个方面来聊聊。 1.基本逻辑资源基本的逻辑资源我建议大家可以去看看两家的芯片做个比较,今天时间有限就不给各位详谈了,通过比较你会发现我上面说的还是有点道理的。 2.内部基本架构从1985年Xilinx公司推出第一片FPGA到现在,FPGA的使用已经有近30年的历史了。目前主流市场的FPGA主要还是Xilinx和Altera两大系列,下面分别来介绍下它们各自的基本结构组成。 Xilinx的FPGA主要由以下单元结构组成:可配置

FPGA的基本结构 FPGA由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。 FPGA的基本结构 每个单元简介如下: 1.可编程输入/输出单元(I/O单元) 目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟使能的触发器,也可以配置成为锁存器。FPGA一般依赖寄存器完成同步时序逻辑设计。一般来说,

比较经典的基本可编程单元的配置是一个寄存器加一个查找表,但不同厂商的寄存器和查找表的内部结构有一定的差异,而且寄存器和查找表的组合模式也不同。 学习底层配置单元的LUT和Register比率的一个重要意义在于器件选型和规模估算。由于FPGA内部除了基本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL,专用的Hard IP Core等,这些模块也能等效出一定规模的系统门,所以简单科学的方法是用器件的Register或LUT的数量衡量。 3.嵌入式块RAM 目前大多数FPGA都有内嵌的块RAM。嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构。 CAM,即为内容地址存储器。写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。简单的说,RAM是一种写地址,读数据的存储单元;CAM与RAM恰恰相反。 除了块RAM,Xilinx和Lattice的FPGA还可以灵活地将LUT配置成RAM、ROM、FI FO等存储结构。 4.丰富的布线资源 布线资源连通FPGA内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。布线资源的划分: 1)全局性的专用布线资源:以完成器件内部的全局时钟和全局复位/置位的布线; 2)长线资源:用以完成器件Bank间的一些高速信号和一些第二全局时钟信号的布线(这里不懂什么是“第二全局时钟信号”); 3)短线资源:用来完成基本逻辑单元间的逻辑互连与布线; 4)其他:在逻辑单元内部还有着各种布线资源和专用时钟、复位等控制信号线。 由于在设计过程中,往往由布局布线器自动根据输入的逻辑网表的拓扑结构和约束条件选择可用的布线资源连通所用的底层单元模块,所以常常忽略布线资源。其实布线资源的优化与使用和实现结果有直接关系。 5.底层嵌入功能单元 底层嵌入功能单元是指通用程度较高的嵌入式功能模块。如锁相环(Phase Locked Loop, PLL)、DLL(Delay Locked Loop)、DSP(Digital Signal Processing)和CPU等。 6.内嵌专用硬核

目录 1概述 6 2基于块的设计方法 6 3STRATIX系列器件介绍7 3.1STRATIX系列器件所具有的新特性:7 3.2STRATIX系列器件内部结构7 3.3内部连线8 3.4内部存储单元8 3.5内置DSP单元10 3.6I/O接口12 3.7时钟系统12 3.8远程升级功能13 3.9其他13 4STRATIX器件家族及封装13

表目录 表1 STRATIX内部存储单元特性9 表2 STRATIX器件内部存储单元容量及最大带宽9 表3 STRATIX系列器件乘法器列表12 表4 STRATIX系列器件I/O端口支持标准12 表5 STRATIX器件家族14 表6 STRATIX系列器件封装14 图目录 图1可编程逻辑设计方法演进趋势 6 图2基于STRATIX系列器件的设计流程7 图3 STRATIX系列器件内部结构8 图4 STRATIX系列器件内部存储单元9 图5 DSP单元内部结构10 图6 DSP单元实现四组2输入乘法器10 图7 DSP单元实现两组2输入乘法累加器11 图8 DSP单元实现两组4输入乘加器11 图9 DSP单元实现一组8输入乘加器11

ALTERA公司STRATIX系列可编程逻辑器件技术交流报告 关键词: ALTERA,STRATIX,可编程逻辑,器件 摘要:本文主要对ALTERA公司STRATIX系列器件及其Block-Based的设计方法进行了简要介绍。 缩略语清单: PLL:Phase Locked Loop 锁相环 MegaRAM:STRATIX器件容量为512K的内部存储单元

1 概述 STRATIX 系列可编程逻辑器件是ALTEREA 公司即将于年内推出的一款高性能可编程逻辑器件。该系列器件采用1.5V,0.13um 工艺,可同时提供最多114,140个LE 和10Mbits RAM 空间。STRATIX 系列器件可提供包含多达224个9bit*9bit 内置乘法器的28个DSP 功能块,其经过优化的结构可以有效实现高性能滤波器和乘法器。 STRATIX 系列器件不仅支持多种IO 标准,而且提供基于其内部最多12个可达到420MHz 锁相环的层次化时钟系统。 2 基于块的设计方法 随着可编程逻辑设计复杂度的不断提高和产品所面临的不断增大的市场压力,可编程逻辑设计方法也在不断演进。图1清楚的表明了这种演进趋势。 í?1 可编程逻辑设计方法演进趋势 由上图可知,随着芯片复杂度的不断提高,基于Block 的设计方法正在成为一种设计趋势。这种设计方法之所以能有效的缩短产品开发周期及面世时间,主要原因是因为这种方法具有以下特点: 可以很好的支持团队开发模式中新模块的并行开发; 可方便的使用数量庞大的可重用功能模块。这些功能模块可能来自原有设计,也 可能来自第三方设计公司或是可编程逻辑器件厂商提供的IP Core 。 在以往的可编程逻辑器件中使用这种设计方法时,通常要在Block 集成阶段面对逻辑优化的问题。这主要是因为各个Block 逻辑在集成阶段往往会因为器件资源等问题相互影响,导致总体性能的下降。为此,STRATIX 系列器件专门针对该问题提供了逻辑

用CPU配置Altera公司的FPGA 一. 概述 目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对FPGA进行配置。专用的EPROM价格不便宜,且大部分都是一次性OTP方式编程。一旦更改FPGA设计,代价不小。为了进一步降低产品的成本和升级成本,可以考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU模拟专用EPROM对FPGA进行配置。本文将以PowerPC860和EP1K30为例,讲解如何利用CPU来配置FPGA。 CPU配置FPGA的优点 与Configuration EPROM方式相比本设计有如下优点: 1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。以A LTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的价格要几十元,容量1M位。提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。即使增加1Mb存储空间,通用存储器也会比FPGA专用EPROM便宜。 2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。如果使用本设计对FPGA配置,选用可擦除的通用存储器保存FPGA的编程数据,更换FPGA版本,无须付出任何硬件代价。这也是降低硬件成本的一个方面。 3.实现真正"现场可编程"--FPGA的特点就是"现场可编程",只有使用CPU对FPGA 编程才能体现这一特点。如果设计周全的话,单板上的FPGA可以做到在线升级。 4.减少生产工序--省去了对"FPGA专用EPROM"烧结的工序,对提高生产率,降低生产成本等均有好处。对于双面再流焊的单板,更可省去手工补焊DIP器件的工序。 当然,与Configuration EPROM方式相比也有一些需要注意的的地方:

Altera CPLD的简介 Altera在近十五年CPLD经验基础上,推出了成本很低的CPLD――MAX II系列。MAX II器件的成本是相竞争CPLD的一半,它采用了新的查找表(LUT)体系,因此每个I/O管脚的成本很低,而且开创了CPLD体系的新纪元。这种即用的非易失器件系列面向通用的小容量逻辑应用,从而设计者能够发挥CPLD器件的优势,替代小型ASIC和ASSP。 MAX II器件采用了成本优化的六层金属0.18微米Flash工艺,其功耗大约是前一代MAX器件的十分之一。它们的容量从240至2,210个逻辑单元(LE)(192至1,700个等效宏单元),多达272个用户I/O管脚。表1是MAX II器件的主要特性,表2是可提供的封装。 MAX II的特性 MAX II器件包括一些能够充分发挥技术创新的新特性,这也是Altera的传统。该器件系列是专为降低新老CPLD应用成本而设计的。 重要的MAX II特性包括: 功耗是前一代CPLD系列的十分之一――MAX II器件的动态功耗很低,所以运行功耗较低。MAX II 系列功耗是低成本MAX 3000A系列的十分之一。 容量翻两番――器件容量等效于大约192至1700个宏单元。这是Altera以往系列的四倍。 性能翻倍――由于MAX II器件系列布线体系、软件算法和工艺技术的改进,性能平均比MAX 7000AE快两倍。 用户Flash存储器――Altera据称是首家在可编程逻辑器件(PLD)内提供用户Flash存储器的可编程逻辑供应商。因此,MAX II器件系列能够省去常用的串行或并行EEPROM,它们的批量价格通常在50美分至2美元之间,从而进一步降低了终端系统的成本。整个系列每个器件的存储容量为8K比特。 实时在系统可编程性(ISP)――用于能够在不中断功能的情况下实时地重新配置MAX II器件。这允许客户为运行中的客户系统增加功能或灵活性。 有关MAX II器件特性的完整说明,请浏览Altera网站https://www.doczj.com/doc/584561476.html,/max2。 表1. 产品系列表(略) 注释: (1) 和最快的商用速度等级相关,是指穿越器件的对角点延迟路径的时间。 (2) 所有的封装支持所有容量间的垂直移植。

著名半导体相关公司LOGO 作者 : 张晓朋 ETHAN 英特尔公司(Intel Corporation),是世界上最大的半导体公司,也是第一家推出 x86 架构处理器的公司,总部位于美国加州圣克拉拉。由罗伯特·诺宜斯、高登·摩尔、安迪·葛洛夫,以集成电路之名(integrated electronics)在 1968 年共同创办 Intel 公司,将高级芯片设计能力与领导业界的制造能力结合在一起。Intel 也有开发主板芯片组、网络卡、闪存、绘图芯片、嵌入式处理器,与对通信与计算相关的产品等。现任经营高层是董事长-克雷格·贝瑞特及总经理兼运行长-保罗·欧德宁。Intel Inside 的广告标语与 Pentium 系列处理器在 90 年代间非常成功的打响Intel 的品牌名号。 超威半导体公司(英文:Advanced Micro Devices, Inc.,简称AMD)是一家专注于微处理器设计和生产的跨国公司,总部位于美国加州硅谷内森尼韦尔。AMD为电脑、通信及消费电子市场供应各种集成电路产品,其中包括中央处理器、图形处理器、闪存、芯片组以及其他半导体技术。公司的主要设计及研究所位于美国和加拿大,主要生产设施位于德国,还在新加坡、马来西亚和中国等地设有测试中心。 英飞凌科技公司(Infineon Technologies)总部位于德国慕尼黑,是德国最大的半导体产品制造商,法兰克福上市代码:IFX。其前身是西门子集团的半导体部门,于1999年独立,2000年上市。其中文名称为亿恒科技,2002年后更名为英飞凌科技。其主要产品为:内存通信芯片;汽车、工业芯片及智能卡。

1. 从好用来说,肯定是Xilinx的好用,不过Altera的便宜 他们的特点,Xilinx的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较满的时候。 Altera的FPGA的短线资源经常不够用,经常要占用LE来充当布线资源(这也是为什么Altera的FPGA可以便宜的原因,资源少些当然便宜),但是如果你是高手,也能把他的性能发挥得很好。 另外就是关于块RAM,Xilinx的双口RAM是真的,Altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用Altera 的就划不来。 2. Xilinx与Altera FPGA比较系列之一逻辑资源速度 一开始没想到这个比较会得到大家的关注,纯粹是出于自己的兴趣。两个厂商都会宣称自己某一方面比对方好,到底是谁的更好呢?这肯定是个仁者见仁,智者见智的问题。最近这段时间比较忙,项目到了比较关键的阶段,加上其他一些杂七杂八的事情,很难有比较完整的时间坐下来完成报告,直到今天才基本把一些文档整理完。在整理的过程中,越来越觉得很难比较两者之间的速度,因为相关的因素实在太多了。软件的好坏,器件本身的延迟,设计等等对最优的速度都有着相当大的影响。做速度比较用的滤波器很难代表其他的设计,算是抛砖引玉,希望能够和大家一起讨论FPGA的速度这个问题。在整理过程中,发现了很多很有趣的事情,比如Stratix III和Stratix II的速度区别等。为此,作者做了一些简单的实验,希望能够找到合理的解释,来分析出现这些现象的原因。 编译之前的考虑 根据作者自己的一些经验,作者把常用的一些开关打开了,以便更好的优化速度。另外,有一些选项作者拿不准是否两个软件都有相似的开关,就没有打开。 为了使得比较更加合理,作者尽可能选择门数和IO速度都比较接近的FPGA。 Xilinx采用ISE9.1 Service Pack1版本,Altera采用Quartus7.1 Servic e Pack1版本, Xilinx:

?2004 Altera Corporation ALM vs. Slice Discussion and Design Examples v.1.3 June 15, 2004 Agenda n ALM Introduction n ALM vs. Slice Comparison n Conclusion

3 ?2004 Altera Corporation -Confidential What is Adaptive Logic Module (ALM) Reg Reg Reg Reg Adder Adder Adder Adder 12345678 Comb. Logic Adaptive Logic Usage Flexible Input Sharing A L M I n p u t s ALM Xilinx Slice Claim n Xilinx Claims ALM = Slice. Why? ?Both Have 8 Inputs to LUT ?Both Have 2 Flip Flops, 2 Bits of Arithmetic n All Cars Have Four Wheels: SUV =Sedan?n Xilinx Also Claims Slices Can Implement 6-Input LUTs What is the Real Story?

5 ?2004 Altera Corporation -Confidential ALM is More than A Simple Slice n Eight Simple Examples Showing Differences ?One 6-Input Function ?Two 5-Input Functions (Input Sharing)?3 and 5-Input Functions ?7-Input Functions (2 Examples)?16-Bit Barrel Shifter ?16-Bit Crossbar Switch ? Ternary Adder n Truth About Xilinx’s “Variable LUT Architecture”White Paper n Slice Discussion is Applicable to Virtex-II, Virtex-II Pro, Spartan-2E and Spartan-3 Families 6-Input Function Example n A Function of 6 Inputs –a , b , c , d , e,f n Stratix II ALM Can Implement Any 6-Input Function module function_6_reg(a, b, c, d, e, f, out, reset, clk); input a, b, c, d, e, f, reset, clk;output out; reg out, reg_a, reg_b, reg_c, reg_d, reg_e, reg_f; always@ (posedge clk) begin if (reset) begin out <= 0; end else begin {reg_a, reg_b, reg_c, reg_d, reg_e, reg_f} <= {a, b, c, d, e, f};out <= (reg_a + reg_b + reg_c + reg_d + reg_e + reg_f == 4) || (reg_a ^ reg_b ^ reg_c ^ reg_d ^ reg_e ^ reg_f); end end