第 2 章逻辑门电路

2.2基本逻辑门电路

在数字系统中,大量地运用着执行基本逻辑操作的电路,这些电路称为基本逻辑电路或门电路。早期的门电路主要由继电器的触点构成,后来采用二极管、

三极管,目前则广泛应用集成电路。

2.2.1三种基本门电路

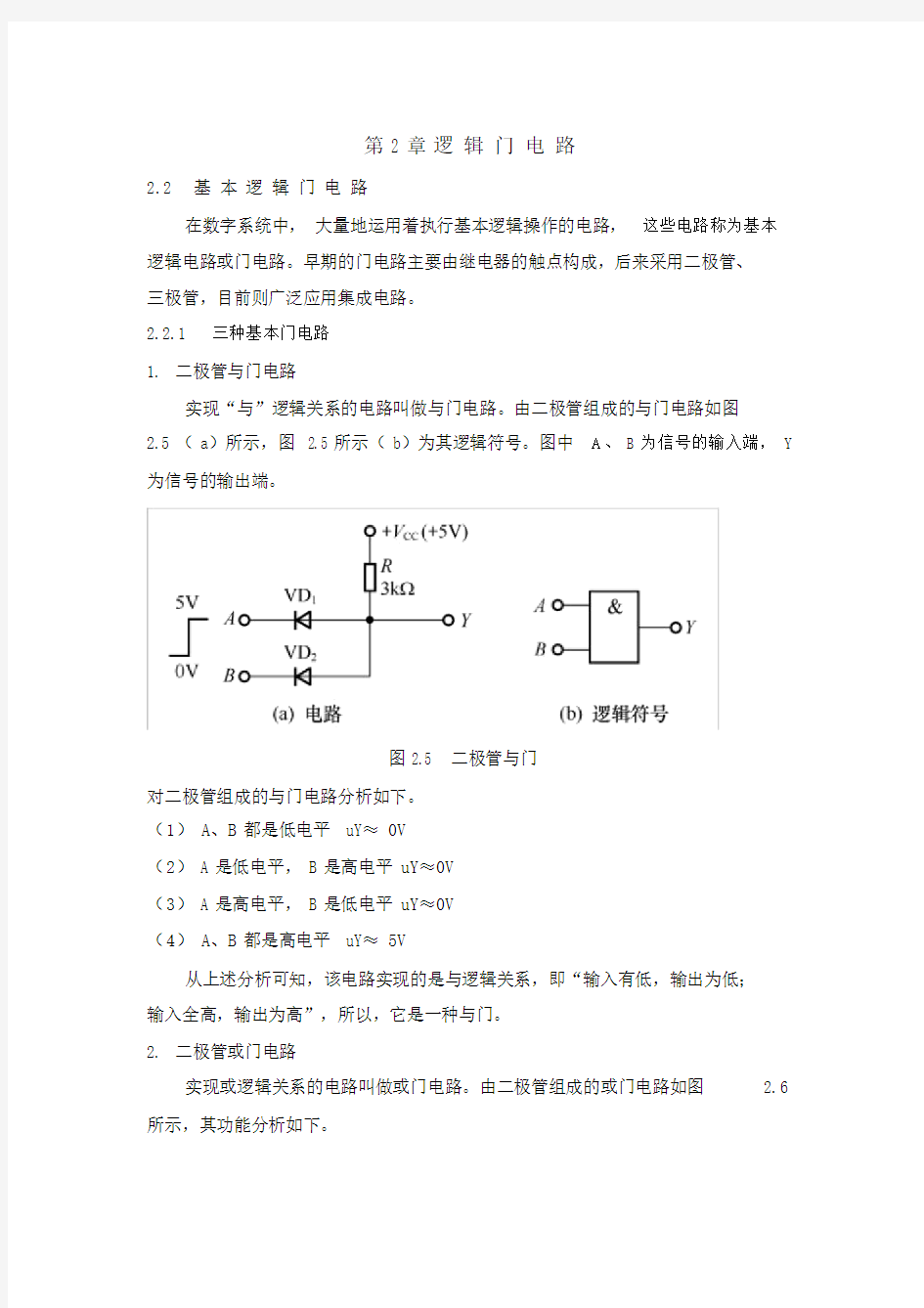

1.二极管与门电路

实现“与”逻辑关系的电路叫做与门电路。由二极管组成的与门电路如图

2.5 ( a)所示,图 2.5 所示( b)为其逻辑符号。图中A、 B 为信号的输入端, Y 为信号的输出端。

图2.5 二极管与门

对二极管组成的与门电路分析如下。

(1) A、B 都是低电平 uY≈ 0V

(2) A 是低电平, B 是高电平 uY≈0V

(3) A 是高电平, B 是低电平 uY≈0V

(4) A、B 都是高电平 uY≈ 5V

从上述分析可知,该电路实现的是与逻辑关系,即“输入有低,输出为低;

输入全高,输出为高”,所以,它是一种与门。

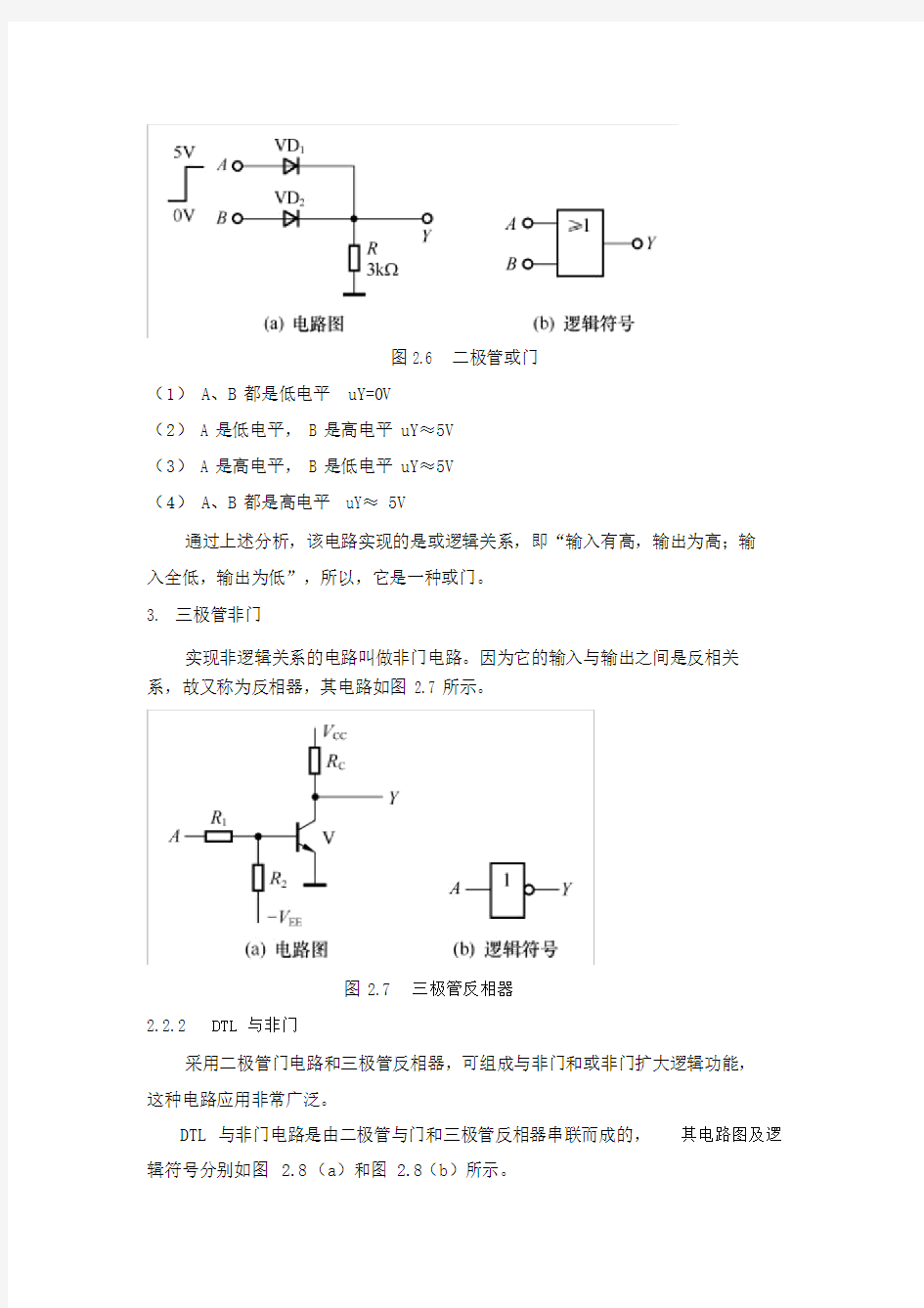

2.二极管或门电路

实现或逻辑关系的电路叫做或门电路。由二极管组成的或门电路如图 2.6所示,其功能分析如下。

图2.6 二极管或门

(1) A、B 都是低电平 uY=0V

(2) A 是低电平, B 是高电平 uY≈5V

(3) A 是高电平, B 是低电平 uY≈5V

(4) A、B 都是高电平 uY≈ 5V

通过上述分析,该电路实现的是或逻辑关系,即“输入有高,输出为高;输

入全低,输出为低”,所以,它是一种或门。

3.三极管非门

实现非逻辑关系的电路叫做非门电路。因为它的输入与输出之间是反相关

系,故又称为反相器,其电路如图 2.7 所示。

图 2.7三极管反相器

2.2.2DTL与非门

采用二极管门电路和三极管反相器,可组成与非门和或非门扩大逻辑功能,

这种电路应用非常广泛。

DTL 与非门电路是由二极管与门和三极管反相器串联而成的,其电路图及逻辑符号分别如图 2.8 (a)和图 2.8 (b)所示。

图2.8 DTL与非门

当输入端 A、 B 都是高电平时, VD1、VD2 均截止,而 VD3、 VD4 和三极管导通,注入三极管的基极电流足够大,三极管饱和导通,输出低电平,uY=0V,在两个输入端 A、B 中有一个为低电平时, VD3、VD4 和三极管均截止,输出高电平,uY=VCC。可见此逻辑门能实现与非逻辑关系。

2.3TTL逻辑门电路

TTL门电路是晶体

- 晶体管逻辑(Transistor- Transistor Logic )门电路管

的简称,这种电路由于其输入级和输出级均采用晶体三极管而得名。

按照国际通用标准,根据工作温度不同,TTL 电路分为54 系列( -55 ℃~125℃)和 74 系列( 0℃~ 70℃);根据工作速度和功耗不同,TTL 电路又分为标准系列、高速( H)系列、肖特基( S)系列和低功耗肖特基(LS)系列。

2.3.1TTL与非门的工作原理

1.TTL 与非门的电路结构

TTL 与非门的基本电路如图 2.9 (a)所示,它由输入级、中间级和输出级三部分

组成。

图2.9 基本 TTL与非门电路及 V1 管的等效电路

2.TTL 与非门的工作原理

(1)当 A、B 两端有一个输入为低电平 0.3 V 时, V1 的发射结导通,其基极电压等于输入低电压加上发射结正向压降。

V2、V5 都截止

V3 和 V4 导通

输出电压为: 3.6 V

实现了“输入有低,输出为高”的逻辑关系。

2)当 A、 B 两端均输入高电平3.6 V 时, V2、 V5 饱和导通,输出为低电平,即uo≈ UCES≈ 0.3 V

V1 处于发射结和集电结倒置使用的放大状态。

uC2=UCES2+uB5=0.3+0.7=1.0 V

由于 uB4=uC2=1.0 V,作用于 V3 和 V4 的发射结的串联支路的电压为:

uC2- uO=1.0-0.3=0.7V

所以,V3 和 V4 均截止。此时,电路实现了“输入全高,输出为低”的逻辑关系。

2.4其他类型的TTL门电路

将两个门的输出端并联以实现与逻辑的功能,把这种连接方式称为“线

与”。如果将两个门电路的输出端连接在一起,如图2.18 所示。当一个门的输出处于高电平,而另一个门的输出为低电平时,将会产生很大的电流,有可能导致器件损坏,无法形成有用的线与逻辑关系。

图 2.18 推拉式输出级并联的情况

2.4.1集电极开路与非门(OC门)

集电极开路与非门是将推拉式输出级改为集电极开路的三极管结构,做成集电极开路输出的门电路(OpenCollector Gate),简称为 OC门,其电路如图 2.19( a)所示。

图2.19 OC与非门的电路和图形符号

将OC门输出连在一起时,再通过一个电阻接外电源,这样可以实现“线与”逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出

的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。而且输出三极管的负载电流又不至于过大。两个 OC门并联时的连接方式如图 2.20 所示。

图2.20OC门输出并联的接法及逻辑图

在图 2.21 中表示出“线与”电路中OC门输出高电平的情况,假定n 个 OC 门连接成“线与”逻辑,带m个与非门负载。当所有OC门都处于截止状态时,“线与”后输出为高电平。

图 2.21 “线与”电路中OC门输出高电平的情况

OC 门除了可以实现多门的线与逻辑关系外,还可用于直接驱动较大电流的

负载,如继电器、脉冲变压器、指示灯等,也可以用来改变TTL电路输出的逻辑电平,以便与逻辑电平不同的其他逻辑电路相连接。

2.4.2 三态门( TSL门)

为保持推拉式输出级的优点,还能作线与连接,人们又开发了一种三态与非门,它的输出除了具有一般与非门的两种状态外,还可以呈现高阻状态,或称开

路状态、禁止状态。

一个简单的三态门的电路如图 2.23( a) 所示,图 2.23( b) 所示为它的逻辑符号,它是由一个与非门和一个二极管构成的, EN为控制端, A、B 为数据输入端。

图2.23 三态与非门电路

图2.23 所示电路中,当EN=1 时电路为工作状态,所以称为控制端高电平

有效。三态门的控制端也可以是低电平有效,即 EN为低电平时,三态门为工作状

态; EN为高电平时,三态门为高阻状态。其电路图及逻辑符号如图 2.24 所示。

图2.24 控制端为低电平有效的三态门

三态门的应用比较广泛,下面举例说明三态门的 3 种应用。电路图如图 2.25

所示。

作多路开关

信号双向传输

构成数据总线

图 2.25三态门三种应用的连接方式

2.8门电路在实际应用中应注意的问题

2.8.1 多余输入端的处理

在使用集成门电路时,如果输入信号数小于门的输入端数,就有多余输入端。一般不让多余的输入端悬空,以防止干扰信号引入。对多余输入端的处理,以不改变电路工作状态及稳定可靠为原则。

对于 TTL 与非门,通常将多余输入端通过1kΩ的电阻 R 与电源 +VCC相连;也可以将多余输入端与另一接有输入信号的输入端连接。这两种方法如图 2.34所示。 TTL 与门多余输入端的处理方法和与非门完全相同。

图 2.34TTL 与非门多余输入端的处理方法

对于TTL 或非门,则应该把多余输入端接地,或把多余输入端与另一个接有输入信号的输入端相接。这两种方法如图2.35 所示。TTL 或门多余输入端的处理方法和或非门完全相同。

图 2.35TTL 或非门多余输入端的处理方法

对于 CMOS电路,多余的输入端必须依据相应电路的逻辑功能决定是接在正

电源 VDD上(与门、与非门)或是与地相接(或门、或非门)。一般不宜与使用的输入端并联使用,因为输入端并联时将使前级的负载电容增加,工作速度下降,动态功耗增加。