实训一 简易数字钟的EDA设计

1.2.1 设计要求

本案例将在QuartusII开发系统中用可编程逻辑器件,完成简易数字钟的EDA设计,具体要求为:

1数字钟功能:数字钟的时间为24小时一个周期;数字钟须显示时、分、秒;

2校时功能:可以分别对时、分、秒进行单独校时,使期调整到标准时间;

3扩展功能:整点报时系统。设计报整点报时电路,每当数字钟计时59分50秒时开始

报时,并发出鸣叫声,到达整点时鸣叫结束,鸣叫频率为100Hz。1.2.2 功能描述

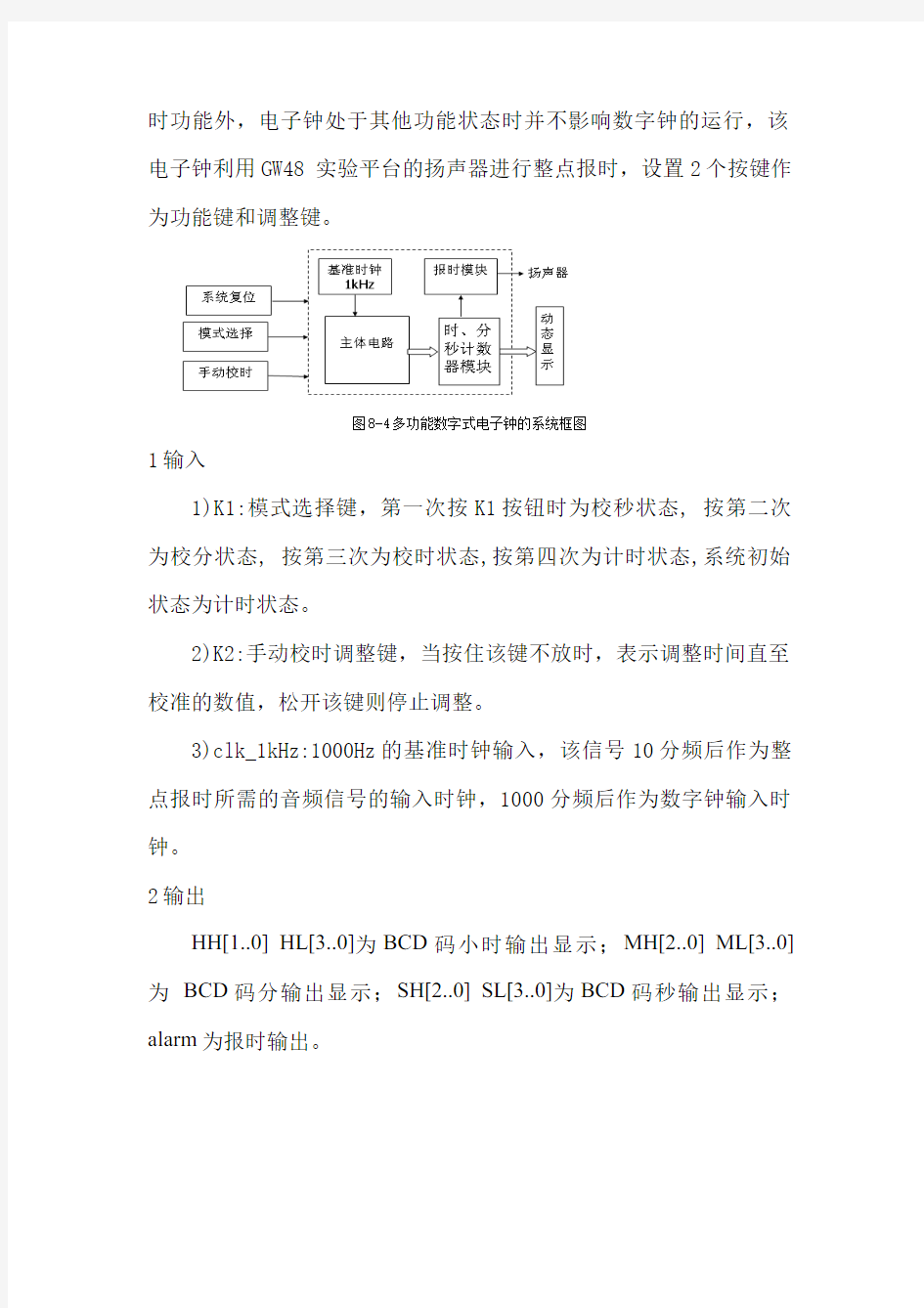

数字式电子钟实际上是一个对标准1Hz进行计数的计数电路,秒计数器满60后向分计数器进位, 分计数器满60后向时计数器进位, 时计数器按24翻1规律计数, 计数输出经译码器送LED显示器, 由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加上一个校时电路,该数字式电子钟除用于计时外,还能整点报时,如图8-4所示为多功能数字式电子钟的构成框图。除校

时功能外,电子钟处于其他功能状态时并不影响数字钟的运行,该电子钟利用GW48 实验平台的扬声器进行整点报时,设置2个按键作为功能键和调整键。

图8-4多功能数字式电子钟的系统框图

1输入

1)K1:模式选择键,第一次按K1按钮时为校秒状态, 按第二次为校分状态, 按第三次为校时状态,按第四次为计时状态,系统初始状态为计时状态。

2)K2:手动校时调整键,当按住该键不放时,表示调整时间直至校准的数值,松开该键则停止调整。

3)clk_1kHz:1000Hz的基准时钟输入,该信号10分频后作为整点报时所需的音频信号的输入时钟,1000分频后作为数字钟输入时钟。

2输出

HH[1..0] HL[3..0]为BCD码小时输出显示;MH[2..0] ML[3..0]为 BCD码分输出显示;SH[2..0] SL[3..0]为BCD码秒输出显示;alarm为报时输出。

1.2.3 数字钟的层次化设计方案

根据上述功能,可以把多功能数字式电子钟系统划分为三部分:时钟源(即标准秒钟的产生电路),时分秒计数器模块、数字钟模块、校时模块、数字秒表模块、闹钟和整点报模块。

1时钟源--晶体振荡器电路

1)原理说明

如精度要求不高可选用555构成的多谐振荡器,设其振荡频率为f0=1kHz,电路原理图如图8-5所示,而后通过分频器电路(1000分频)即可产生1Hz的方波信号供秒计数器进行计数,分频器电路可由3片十进制计数器级联而得,根据1.2.2节的描述,本设计案例选用图8-5的多谐振荡器电路的输出作为数字式电子钟的基准时钟输入,基准时钟输入一方面用于定时报时和整点报时所需的音频信号。另一方面该信号惊10分频后作为数字秒表的输入时钟,经1000分频后作为数字钟输入时钟。

2)时钟电路子模块counter1k的设计

时钟电路子模块可由3个十进制计数器74160级联而成,输出有10分频输出clk_10, 1000分频输出clk_1Hz,其原理图如图8-7所示,74LS160为同步可予置4bit十进制加法计数器,它具有同步载入,异步清零的功能。

图8-5 多谐振荡器电路 图8-6时钟电路子模块原理图在QuartusII中,利用原理图输入法完成源程序的输入、编译和仿真。时钟电路子模块的仿真输出波形文件如图8-7所示。在仿真结果正确无误后,可将以上设计的时钟电路子模块counter1k设置成可调用的元件counter1k.sym如图8-8所示。,以备高层设计中使用。

图8-7时钟电路仿真输出波形 图8-8时钟电路模块元件符号图

2时分秒计数器模块

1)原理说明

时分秒计数器模块由秒个位、十位计数器、分个位、十位计数及时个位、十位计数电路构成。其中:秒个位和秒十位计数器、分个位和分十位计数为六十进制计数器,而根据设计要求时个位和时十位构成的为二十四进制计数器。

因此时分秒计数器模块可划分为时计数、分计数和秒计数3个子模块,根据设计要求时计数子模块为一个二十四进制可预置BCD码计数器模块;分计数和秒计数子模块均为六十进制可预置BCD码计