简单频率计设计

物理与电子工程学院电子信息科学与技术专业 2011级董思林

指导教师何传红

摘要:随着数字电子技术的发展,频率测量成为一项越来越普遍的工作,因此测频计常受到人们的青睐。EDA技术是以大规模可编程逻辑器件为设计载体,以硬件语言为系统逻辑描述的主要方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件设计的电子系统到硬件系统的设计,最终形成集成电子系统或专用集成芯片的一门新技术,其设计的灵活性使得EDA技术.快速发展和广泛应用。

关键词:可编程逻辑器件;计数;分频;脉冲;扫描

1 引言

在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得非常重要。测量频率的方法有多种,其中电子计数器测量具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内量被测信号的脉冲个数;二是间接测频法,如周期测频法。直接测频法适用于高频信号的频率测量,间接测频法适用于低频号的频率测量。本设计采用直接测频法,以QuartusⅡ软件为设计平台,采用VHDL语言实现数字频率计的整体设计。伴随着集成电路(IC)技术的发展,电子设计自动化(EDA)逐渐成为重要的设计手段,已经广泛应用于模拟与数字电路系统等许多领域。电子设计自动化是一种实现电子系统或电子产品自动化设计的技术,它与电子技术,微电子技术的发展密切相关,它吸收了计算机科学领域的大多数最新研究成果,以高性能的计算机作为工作平台,促进了工程发展。EDA的一个重要特征就是使用硬件描述语言(HDL)来完成的设计文件,在电子

设计领域受到了广泛的接受。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,有硬件描述语言VHDL 完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作,最终形成集成电子系统或专业集成芯片的一门新技术。EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

2 设计原理

2.1 基本原理

数字频率计的主要功能是测量周期信号的频率。频率是单位时间(1秒)内信号发生周期变化的次数。在给定的1秒时间内对信号波形计数,并将所计数值显示出来,就能读取被测信号的频率。数字频率计首先必须获得相对稳定与准确的时间,然后通过计数器计算这一段时间间隔内的方波脉冲个数并显示出来。这就是数字频率计的基本原理。

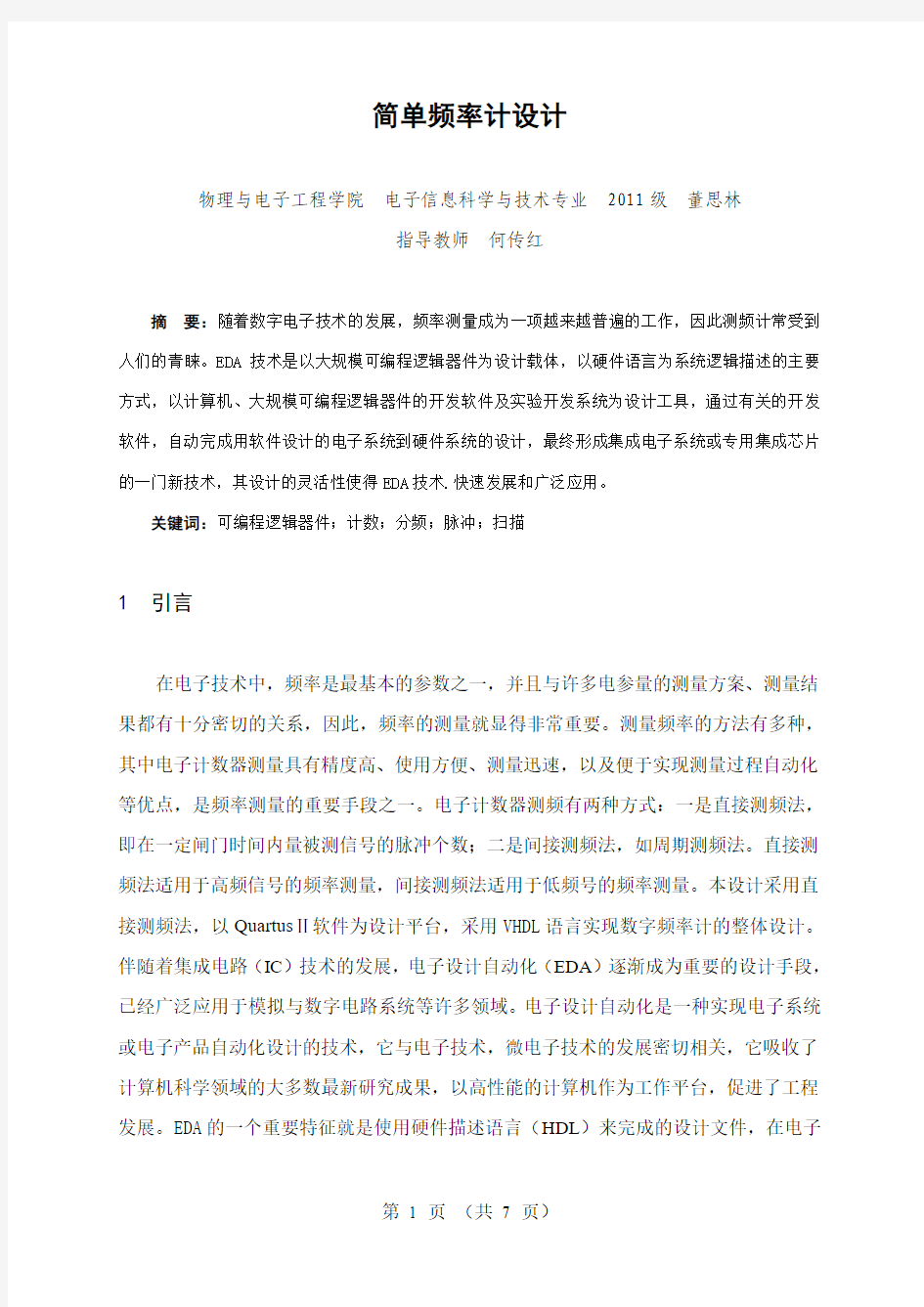

2.2 系统框图

通过测频控制信号发生器将由脉冲发生器产生的信号转换成所需要的控制信号clk1和en,待测信号计数器在en的控制下对待测信号进行测量并通过锁存与译码器在clk1的控制下按要求进行显示,大体结构如图1所示:

图2.2 系统框图

3 整体功能介绍

3.1 计数器设计

频率计的核心元件之一是含有时钟使能及进位扩展输出的十进制计数器。为此,这里用一个双十进制计数器器件74390和其他一些辅助元件来完成。电路框图如图3.1所示。

图3.1 含有时钟使能的2位十进制计数器

图中,74390连接成两个独立的十进制计数器,待测频率信号clk通过一个与门进入74390的计数器“1”端的时钟输入端1CLKA。与门的另一端由计数使能信号enb控制:当enb=1时允许计数;enb=0时禁止计数。计数器1的4位输出q[3] 、q[2] 、q[1] 和q[0] 并成总线表达方式,即q[3..0] ,由图左下角的OUTPUT输出端口向外输出计数值。同时由一个4输入与门和两个反相器构成进位信号,进位信号进入第二个计数器的时钟输入端2CLKA。第二个计数器的4位计数输出是q[7] 、q[6] 、q[5] 和q[4],总线输出信号是q[7..4].这两个计数器的总得进位信号,可由一个6输入与门和两个反相器产生,由cout输出。clr是计数器的清零信号。

对图3.1所示电路进行仿真,其波形图如下图3.1.1所示。

图3.1.1 仿真波形图

3.2 时序控制电路设计

欲使电路能自动测频,还需增加一个测频时序控制电路,如图3.2所示。该电路由三部分组成:4位二进制计数器7493、4-16译码器74154和两个由双与非门构成的RS 触发器。

图3.2 测频时序控制电路

3.3 时钟分频模块设计

由于设计中利用了一个50MHz的时钟信号输入,需要将其分频为合适的频率供给本设计中的各个模块。其程序代码如下:

module CLK_DIV(CLK,DIVCLK); //时钟偶数分频模块

input CLK; //定义输入时钟

output DIVCLK; //定义输出时钟

reg DIVCLK; //定义寄存器

reg [DIV_WIDTH-1:0]counter; //定义计数寄存器

parameter DIV_Num = 500000; //参数,定义分频参数

parameter DIV_WIDTH = 19; //参数,定义分频参数占用的位宽

always @ (posedge CLK) //分频过程

begin

if(counter == ((DIV_Num>>1)-1)) //注意分频数的计算公式

begin

counter <= 0;

DIVCLK <= ~DIVCLK;

end

else

counter <= counter + 1'b1;

end

endmodule

利用此代码生成元件命名为CLK_DIV,供上层文件调用。

3.4 数码管动态扫描显示驱动模块设计

本设计利用8位7段LED数码管,但只需要2位,需采用动态扫描驱动,为显示频率计的结果,需要在计数器和数码管之间放置一个驱动电路模块,由于数码管的现实字符段码过于冗长,这里只作简要说明。代码总共分为三部分:第一部分是相关参数的定义和段码字符的赋值;第二部分有两个case语句,第一个case语句实现对莫一位数码管的定义,,第二个case语句实现对数码管某一个段进行定义;第三部分则是对数码管具体要显示哪个字符进行初始化。

3.5 顶层电路设计

将图3.1所示电路包装入库,元件名取为counter8;将图3.2所示电路包装入库,元件名取为ft_ctrl。有了counter8和ft_ctrl,就可以做成自动测频和数据显示的实用频率计了,电路如图3.5所示。图中counter8为第1步生成的2位十进制计数器模块,ft_ctrl为第2步生成的时序控制模块,只含有两个输入信号:待测频率输入信号F_IN 和测频控制时钟clk。时钟分频模块CLK_DIV在此设计中被调用(例化)了3次,因为此模块采用了参数可配置的设计模式,所以调用同一个原型,通过改变参数就可以实现不同的特性,其中最上面一个时钟分频模块把50MHz分频到1024Hz(参数DIV_Num 为48828,所以输出频率为50MHz/48828≈1024Hz;参数DIV_WIDTH随DIV_Num而变;中间一个分频模块把1024Hz分频到8Hz作为时序控制模块的时钟,则计数使能信号CNT_EN的脉冲宽度即

为1秒,从而可使数码管直接显示F_IN的频率值了;下面一个分频模块把1024Hz分频到约51Hz作为被测频率F_IN输入到十进制计数器。

图3.5 顶层电路设计电路

4 设计总结

通过这次EDA课程设计,我对课堂上所学到的理论知识的理解加深了许多,自己动脑、动手设计的能力也得到了较大提高。在这次课程设计的过程中,我对 VHDL语言有了更深的认识。通过查阅相关资料和动手设计我发现我以前对 VHDL 语言的认识太过肤浅,认为VHDL语言只能用于设计小型的电路系统。但有了更深刻的认识之后我发现学好VHDL语言可以设计出大规模的、功能复杂的电路系统。以前之所以会有错误的认识是因为自己对VHDL语言的了解和掌握还不够。现在仔细想想,这次课程设计使得我对 VHDL 语言的理解与应用能力得到了较大的提升,也让我认识到只要深入学习,提升的空间永远是存在的。在设计的过程中我遇到了一些问题,通过查阅书本我发现了产生错误的原因并解决了问题完成了设计。经过反思我发现较大一部分错误是因为操作的不熟练造成的,这也让我明白了要保持设计的高效率必须经常练习。另一方面我

也发现了动手实践的重要性。动手实践是理论知识得以灵活运用的必要前提,也是今后走上工作岗位之后能够很好的完成设计工作的技术保证。只有遇到实际问题并根据自己对课堂上获得的专业知识的理解来解决才能真正的提高自己的能力。这也提醒我在平时的学习生活中不能一味埋头于课本知识,当今社会竞争越来越激烈,社会对人才的要求越来越全面,只有理论知识是远远不够的,必须靠实践作支撑。虽然此次设计完成了,但是我意识到,我对FPGA技术仅仅只是停留在入门的阶段,想要有更大的发展,更深入的研究,还需要更多的努力与实践。因此在学习之余我们应该积极参加各种与专业知识有关的实践活动和竞赛,巩固所学的理论知识,多注重培养实际动手能力和专业技术能力,这样才能在以后的工作岗位上有所作为。

参考文献:

[1] 潘松.黄继业.潘明.EDA技术实用教程-Verilog HDL版(第四版). 科学出版社

[2] 杨欣.电子设计从零开始(第2版),清华大学出版社

[3] 康华光.电子技术基础·模拟部分,高等教育出版社

[4] 康华光.电子技术基础·数字部分,高等教育出版社

[5] 顾斌,赵明忠,姜志鹏,马才根.数字电路EDA设计,西安电子科技大学出版社