带使能功能的八位双向总线驱动器74HC245 中文资料

这种八位总线收发器是为数据总线间进行异步两路通讯而设计的。采用控制功能可以尽量减少外部定时电路的要求。这种电路可以将数据从A 总线传送到B 总线,也可将数据从B 总线传送到 A 总线,具体传送方向要看方向控制(DIR)输入的逻辑电平而定。可以用使能输入来禁止这种电路,使总线之间能有效地隔离。

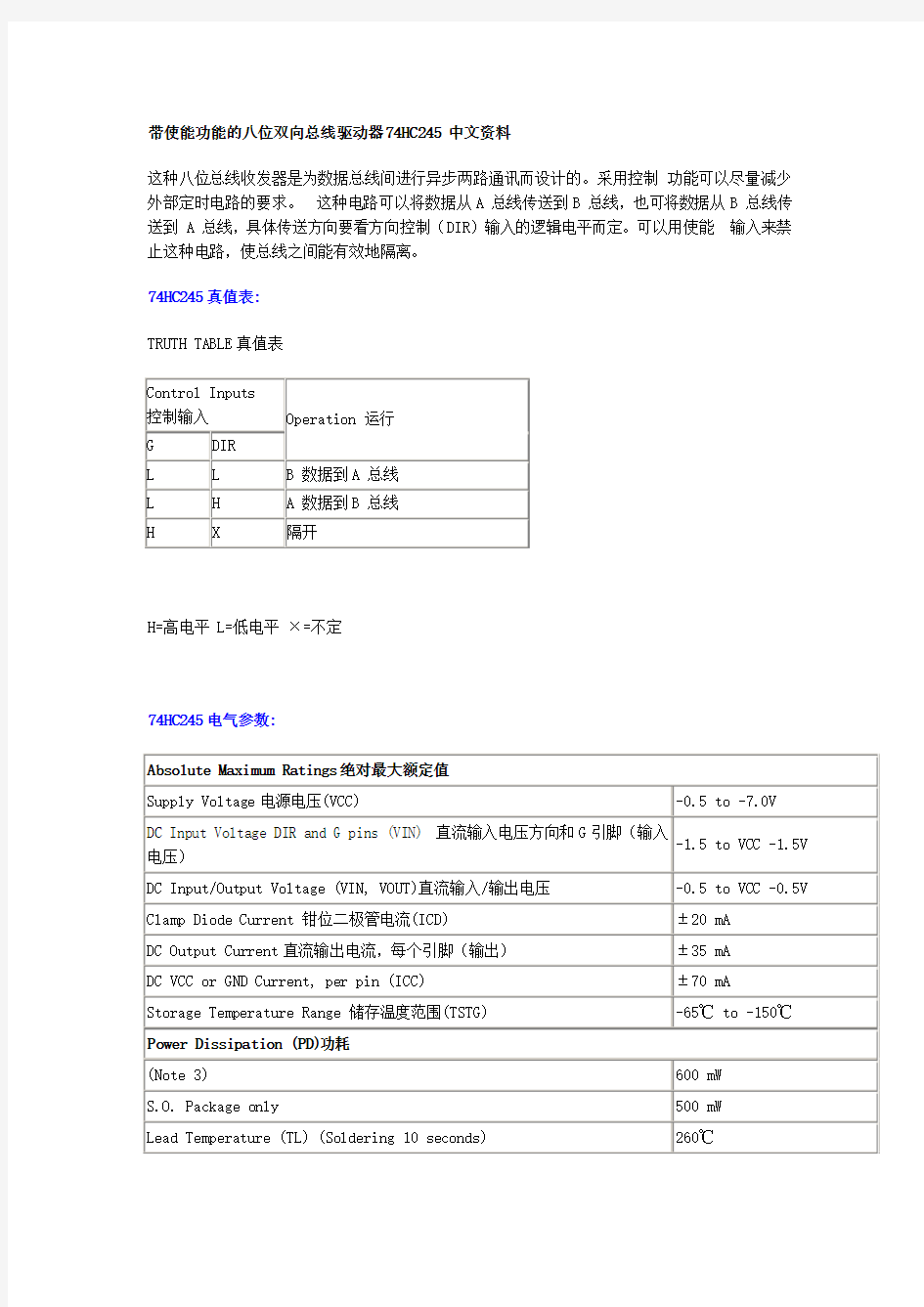

74HC245真值表:

TRUTH TABLE真值表

H=高电平 L=低电平×=不定

74HC245电气参数:

Note 1: Maximum Ratings are those values beyond which damage to the

device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground. Note 3: Power Dissipation temperature derating —plastic “N” package: 12 mW/℃ from 65℃ to 85℃.

DC SPECIFICATIONS直流电气规格

AC Electrical C haracteristics VCC=5V, TA=25℃, tr= tf =6ns交流电气特性

AC Electrical Characteristics VCC=2.0V to 6.0V, CL=50 pF, t r= tf =6ns 交流电气特性

总线型运动控制系统 传统运动控制系统中常以脉冲和模拟量作为控制信号,并将控制信号发送到电机驱动器中,再由电机驱动器驱动电机运行。得益于总线技术的发展,运动控制器厂家将总线技术应用运动控制器中。上位机通过总线将运动参数传送至电机驱动器,再由电机驱动器驱动电机运行。常见的总线技术有ProfiNet,ProfiBus,EhertCA T,RTEX,CCLINK等等。 总线型运动控制系统相对传统的运动控制系统有诸多优点。 1.接线简化。 在传统运动控制系统中,上位机与电机驱动器通过大量的数字量或者模拟量IO连接,以发送控制信号和接受反馈信号。这样会使接线数量增加,接线出错的几率比较大,线材成本上升,布线时间长而复杂。在总线型运动控制系统中,上位机的总线通讯接口可以通过线性拓扑方式连接多个支持总线通讯的电机驱动器。 2.拥有故障自诊断特性。 传统型运动控制系统中的上位机与电机控制器的信息交换是通过有限的IO进行的。能获取的信息是极有限。总线型运动控制系统拥有多种诊断功能。可以实时监控电机的运行状态,实时获取运行状态的信息。如果电机运行有异常,其相应的电机驱动器可通过总线向上位机发送异常信息。如线缆短路或短路、接头接触不良,电压异常等物理层诊断。 3.方便调试。 总线型运动控制系统,可以通过上位应用软件监控和调整各电机驱动器节点的参数。不用通过各电机驱动器的显示面板调整参数。 4.可靠性高 传统运动控制系统的中脉冲信号和模拟量信号,容易受到电磁干扰,可导致信号失真。总线型运动控制系统数字式通讯方式,无信号漂移问题。 总线型运动控制系统应用示例:3S总线控制系统通过EherCAT总线控制7轴运动。3S 总线系统可以控制多达128个轴,支持复杂插补运算;可控制多达10台不同类型的机器人;提供多达8192点数字量或模拟扩展功能;可接入视觉系统实现定位功能。

实验报告 一、实验设计方案 实验框图 实验原理 1、SW_BUS低电平有效,此时将K[7..0]的数据送到总线,通过L[7..0]双向数据端口 输出显示总线的数据,使用的芯片是74244八位单向三态缓冲器; 2、R3_BUS、R2_BUS、R1_BUS低电平有效,其功能是将数据要传入的寄存器打开, 若相应的lddr为1(高电平有效),将数据传入相应的寄存器; 3、总线数据传输时,控制信号中只能有一个有效,寄存器的端口送至数据总线,所以 每个BUS接口对应每个R寄存器的显示; 4、通过读写的双重作用,实现R1和R2的数据交换。 表达式 Reg3←Reg1;Reg1←Reg2;Reg2←Reg3 方法一:vhdl代码 library ieee; use ieee.std_logic_1164.all; entity exp_bus is port(clk:in std_logic; sw_bus,r1_bus,r2_bus,r3_bus:in std_logic; k:in std_logic_vector(7 downto 0); lddr:in std_logic_vector(3 downto 1); l:inout std_logic_vector(7 downto 0)); end exp_bus; architecture rtl of exp_bus is

signal r1,r2,r3,bus_Reg:std_logic_vector(7 downto 0); begin ldreg:process(clk,lddr,bus_reg) begin if clk'event and clk='1' then if lddr(1)='1'then r1<=bus_reg; elsif lddr(2)='1'then r2<=bus_reg; elsif lddr(3)='1'then r3<=bus_reg; end if; end if; end process; bus_reg<=k when (sw_bus='0'and r1_bus='1'and r2_bus='1'and r3_bus='1')else r1 when (sw_bus='1'and r1_bus='0'and r2_bus='1'and r3_bus='1')else r2 when (sw_bus='1'and r1_bus='1'and r2_bus='0'and r3_bus='1')else r3 when (sw_bus='1'and r1_bus='1'and r2_bus='1'and r3_bus='0')else (others=>'0'); l<=bus_reg when (sw_bus='0' or r1_bus='0' or r2_bus='0' or r3_bus='0')else (others=>'Z'); end rtl; 方法二:bdf实验原理图

CAN总线接口电路设计的关键问题及解决方法 摘要:文章总结了CAN接口电路设计中的几个关键问题,提出应采取合理设置光电隔离电路、隔离光电耦合器两侧的电源、设置必需的上拉电阻、总线阻抗匹配、增加抗干扰等措施, 提高了CAN总线接口电路的可靠性与安全性。 0引言 CAN总线是一种有效支持分布式控制和实时控制的串行通信网络,以其高性能和高可靠性在自动控制领域得到了广泛的应用。为提高系统的驱动能力,增大通信距离,实际应用 中多采用Philips公司的82C250作为CAN控制器与物理总线间的接口,即CAN收发器,以增强对总线的差动发送能力和对CAN控制器的差动接收能力。为进一步增强抗干扰能力,往往在CAN控制器与收发器之间设置光电隔离电路。典型的CAN总线接口电路原理如图1所示。 1接口电路设计中的关键问题 1.1光电隔离电路 光电隔离电路虽然能增强系统的抗干扰能力,但也会增加CAN总线有效回路信号的传输延迟时间,导致通信速率或距离减少。82C250等型号的CAN收发器本身具备瞬间抗干扰、降低射频干扰(RFI)以及实现热防护的能力,其具有的电流限制电路还提供了对总线的进一步保护功能。因此,如果现场传输距离近、电磁干扰小,可以不采用光电隔离,以使系统达到最大的通信速率或距离,并且可以简化接口电路。如果现场环境需要光电隔离,应选用高速光电隔离器件,以减少CAN总线有效回路信号的传输延迟时间,如高速光电耦合器6N137,传输延迟时间短,典型值仅为48ns,已接近TTL电路传输延迟时间的水平。 1.2电源隔离 光电隔离器件两侧所用电源Vdd与Vcc必须完全隔离,否则,光电隔离将失去应有的作用。电源的隔离可通过小功率DC/DC电源隔离模块实现,如外形尺寸为DIP-14标准脚位的5V 双路隔离输出的小功率DC/DC模块。 1.3上拉电阻 图1中的CAN收发器82C250的发送数据输入端TXD与光电耦合器6N137的输出端OUT 相连,注意TXD必须同时接上拉电阻R3。一方面,R3保证6N137中的光敏三极管导通时输出低电平,截止时输出高电平;另一方面,这也是CAN总线的要求。具体而言,82C250的TXD端的状态决定着高、低电平CAN电压输入/输出端CANH、CANL的状态(见表1)。CAN 总线规定,总线在空闲期间应呈隐性,即CAN网络中节点的缺省状态是隐性,这要求82C25O 的TXD端的缺省状态为逻辑1(高电平)。为此,必须通过R3确保在不发送数据或出现异常情况时,TXD端的状态为逻辑1(高电平)。 表1TXD与CANH、CANL的关系表 TXD状态CANH电平(V)CANL电平(V)CAN总线状态 1 2.5 2.5隐性(逻辑1)

PCI总线驱动的机制 1.总线子系统初始化 系统初始化时会调用 ■void __init driver_init(void) { 。。。。。。 buses_init(); 。。。。。。 } ■ ★I nclude/linux/kobject.h #define decl_subsys(_name,_type,_uevent_ops) \ struct subsystem _name##_subsys = { \ .kset = { \ .kobj = { .name = __stringify(_name) }, \ .ktype = _type, \ .uevent_ops =_uevent_ops, \ } \ } ★ Drivers/base/bus.c static struct kobj_type ktype_bus = { .sysfs_ops = &bus_sysfs_ops, }; ★ static decl_subsys(bus, &ktype_bus, NULL); bus_subsys={ .ket = { .kobj = { .name = “bus”, .ktype = &ktype_bus, .uevent_ops = NULL, } } ★int __init buses_init(void) { return subsystem_register(&bus_subsys); }

在buses_init中调用subsystem_register时,bus_subsys作为sysfs root 目录下的项被建立(因为其kset.kobj.parent的值为NULL) ■pci总线初始化 ★struct bus_type pci_bus_type = { .name = "pci", .match = pci_bus_match, .uevent = pci_uevent, .probe = pci_device_probe, .remove = pci_device_remove, .suspend = pci_device_suspend, .suspend_late = pci_device_suspend_late, .resume_early = pci_device_resume_early, .resume = pci_device_resume, .shutdown = pci_device_shutdown, .dev_attrs = pci_dev_attrs, }; ★struct device_attribute pci_dev_attrs[] = { __ATTR_RO(resource), __ATTR_RO(vendor), __ATTR_RO(device), __ATTR_RO(subsystem_vendor), __ATTR_RO(subsystem_device), __ATTR_RO(class), __ATTR_RO(irq), __ATTR_RO(local_cpus), __ATTR_RO(modalias), #ifdef CONFIG_NUMA __ATTR_RO(numa_node), #endif __ATTR(enable, 0600, is_enabled_show, is_enabled_store), __ATTR(broken_parity_status,(S_IRUGO|S_IWUSR), broken_parity_status_show,broken_parity_status_store), __ATTR(msi_bus, 0644, msi_bus_show, msi_bus_store), __ATTR_NULL, }; ★static int __init pci_driver_init(void) { return bus_register(&pci_bus_type); } postcore_initcall(pci_driver_init); 通过postcore_initcall声明,使pci_driver_init函数被链接到.initcall.init段。这个段的函数在初始化时由static void __init do_initcalls(void)函数调用。最终系统在初始化线程static int __init

摘要 随着汽车产业的不断发展,汽车的功能也越发丰富实用,但这些功能大多数是通过不同的电子器件实现的,功能的丰富意味着车载电子设备的增多,电子设备的增多也意味着需要的连接线束的增多,传统的点对点连接已然不再使用于现代汽车,现代汽车急需一项能解决电子器件连接同时能减少连接线束的技术。CAN 总线技术应运而生,CAN总线技术通过共享车载电子元件的数据,成功减少了车内线束数量,并且其强大的数据传输能力提高了汽车的整体水平,使汽车工业迈进了一个新台阶。 数据流一词自CAN总线技术诞生以来便一直活跃在人们的视野中,可见数据流在汽车工业中的重要地位,汽车的创新研发、维修维护、改装等都需要以汽车数据流作为重要依据。现代汽车数据流多数是使用汽车诊断仪通过汽车的OBD 诊断接口进行读取的,但是汽车诊断仪造价不菲,且体积较大不便携带。 本论文基于CAN总线技术的成熟发展及汽车数据流的读取问题进行讨论,设计一款低成本、便于使用携带的汽车发动机数据流显示系统。选用51单片机作为系统的核心,与汽车CAN总线建立通信,以LCD1602作为显示载体,将采集到的数据流进行实时显示。该系统以汽车内部电源作为系统供电电源,即插即用,体积小巧便于携带使用。 关键词:汽车;CAN总线;发动机数据流;LCD;设计 ABSTRACT With the continuous development of the automobile industry, the function of the car is more and more practical, but most of these functions are realized through different electronic devices. The rich function means the increase of the vehicle electronic equipment. The increase of the electronic equipment also means the increase of the required connection wire harness, the traditional point to point connection is no longer For modern vehicles, modern cars need a technology that can solve the connection of electronic devices and reduce the wiring harness at the same time. CAN bus technology emerges as the times require. By sharing the data of the vehicle electronic components, the CAN bus technology has successfully reduced the number of the inner line of the car, and its powerful data transmission capacity has improved the overall level of the car and made the automobile industry into a new step.

http ://https://www.doczj.com/doc/946800427.html, 一种两线双向高速串行音频数据传输总线控制器的实现方法 瞿军武, 薛骏,施彦(无锡中感微电子股份有限公司,江苏无锡,214135) 摘要:本文提出了一种两线双向高速串行音频数据传输总线控制器在蓝牙耳机硬件系统中的应用, 可以实现芯片间高速传输数据,实现同步发送和接收音频数据以及命令字。同时, 通过自定义数据格式,优化了数据格式,并降低了数据发送和接收的复杂度。考虑到PAD 的承受能力,目前传输速率最大可 以达到18Mb/s 。仅使用两线完成了数据的传输, 从而大大减少了芯片IO 的使用。关键字:蓝牙耳机;两线双向;高速;串行总线控制器;IO ;FPGA A Realization Method of Two-wire Bidirectional High Speed Serial Audio Data Transmission Bus Controller QU Jun-wu,XUE Jun ,SHI Yan (Zgmicro co,.ltd,Wuxi 214135,China ) Abstract:This paper proposes a two-wire bidirectional high-speed serial audio data transmission bus controller applied in Bluetooth headset hardware system,which can realize high-speed data transmission between chips,synchronous transmission and reception of audio data and command words.By the self-defined data format,the data format is optimized and the complexity of data sending and receiving is reduced.Considering the bearing capacity of PAD,the maximum transmission rate can reach 18Mb/s at present.Only two lines are used to complete data transmission,which greatly reduces the use of IO on chip. Key words:Bluetooth headset;two-wire bidirectional;high-speed;serial bus controller;IO;FPGA 55

1 引言 SPI ( Serial Peripheral Interface--串行外设接口) 总线是一种同步串行外设接口, 它可以使MCU与各种外围设备以串行方式进行通信以交换信息. 由于SPI总线一共只需3~4位数据线和控制线即可实现与具有SPI总线接口功能的各种I/O器件进行接口, 而扩展并行总线则需要8根数据线、8~16位地址线、2~3位控制线, 因此, 采用SP I总线接口可以简化电路设计, 节省很多常规电路中的接口器件和I/O口线, 提高设计的可靠性[1]。嵌入式系统中用软件GPIO (General Programmable Input/Output—通用可编程输入/输出口) 模拟总线接口目前是十分常见的一种节约硬件资源的方法,采用GPIO模拟SPI总线当前也有许多种方法,但多以GPIO口模拟SPI主机而另一方则为在硬件上具有GPIO功能的设备,实现其相互通信的情况。而主、从机均为模拟的情况则很少见到。本文给出的是主机和从机通信均为在GPIO或不具有SPI硬件功能的设备间的通信,即相互通信双方均要采用GPIO口模拟时序来实现SPI规范,实现相互通信。本文以两个89C52处理器GPIO各自来模拟、SPI主机和SPI从机为例,详细介绍了SPI主从机设计和实现方法,代码采用ANSI 收稿日期:2007-05-18 嵌入式系统中GPIO模拟SPI总线主/从双向 通信的设计与实现 孙 松 (黄石理工学院电气与电子信息工程学院,湖北 黄石 435003) 摘 要:本文以两个89C52处理器GPIO各自来模拟SPI主机和SPI从机为例,详细介绍了SPI主/从机设计和实现方法,代码采 用ANSI C编写具有很好的移植性。 关键字:嵌入式系统; 模拟SPI总线; 89C52 中图分类号:TP336 文献标识码:B 文章编号:1003-7241(2007)10-0038-03 The Design of GPIO for SPI Host/Slave Communication SUN Song (School of Electric and Electronic Information Engineering ,Huangshi Institute of Technology, Huangshi 435003 China) Abstract: This paper introduces the method of implementation of GPIO for SPI-bus-based host/slave communication by two 89C52 MCU. The code is ANSI C. Keyword: embedded system; SPI-bus analogue; 89C52 C编写具有很好的移植性。 2 SPI总线标准简介 SPI接口的全称是"Serial Peripheral Interface",意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。SPI接口是以主从方式工作的,这种模式通常有一个主器件和一个或多个从器件,其接口包括以下四种信号:(1)MOSI-主器件数据输出,从器件数据输入(2)MISO-主器件数据输入,从器件数据输出(3)SCLK-时钟信号,由主器件产生(4)/SS-从器件使能信号,由主器件控制。SPI点对点通信如图1所示。 图1 SPI点对点通信 38 | T echniques of Automation & Applications

linux内核学习---总线,设备,驱动 Linux 设备模型中三个很重要的概念就是总线,设备,驱动.即 bus,device,driver,而实际上内核中也定义了这么一些数据结构,他们是 struct bus_type,struct device,struct device_driver,这三个重要的数据结构都来自一个地方,include/linux/device.h.我们知道总线有很多种,pci总线,scsi 总线,usb 总线,所以我们会看到Linux 内核代码中出现pci_bus_type,scsi_bus_type,usb_bus_type,他们都是 struct bus_type 类型的变量.而struct bus_type 结构中两个非常重要的成员就是 struct kset drivers 和 struct kset devices。kset 和另一个叫做 kobject 正是 Linux Kernel 2.6 中设备模型的基本元素。 这里我们只需要知道,drivers 和 devices 的存在,让struct bus_type 与两个链表联系了起来,一个是devices 的链表,一个是 drivers 的链表,也就是说,知道一条总线所对应的数据结构,就可以找到这条总线所关联的设备有哪些,又有哪些支持这类设备的驱动程序. 而要实现这些,就要求每次出现一个设备就要向总线汇报,或者说注册,每次出现一个驱动,也要向总线汇报,或者说注册.比如系统初始化的时候,会扫描连接了哪些设备,并为每一个设备建立起一个 struct device 的变量,每一次有一个驱动程序,就要准备一个 struct device_driver 结构的变量.把这些变量统统加入相应的链表,device 插入 devices 链表,driver 插入 drivers 链表. 这样通过总线就能找到每一个设备,每一个驱动。 struct bus_type 中为 devices 和 drivers 准备了两个链表,而代表 device 的结构体 struct device 中又有两个成员,struct bus_type *bus 和 struct device_driver *driver。同样,代表driver 的结构体 struct device_driver 同样有两个成员,struct bus_type *bus 和 struct list_head devices。struct device 和struct device_driver 的定义和 struct bus_type 一样,在 include/linux/device.h 中。凭一种男人的直觉,可以知晓,struct device 中的 bus 记录的是这个设备连在哪条总线上,driver 记录的是这个设备用的是哪个驱动,反过来,struct device_driver 中的 bus 代表的也是这个驱动属于哪条总线,devices 记录的是这个驱动支持的那些设备,没错,是 devices(复数),而不是 device(单数),因为一个驱动程序可以支持一个或多个设备,反过来一个设备则只会绑定给一个驱动程序。 上面是理论知识,下面我们具体以展讯平台的I2C设备重力加速度传感器MC3XXX驱动为例进行实例分析: 1.首先在Board-sp7715ga.c文件中通过sc8810_add_i2c_devices函数(其实是i2c_register_board_info函数)将指定的I2C设备( MC3XXX_ACC_I2C_NAME, MC3XXX_ACC_I2C_ADDR---包括设备名和设备地址)申请一个I2C struct device 结构,并且挂入I2C总线中的devices 链表中来。 注意:该device挂入devices链表的操作会先于I2C设备驱动加载的操作被执行。i2c_register_board_info函数对此进行了特别说明:

基于HI-8582的ARINC429总线设计 摘要:简要介绍了ARINC429总线和HI-8582芯片的特点,给出了基于HI-8582的ARINC429总线设计思路和方法。最后结合工程实际给出了单片机AT89C52的数据收、发程序实例。关键词:HI-8582,ARINC429接收,ARINC429发送,A T89C52 1 ARINC429总线及协议芯片HI-8582简介 1.1 ARINC429航空总线简介 ARINC429总线是美国航空无线电公司制定的民用航空数字总线传输标准,它规定了使用该总线的航空电子设备的信息流向和ARINC429基本数据字的格式。ARINC429为单向传输总线,信息只能从通信设备的发送口输出,经传输总线传至与它相连的需要该信息的其他设备的接收口。在需要两个通信设备间双向传输时,则在每个方向各用一根独立的传输总线。ARINC429通信采用带有奇数奇偶校验的32位信息字,信息字通过标牌识别,最多具备256个标牌。采用双极性归零制的三态码调制方式,即调制信号由“高”、“零”和“低”状态组成的三电平状态调制。 1.2 HI-8582简介 目前在机载设备中使用的ARINC429总线协议芯片较多,相比之下,HOLT INTEGRATED CIRCUITS公司生产的HI-8582是一款性能价格比较高的ARINC429协议芯片。该器件的主要功能如下: ●符合ARINC429总线协议; ●具有独立的双向接收和发送接口; ●无需驱动,可直接上ARINC429总线; ●标牌可程序化识别; ●串行数据速率可设位为100kbps或12.5kbps; ●对接收的数据可进行奇偶状态校验;并可对发送数据奇偶状态进行设置; ●可自动产生字与字之间的间隔; ●52脚PQFP封装,节省印制板空间。 2 AT89C52与HI-8582的接口设计 2.1 接口原理介绍 由于AT89C52是8位处理器,而HI-8582是16位接口芯片,在接口设计中利用一片CPLD 实现接口,设计中选用了ALTERA公司的EPM7128作为接口电路。电路框图见图1。 图1中,D1为单片机AT89C52,其中P0端口用于数据的的交换,P2端口用于控制,利用两个外中断INT0、INT1接收收到的429信号,单片机的复位信号是硬件看门狗产生的,图1中没有画出,复位信号RST作为CPLD的输入信号,单片机的时钟选用12MHz,同时12MHz 作为CPLD的时钟源。D2为CPLD器件EPM7128,主要完成8位总线和16位总线的转换、数据交换、编译码、产生HI-8582的时钟和复位信号。D3为ARINC429接口电路HI-8582,BD00~BD11为双向数据总线与EPM7128相接,其余均为离散量。

VHDL中双向端口设计小结【转】 FPGA / VHDL 2009-08-03 16:00 阅读53 评论0 字号:大中小 在工程应用中,双向电路是设计者不得不面对的问题.在实际应用中,数据总线往往是双向的.如何正确处理数据总线是进行时序逻辑电路设计的基础.在程序设计过程中,关键技术在于:实体部分必须对端口属性进行申明,端口属性必须为inout类型,在构造体需要对输出信号进行有条件的高阻控制.在双向电路的处理问题上,常用的处理方式有两种,在介绍双向电路的处理方式之前,先看看双向电路的 基本格式: ENTITY bidir_pin IS ( bidir : INOUT std_logic; oe, clk, from_core : IN std_logic; to_core : OUT std_logic; …… END bidir_pin; ARCHITECTURE behavior OF bidir_pin IS BEGIN bidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”; to_core <= bidir; END behavior; 该程序揭示了双向电路的处理技巧,首先在实体部分bidir属于双向信号,在端口定义时,端口属性为inout类型,即把bidir信号作为输入三态输出.语句“bidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”;”表示bidi r信号三态输出,语句”to_core <= bidir;”把bidir信号作为输入信号. 由此可见,双向电路在程序设计中,didir输入当着普通的in类型,而在输出时,需要加一定的控制条件,三态输出.问题的关键在于:如何确定这个条 件? 1)双向信号作一个信号的输入,作另一信号的输出 ENTITY bidir IS PORT( bidir : INOUT STD_LOGIC_VECTOR (7 DOWNTO 0); oe, clk : IN STD_LOGIC; from_core : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

在总结的过程中参考了下面一些资料,在此表示感谢: [1]