实验二(1)三态门电路设计

班级姓名学号

一、实验目的

熟悉Quartusll仿真软件的基本操作,并用VHDL/Verilog语言设计一个三态门。

二、实验内容

1、熟悉Quartusll软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)

2、用VHDL语言设计一个三态门,最终在FPGA芯片上编程指令译码器,并验证逻辑实现。

三、实验方法

1、实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4 的FPGA试验箱。

2、实验步骤:

1、新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name 为stm)-【next】(设置文件名zlym.vhd —在【add])-[properties 】

(type=AHDL)-【next] (family=FLEX10K name=EPF10K10TI144-4)-【next]-【finish](2).新建:【file]-【new](第二个AHDL File)-【OK]

2、写好源代码,保存文件(stm.vhd )。

3、编译与调试。确定源代码文件为当前工程文件,点击【process in g] - [ start compilation ] 进行文件编译。编译结果有一个警告,文件编译成功。

4、波形仿真及验证。新建一个vector waveform file。按照程序所述插入EN,A以及dataout)四个节点(EN,A为输入节点,dataout为输出节点)。(操作为:右击-【in sert ]-【in sert node or bus]-【node finder ] (pins=all; [list])-【>>]-【ok]-【ok])。任意设置EN,A的输入波形…点击保存按钮保存。然后【start simulation ],出name dataout的输出图。

5、时序仿真。暂时不知道什么是时序仿真

6、F PGA芯片编程及验证

选择pins,连接计算机到实验箱,操作。

四、实验过程

3、编译过程

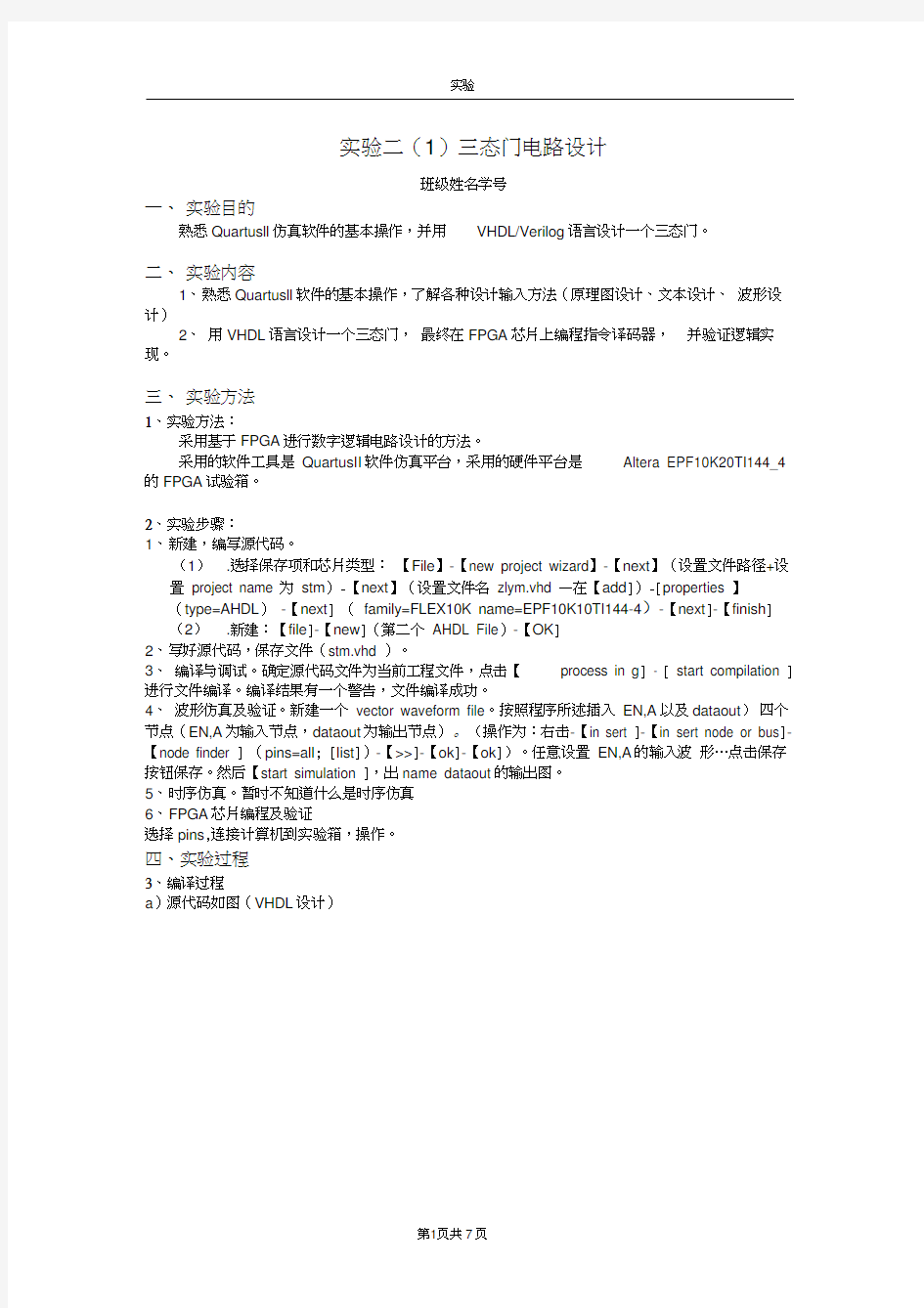

a)源代码如图(VHDL设计)

Li&rary XEtE ;

USE IEEE -3TD_L?GIC_11€4 *ALL;

une IEEE . STD^LCaiC^UUSZCWED . JLLL^ B an 匸 i t y s tm i. s

S ?art <

EN r A :m srd logxc;

daDaout : Out st-d 1 o Q J _C

b ) 编译、调试过程

确定源代码文件为当前工程文件,点击【 process in g 】-【start compilation 】进行文件编译。

编译结果有四个警告,文件编译成功。 c ) 结果分析及结论 结果正确,

4、波形仿真

a ) 波形仿真过程(详见实验步骤)

b ) 波形仿真波形图

c )结果分析及结论 0-10ns : EN=0 A=0 10-20 ns: EN=0 A=1 20-30ns: EN=1 A=1 30-40ns: EN=1 A=0 通

著 slm.vhd

| TJ^ sthn.Yrjf

{}

----- tT>

B g

); 亡nd.

s tm;

1C S aurc-tLX tectnre JbFnr o r a i

S BEGIN

匹

S PROCE SS £EET P A>

q. 3

BEG-TN

s

IF (EN^?工?)THEN

15

dataout<=A ; 16 s

ELSE

17 dataout< =f Z'; 18 END IF;

19

m PROCESS ; 20 CND

ijiiv;

dataout=z dataout=z dataout=1 dataout=0

s

G

7

过波形图可以得出实验结果正确

5、时序仿真

a)时序仿真过程

做好上述步骤后,编译【classic timing analysis】-在compilation report 中选择【timing analysis 】-【tpd】(引脚到引脚的延时)

b)时序仿真图

b)结果分析及结论

A引脚到dataout引脚的实际p2p时间为6.568ns,二EN引脚到dataout引脚的实际p2p时间为

6,542ns。A比EN慢0.026ns,可由于结果是由时间长的那个决定,故整体为 6.568ns。tpd (引脚到引脚的延时)

6、Programming 芯片编程

a)芯片编程过程

写好代码和得到波形图后,【Assig nme nts】-【Pins]-连接端口。设置好两入一出(如In put:

pin_87 In put: pin_88, Output: pin_06 ),从计算机连接数据线到EPF10K20TI144_4 的FPGA

0代表不灯亮,1代表灯亮。

c)结果分析与结论

由逻辑关系得的上述结果。结果正确。

五、实验结论(实验总结与实验心得)

第二次实验使用这个软件明显熟练了,而且对时序仿真与波形仿真有了初步认识。

实验二(2)2选1多路复用器

班级计科1504姓名张洁学号201508010402

一、实验目的

熟悉Quartusll仿真软件的基本操作,并用VHDL/Verilog语言设计一个三态门。

二、实验内容

1、熟悉Quartusll软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)

2、用VHDL语言设计一个2选1多路复用器,最终在FPGA芯片上编程指令译码器,并验证逻辑实现。

三、实验方法

7、实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4 的FPGA试验箱。

8实验步骤:

2、新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径+设置project name 为exy)-【next】(设置文件名zlym.vhd —在【add])-[properties 】

(type=AHDL)-【next] (family=FLEX10K name=EPF10K10TI144-4)-【next]-【finish](2).新建:【file]-【new](第二个AHDL File)-【OK]

2、写好源代码,保存文件(exy.vhd)。

3、编译与调试。确定源代码文件为当前工程文件,点击【process in g] - [ start compilation ] 进行文件编译。编译结果有一个警告,文件编译成功。

4、波形仿真及验证。新建一个vector waveform file。按照程序所述插入EN,A[7].B[7]以及dataout[7])四个节点(EN,A[7],B[7]为输入节点,dataout为输出节点)。(操作为:右击-【insert ] -【insert node or bus ]-【node finder ] (pins=all; [ list])-【>>]-【ok]-【ok])。任意设置EN,A 的输入波形??点击保存按钮保存。然后【start simulation ],出name dataout的输出图。

5、时序仿真。暂时不知道什么是时序仿真

6、FPGA芯片编程及验证

选择pins,连接计算机到实验箱,操作。

四、实验过程

9、编译过程

a)源代码如图(VHDL设计)

2use IEEE ?STD LOGTU l l昏今?仏匚;

3use IEEE ?5TD【I?0(5Tc[uMSTGNED, ALL:

T H entity exy is

■5part

仍B ( EN:in std loffiG;

A: in a t d_log'ic v&Gt&r [7 downto Q>;

S fi : in acil_logiG_v&ct.ar (7 down DO O>;

勺dataout: QU.C std 丄口gid veGLar 7 downto

10); 1 —

11end exy;

12S architectare bhv af exy is

13H BEGIN

IT SFROCL55 (A, S.LIf)

15 BEGIN

1€ H IFtEN-'l^ THEN

17 d 且.匸aou.t<=A;

16 S ELSE

19dataout<=&;

20END IF:

21END PROCESS;

b)编译、调试过程

确定源代码文件为当前工程文件,点击【编

译结果有四个警告,文件编译成功。

c)结果分析及结论

结果正确,

10、波形仿真

a)波形仿真过程(详见实验步骤)

b)波形仿真波形图

i^.vh

d

Library IEEE;

Master Time Bar: s?4 Pointei:22 7 ns Inteivat7.75 ns Start:0 ps

J ps

10JD ns T

20.0 its30. O ns

~ i

40.

14.95 ns

J

(J创X loT

14.95

processing】-【start compilation 】进行文件编译。

c) 结果分析及结论 0-10ns : EN=O 10-20 ns: EN=0 20-30ns: EN=1 30-40ns: EN=1

通过波形图可以得出实验结果正确 10、 时序仿真

c )时序仿真过程

做好上述步骤后, 编译【classic timing analysis 】-在 compilation report 中选择【timing analysis 】 -【tpd 】(引脚到引脚的延时) b )时序仿真图

d )结果分析及结论

EN 引脚到dataout 引脚的实际p2p 时间比A,B 引脚到dataout 引脚的实际p2p 时间长。由于 结果是由时间长的那个决定,故整体为 9.726ns 。 tpd (引脚到引脚的延时) 11、 Programming 芯片编程 b )芯片编程过程

dataout=B dataout=B dataout=A dataout=A

写好代码和得到波形图后,【Assig nme nts】-【Pins]-连接端口。设置好三入一出(如In put: pin_87 In put: pin_88,l nput: pin_89 Output: pin_06 ),从计算机连接数据线到EPF10K20TI144_4 的FPGA试验箱。连接电源,开始按开关。找到pin 87,88,06的位置,改变87,88,89的开关

状态。看06灯的亮熄情况并记录。

b)编程芯片验证结果

0代表不灯亮,1代表灯亮。

c)结果分析与结论由逻辑关系得的上述结果。结果正确。

五、实验结论(实验总结与实验心得)

这一次的实验题目相比较来说比较简单易懂,而且在前面实验做铺垫的情况下,做起来比较顺手。感觉自己有了一点进步。