实验五:译码器和数据选择器的使用

1.实验目的

1) 熟悉数据分配器和译码器的工作原理与逻辑功能。

2) 掌握数据分配器和译码器的使用

2.理论准备

1) 具有译码功能的逻辑电路称为译码器。译码即编码的逆过程,将具有特定意义的二进

制码进行辨别,并转换成控制信号。按用途来分,译码器大体上有以下3类:

(1)变量译码器;

(2)码制变换译码器;

(3)显示译码器。

2) 数据选择器又称多路开关,它是以“与或非”门或以“与或”门为主体的组合电路。

它在选择控制信号的作用下,能从多个输入数据中选择某一个数据作为输出。常见的数据选择器有以下5种:

(4)4位2通道选1数据选择器;

(5)4通道选1数据选择器;

(6)无“使能”端双4通道选1数据选择器;

(7)具有“使能”端的互补输出地单8选1数据选择器。

3.实验内容

1) 3线-8线译码器(74138)的功能测试

2) 用3-8译码器设计一位全减器

3) 用双4选1数据选择器(74153)设计一位全减器

提示说明:

①用译码器设计组合逻辑电路设计原理;

②利用译码器产生输入变量的所有最小项,再利用输出端附加门实现最小项之和;

③双4选1数据选择器:在控制信号的作用下,从多通道数据输入端中选择某一通道的数据输出Y=[D0(A1’A0’)+D1(A1’A0)+D2(A1A0’)+D3(A1A0)].S。

4.设计过程

1)用3-8译码器设计一位全减器。

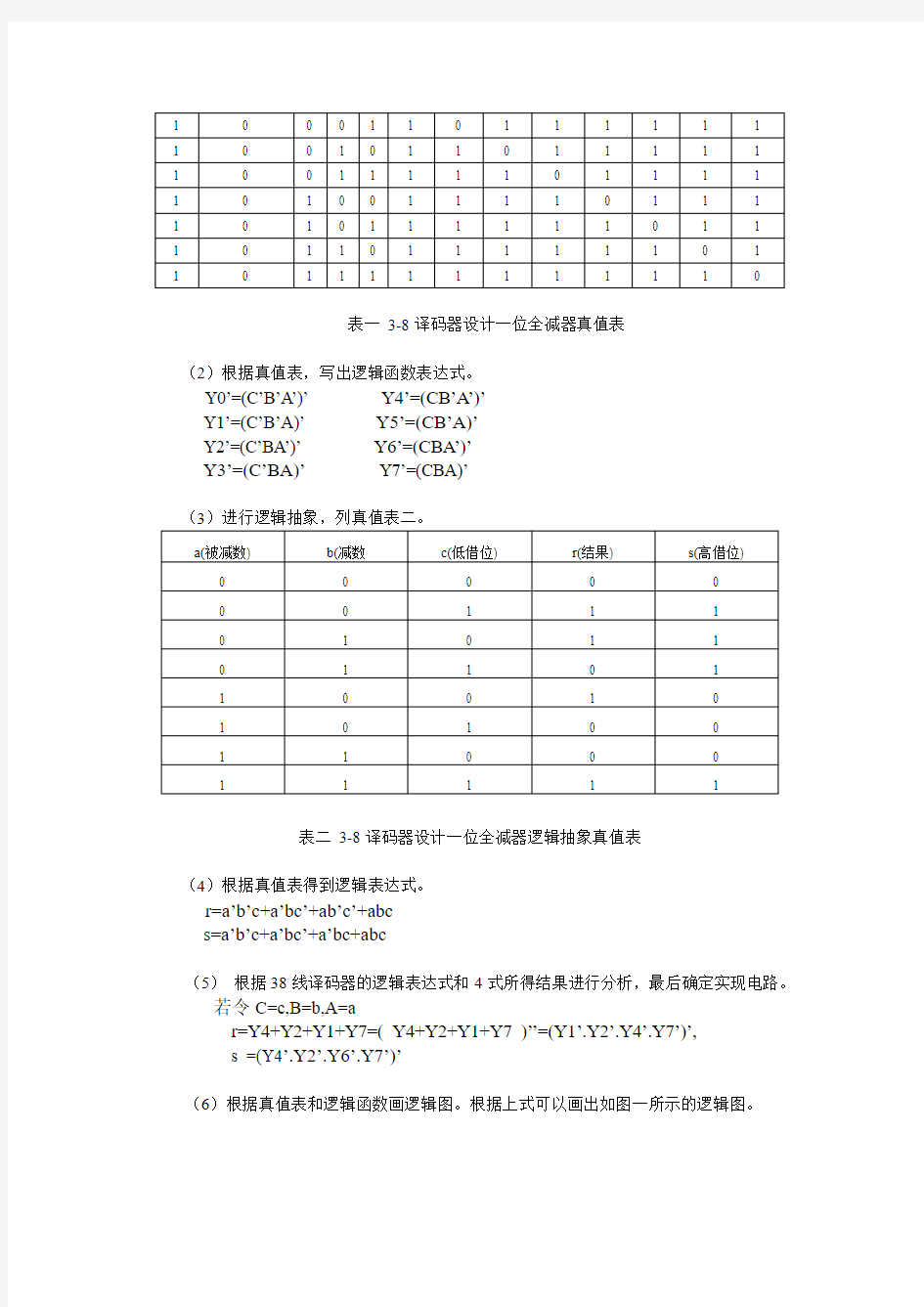

(1)分析设计要求,列出真值表。如表一。

输入输出

G1 G2A+G2B C B A Y

0Y

Y1 Y2 Y3 Y4 Y5 Y6

0 x x x x 1 1 1 1 1 1 1 1 x 1 x x x 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1

1 0 0 0 1 1 0 1 1 1 1 1 1

1 0 0 1 0 1 1 0 1 1 1 1 1

1 0 0 1 1 1 1 1 0 1 1 1 1

1 0 1 0 0 1 1 1 1 0 1 1 1

1 0 1 0 1 1 1 1 1 1 0 1 1

1 0 1 1 0 1 1 1 1 1 1 0 1

1 0 1 1 1 1 1 1 1 1 1 1 0

表一3-8译码器设计一位全减器真值表

(2)根据真值表,写出逻辑函数表达式。

Y0’=(C’B’A’)’ Y4’=(CB’A’)’

Y1’=(C’B’A)’ Y5’=(CB’A)’

Y2’=(C’BA’)’ Y6’=(CBA’)’

Y3’=(C’BA)’Y7’=(CBA)’

(3)进行逻辑抽象,列真值表二。

a(被减数) b(减数c(低借位) r(结果) s(高借位)

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

表二3-8译码器设计一位全减器逻辑抽象真值表

(4)根据真值表得到逻辑表达式。

r=a’b’c+a’bc’+ab’c’+abc

s=a’b’c+a’bc’+a’bc+abc

(5)根据38线译码器的逻辑表达式和4式所得结果进行分析,最后确定实现电路。

若令C=c,B=b,A=a

r=Y4+Y2+Y1+Y7=( Y4+Y2+Y1+Y7 )’’=(Y1’.Y2’.Y4’.Y7’)’,

s =(Y4’.Y2’.Y6’.Y7’)’

(6)根据真值表和逻辑函数画逻辑图。根据上式可以画出如图一所示的逻辑图。

图1 3-8译码器设计一位全减器逻辑图

2) 用双4选1数据选择器(74153)设计一位全减器。

1)根据真值表和逻辑函数画逻辑图。根据上式可以画出如图二所示的逻辑图。

图2 双4选1数据选择器设计一位全减器逻辑图

5.实验结果

1) 3-8译码器设计一位全减器逻辑图仿真后,波形图如图三所示。

图3 3-8译码器设计一位全减器仿真波形图

2)双4选1数据选择器设计一位全减器逻辑图仿真后,波形图如图四所示。

图4 双4选1数据选择器设计一位全减器仿真波形图

6.思考题

(1)如何将译码器作为数据分配器?

答:将G2B接低电平,G1作为使能端,C、B和A作为选择通道地址输入,G2A作为数据输入。如:G1=1,CBA=010时,因为Y2=[(G1?G2A’?G2B)?C’?B?A’]’=G2A,而其余输出端均为高电平,因此,当地址CBA=010时,只有输出端Y2得到与输入相同的数据波形。

实验五译码器及其应用 一、实验目的 1、掌握中规模集成译码器的逻辑功能和使用方法 2、熟悉数码管的使用 二、实验设备与器件 1、+5V直流电源 2、逻辑电平开关 3、逻辑电平显示器 4、拨码开关组 5、译码显示器 6、 74LS138×2 CC4511 三、实验内容 1、74LS138译码器逻辑功能测试 将译码器使能端S1、2S、3S及地址端A2、A1、A0分别接至逻辑电平开关输出口,八个Y???依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表6-输出端0 7Y 1逐项测试74LS138的逻辑功能。 图6-1(a)、(b)分别为其逻辑图及引脚排列。 其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。 当S1=1,2S+3S=0时,器件正常工作,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。 图6-1 3-8线译码器 74LS138逻辑图及引脚排列 表6-1

2、二进制译码器还能方便地实现逻辑函数,如图6-3所示,实现的逻辑函数是 Z = C B A C B A C B A +++ABC 图6-2 作数据分配器 图6-3 实现逻辑函数

3、码显示译码器及译码显示电路 数据拨码开关的使用。 将实验装置上的四组拨码开关的输出A i、B i、C i、D i分别接至4组显示译码/驱动器CC4511的对应输入口,LE、BI、LT接至三个逻辑开关的输出插口,接上+5V显示器的电源,然后按功能表6-2输入的要求揿动四个数码的增减键(“+”与“-”键)和操作与LE、BI、LT对应的三个逻辑开关,观测拨码盘上的四位数与LED数码管显示的对应数字是否一致,及译码显示是否正常。 a、七段发光二极管(LED)数码管 LED数码管是目前最常用的数字显示器,图6-5(a)、(b)为共阴管和共阳管的电路,(c)为两种不同出线形式的引出脚功能图。 符号及引脚功能 b、BCD码七段译码驱动器 此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511(共阴)等,本实验系采用CC4511 BCD码锁存/七段译码/驱动器。驱动共阴极LED数码管。 图6-6为CC4511引脚排列 其中图6-6 CC4511引脚排列 A、B、C、D—BCD码输入端 a、b、c、d、e、f、g—译码输出端,输出“1”有效,用来驱动共阴极LED数码管。 LT—测试输入端,LT=“0”时,译码输出全为“1”

《数据库技术与应用》上机实验报告 目录: 一、概述 二、主要上机实验内容 1.数据库的创建 2.表的创建 3.查询的创建 4.窗体的创建 5.报表的创建 6.宏的创建 三、总结 一、概述 (一)上机内容: 第七周:熟悉Access界面,数据库和表的创建,维护与操作 1. 熟悉Access的启动,推出,界面,菜单,工具栏等; 2. 练习使用向导创建数据库、创建空数据库; 3. 练习创建表结构的三种方法(向导、表设计器、数据表)、表中字段属性设置; 4. 练习向表中输入不同类型的数据; 5. 练习创建和编辑表之间的关系; 6. 练习表的维护(表结构、表内容、表外观) 7. 练习表的操作(查找、替换、排序、筛选等) 第八周:练习创建各种查询 1.选择查询(单表、多表、各种查询表达式) 2.参数查询 3.交叉表查询 4.操作查询(生成查询、删除查询、更新查询、追加查询) 第十周:练习创建各种类型的窗体 1.自动创建纵栏式窗体和表格式窗体; 2.向导创建主|子窗体

3.图表窗体的创建 4.练习通过设计器创建窗体 5.练习美化窗体 第十三周:练习创建各种类型的报表 1.自动创建纵栏式报表和表格式报表; 2.向导创建报表(多表报表、图表报表、标签报表) 3.练习通过设计视图创建报表(主|子报表、自定义报表) 4.练习在报表中添加计算字段和分组汇总数据 第十五周:综合应用 1.了解Access数据库系统开发的一般方法; 2.课程内容的综合练习; 3.编写上机实验报告、答疑 (二)上机完成情况 第七周:熟悉Access界面,数据库和表的创建,维护与操作 完成了创建表,向表中输入不同类型的数据,创建和编辑表之间的关系,进行了表的维护,修改了表的结构、内容、外观,最后进行了表的操作,查找、替换、排序、筛选等。 已完成 第八周:练习创建各种查询 练习选择查询、参数查询、交叉表查询,然后练习并操作查询,生成查询、删除查询、更新查询、追加查询等。 已完成 第十周:练习创建各种类型的窗体 自动创建纵栏式窗体和表格式窗体,向导创建主|子窗体和图表窗体,练习通过设计器创建窗体,美化窗体。 基本完成 第十三周:练习创建各种类型的报表 自动创建纵栏式报表和表格式报表,向导创建报表,练习通过设计视图创建报表,在报表中添加计算字段和分组汇总数据。 已完成 第十五周:综合应用

谢谢欣赏实验三数据选择器 实验人员:班号:学号: 一、实验目的 (1) 熟悉并掌握数据选择器的功能。 (2) 用双4选1数据选择器74LS153设计出一个16选1的数据选择器。 (3) 用双4选1数据选择器74LS153 设计出一个全加法器。 二、实验设备 数字电路实验箱,74LS00,74LS153。 三、实验内容 (1) 测试双4选1数据选择器74LS153的逻辑功能。 74LS153含有两个4选1数据选择器,其中A0和A1为芯片的公共地址输入端,Vcc 和GND分别为芯片的公共电源端和接地端。Figure1为其管脚图: Figure 1 1Q=A1A01D0+A1A0?1D1+A1A0?1D2+A1A0?1D3 2Q=A1A02D0+A1A0?2D1+A1A0?2D2+A1A0?2D3 按下图连接电路: Figure 2 (2) 设某一导弹发射控制机构有两名司令员A、B和两名操作员C、D,只有当两名司令员均同意发射导弹攻击目标且有操作员操作,则发射导弹F。利用所给的实验仪器设计出一个符合上述要求的16选1数据选择器,并用数字电路实验箱上的小灯和开关组合表达实验结果。 思路: 由于本实验需要有四个地址输入端来选中16个数据输入端的地址之中的一个,进而实现选择该数据输入端中的数据的功能,即16选1。而公共的A0、A1两个地址输入端和S使能端(用于片选,已达到分片工作的目的,进而扩展了一位输入)一共可以提供三个地址输入端,故需要采用降维的方法,将一个地址输入隐藏到一个数据输入端Dx 中。本实验可以降一维,也可以降两位。由于两位比较复杂,本实验选择使用降一维的方式。 做法: 画出如应用题中实现所需功能的卡诺图: 谢谢欣赏

实验三译码器与编码器的设计与仿真 一、实验内容 1.参照芯片74LS138的电路结构,用VHDL语言设计3-8译码器; 2.参照芯片74LS148的电路结构,用VHDL语言设计8-3优先编码器。二、电路功能介绍 1.74148:8-3优先编码器(8 to 3 Priority Encoder) 用途:将各种输入信号转换成一组二进制代码,使得计算机可以识别这一信号的作用。键盘里就有大家天天打交道的编码器,当你敲击按键时,被敲击的按键被键盘里的编码器编码成计算机能够识别的ASCII码。译码器与编码器的功能正好相反。 2.74138:3-8译码器(3 to 8 Demultiplexer),也叫3-8解码器 用途:用一组二进制代码来产生各种独立的输出信号,这种输出信号可以用来执行不同的工作。显示器中的像素点受到译码器的输出控制。 逻辑框图:用逻辑符号(Symbol)来解释该电路输入与输出信号之间的逻辑关系,既省事又直观。如下图所示。 一、编码器 1.VHDL实现 library IEEE; use IEEE.std_logic_1164.all; entity pencoder is port ( i7,i6,i5,i4,i3,i2,i1,i0:in STD_LOGIC; a2,a1,a0,idle:out STD_LOGIC); 解 码 信 号 输 出 端低 电 平 有 效 代 码 输入 端 使能输入端

end pencoder; architecture pencoder_arch of pencoder is signal h:STD_LOGIC_VECTOR(7 downto 0); begin h(7)<=i7; h(6)<=i6 and not i7; h(5)<=i5 and not i6 and not i7; h(4)<=i4 and not i5 and not i6 and not i7; h(3)<=i3 and not i4 and not i5 and not i6 and not i7; h(2)<=i2 and not i3 and not i4 and not i5 and not i6 and not i7; h(1)<=i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; h(0)<=i0 and not i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; idle<=not i0 and not i1 and not i2 and not i3 and not i4 and not i5 and not i6 and not i7; a0<=h(1) or h(3) or h(5) or h(7); a1<=h(2) or h(3) or h(6) or h(7); a2<=h(4) or h(5) or h(6) or h(7); 2.波形图:

Verilog HDV 数字设计与综合 实验报告 微电子0901班 姓名:袁东明 _ 学号:_04094026 一、实验课题: 1.八选一数据选择器 2.四位数据比较器 二、八选一数据选择器Verilog程序: 2.1主程序 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out); input [2:0] a,b,c,d,e,f,g,h; input s0,s1,s2; output [2:0] out; reg [2:0] out; always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin case({s0,s1,s2}) 3'd0 : out=a;

3'd1 : out=b; 3'd2 : out=c; 3'd3 : out=d; 3'd4 : out=e; 3'd5 : out=f; 3'd6 : out=g; 3'd7 : out=h; endcase end endmodule 2.2激励程序 module sti; reg [2:0] A,B,C,D,E,F,G,H; reg S0,S1,S2; wire [2:0] OUT; option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT); initial begin A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;

译码器、编码器及其应用 一、实验目的 (1) 掌握中规模集成译码器的逻辑功能和使用方法; (2) 熟悉掌握集成译码器和编码器的应用; (3) 掌握集成译码器的扩展方法。 二、实验设备 数字电路实验箱,74LS20,74LS138。 三、实验内容 (1) 74LS138译码器逻辑功能的测试。将74LS138输出??接数字实验箱LED 管,地址输入接实验箱开关,使能端接固定电平(或GND)。电路图如Figure 1所示: Figure 2 ??????????????时,任意拨动开关,观察LED显示状态,记录观察结果。 ??????????????时,按二进制顺序拨动开关,观察LED显示状态,并与功能表对照,记录观察结果。 用Multisim进行仿真,电路如Figure 3所示。将结果与上面实验结果对照。

Figure 4 (2) 利用3-8译码器74LS138和与非门74LS20实现函数: ?? 四输入与非门74LS20的管脚图如下: 对函数表达式进行化简: ?? ?? A ? ??????????? ???? 按Figure 5所示的电路连接。并用Multisim进行仿真,将结果对比。 Figure 6

(3) 用两片74LS138组成4-16线译码器。 因为要用两片3-8实现4-16译码器,输出端子数目刚好够用。 而输入端只有 A、、三个,故要另用使能端进行片选使两片138译码器 进行分时工作。而实验台上的小灯泡不够用,故只用一个灯泡,而用连接灯泡的导线测试?,在各端子上移动即可。在multisim中仿真电路连接如Figure 7所示(实验台上的电路没有接下面的两个8灯LED): Figure 8 四、实验结果 (1) 74LS138译码器逻辑功能的测试。 当输入 A时,应该是输出低电平,故应该第一个小灯亮。实际用实验台测试时,LE0灯显示如Figure 9所示。当输入 A时,应该是输出低电平,故理论上应该第二个小灯亮。实际用实验台测试时,LE0灯显示如Figure 6所示。 Figure 10

MySQL数据库技术实验报告 系别班级学号姓名地点 地点机房课程名称MySQL数据库技术实验名称实验1 MySQL的使用 实验过程 目的要求: (1)掌握MySQL服务器安装法 (2)掌握MySQL Administrator的基本使用法 (3)基本了解数据库及其对象 实验准备: (1)了解MySQL安装的软硬件要求 (2)了解MYSQL支持的身份验证模式 (3)了解MySQL各组件的主要功能 (4)基本了解数据库、表、数据库对象 实验容: 1.安装MySQL服务器和MySQL界面工具 安装MySQL界面工具。(插入安装好的界面工具截图即可) 2.利用MySQL客户端访问数据库 (1)打开开始,程序,MySQL,MySQL server 5.1,MySQL command line client,进入MySQL客户端界面,输入管理员密码登录。 (2)在客户端输入“help”或“\h”,查看MySQL帮助菜单,仔细阅读帮助菜单的容。

(3)实用show语句查看系统自动创建的数据库。 (4)实用USE语句选择mysql数据库为当前数据库。

(5)使用SHOW TABLES 语句查看当前数据库中的表。 (6)使用了一条SELECT语句查看mysql数据库中存储用户信息表的user的容。 (7)使用use语句将当前的数据库设定为information_schema,并查看数据库数据库中有哪些表。<图表见下页>

实验小结: 在安装MySql中有时可能不能安装不成功,那么卸载时,会存在删除不完全的情况。导致再次安装时依然不成功。 在对某个数据库进行操作之前,必须先选中该数据库。 在MySql安装过程中,注意修改字符集为gb2312或gbk, 以支持中文信息输入。

实验报告 一、实验目的 熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。 二、实验设备 GW48系列SOPC/EDA实验开发系统实验箱一台计算机一台 三、实验内容 1首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出下图所示的仿真波形。最后在实验系统上进行硬件测试,验证本项设计的功能。 源程序为: ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ;

图(1 ) 2选1多路选择器的编译图 、图(2) 功能仿真的波形图 图(3 ) 功能引脚图

图(4) 2选1多路选择器的RTL电路 2. 将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图,并将此文件放在同一目录中。并对上例分别进行编译、综合、仿真,并对其仿真波形做出分析说明。以下是程序: 图(5) 双二选一多路选择器的编译图

图(6) 双路数据选择器功能仿真图 图(7) 双二选一多路选择器的引脚锁定图图 5 双2选1多路选择器 图(8) 双路数据选择器RTL电路图

图(9) 编程下载图 3.、引脚锁定以及硬件下载测试。若选择目标器件是EP1C3,建议选实验电路模式5,用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2 和a1 分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。通过短路帽选择clock0接256Hz信号,clock5 接1024Hz,clock2 接8Hz 信号。最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。 图(10) 实验电路模式5

实验三译码器和编码器 一实验目的 1.掌握译码器、编码器的工作原理和特点。 2.熟悉常用译码器、编码器的逻辑功能和它们的典型应用。 二、实验原理和电路 按照逻辑功能的不同特点,常把数字电路分两大类:一类叫做组合逻辑电路,另一类称为时序逻辑电路。组合逻辑电路在任何时刻其输出的稳态值,仅决定于该时刻各个输入信号取值组合的电路。在这种电路中,输入信号作用以前电路所处的状态对输出信号无影响。通常,组合逻辑电路由门电路组成。 组合逻辑电路的分析方法:根据逻辑图进行二步工作: a.根据逻辑图,逐级写出函数表达式。 b.进行化简:用公式法、图形法或真值表进行化简、归纳。 组合逻辑电路的设计方法:就是从给定逻辑要求出发,求出逻辑图。一般分四步进行。 a.分析要求;将问题分析清楚,理清哪些是输入变量,哪些是输出函数。 b.列真值表。 c.进行化简:变量比较少时,用图形法。变量多时,可用公式化简。 d.画逻辑图:按函数要求画逻辑图。 进行前四步工作,设计已基本完成,但还需选择元件——集成电路,进行实验论证。 值得注意的是,这些步骤并不是固定不变的程序,实际设计时,应根据具体情况和问题难易程度进行取舍。 1.译码器 译码器是组合电路的一部分,所谓译码,就是把代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。译码器分成三类: a.二进制译码器:如中规模2—4线译码器74LS139。,3—8线译码器74LS138等。 b.二—十进制译码器:实现各种代码之间的转换,如BCD码—十进制译码器74LS145等。 c.显示译码器:用来驱动各种数字显示器,如共阴数码管译码驱动74LS48,(74LS248),共阳数码管译码驱动74LS47(74LS247)等。 2.编码器 编码器也是组合电路的一部分。编码器就是实现编码操作的电路,编码实际上是译码相反的过程。按照被编码信号的不同特点和要求,编码器也分成三类: a.二进制编码器:如用门电路构成的4—2线,8—3线编码器等。 b.二—十进制编码器:将十进制的0~9编成BCD码,如:10线十进制—4线BCD码编码器74LS147等。 c.优先编码器:如8—3线优先编码器74LS148等。 三、实验内容及步骤 1.译码器实验 (1)将二进制2-4线译码器74LS139,及二进制3-8译码器74LS138分别插入实验系统IC 空插座中。 按图1.3.1接线,输入G、A、B信号(开关开为“1”、关为“0”),观察LED输出Yo、Y1、Y2、Y3的状态(亮为“1”,灭为“0”),并将结果填入表1.3.1中。

MySQL数据库技术 实验报告 系别班级学号姓名地点 计算机科学系计科1102常赵有C111机房 课程名称MySQL数据库技术实验名称实验1 MySQL的使用 实验过程

目的要求: (1)掌握MySQL服务器安装方法 (2)掌握MySQL Administrator的基本使用方法 (3)基本了解数据库及其对象 实验准备: (1)了解MySQL安装的软硬件要求 (2)了解MYSQL支持的身份验证模式 (3)了解MySQL各组件的主要功能 (4)基本了解数据库、表、数据库对象 实验内容: 1.安装MySQL服务器和MySQL界面工具 安装MySQL界面工具。(插入安装好的界面工具截图即可) 2.利用MySQL客户端访问数据库 (1)打开开始,程序,MySQL,MySQL server 5.1,MySQL command line client,进入MySQL客户端界面,输入管理员密码登录。 (2)在客户端输入“help”或“\h”,查看MySQL帮助菜单,仔细阅读帮助菜单的内容。

(3)实用show语句查看系统自动创建的数据库。 (4)实用USE语句选择mysql数据库为当前数据库。 (5)使用SHOW TABLES 语句查看当前数据库中的表。

(6)使用了一条SELECT语句查看mysql数据库中存储用户信息表的user的内容。 (7)使用use语句将当前的数据库设定为information_schema,并查看数据库数据库中有哪些表。

实验小结: 在安装MySql中有时可能不能安装不成功,那么卸载时,会存在删除不完全的情况。导致再次安装时依然不成功。 在对某个数据库进行操作之前,必须先选中该数据库。 在MySql安装过程中,注意修改字符集为gb2312或gbk, 以支持中文信息输入。

实验2 译码器及其应用 一实验目的 1、掌握中规模集成译码器的逻辑功能和使用方法。 2、熟悉数码管使用。 二实验原理 译码器是一个多输入、多输出的组合逻辑电路。他的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。 1、3线—8线译码器74LS138 图5-6-1 表5-6-1 二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图5-6-2所示。

图 利用使能端方便地将两个3---8译码器组合成一个4---16译码器,如图5-6-4所示。 图5-6-4

2数码显示译码器 A、七段发光二极管(LED)数码管 图5-6-5 B、BCD码七段译码驱动器 本实验采用CC4511 BCD码锁存/七段译码/驱动器。驱动共阴级LED数码管。 如图5-6-6所示。Array A0、A1、A2、A3----BCD 码输入端; Ya\Yb\Yc\Yd\Ye\Yf\Yg--- -译码输出端,输出“1” 有效; LT·---测试输入端; BI·---消隐输入端; LE---锁定端。 表5-6-2为CC4511功能表。译码器还有拒伪码功能,当输入码超过1001时,输 出全为“0”,数码管熄灭。

下图是CC4511和LED数码管连接图: 三实验设备 1、+5V直流电源 2、连续脉冲源 3、逻辑电平开关 4、逻辑电平显示器 5、拨码开关组 6、译码显示器 7、74LS138*2 CC4511 四实验内容 1、数码拨码开关的使用。 2、74LS138译码器逻辑功能测试。 3、用74LS138构成时序脉冲分配器 4、用两片74LS138组合成一个4线—16线译码器,并进行实验。

北京邮电大学国际学院 _11-12_学年第_二_学期实验报告 课程名称:数据库技术与应用 项目名称:基本SOL语句的用法 项目完成人: 姓名:武学超学号: 指导教师:____ ____韩祥斌_____________ 日期: 2012 年 3 月 16 日

目录 一、实验目的............................................. 错误!未定义书签。 1. 结合数据库技术与应用教学的基本知识,理解并掌握基本SQL语句的用法。错误! 未定义书签。 二、实验内容............................................. 错误!未定义书签。 1. 回顾基本SQL语句的语法............................... 错误!未定义书签。 2. 回顾MySQL的基本用法................................. 错误!未定义书签。 3. 初始化数据库,将文件中的内容复制并粘贴到MySQL-Front 的SQL编辑器中,然 后点击“运行”........................................... 错误!未定义书签。 4. 了解实验用例的背景,并进行如下SQL语句的训练:....... 错误!未定义书签。 三、实验环境............................................. 错误!未定义书签。 1. 32位Xp系统下 Mysql 程序(命令行).................. 错误!未定义书签。 四、实验结果............................................. 错误!未定义书签。 1. 问题讨论............................................. 错误!未定义书签。 2. 试验心得............................................. 错误!未定义书签。

电气工程学院电工电子教学基地 数字电子技术实验 实验报告 仿真实验1 用数据选择器设计函数发生器 学号:18291035 姓名:陈涟漪 班级:电气1802 成绩: 指导教师:周晖 完成时间:2020年5 月15 日

数字电子技术实验 仿真实验1 用数据选择器设计函数发生器 1 实验任务 使用数据选择器74LS151和适当门电路设计一函数发生器,能够实现4位二进制码数据范围指示功能。要求该函数发生器能区别以下三种情况: (1)0≤X≤4; (2)5≤X≤9; (3)10≤X≤15。 2 实验电路

3 实验步骤 采用A、B、C、D取0或1依次表示这四位二进制码的从高到低位的取值(例如:A=0,B=1,C=0,D=0表示四位二进制码0100)。则对于第一组来说,共有5个四位二进制码包含在其中,用卡诺图表示如下: 化简即得: 同理,也有5个数包含在第二组中,卡诺图如下: 化简即得: 第三组包含了6个数,卡诺图如下:

化简即得: 对以上三个式子都去两次非并利用摩根定律可得: 这样就完成了该问题的逻辑转化。 根据前面对该实验分析所得到的逻辑表达式可以发现,输入变量为A、B、C、D,但是在后面的逻辑运算中它们的“非”都用到了,也就是第一步我们要得到这四个变量的非。然后再进行后面的与非运算。三个输出变量的状态也可以用三个灯泡来表示,这里采用了三个颜色不同的灯泡用以区分。到这里,逻辑图就可以很容易的用Multisim软件模拟出来。 其中,最上面的X1灯泡亮时,表示输入数字在0≤X≤4范围内,X2亮时表示输入数字在5≤X≤9范围内,X3亮时表示输入数字在10≤X≤15范围内。这里还是用了四个开关,每个开关“开”表示1,“关”表示0,四个开关以ABCD的顺序来表示四位二进制数。四位二进制数同上,也有16中情况,这里不做一一展示,只对每一类给出一种模拟结果。

译码器实验报告 实验三译码器及其应用 一、实验目的 1、掌握译码器的测试方法。 2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。 3、掌握用译码器构成 组合电路的方法。4、学习译码器的扩展。 二、实验仪器 1、数字逻辑电路实验板1块 2、74hc138 3-8线译码器2片 3、74hc20 双4输入与非 门1片 三、实验原理 1、中规模集成译码器74hc138 74hc138是集成3线-8线译码器,

在数字系统中应用比较广泛。图3-1是其引脚排列。其中a2 、a1 、a0 为地址输入端,0y~7y为译码输出端,s1、2s 、3s 为使能端。74hc138真值表如下:74hc138引脚图为:74hc138工作原理为:当s1=1,s2+s3=0时,电路完成译码功能,输出低电平有效。其 中: 2、译码器应用 因为74hc138 三-八线译码器的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项,因此可以利用八条输出线组合构成三变量的任意组合电路。 四、实验内容 1、译码器74hc138 逻辑功能测试(1)控制端功能测试测试电路如图:按上表所示条件输入开关状态。观察并记录译码器输出状态。led指示灯亮为0,灯不 亮为1。

(2)逻辑功能测试 将译码器使能端s1、2s 、3s 及地址端a2、a1、a0 分别接至逻辑电平开关输出口,八个输出端y7 ?????y0依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按 下表逐项测试74hc138的逻辑功能。 2、用74hc138实现逻辑函数y=ab+bc+ca 如果设a2=a,a1=b,a0=c,则函数y 的逻辑图如上所示。用74hc138和74hc20各一块 在实验箱上连接下图线路。并将测试结果下面的记录表中。 3、用两个3线-8线译码器构成4线-16线译码器。利用使能端能方便地将两个3/8译码器组合成一个4/16译码器,如下图所示。 五、实验结果记录:2、74hc138实现逻辑函数y=ab+bc+ca,实验结果记录: 六、实验注意事项

实验三选数据选择器实 验报告 集团公司文件内部编码:(TTT-UUTT-MMYB-URTTY-ITTLTY-

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8”的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在 随后弹出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在 What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对 话框中选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save

实验报告 ----- 李瑞辉 一、实验目的 1. 学会用逻辑图和VHDL 语言设计3-8 译码器; 2. 学会用逻辑图和VHDL 语言设计8-3 编码器; 二、实验原理 1.74148:8-3优先编码器(8 to 3 Priority Encoder) (1)用途:将各种输入信号转换成一组二进制代码,使得计算机可以识别这一信号的作用。 (2)逻辑表达式 ①使能输出端O E的逻辑方程为: EO =I0· I1· I2· I3· I4· I5· 67· EI ②扩展片优先编码输出端G S的逻辑方程为: GS = (I0+I1+I2+I3+I4+I5+I6+I7)· EI ③由74148真值表可列输出逻辑方程为: A2 =(I4+I5+I6+I7)EI A1 = (I2I4I5+I3I4I5+I6+7)· EI A0 = (I1I2I4I6+I3I4I6+I5I6+I7)· EI (3)真值表 INPUTS OUTPUTS EN0N 1N 2N 3N 4N 5N 6N 7N A2 A1 A0 EO GS 1×××××××× 1 1 1 1 1

0××××××× 00 0 00 1 0×××××× 0 10 0 10 1 0××××× 0 1 10 1 00 1 0×××× 0 1 1 10 1 10 1 0××× 0 1 1 1 1 1 0 00 1 0×× 0 1 1 1 1 1 1 0 10 1 0× 0 1 1 1 1 1 1 1 1 00 1 00 1 1 1 1 1 1 1 1 1 10 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 2. 74138:3-8译码器(3 to 8 Demultiplexer),也叫3-8解码器 (1)用途:与编码器相反。用一组二进制代码来产生各种独立的输出信号,这种输出信号可以用来执行不同的工作。 (2)逻辑表达式 (m i 是最小项) (3)真值表 INPUT OUTPUT

实验二译码器及其应用 一、实验目的 1、掌握3 -8线译码器、4 -10线译码器的逻辑功能和使用方法。 2、掌握用两片3 -8线译码器连成4 -16线译码器的方法。 3、掌握使用74LS138实现逻辑函数和做数据分配器的方法。 二、实验原理 译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路称为译码器。译码器在数字系统中有广泛的应用,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。不同的功能可选用不同种类的译码器。 下图表示二进制译码器的一般原理图: 它具有n个输入端,2n个输出端和一个使能输入端。在使能输入端为有效电平时,对应每一组输入代码,只有其中一个输出端为有效电平,其余输出端则为非有效电平。每一个输出所代表的函数对应于n个输入变量的最小项。二进制译码器实际上也是负脉冲输出的脉冲分配器,若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称为多路数据分配器)。 1、3-8线译码器74LS138 它有三个地址输入端A、B、C,它们共有8种状态的组合,即可译出8个输出信号Y0~Y7。它还有三个使能输入端E1、E2、E3。功能表见表1,引脚排列见图2。 表1 74LS138的功能表

三、实验设备与器材 1、数字逻辑电路实验箱 2、数字万用表 3、双踪示波器 3、芯片74LS138两片,74LS42、74LS20各一片 四、实验内容及实验步骤 1、74LS138译码器逻辑功能测试 在数字逻辑电路实验箱IC插座模块中找一个DIP16的插座插上芯片74LS138,并在DIP16插座的第8脚接上实验箱的地(GND),第16脚接上电源+5V(VCC)。将74LS138的输出端Y0~Y7分别接到8个发光二极管上(逻辑电平显示单元),输入端接拨位开关输出(逻辑电平输出单元),逐次拨动开关,根据发光二极管显示的变化,测试74LS138的逻辑功能。 2、两片74LS138组合成4线-16线译码器 按下图连线: 将16个输出端接逻辑电平显示(发光二极管),4个输入端接逻辑电平输出(拨位开关),逐项测试电路的逻辑功能。 3、用74LS138实现逻辑函数和做数据分配器 (1)实现逻辑函数

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8” 的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在随后弹 出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对话框中 选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命 令保存。

四.综合适配 1.选择Processing =>Start Compilation命令,检查发现无程序语法错误。 2.执行Tools =>Netlist Viewer =>RTL Viewe, 生成RTL图。 五.模拟仿真 1.在 File 菜单下,点击 New 命令。在随后弹出的对话框中,切换到 Other Files 页。选中 Vector Waveform File 选项,点击 OK 按钮。 2.选择命令 Edit=>End Time ,时间设置为30000ns , 进入到波形编辑界 面。在 Edit 菜单下,点击Insert Node or Bus… 命令,或在结点名字区连续双击鼠标左键两次,在新出现的框图中点击Node Finder出现结点查找器窗口搜索结点名, 在上一个框图中点击 Node Finder… 按钮后,打开Node Finder 对话框。点击 List 按钮,列出电路所有的端子。点击 >> 按钮,全部加入。点击 OK 按钮,确认。 3.回到 Insert Node or Bus 对话框,点击 OK 按钮,确认。 4.编辑输入激励信号波形.选中 a 信号,在 Edit 菜单下,选择 Value => Clock… 命令。在随后弹出的对话框的 Period 栏目中设定参数为10ns,点击 OK 按钮,重复前面的操作,设置输入信号b的参数为20ns ,c信号的参数为30ns,d信号的参数为40ns,e信号的参数为50ns,f信号的参数为60ns,g信号的参数为70ns,h信号的参数为80ns,输入激励信号波形编辑完毕。同样的,s[0]、s[1]、s[2]的参数分别设置为10ns、20ns、30ns。 5.功能仿真:(1)Processing=>Generate Functional Simulation Netlist

实验六编码器、译码器及应用电路设计 一、实验目的: 1、掌握中规模集成编码器、译码器的逻辑功能测试和使用方法; 1、学会编码器、译码器应用电路设计的方法; 3、熟悉译码显示电路的工作原理。 二、实验原理: 编码是用文字、符号或者数字表示特定对象的过程,在数字电路中是用二进制数进行编码的,相应的二进制数叫二进制代码。编码器就是实现编码操作的电路。本实验使用的是优先编码器74LS147,当输入端有两个或两个以上为低电平时,将对输入信号级别相对高的优先编码,其引脚排列如图6—1所示。 图6—1 74LS147引脚排列图图6—2 74LS138引脚排列图译码是编码的逆过程,是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配和组合控制信号等。不同的功能可选用不同种类的译码器。 译码器按照功能的不同,一般分为三类: 1、变量译码器(二进制译码器):用以表示输入变量的状态,如2—4线、3—8线、4—16线译码器。以3—8线译码器74LS138为例介绍: 图6—2为74LS138的引脚图,其中,A2A1A0为地址输入端,为译码器输出端,为使能端(只有当时,才能进行译码)。 图6—3 74LS42引脚排列图图6—5为CC4511引脚排列图 2、码制变换译码器:用于同一个数据的不同代码之间的相互变换。这种译码器的代表是4—10线译码器,它的功能是将8421BCD码译为十个对象,如74LS42等。它的原理与 74LS138译码器类同,只不过它有四个输入端,十个输出端。4位输入代码共有0000—1111

XX大学数学与计算科学学院 学生实验报告 专业班级姓名学号 实验 日期 2014 年5月1 日至2014 年6 月2 日实验 项目数据库技术及应用实验报告 实验内容与要求一、数据库习题部分 书上习题P72-3,P97-11 二、数据库应用系统设计 从以下二个选题中选取其一,进行相应的系统设计 1) 本专业毕业生信息管理系统设计(2010-2013) 要求最少建立一个不少于30个人的基本信息表数据库,建立完全的个人信息,设置一个超级管理员,3个二级用户帐号,3个三级权限用户帐号。 2) 班级电子资源管理系统 模拟电子图书馆的图书管理系统设计班级电子资源数据库系统,提供资源上传、下载、查询等功能数据操纵。 指 导 教 师 意 见 成绩:签名: 2014 年6 月日备 注

数据库习题部分 习题3 操作环境:Mysql , Navicat for My sql 一、建立关系表Supplier、project、part、spp /* 选择对应数据库,并建立名为supplier的table,需要注意的是图

上的credit在截图定义为int型了(以为会是信用评分),后用alter命令改为了varchar(20) */ 二、用insert语句插入数据 /*因为insert的繁琐,实际的数据录入是以图形化Mysql工具Navicat 进行操作的,如下图*/

三、 1.从supplier中查询下列信息,结果按升序输出 2.列出项目负责人名字,不重复 3.查询以J开头或以L结尾的项目名称

4.查询项目经费高于500万元的项目负责人名字,查询结果包含负责人,项目名称,项目经费,并降序列出项目经费 5.列出信誉为优的供应商及所在城市 6.列出项目经费在500~2000万元之间的项目号和项目名