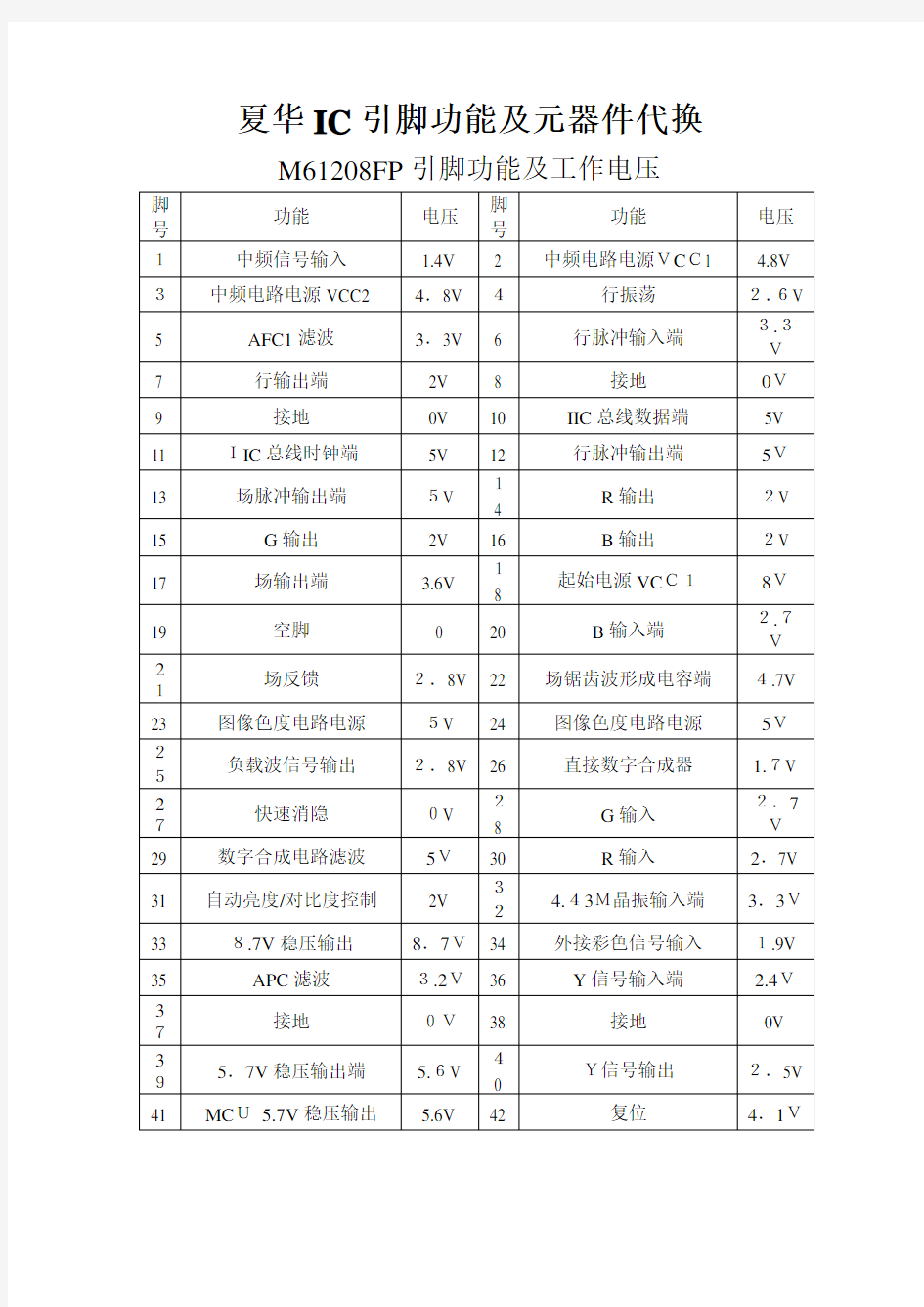

夏华IC引脚功能及元器件代换M61208FP引脚功能及工作电压

J系列CPU(SDA555X)各脚功能及电压

SMT贴片元器件封装类型的识别 封装类型是元件的外观尺寸和形状的集合,它是元件的重要属性之一。相同电子参数的元件可能有不同的封装类型。厂家按照相应封装标准生产元件以保证元件的装配使用和特殊用途。 由于封装技术日新月异且封装代码暂无唯一标准,本指导只给出通用的电子元件封装类型和图示,与SMT工序无关的封装暂不涉及。 1、常见SMT封装 以公司内部产品所用元件为例,如下表:

通常封装材料为塑料,陶瓷。元件的散热部分可能由金属组成。元件的引脚分为有铅和无铅区别。

2、 SMT 封装图示索引 以公司内部产品所用元件为例,如下图示: 名称 图示 常用于 备注 Chip 电阻,电容,电感 MLD 钽电容,二极管 CAE 铝电解电容 Melf 圆柱形玻璃二极管, 电阻(少见) SOT 三极管,效应管 JEDEC(TO) EIAJ(SC) TO 电源模块 JEDEC(TO) OSC 晶振 Xtal 晶振

SOD二极管JEDEC SOIC芯片,座子 SOP芯片 前缀: S:Shrink T:Thin SOJ芯片 PLCC芯片 含LCC座子 (SOCKET)DIP变压器,开关 QFP芯片 BGA芯片 塑料:P 陶瓷:C QFN芯片 SON芯片

3、常见封装的含义 1、BGA(ball grid array):球形触点陈列 表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚LSI用的一种封装。封装本体也可做得比QFP(四侧引脚扁平封装)小。例如,引脚中心距为的360 引脚BGA 仅为31mm 见方;而引脚中心距为的304 引脚QFP 为40mm 见方。而且BGA 不用担心QFP 那样的引脚变形问题。该封装是美国Motorola公司开发的,首先在便携式电话等设备中被采用。 2、DIL(dual in-line):DIP的别称(见DIP)。欧洲半导体厂家多用此名称。 3、DIP(dual in-line Package):双列直插式封装 引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP应用范围包括标准逻辑IC,存贮器LSI,微机电路等。引脚中心距,引脚数从6到64。封装宽度通常为。有的把宽度为和的封装分别称为skinny DIP 和slimDIP(窄体型DIP)。但多数情况下并不加区分,只简单地统称为DIP。 4、Flip-Chip:倒焊芯片 裸芯片封装技术之一,在LSI芯片的电极区制作好金属凸点,然后把金属凸点与印刷基板上的电极区进行压焊连接。封装的占有面积基本上与芯片尺寸相同。是所有封装技术中体积最小、最薄的一种。但如果基板的热膨胀系数与LSI芯片不同,就会在接合处产生反应,从而影响连接的可靠性。因此必须用树脂来加固LSI 芯片,并使用热膨胀系数基本相同的基板材料。5、LCC(Leadless Chip carrier):无引脚芯片载体 指陶瓷基板的四个侧面只有电极接触而无引脚的表面贴装型封装。是高速和高频IC用封装,也称为陶瓷QFN 或QFN-C(见QFN)。

全新IC手 册 珍藏版 汇佳技术咨询部

目录 AN5071……………………………………AN51 95B…………………………………AN5199……………………………………AN52 65………………………………AN5274………………………………AN5277………………………………AN5521………………………………AN5534………………………………AN5539………………………………AN5891………………………………AT24C04……………………………AT24C08……………………………CCFZ3005……………………………CTV222S……………………………DBL2044……………………………DDP3310B……………………………DPTV-3D……………………………DPTV-DX……………………………DPTV-IX……………………………GAL16V8C……………………………HEF4052……………………………HL4066………………………………

IS42G32256-8PQ……………………KA2107………………………………KA2500………………………………KA5Q1265RF…………………………KA5Q1565RF…………………………KA7631………………………………KS88C8424/32/P84 32………………L78MR05……………………………LA4285………………………………LA75665……………………………LA76810……………………………LA76832……………………………LA7830………………………………LA7838………………………………LA7840………………………………LA7846………………………………LA7910………………………………LA7954…………………………………LA86C3348A……………………………LM1269…………………………………LM324…………………………………LV1116……………………………………M3 400N4………………………………M37225ECSP……………………………

12345 6 78 9 10 11 12 13 14 74LS00 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 2输入四与非门 74LS00 1 2 3 4 5678 9 10 11 12 13 14 74LS02 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 4Y 4B 4A Vcc 3B 二输入四或非门 74LS02 六反相器 74LS04 1 2 3 4 5678 9 10 11 12 13 14 74LS10 1B 1Y 1A 2A 3B 2B GND 2Y 2C 3Y 3C 3A Vcc 1C 三输入三与非门 74LS10 1 2 3 4 5678 9 10 11 12 13 14 74LS20 1B 2C 1A NC 2B 1C GND 1Y 1D 2Y NC 2A Vcc 2D 四输入二与非门 74LS20 4线-10线译码器 74LS42 1234 5 6789 10 11 12 13 14 15 16 74LS48 B C LT BI/RBO RBI D A GND e d c b a g f Vcc BCD-七段译码器/驱动器 74LS48 12 345678 9 10 11 12 13 14 74LS74 1CLR 1D 1CLK 1PR 1Q GND 2Q 2PR 2CLK 2D 2CLR Vcc 2Q 正沿触发双D 型触发器 74LS74 双J-K 触发器 74LS76 二输入四异或门 74LS86 常用集成电路管脚图(一) 4位移位寄存器 74LS95 负沿触发双J-K 触发器 74LS112

1、目的: 规范元件成型方式与尺寸,使之标准化作业。 2、适用范围: 适用于茂硕科技元件成型工艺文件;如果客户有其它或高于此规范的特别要求,一律按客户要求执行。 3、职责: 3.1 工艺拟制者负责按本规范操作。 3.2 工艺审核人员负责对规范进行对工艺的全面审核。 3.3工程部经理负责本规范在工艺拟制者中有效执行。 4、程序内容: 4.1操作规范: 4.1.1 收集和确认客户最新资料,文件(如:ENP的ECO,BOM线路图,元件位置图等),产品样板,空PCB板,元器件材料。 4.1.2 对客户资料,文件进行研究,并用通俗易懂的语言将其描述清楚。 4.1.3 对关键性的加工事项和图形示意图,材料加工要求需要进行仔细的研究和确认。 4.1.4 前加工易出错的工序要求特别注意,并加注到生产工艺中。 4.1.5 在成形过程中,除特殊情况下,手工持取元器件一般是持取元器件本体,禁止持取元器件引线,以防止污染元器件引线,从而引起焊接不良。 4.1.6 对于电阻、二极体、电容等非功率半导体元器件,其本体一般没有金属散热器,可以直接持取本体;对于功率半导体元器件如IC,手工持取本体时,禁止触摸其散热面,以免影响散热材料的涂敷或装配。 4.2 工艺制作软件统一用EXCEL2000。 4.3 工艺规范依据主要参照IPC-A-610C标准,元件两引脚间对应于PCB板两焊盘间(W),在PCB板间焊点免除零件脚长即元件焊接后深处的高度为L(mm),如各项目对于元件管脚伸出长度由特别要求时,以客户的要求为准。元件成型方式大致分为立式成型和卧式成型两种,元件成型管脚长度分为三种: (1).元件成型管脚长度=元件管脚伸出长度(L)+PCB板厚(T) (2).元件成型管脚长度=元件管脚伸出长度(L)+PCB板厚(T)+抬高于PCB板面高度(H)

教你认识如何看懂集成电路的线路图 集成电路应用电路图功能集成电路应用电路图具有下列一些功能: ①它表达了集成电路各引脚外电路结构、元器件参数等,从而表示了某一集成电路的完整工作情况。 ②有些集成电路应用电路中,画出了集成电路的内电路方框图,这时对分析集成电路应用电路是相当方便的,但这种表示方式不多。 ③集成电路应用电路有典型应用电路和实用电路两种,前者在集成电路手册中可以查到,后者出现在实用电路中,这两种应用电路相差不大,根据这一特点,在没有实际应用电路图时可以用典型应用电路图作参考,这一方法修理中常常采用。 ④一般情况集成电路应用电路表达了一个完整的单元电路,或一个电路系统,但有些情况下一个完整的电路系统要用到两个或更多的集成电路。 .集成电路应用电路特点集成电路应用电路图具有下列一些特点: ①大部分应用电路不画出内电路方框图,这对识图不利,尤其对初学者进行电路工作分析时更为不利。 ②对初学者而言,分析集成电路的应用电路比分析分立元器件的电路更为困难,这是对集成电路内部电路不了解的原缘,实际上识图也好、修理也好,集成电路比分立元器件电路更为方便。 ③对集成电路应用电路而言,大致了解集成电路内部电路和详细了解各引脚作用的情况下,识图是比较方便的。这是因为同类型集成电路具有规律性,在掌握了它们的共性后,可以方便地分析许多同功能不同型号的集成电路应用电路。 .集成电路应用电路识图方法和注意事项分析集成电路的方法和注意事项主要有下列几点:(1)了解各引脚的作用是识图的关键了解各引脚的作用可以查阅有关集成电路应用手册。知道了各引脚作用之后,分析各引脚外电路工作原理和元器件作用就方便了。例如:知道①脚是输入引脚,那么与①脚所串联的电容是输入端耦合电路,与①脚相连的电路是输入电

元件成形工艺规范 1、目的 规范常用通孔插装元器件的成形工艺,加强元件前加工和成形的质量控制,避免和减少元件成形产生的损耗,保障元件的性能,提高产品的可靠性。 2、适用范围 本规范适用于本公司产品的插装元件成形、品质检验、加工要求制作依据。 3、引用/参考标准 IPC-A-610C 电子组装件的验收条件 4、名词解释 4.1引脚(引线):从元器件延伸出的用于机械或电气连接的单根或绞合金属线。 4.2通孔安装:利用元器件引脚穿过PCB板上孔做电气连接和机械固定。 4.3封装保护距离:安装在通孔中的组件从器件的本体球状连接部分或引脚焊接部分到器件引脚折弯处的距离至少相当于一个引脚的直径或厚度或0.8mm中的最大者,下图示 出了三种器件的封装保护距离d o 4.4变向折弯:弓I脚折弯后引脚的伸展方向有发生改变。

4.5无变向折弯:引脚折弯后引脚的伸展方向没有发生改变。非变向折弯通常用于消除装 4.6抬高距离:安装于PCB板上的元器件本体底部到板面的垂直距离。 5、规范内容 5.1准备工作规范 5.1.1元件成形全过程必须有静电防护措施。 5.121 —般情况下,元件成形过程中,如果会接触到元件引脚,就必须戴指套。 5.122个别有散热面的元件,要求不能接触到散热面,也必须戴指套。 5.1.2.3 元件手工折弯时的元件持取方法:不能直接持取元件本体而进行管脚折弯,必 须持取元件管脚部份进行折弯,同时需要戴指套操作。 F图是两种成形方式对比,图左是正确的加工方式,图右是错误的加工方式: 5.1.3引脚折弯参数选择 5.1.3.1 封装保护距离d 以下是常见元件的封装保护距离

元器件封装及基本管脚定义说明 以下收录说明的元件为常规元件 A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类. (像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。 元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器 1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4 II. 贴片式 [0201 0402 0603 0805 1206] 贴片电阻 0603表示的是封装尺寸与具体阻值没有关系 但封装尺寸与功率有关通常来说 0201 1/20W 0402 1/16W 0603 1/10W

0805 1/8W 1206 1/4W 电容电阻外形尺寸与封装的对应关系是: 0402=1.0x0.5 0603=1.6x0.8 0805=2.0x1.2 1206=3.2x1.6 1210=3.2x2.5 1812=4.5x3.2 2225=5.6x6.5 III. 整合式 [0402 0603 4合一或8合一排阻] IIII. 可调式[VR1~VR5] 2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225] II. 有极性电容分两种: 电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种] 钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25V D TYP E (7343 35V] 3. 电感: I.DIP型电感 II.SMD 型电感

关于元件整形要求说明 目的: 规范和指导现场作业人员的操作步骤及质量要求,了解整形的制作过程,成型条件,元件图形标准的认识 使用范围: 本说明适用于电子产品中元器件成型方式,组合及相关质量要求说明 图示说明: a.上图H代表元件抬高要求的高度控制 b.上图W表示两引脚之间的宽度间距控制 c.上图L表示元件引脚伸出长度控制 d.上图R表示引脚限位卡口的弧度控制 e.计算元件下方全部引脚的总长度的时候需要将抬高度H加上引脚伸出长度L值 f.上图R的弧度尺寸已经包含在H高度尺寸内 仓库领出原材料封装要求: 对于批量性生产需要使用的电子元件,要求来料时必须是原包装,不可以是散装物料,这样才可以实行机械加工,减少时间。 元件机加工操作流程: a.首先加工人员必须熟悉单个元件所要成型元件的形状及品质要求,通过了解工艺部门 制定的元件成型说明图示,文件说明,成型元件清单及成型条件说明内容方可开始作业 b.根据成型条件找出相对应的整形设备,调整好距离及其他各项参数(如不能正确调整 可通知现场工艺和设备调试人员) c.根据工艺指导说明文件中需要成型的元件清单,依次对此型号产品所需元件进行成型 条件加工,注意必须对第一个加工好的元件进行首件确认,使用游标卡尺核对引脚长度,引脚之间的宽度及弯曲弧度是否是文件规定数值,并且元件型号正确,如确认结果符合要求可继续操作,连续测量5个单个元件才可以连续作业,如不符合要求调整设备也可通知现场工艺和设备调试人员进行处理 d.在加工过程中必须阶段性对成型好的元件进行抽查检验,防止设备不稳定或人为造成 尺寸偏差,造成元件不良或报废 e.记录加工元件型号和数量,保持数据清晰,正确具有可追溯性 f.单个元件加工完成后使用塑料袋将成型完好的元件封装起来,在外层贴上产品型号, 元件型号规格,加工数量,加工尺寸要求及作业者签字 手工成型说明

创建元件电气图形符号 在绘制原理图过程中,可能会出现下列几种情况: 1)找不到所需要放置的元件的电气图形符号(可能由于元件的型号比较新或比较特殊, 电气图形库中没有收录)。 2)查找到的元件的电气图形符号不复合要求。如Miscellaneous.lib库中的Diode(二极管)电气图形符号、NPN(三极管)电气图形符号与GB4728-85标准不一致。 3)元件的电气图形符号库内的引脚编号与PCB封装库内元件的引脚编号不一致。如 Miscellaneous.lib库中的Diode(二极管)电气图形符号的引脚的编号是1、2,而在PCB库中的二极管封装形式(如Diode0.4)的引脚编号是A、K。 4)元件的电气图形符号的尺寸偏大,或引脚尺寸太长,占用的图纸面积太多。 出现上述的情况后可以通过修改已有元件库中元件电气图形符号的方法或重新创建电气图形符号的方法来满足需要。如图2所示的原理图中的数码管电气图形符号。 下面介绍启动创建、修改元件电气图形号的操作过程。 启动元件电气图形修改界面 1)执行菜单命令“File/New”,在图1所示的窗口中选择“Schematic Library Document”,鼠标左键单击“OK”按钮即可启动元件电气图形符号编辑器。修改库文件的名称,库文件名称的后缀必须以“lib”结尾。双击库文件名得到库元件编辑窗口,单击“Browse Schlib”得到如图3所示的编辑界面。 图1创建原理图库元件文件 原理图库元件的编辑界面与原理图的编辑界面相似,也包括菜单栏,工具栏,资源管理器,浏览库文件窗口,编辑区域等部分。菜单栏、工具栏的功能与原理图相类似。通过资源理器可以在不同的文件之间进行切换。浏览库文件窗口中,“Component”列表中列出了当前库文件中的库元件,Components(元件列表窗)内列出当前被编辑元件所在库中的所有元件,“Mask”(元件过滤器)文本盒的作用与原理图编辑器中的“Filter”相同,元件列表窗内的元件的显示通过“Mask”过滤器的过滤来决定,如该文本盒内容为“*”时,将显示当前元件库内的所有元件。单击元件列表窗下的“<<”按钮,则将列表窗内的第一个元件作为当前编辑元件。单击元件列表窗下的“>>”按钮,则将列表窗内的最后一个元件作为当前编辑元件。单击元件列表窗下的“<”按钮,则将列表窗内的上一个元件作为当前编

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2. 555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图2 555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS 端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和 地端GND。这个特殊的触发器有两个特点: (1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s 即触发端(TR)则要求低电乎; (2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是

电气连接终端(引线和元器件引脚) 以下条件适用于引线和元器件引脚。较适合的的绕线法可使引脚 / 引线与接线端间有足够的机械性连接以确保引脚/ 引线不在焊接过程中移动。一般机械性连接以180°绕线形成。 以上绕线条件的例外是当接线于双叉、槽形、穿孔接线柱时,引脚 / 引线可直接穿过,无需绕线。除了槽形接线柱外(6.7.4节),无绕线的引脚 / 引线应以粘结支撑,粘贴或恰当程度的约束以提供对固定部件的机械性支持,防止振动、震荡及引线的移位由引线传送破坏焊点。 本章内容分成11节。因不能对所有引线/ 引脚与接线端的组合一一对号入座,所以条件一般概括以便应用于相似的组合。例如:连接在塔形接线柱的电阻器引脚和多芯跨接线有相同的绕线和定位要求,但只有多芯线可能会鸟笼形发散。 除了本章的条件外,焊接应满足第5章的标准。 本章包括以下内容: 6.1 端接–边缘夹簧接线端 6.2 铆装件 6.2.1 扁平包式翻边 6.2.2 嗽叭口形翻边 6.2.3 花瓣形翻边 6.2.4 连接终端 6.2.4.1 塔形接线柱 6.2.4.2 双叉式接线柱 6.2.5 镕合固定 6.3 导线 / 引脚预备–镀锡 6.4 引脚的成形–应力释放 6.5 环形绕线 6.6 应力释放引脚 / 引线弯曲6.6.1 线把 6.6.2 单线 6.7 引脚 / 引线布局 6.7.1 塔形接线柱和直针接线柱6.7.2 双叉接线柱 6.7.2.1 边侧绕线固定 6.7.2.2 底与顶部绕线固定 6.7.3 粘结支撑 6.7.4 槽形接线柱 6.7.5 穿孔接线柱 6.7.6 钩形接线柱 6.7.7 焊锡杯 6.7.8 串联接线柱 6.7.9 AWG30和更小直径接线6.8 绝缘层 6.8.1 间隙 6.8.2 损伤 6.8.2.1 焊前 6.8.2.2 焊后 6.8.3 挠性封套 6.9 导线 / 芯线 6.9.1 形变 6.9.2 芯线发散(鸟笼形)6.9.3 损伤 6.10 接线柱–焊接 6.10.1 塔形接线柱 6.10.2 双叉接线柱 6.10.3 槽形接线柱 6.10.4 穿孔接线柱 6.10.5 钩 / 针形接线柱 6.10.6 焊锡杯 6.11 导线–损伤–焊后

第一节三端稳压IC 电子产品中常见到的三端稳压集成电路有正电压输出的78××系列和负电压输出的79××系列。故名思义,三端IC是指这种稳压用的集成电路只有三条引脚输出,分别是输入端、接地端和输出端。它的样子象是普通的三极管,TO-220的标准封装,也有9013样子的TO-92封装。 用78/79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。该系列集成稳压IC型号中的78或79后面的数字代表该三端集成稳压电路的输出电压,如7806表示输出电压为正6V,7909表示输出电压为负9V。 78/79系列三端稳压IC有很多电子厂家生产,80年代就有了,通常前缀为生产厂家的代号,如TA7805是东芝的产品,AN7909是松下的产品。(点击这里,查看有关看前缀识别集成电路的知识) 有时在数字78或79后面还有一个M或L,如78M12或79L24,用来区别输出电流和封装形式等,其中78L调系列的最大输出电流为100mA,78M系列最大输出电流为1A,78系列最大输出电流为1.5A。它的封装也有多种,详见图。塑料封装的稳压电路具有安装容易、价格低廉等优点,因此用得比较多。79系列除了输出电压为负。引出脚排列不同以外,命名方法、外形等均与78系列的相同。 因为三端固定集成稳压电路的使用方便,电子制作中经常采用,可以用来改装分立元件的稳压电源,也经常用作电子设备的工作电源。电路图如图所示。 注意三端集成稳压电路的输入、输出和接地端绝不能接错,不然容易烧坏。一般三端集成稳压电路的最小输入、输出电压差约为2V,否则不能输出稳定的电压,一般应使电压差保持在4-5V,即经变压器变压,二极管整流,电容器滤波后的电压应比稳压值高一些。 在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率的条件下不用)。当稳压管温度过高时,稳压性能将变差,甚至损坏。 当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。 第二节语音集成电路 电子制作中经常用到音乐集成电路和语言集成电路,一般称为语言片和音乐片。它们一般都是软包封,即芯片直接用黑胶封装在一小块电路板上。语音IC一般还需要少量外围元件才能工作,它们可直接焊到这块电路板上。

TDA集成块引脚功能 TDA8362集成块引脚功能 脚号功能电压(v) 1 音频去加重 3 2 中频调整回路 5.9 3 中频调整回路 5.9 4 视频识别输入7.9 5 伴音中频输入 3.8 6 外接音频输入 3.8 7 图像中频输出 3.5 8 电源退耦回路 1.7 9 地0 10 +8V电源8 11 地0 12 调谐滤波退耦 3.4 13 内部视频信号输入 4.7 14 清晰度控制0~4.3 15 外部视频信号输入 4.2 16 色度信号输入AV/TV开关(TV/AV1/S/AV2) 0/7.6/4/7.6 17 亮度控制0~4.2 18 B输出 2.7 19 G输出 2.7 20 R输出 2.7 21 RGB和消隐输入0.5 22 R输入 3.4 23 G输入 3.4 24 B输入 3.4 25 对比度控制0~3.6 26 色饱和度控制0~4.4 27 色相控制输入与SECAM.CVBS输出0~5/6 28 B-Y输入 3.8 29 R-Y输入 3.8 30 R-Y输出 1.5 31 B-Y输出 1.5 32 4.43基频与SECAM识别输出(P.N/S) 0.5/5 33 色同步相位检波 5.1 34 3.58MHZ晶振连接 1.4 35 4.43MHZ晶振连接 2

36 行起振电源8.4 37 行激励输出0.5 38 行逆程入\沙堡脉冲出 2.8 39 行中心调整与滤波 2.8 40 行相位滤波回路 3.9 41 场逆程输入 2.4 42 场起振 2.7 43 场激励输出 1 44 AFC输出 4.7 45 中频输入4.1 46 中频输入 4.1 47 高频头AGC输出8.8 48 AGC检波 3.8 49 RF AGC调节 1.3 50 音频输出 3.3 51 伴音解调退耦 4.1 52 电源退耦6.5TDA3862的亮度信号是由IC的7脚输出全电视信号,经IC的7脚上的三极管发射极输出经三极管缓冲由发射极输出经4.5MHz、5.5MHz、6.0MHz、6.5MHz 信号陷波分别送入集成电路4053的12脚和13脚,利用其内部的开关进行制式转换。通过集成电路4053的9脚和10脚控制和AV输入端子进来的信号进行切换,最终得到的信号由集成电路4053的15脚输出。 各种制式信号的亮度和对比度信号分离都是在集成电路内部完成。当然进行亮色分离之前,必须确知当前信号的彩色制式,这也是有IC的内部完成。在亮度分离中,唯一与外部电路相关的引脚是12脚,该脚的功能是调整内部彩色、滤波器的频率。 1. 黑屏,但字符显示正常:⑴.检查是否工作在AV 状态。⑵.测试IC的17脚和25脚电压是否太低。⑶.测试字符底色消隐电压(IC的21脚)是否太高,太高会使整幅画面被消隐,可把该脚对地短接一下看看要是出现图像是由此造成。 ⑷. 沙堡脉冲异常会使屏黑有字符,IC的38脚与地短路屏幕上没有什么明显情况,要是把38脚给它弄开路就会出现黑屏,字符正常的怪病来。 2. 无色彩或缺色:由TDA8362与TDA4665组成的电视机。NTSC制式正常,但PAL制式无色维修时可把TDA4665弄下来。把IC的30脚和29脚、31脚和28脚各用一个电容0.1μF连接起来瞧瞧电视机是否有彩色出现如果有那是DTA4665完蛋了。(有时色彩得等一会才出现)。 IC的行震荡是在IC的内部完成但是它需要IC的35 脚晶振提供效准信号,电路才能正常工作。 当信号从AV/TV或S端子送来的视频信号或亮度信号号,在IC的内部同步分离,产生复合同步脉冲,在进一步分离出行/场同步信号。IC的36脚是供给内部小信

元器件引脚成形与切脚工艺、检验工艺规程 (手工插装元器件)

1.目的 1.1.1.1.本规程规定了手工插装电子元器件引脚成形与切脚应满足的工 艺要求,以及引脚成形与切脚过程的检验程序。 2.适用范围 2.1.1.1.本规程适用于产品分立电子元器件插装前的引脚成形与切脚,规 定了元器件引脚成形与切脚的技术要求和质量保证措施,同时也 可作为设计、生产、检验的依据。 3.适用人员 3.1.1.1.本规程适用于产品生产的工艺人员、电子装联操作人员、质量检 验人员等。 4.参考文件 4.1.1.1.IPC-A-610D 《电子组件的可接受性》。 4.1.1.2.IPC J-STD-001D 《焊接的电气和电子组件要求》。 4.1.1.3.QJ 3171—2003 《航天电子电气产品元器件成形技术要求》。 4.1.1.4.QJ 165A—1995 《航天电子电气产品安装通用技术要求》。 4.1.1. 5.ANSI/ESD S20.20-2007 《静电放电控制方案》。 5.名词/术语 5.1.1.1.功能孔:PCB上用于电气连接的孔。 5.1.1.2.非功能孔:PCB上用于机械安装或固定的孔。 5.1.1.3.支撑孔(Supported Hole):两层及多层PCB上的功能孔,孔壁上 镀覆金属,俗称镀通孔。 5.1.1.4.非支撑孔(Unsupported Hole):单层或双层PCB上的功能孔,孔 壁上不镀覆金属,俗称非镀通孔。 5.1.1.5.淬火引脚(Tempered lead):元器件的引脚经过淬火处理。

6.工艺 元器件成形与切脚是整个PCBA生产的首要工序,成形与切脚的质量直接影响后续的产品生产。 6.1.工艺流程 6.1.1.成形与切脚的工艺流程图 图6-1元器件成形与切脚工艺流程

集成块的管脚认识 在电子技术高速发展的今天,集成电路的使用已经相当普遍。我们在使用集成块时,首先遇到的一个问题就是如何正确识别集成电路的各管脚,使之与电路图中所标的管脚相对应,这是使用者必须熟练掌握的一项基本技能。 半导体集成电路的品种、规格繁多,但就其管脚的排列情况常见的有以下 3 种形式:一是按圆周分布,即所有管脚分布在同一个圆周上;二是双列分布,即管脚分两行排列;三是单列分布,即管脚单行排列。 为了便于使用者识别集成电路的管脚排列顺序,各种集成电路一般都标有一定的标记,现把常见的几种标记及管脚顺序的识别方法分述如下: 1 .管键标记:使用这种识别标记的集成电路,用圆柱形金属外壳封装,其管脚按圆周分布,外形如图① 所示。它的管脚排列顺序是:从管顶往下看,自管键开始沿逆时针方向依次是第 1 、 2 、3…… 脚(见图① )。5G1555 、 AN374 等的管脚就是这样排列的。 2 .弧形凹口标记:这种识别标记多用在双列直插型集成电路上。弧形凹口位于集成电路的一个端部,其外形如图② 所示。管脚排列顺序的识别方法是,正视集成块外壳上所标的型号,弧形凹口下方左起第 1 脚为该集成电路的第 1 脚,以这个管脚开始沿逆时针方向依次是第2 、 3 、4…… 脚(见图② )。 TA7614AP 、μPC1353C 等就是使用这种识别标记的。

3 .圆形凹坑、小圆圈、色条标记:双列直插型和单列直插型的集成电路多采用这种识别标记,其外形如图③ 所示。这种集成电路的管脚识别标记和型号都标在外壳的同一平面上。它的管脚排列顺序是,正视集成块的型号,圆形凹坑(或小圆圈、色条)的下方左起第一脚为集成电路的第 1 脚。对于双列直插型的集成块,从第 1 脚开始沿逆时针方向,依次是第 2 、 3 、4…… 脚;对于单列直插型的集成块,从第 1 脚开始其后依次是第 2 、 3 、4…… 脚(见图③ )。 LA4422 、 NE555P 、 CD4017BCN 等都是使用这种识别标记。 4 .斜切角标记:这种标记一般用在单列直插型集成电路上,其外形如图④ 所示。其管脚的排列顺序是,从斜切角的这一端开始,依次是第 1 、2 、3…… 脚(见图④ )。 AN5710 、 LA4140 等都是使用这种识别标记。 应当指出有不少集成电路同时使用两种识别标记,如μPC1366 ,既使用弧形凹口标记,又使用小圆圈标记。但两种标记对集成电路的管脚排列顺序的识别效果是统一的(见图⑤ 所示)。也有少数的集成电路,外壳上没有以上所介绍的各种标记,而只有该集成电路的型号,对于这种集成电路管脚序号的识别,应把集成块上印有型号的一面朝上,正视型号,其左下方的第 1 脚为集成电路的第 1 脚位置,然后沿逆时针方向计数,依

Dxp规则报错及解决方法 1.[Short-Circuit Constraint Violation] 详细:Advanced PCB stm32.PcbDoc Short-Circuit Constraint: Between Via (73.3044mm,64.9224mm) Top Layer to Bottom Layer And Track (73.3044mm,64.9224mm)(73.32061mm,64.90619mm) Top Layer 16:41:48 2013/4/16 497 原因:过孔没有标明网络 解决:上下两层短路,注意一下过孔有无错误 2.[Silkscreen Over Component Pads Constraint Violation] 详细:Advanced PCB stm32.PcbDoc Silkscreen Over Component Pads Constraint: Between Track (84.85998mm,42.58mm)(84.85998mm,43.78mm) Top Overlay And Pad C23-1(85.36mm,43.18mm) Top Layer [Top Overlay] to [Top Solder] clearance [0.02503mm] 原因:丝印层与焊盘的距离问题 解决:在网上查资料后,发现,将规则(Rules...)里面的Manufacturing某个参数改一下就可以避免这种绿色警告,分享如下。首先,design-->rules...-->左边若干选项中有一个Manufacturing,子选项Silkscreen over Component Pads 3.[Minimum Solder Mask Sliver Constraint Violation] 详细:Advanced PCB stm32.PcbDoc Minimum Solder Mask Sliver Constraint: Between Pad *1-16(76.68859mm,74.71903mm) Multi-Layer And Pad U1-48(75.89561mm,73.37141mm) Top Layer [Top Solder] Mask Sliver [0.24442mm] 17:20:01 2013/4/16 100 原因:焊盘间的最小间距问题 解决:首先,design-->rules...-->左边若干选项中有一个Manufacturing,子选项minimum solder mask sliver,原来的constraints选框内显示的clearance将间距改为0之后绿色警告消失。 4.[Un-Routed Net Constraint Violation] 详细:Advanced PCB stm32.PcbDoc Un-Routed Net Constraint: Between Track (73.3472mm,83.812mm)(76.89332mm,83.812mm) Top Layer And Pad *1-6(73.6886mm,89.719mm) Bottom Layer 17:23:03 2013/4/16 359 原因:存在没有连或没有连好的线 解决:根据提示找到该线补连 5.[Clearance Constraint Violation] 详细:stm32.PcbDoc Advanced PCB Clearance Constraint: Between Via (73.32061mm,64.90619mm) Top Layer to Bottom Layer And Polygon Arc (73.3044mm,64.9224mm) Top Layer 18:53:43 2013/4/17 1 原因:不同网络的最小间隔问题 解决:首先,design-->rules...-->左边若干选项中有一个Electrical,子选项clearance,原来的Different Nets Only最小清除改为0.1之后警告消失。 6.[Clearance Constraint Violation]

迪美光电电路板焊接标准概述 ---A手插器件焊接工艺标准 一.没有引脚的PTH/ VIAS (通孔或过锡孔) 标准的 (1)孔完全充满焊料。焊盘表面显示良好的润湿。 (2)没有可见的焊接缺陷。 可接受的 (1)焊锡润湿孔壁与焊盘表面。 (2)直径小于等于1.5mm的孔必须充满焊料。 (3)直径大于1.5mm的孔没有必要充满焊料但整个孔表面和上表面必须有焊锡润湿。

不可接受的 (1)部分或整个孔表面和上表面没有焊料润湿。 (2)孔表面和焊盘没有润湿。在两面焊料流动不连续。 二.直线形导线 1、最小焊锡敷层(少锡) 标准的 (1)焊点光滑、明亮呈现羽翼状薄边,显示出良好的流动和润湿。(2)导线轮廓可见。

可接受的 (1)焊锡的最大凹陷为板厚(W)的25%,只要在引脚与焊盘表面仍呈现出良好的浸润。 不可接受的 (1)焊料凹陷超过板厚(W)的25%。 (2)焊接表现为由焊锡不足引起的没有充满孔和/或焊盘没有完全润湿。 2、最大焊锡敷层(多锡) 标准的 (1)焊点光滑、明亮呈现羽翼状薄边,显示出良好的流动和润湿。

(2)引脚轮廓可见。 可接受的 (1)在导体与终端之间多锡,但仍然润湿且结合成一个凹形焊接带。(2)引脚轮廓可见。 不可接受的 (1)在导体与终端焊盘之间形成了一个多锡的凸形焊接带。 (2)引脚轮廓不可见。 3、弯曲半径焊接

标准的 (1)焊接带呈现凹形,并且没有延伸到元件引脚形成的弯曲半径处。 可接受的 (1)焊料没有超出焊盘区域且焊接带呈现凹形。 (2)焊料到元件本体之间的距离不得小于一个引脚的直径。 不可接受的 (1)焊料超出焊接区域并且焊接带不呈现凹形。 (2)焊料到元件本体之间的距离小于一个引脚的直径。

电源驱动芯片uc3842引脚图及引脚功能 电流型脉宽调制器UC3842 的主要优点:单端输出,可直接驱动双极型功率管或场效应管;管脚数量少,外围电路简单;电压调整率可达0.01%;工作频率更可高达500 kHz;启动电流小于 1 mA,正常工作电流为12 mA;欠压锁定,带滞后;锁存脉宽调制,可逐周限流;并可利用高频变压器实现与电网隔离。它适用于无工频变压器的低于250w的小功率开关电源,其工作温度为0~+70℃,最高输入电压为36 V,具有最大电流为1 A的拉、灌输出电流。 UC3842外形图 UC3842引脚图和内部电路方框图

UC3842各引脚功能简介如下: ---1脚COMP是内部误差放大器的输出端,通常此脚与2脚之间接有反馈网络,以确定误差放大器的增益和频响。 ---2脚FEED BACK是反馈电压输入端,此脚与内部误差放大器同向输入端的基准电压(一般为+ 2.5V)进行比较,产生控制电压,控制脉冲的宽度。 ---3 脚ISENSE是电流传感端。在外围电路中,在功率开关管(如VMos管)的源极串接一个小阻值的取样电阻,将脉冲变压器的电流转换成电压,此电压送入3 脚,控制脉宽。此外,当电源电压异常时,功率开关管的电流增大,当取样电阻上的电压超过1V时,UC3842就停止输出,有效地保护了功率开关管。 ---4脚RT/CT是定时端。锯齿波振荡器外接定时电容C和定时电阻R的公共端。 ---5脚GND是接地。 ---6脚OUT是输出端,此脚为图滕柱式输出,驱动能力是±lA。这种图腾柱结构对被驱动的功率管的关断有利,因为当三极管VTl截止时,VT2导通,为功率管关断时提供了低阻抗的反向抽取电流回路,加速功率管的关断。 ---7脚Vcc是电源。当供电电压低于+16V时,UC3824不工作,此时耗电在1mA以下。输入电压可以通过一个大阻值电阻从高压降压获得。芯片工作后,输入电压可在+10~+30V之间波