文章编号:167121742(2007)022*******

DMA 控制器在DSP 数据采集系统中的应用

马 跃, 卿粼波, 滕奇志

(四川大学电子信息学院图像信息研究所,四川成都610064)

摘要:DMA 控制器可以无需CPU 介入而在内部存储器、外部存储器和芯片外设之间传送数据,其在DSP 系统

中有广泛的应用价值。基于以DSP 芯片TMS320VC5509为核心的数据采集处理系统,通过对FIFO 、SDRAM 和

TMS320VC5509DMA 控制器的介绍,分别给出了具体的接口电路硬件设计和实际软件的代码示例。

关 键 词:TMS320VC5509;DMA 控制器;EMIF ;数据采集

中图分类号:TN91413

文献标识码:A

收稿日期

:2006209228;修订日期:20062112031 引言

随着信息技术的飞速发展,数字信号处理器(Digital Signal Processor )技术应运而生,并得到迅速发展。其开发手段不断改进,功能日益强大,性能价格比不断上升,因而DSP 系统被广泛应用于当今技术革命的各个领域中。基于TI 公司的TMS320VC5509为核心的数据采集系统,着重介绍了如何利用DSP5509的DMA 控制器,实现系统中图像数据的传输功能。

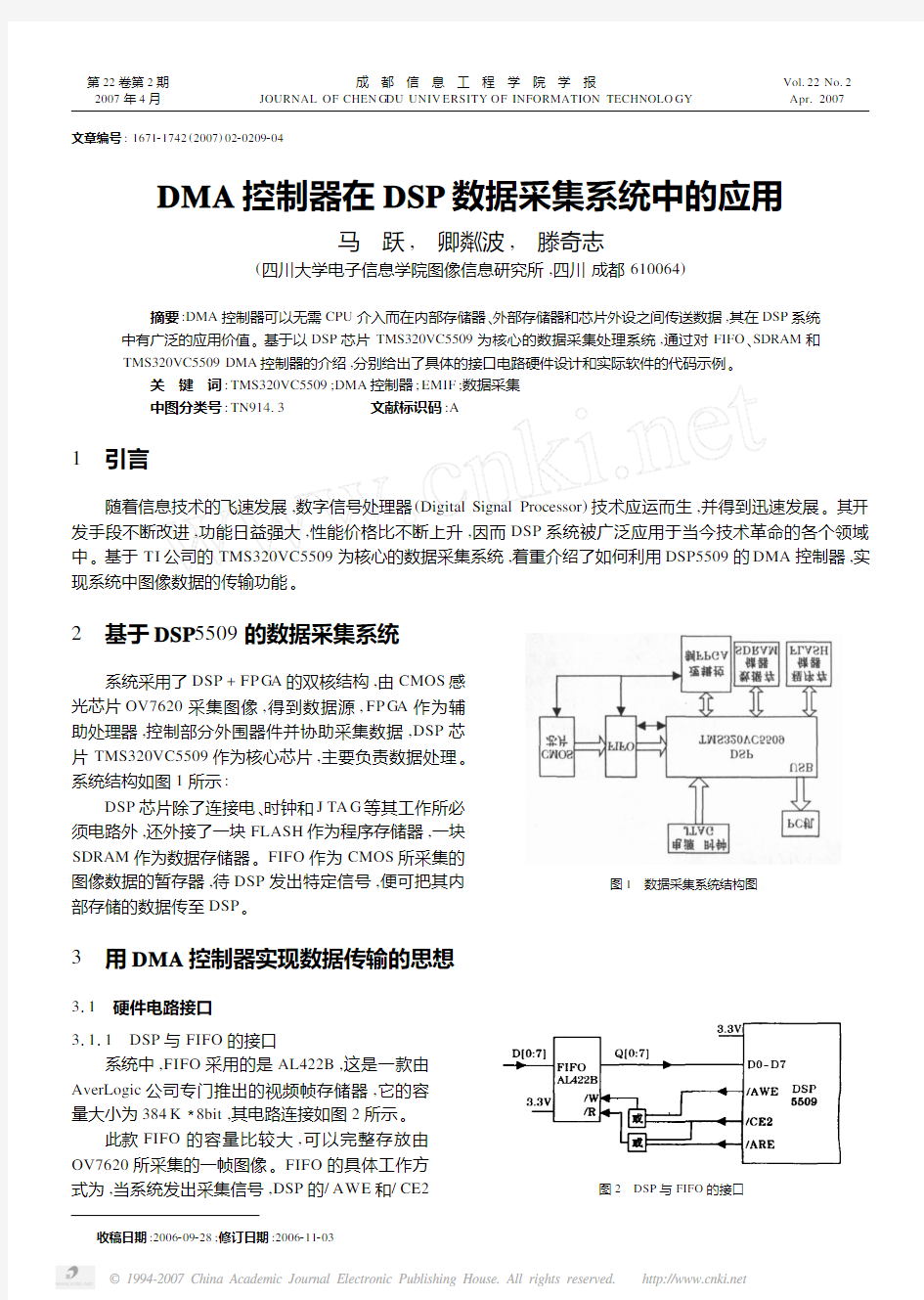

图1 数据采集系统结构图

2 基于DSP 5509的数据采集系统

系统采用了DSP +FP G A

的双核结构,由CMOS 感

光芯片OV7620采集图像,得到数据源,FP G A 作为辅

助处理器,控制部分外围器件并协助采集数据,DSP 芯

片TMS320VC5509作为核心芯片,主要负责数据处理。系统结构如图1所示:

DSP 芯片除了连接电、时钟和J TA G 等其工作所必

须电路外,还外接了一块FLASH 作为程序存储器,一块

SDRAM 作为数据存储器。FIFO 作为CMOS 所采集的

图像数据的暂存器,待DSP 发出特定信号,便可把其内

部存储的数据传至DSP 。3 用DMA 控制器实现数据传输的思想

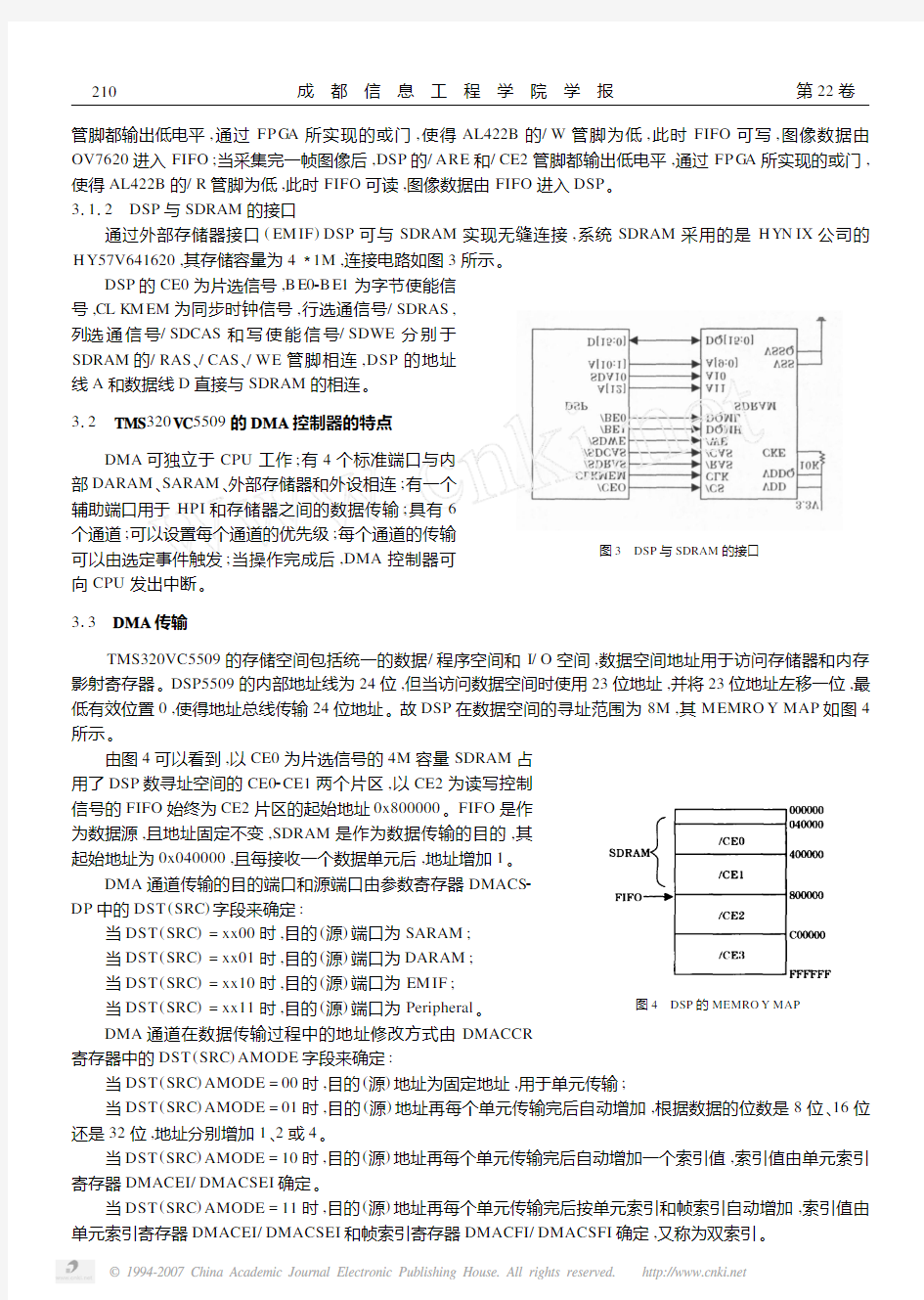

图2 DSP 与FIFO 的接口

311 硬件电路接口

31111 DSP 与FIFO 的接口

系统中,FIFO 采用的是AL422B ,这是一款由

AverLogic 公司专门推出的视频帧存储器,它的容

量大小为384K 38bit ,其电路连接如图2所示。

此款FIFO 的容量比较大,可以完整存放由

OV7620所采集的一帧图像。FIFO 的具体工作方

式为,当系统发出采集信号,DSP 的/AWE 和/CE2

第22卷第2期

2007年4月成 都 信 息 工 程 学 院 学 报JOURNAL OF CHEN G DU UNIV ERSITY OF INFORMATION TECHNOLO GY Vol.22No.2Apr.2007

管脚都输出低电平,通过FP G A 所实现的或门,使得AL422B 的/W 管脚为低,此时FIFO 可写,图像数据由OV7620进入FIFO ;当采集完一帧图像后,DSP 的/ARE 和/CE2管脚都输出低电平,通过FP G A 所实现的或门,使得AL422B 的/R 管脚为低,此时FIFO 可读,图像数据由FIFO 进入DSP 。

31112 DSP 与SDRAM 的接口

通过外部存储器接口(EM IF )DSP 可与SDRAM 实现无缝连接,系统SDRAM 采用的是H YN IX 公司的H Y57V641620,其存储容量为431M ,连接电路如图3所示。

图3 DSP 与SDRAM 的接口DSP 的CE0为片选信号,B E02B E1为字节使能信

号,CL KM EM 为同步时钟信号,行选通信号/SDRAS ,

列选通信号/SDCAS 和写使能信号/SDWE 分别于

SDRAM 的/RAS 、/CAS 、/WE 管脚相连,DSP 的地址

线A 和数据线D 直接与SDRAM 的相连。

312 TMS 320VC 5509的DMA 控制器的特点

DMA 可独立于CPU 工作;有4个标准端口与内部DARAM 、SARAM 、外部存储器和外设相连;有一个

辅助端口用于HPI 和存储器之间的数据传输;具有6

个通道;可以设置每个通道的优先级;每个通道的传输

可以由选定事件触发;当操作完成后,DMA 控制器可

向CPU 发出中断。

313 DMA 传输

TMS320VC5509的存储空间包括统一的数据/程序空间和I/O 空间,数据空间地址用于访问存储器和内存影射寄存器。DSP5509的内部地址线为24位,但当访问数据空间时使用23位地址,并将23位地址左移一位,最低有效位置0,使得地址总线传输24位地址。故DSP 在数据空间的寻址范围为8M ,其M EMRO Y MAP 如图4所示。

图4 DSP 的MEMRO Y MAP

由图4可以看到,以CE0为片选信号的4M 容量SDRAM 占

用了DSP 数寻址空间的CE02CE1两个片区,以CE2为读写控制

信号的FIFO 始终为CE2片区的起始地址0x800000。FIFO 是作

为数据源,且地址固定不变,SDRAM 是作为数据传输的目的,其

起始地址为0x040000,且每接收一个数据单元后,地址增加1。

DMA 通道传输的目的端口和源端口由参数寄存器DMACS 2

DP 中的DST (SRC )字段来确定:当DST (SRC )

=xx00时,目的(源)端口为SARAM ;当DST (SRC )

=xx01时,目的(源)端口为DARAM ;当DST (SRC )

=xx10时,目的(源)端口为EM IF ;当DST (SRC )=xx11时,目的(源)端口为Peripheral 。DMA 通道在数据传输过程中的地址修改方式由DMACCR

寄存器中的DST (SRC )AMODE 字段来确定:

当DST (SRC )AMODE =00时,目的(源)地址为固定地址,用于单元传输;

当DST (SRC )AMODE =01时,目的(源)地址再每个单元传输完后自动增加,根据数据的位数是8位、16位还是32位,地址分别增加1、2或4。

当DST (SRC )AMODE =10时,目的(源)地址再每个单元传输完后自动增加一个索引值,索引值由单元索引寄存器DMACEI/DMACSEI 确定。

当DST (SRC )AMODE =11时,目的(源)地址再每个单元传输完后按单元索引和帧索引自动增加,索引值由单元索引寄存器DMACEI/DMACSEI 和帧索引寄存器DMACFI/DMACSFI 确定,又称为双索引。

012成 都 信 息 工 程 学 院 学 报 第22卷

4 程序加载

调用DMA库函数首先要在头文件中包含csl-dma.h文件,文件中定义了一名为DMA-Config的结构体如: typedef struct{

Uint16dmacsdp; DMA通道控制寄存器

Uint16dmaccr;DMA通道中断寄存器

Uint16dmacicr;DMA通道状态寄存器

DMA-AdrPtr dmacssal;DMA通道源起始地址(低字段)

Uint16dmacssau;DMA通道源起始地址(高字段)

DMA-AdrPtr dmacdsal;DMA通道目的地址(低字段) Uint16dmacdsau;DMA通道目的地址(高字段

) Uint16dmacen;DMA通道数据单元数量寄存器

Uint16dmacfn;DMA通道帧数寄存器

#if -DMA-DST-AND-SRC-INDEX-SU PPOR T

对于5509A,5510P G2

Uint16dmacsfi;

Uint16dmacsei;

Uint16dmacdfi;

Uint16dmacdei;

#else对于5509,5510P G1

Uint16dmacfi;DMA通道帧索引寄存器

Uint16dmacei;DMA通道单元索引寄存器

#endif

}DMA-Config;

在定义了结构体DMA-Config后,便可以在主程序中声明所需的配置: DMA-Config myconfig={

……

}

声明配置结构后,需调用DMA-open函数初始化DMA句柄:

DMA-Handle myhDma;

然后打开DMA通道0:

myhDma=DMA-open(DMA-CHA0,0);

调用DMA-config函数对DMA进行配置:

myconfig.dmacssal=

(DMA-AdrPtr)(((Uint32)(myconfig.dmacssal)<<1)

&0xFFFF);

myconfig.dmacdsal=

(DMA-AdrPtr)(((Uint32)(myconfig.dmacdsal)<<1)

0xFFFF);

配置通道:

DMA-config(myhDma,&myconfig);

调用DMA-start函数开始DMA传送:

DMA-start(myhDma);

等待DMA状态寄存器的帧状态位指示传输结束:112

第2期 马跃等:DMA控制器在DSP数据采集系统中的应用

212成 都 信 息 工 程 学 院 学 报 第22卷 while(!DMA-F GETH(myhDma,DMACSR,FRAM E)){

}

关闭句柄:

DMA-close(myhDma);

5 结束语

着重介绍了如何利用DSP的DMA控制器在系统中从FIFO向SDRAM传输数据,经实践检验,此方法结构简单、可靠性高,并实现了DSP对并行数据的高速采集,不仅在系统中得到了很好的应用,在其它需要实时数据采集系统中也有很广泛的应用前景。

参考文献:

[1] TMS320C55X Chip Support Library API User’s Guide[Z].TI Inc,2004.

[2] The TMS320VC5503/5507/5509/5510Direct Memory Access(DMA)Controller Reference Guide[Z].TI

Inc,2005.

[3] 彭启琮.TMS320VC55x系列DSP的CPU与外设[M].北京:清华大学出版社,2005.

[4] 汪春梅,孙洪波,任治刚.TMS320C5000系列DSP系统设计与开发实例[M].北京:电子工业出版社,

2004.

Application of DMA controller to DSP image collection system

MA Yue, Q IN G Lin2bo, TEN G Qi2zhi

(College of Electronics&Information Engineering,SCU,Chengdu610064,China)

Abstract:The DMA controller can transmit data among the interior memorizer,exterior memorizer and chip periph2

eral without the CPU intervention.It has comprehensive application value in the DSP system.Based on the TMS320VC5509image collection system the material demonstration for the interface circuit hardware design and the practical software code are provided with the introduction of the FIFO,SDRAM and TMS320VC5509DMA.

K ey w ords:TMS320VC5509;DMA controller;EM IF;data collection

复习思考题 第章DMA控制器 1.试说明在DMA方式时内存往外设传输数据的过程。 2.对一个DMA控制器的初始化工作包括哪些内容? 3.DMA控制器8237A什么时候作为主模块工作?什么时候作为从模块工作?在这两种情况下,各控制信号处于什么状态? 4.8237A有哪几种工作方式?各自用在什么场合? 5.什么叫DMA控制器的自动预置功能?这种功能是用得很普遍的,举一个例子说明它的使用场合。 6.用DMA控制器进行内存到内存的传输时,有什么特点? 7.DMA控制器8237A是怎样进行优先级管理的? 8.设计8237A的初始化程序。8237A的端口地址为0000-000FH,设通道0工作在块传输模式,地址加1变化,自动预置功能;通道1工作于单字节读传输,地址减1变化,无自动预置功能;通道2、通道3和通道1工作于相同方式。然后对8237A设控制命令,使DACK 为高电平有效,DREQ为低电平有效,用固定优先级方式,并启动8237A工作。9.CPU对DMA控制器的总线请求响应要比对中断请求响应快,请分析其原因。10.8237A在进行单字节方式DMA传输和块方式DMA传输时,有什么区别? 11.什么是DMA传送?DMA传送与中断方式传送的基本区别是什么? 12.8237A在实行存储器与存储器之间传输时,与存储器和外设之间的传输有什么不同?13.8237A采用压缩时序方式,试估算在最好情况下传送10KB数据需要多少时间?再试用最高效的程序衽同样数量数据的传输,大约要多少时间?(时钟都以5MHz算) 14.8237A为了在16位以上的微机系统中应用,必须设计适当的页面地址寄存器。如个人计算机中那样设计,请问: (1)如何知道什么时候该换页?如何换页? (2) 换页时应对DMA控制器作什么处理? (3) 如果通道0也需要页面地址,如何获得RA、RB的控制信号? 15.在个人计算机中8237A的通道2为什么设置成单字节传送?如果用成块传送会发生什么问题?如何解决? 16.ADSTB信号与AEN有什么不同?它们各自起什么作用? 17.一个系统需要接6个用DMA控制的外设,如何用8237A实现这个系统的连接,请画出连接图,并说明方式控制字应如何设置。如用固定优先级请列出你所设计方案中6个设备的优先级排列。 18.用简化框图形式表示一个DMA系统的基本构成,请标明DMA控制器与CPU、系统总线及外设连接的关键信号。 19.8237A上设有一个READY控制端以适应慢速存储器或外设的需要,这是否与DMA的快速传送宗旨相违背?为什么? 20.DMA操作过程中,DMA控制器将代替CPU控制系统总路线,根据它的这一任务,请列出DMA控制器必须具有的几项功能。 21.单字节传送、成组传送与请示传送三种DMA方式在传送方式、DMA请示方面有什么差别? 22.图中是一个DMA系统框图,DMA控制器是个可编程器件,外设也由一个可编程接口电路控制。请在各框图间连上必要的线,并标明它胶的名称。(附图6-55)

DMA简介(1) DMA,全称为:Direct Memory Access(即直接存储器访问),DMA 用来提供在外设和存储器之间、存储器和存储器之间的高速数据传输。当CPU 初始化这个传输动作,传输动作本身是由DMA控制器来实行和完成。DMA传输对于高效能嵌入式系统算法和网络是很重要的,因为DMA 传输方式无需CPU 直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,而是直接通过硬件为RAM 与I/O 设备开辟一条直接传送数据的通路,能使CPU 的效率大为提高。 STM32 最多有2 个DMA 控制器(DMA2 仅存在大容量产品中),DMA1 有7 个通道(如上图所示),DMA2 有5个通道。每个通道专门用来管理来自于一个或多个外设对存储器访问的请求。例如,在通道1 上有以下几个DMA请求:ADC1、TIM2_CH3、TIM4_CH1。 由上可知,每一条独立的DMA通道都对应着若干个可以产生DMA请求的置外设,这些DMA请求信号通过逻辑或后输出到对应的DMA通道上,如通道1就是由ADC1、TIM2_CH3和TIM4_CH1产生的DMA 请求信号通过逻辑或后输出到通道1上,所以每一条通道任意一个时刻只能输出一个DMA请求(由于逻辑或是只要有一个请求信号便会输出到通道上,意味着在出现两个或以上的DMA请求信号的情况下无法分别到底是哪个外设的请求,因此,我们在使用某一条通道时,应尽可能做到只有一个外设的DMA请求或者时分复用)。 仲裁器是用来协调各个DMA 通道的优先级(这里我们所说的优先级指的是DMA通道的优先级,而不是来自外设的DMA请求的优先级)。然后,再由仲裁器根据优先级来处理各个通道的 从外设(TIMx、ADC、SPIx、I2Cx 和USARTx)产生的DMA 请求,通过逻辑或输入到DMA 控制器,这就意味着同时只能有一个请求有效(从7个通道输出的请求信号只有一个有效)。外设的DMA 请求可以通过设置相应的外设寄存器中的控制位,被独立地开启或关闭。下表是DMA1 各通道一览表:

1.试说明在DMA方式时内存往外设传输数据的过程。 答:当一个接口要由内存往其输出数据时,就往DMA 控制器发一个DMA 请求;DMA 控制器接到请求以后,便往控制总线上发一个总线请求;若CPU 允许让出总线便发出一个总线允许信号;DMA 控制器接到此信号后,就将地址寄存器的内容送到地址总线上,同时往接口发一个DMA 回答信号并发一个I/O 写信号和一个内存读信号;内存接到读信号后将数据送到数据总线,I/O 写信号将数据送到接口,并撤除DMA 请求信号,于是DMA 控制器的地址寄存器的内容加1 或减1,计数器的值减1,而且撤除总线请求信号,就完成了对一个数据的DMA 输出传输。 2.对一个DMA控制器的初始化工作包括哪些内容? 答:①将数据传输缓冲区的起始地址或者结束地址送到地址寄存器中; ②将传输的字节数或字数送到计数器中。 ③通过模式寄存器设置工作方式等。 3.DMA控制器8237A什么时候作为主模块工作?什么时候作为从模块工作?在这两种情况下,各控制信号处于什么状态? 答:1.在外设向8237A 发DMA 请求,8237A 向CPU 发总线请求得到CPU 总线允许时,获得了总线控制权就作为总线主模块工作。2.当CPU 把数据送到8237A 的寄存器或者从8237A 的寄存器取出时,8237A 就象I/O接口一样作为总线的从模块工作。3.主模块工作时的控制信号:DREQx 有效,HRQ 高,HLDA 高,DACKx 有效,AEN高,IOR、MEMW 或IOW、MEMR有效,16位地址送地址总线。从模块工作时的控制信号:CS和HRQ为低,A3 ~A0 为某一确定值,IOR或IOW有效。

第十章DMA控制器8237A 1.试说明在DMA方式下,传输单个数据的全过程。 答:内存往外设传输单个数据: (1)当一个接口准备就绪,要进行DMA传输时,该接口往DMA 控制器发一个DMA请求; (2)DMA控制器采样到DRED有效电平后,若屏蔽寄存器是开放的,便往控制总线上发一个总线保持请求; (3)若CPU允许让出总线,则发回一个总线保持允许信号;(4)DMA控制器接到此信号后,就将其内部地址寄存器的内容送到地址总线上; (5)同时,DMA控制器往接口发一个DMA回答信号,并发出一个内存读信号和一个I/O写信号; (6)接口收到DMA回答信号后,撤除DMA请求信号,且内存把数据送到数据总线上; (7)接口锁存数据总线上的数据后,一般往DMA控制器回送一个准备好信号; (8)DMA控制器的地址寄存器内容加1或减1,字节计数器的值减1; (9)DMA控制器撤除总线保持请求信号,CPU收回总线控制权。这样,就完成了对一个数据的DMA输出过程。 外设往内存传输单个数据的过程: (1)当一个接口中有数据要输入时,就往DMA控制器发一个DMA 请求信号; (2)DMA控制器接到DMA请求后,(若屏蔽触发器是开放的)便往控制总线上发一个总线保持请求信号; (3)若CPU允许让出总线,则发回一个总线保持允许信号;(4)DMA控制器接到此信号后,就将其内部地址寄存器的内容送到

地址总线上; (5)同时,DMA控制器往接口发一个DMA回答信号,并发一个I /O读信号和一个内存写信号; (6)接口收到DMA回答信号后,撤除DMA请求信号,并将数据送到数据总线上; (7)内存在收到数据后,一般往DMA控制器回送一个准备好信号;(8)DMA控制器的地址寄存器内容加1或减1,字节计数器的值减1; (9)DMA控制器撤除总线保持请求信号,CPU收回总线控制权。这样,就完成了对一个数据的DMA输入过程。 2.为使DMA控制器正常工作,系统对DMA控制器进行初始化的过程分为哪两个主要方面? 答: (1) 将数据传输缓冲区的起始地址或结束地址送到地址寄存器中; (2) 将传输的字节数或字数送到计数器中。 3.8237A什么时候作为主模块工作?什么时候作为从模块工作?在这两种情况下,各控制信号处于什么状态? 答:当DMA控制器得到总线控制权,可以控制系统总线时,便成为总线主模块;当DMA控制器接受CPU对它的读写操作时,便成了总线从模块。 作总线主模块时:它会往总线上提供要访问的内存地址,地址的低八位放在A0 ~ A7上,地址的高八位放在DB0~DB7上,此时,AEN信号为有效的高电平,存储器读和I/O写有效,或者存储器写和I/O读有效。 作总线从模块时:8237A接收16位地址,用较高的12位地址产生片选信号,据此判断本片是否被选中,用低4位地址来选择内部寄存器。片选信号为有效的低电平,HRQ和AEN都为无效的低电平,I/O读

中图分类号:TP332文献标识码:A文章编号:1009-2552(2011)03-0042-05 嵌入式音频处理器中DMA控制器的设计 王俊,应忍冬 (上海交通大学电子工程系,上海200240) 摘要:高性能的DMA控制器是音视频等多媒体处理器的重要组成部分。通过分析DMA控制器在嵌入式音频处理HiPAP中担负的数据传输任务及数据特点,设计了面向AMBA AHB总线的双通道高性能的DMA控制器。在FPGA平台上的实际运行结果显示,该DMA控制器的数据传输性能比使用CPU至少提升了45%。 关键词:DMA;控制器;AHB Design of DMA controller in embedded audio processor WANG Jun,YING Ren-dong (Department of Electronic Engineering,Shanghai Jiaotong University,Shanghai200240,China) Abstract:High-performance DMA controller is the key component in multimedia processor.After the analysis for data transfer in embedded audio processor HiPAP,an AHB supported2-channel audio DMA controller is proposed in this paper.Compared with CPU,the performance of data transfer is improved by up to45%on FPGA platform. Key words:DMA;controller;AHB 0引言 对于多媒体处理而言,使用ASIC(Application Specific Integrated Circuit)编解码IP(Intellectual Property)能够高速同时低功耗地完成编解码任务,但是它们不能被修改,当音视频标准或者协议升级时,必须开发新的IP。而使用配备专用加速指令的音视频处理器,则只需要更新固件就可以完成新的任务,由于这些处理器有着很好的灵活性,因此发展非常迅速[1]。近年来,各大公司都推出了针对音频编解码的音频处理器,比如,Tensilica公司的DIA-MOND330HiFi以及ARM公司的AudioDE等。 随着处理器性能的提高,系统各模块间的数据交换成为提高系统运行速度的瓶颈[2]。使用DMA (Direct Memory Access)方式能够有效代替CPU的load/store指令。在DMA方式下,CPU只需要在数据传输之前对DMA控制器(Direct Memory Access Controller)进行少量的初始化操作,之后CPU就无需介入数据传输过程,可以和DMA并发的工作。这样,CPU的利用率得到了大幅提升[3]。 面对嵌入式音频处理器的数据传输需求,传统的通用DMA控制器并不能很好的满足。本文介绍了音频处理器HiPAP(High Performance Audio Pro-cessor)中双通道音频DMA控制器的设计与实现。1系统架构与数据传输需求 1.1音频处理器的数据传输需求 在一个包含音频处理器芯片的SoC系统中,音频处理器负责诸如编解码之类的音频处理。除此之外,系统一般还拥有负责全局控制的主处理器,通用DMA控制器和存储器等的各种外设以及连接所有模块的总线。在音频处理器的运行过程中,涉及处理器控制的数据传输可按照其特点分为两类:第一类,大数据量、较低实时性的传输。这包括在音频处理器处理前将原始码流载入音频处理器的本地存储器内,以及在处理完成后将输出数据传输至主存或者音频DAC。 收稿日期:2010-09-16 作者简介:王俊(1985-),男,硕士研究生,主要研究方向为集成电路芯片设计与验证。 — 24 —

第一讲: 第六章DMA控制器和定时/计数器 回顾:微型计算机与外部设备之间的数据传送控制方式 本讲重点:DMA的基本概念,DMA 控制器芯片8237的性能概述,内、外部结构,工作周期,工作方式,通道的优先级及数据传输速率。 讲授内容: 6. 1 DMA控制器Intel8237 一、DMA概述 我们已经介绍了微机系统中各种常用的数据输入输出方法,有程控法(包括无条件及条件传送方式)和中断法,这些方法适用于CPU与慢速及中速外设之间的数据交换。但当高速外设要与系统内存或者要在系统内存的不同区域之间,进行大量数据的快速传送时,就在一定程度上限制了数据传送的速率。以Intel8088CPU为例,CPU从内存(或外设)读数据到累加器,然后再写到外设端口(或内存)中,若包括修改内存地址,判断数据块是否传送完,Intel8088CPU(时钟接近5MHz)传送一个字节约需要几十微秒的时间,由此可大致估计出用程控及中断的方式来进行数据传送,其数据传送速率大约为每秒几十KB字节。 为了提高数据传送的速率,人们提出了直接存储器存取(DMA)的数据传送控制方式,即在一定时间段内,由DMA控制器取代CPU,获得总线控制权,来实现内存与外设或者内存的不同区域之间大量数据的快速传送。 典型的DMAC的工作电路如图6-1。DMA数据传送的工作过程大致如下: ①外设向DMAC发出DMA 传送请求。 ②DMAC通过连接到CPU 的HOLD信号向CPU提出DMA 请求。 ③CPU在完成当前总线操作 后会立即对DMA请求做出响 应。CPU的响应包括两个方面: 一方面,CPU将控制总线、数据 总线和地址总线浮空,即放弃对 这些总线的控制权;另一方面, CPU将有效的HLDA信号加到 图6-1 DMAC的工作电路 DMAC上,用此来通知DMAC,

DSP的DMA控制器与ARM的DMA控制器比较 分类:技术相关总结2009-10-17 15:18 1836人阅读评论(0) 收藏举报 工作任务c 去年,曾经使用过TI的DSP,TMS320VC5502(属于TMS320C5000系列),用过了它的DMA 功能,前段时间,又使用了STM32的DMA。现总结它们主要的区别: DSP的DMA传输的数据可以细分,一个总的传输块(BLOCK)里面,又可以分若干个帧(FRAME),每传完一帧都可以开启中断。而且在整个DMA传输期间,不管是循环模式或者是其他一次性的模式,都可以中途暂停,因为它的DMA控制器可以记录当前暂停时的传输大小,和传输地址索引,然后下次再次开启的时候,会紧接着上次中断后的地方来传输。而STM32的DMA就显得功能没那么大, 设定了传输大小后,不能再细分区域。而且传输过程中,不能暂停。缺了这些功能,其实不会影响一般使用的,只在某些特定的使用中,就显得没DSP的DMA那么方便了。 STM32的DMA控制器只有一套工作寄存器。而DSP的DMA控制器,不单单有一套工作寄存器,而且还多了一个备份寄存器,称为配置寄存器。按照其命名可以很容易的理解,工作寄存器肯定就是提高给DMA控制器使用,也就是说,当前DMA控制器传输所用的配置是由工作寄存器得来的。而配置寄存器,就是由用户配置的,该寄存器可以在任何时候,包括DMA在启用的时候,都可以配置(某些特定寄存器不能在DMA启动的时候配置,具体请参考其手册),假如使用AUTO自动初始 化模式,在完成一个BLOCK传输后,会讲配置寄存器值复制到工作寄存器,改变DMA传输参数;假如非AUTO模式,就在再次使能通道的时候进行寄存器复制。这样就带来了一个好处,DMA控制参数,可以在DMA传输的过程中,对下一次传输进行预配置,然后等传输完的时候,启用新参数继续传输。而STM32的DMA,假如DMA在启动,假如需要改变下一次传输的参数,那只能乖乖的等它将这次任务完成了,然后停止DMA,再去配置工作寄存器,再重新启动DMA。也就是说,DSP 的DMA,多了一个备份配置寄存器,带来的好处是,无需停止DMA,就可以实现传输参数的改变。 注:不管是STM32或者5502的DMA,在非循环模式下,每次传输完后,假如要传输新的数据,都需要重新配置目标地址和源地址和传输数据等参数。而且STM32还要重新给DMA配置通道。 DMA传输是“直接存储器访问”的缩写,由DMA控制器完成数据传输,不需要CPU操作,因此可节省CPU开销,传输速度快,突发操作每时钟搬移一个数据。要通过CPU搬移数据的话,CPU要先读到他的寄存器,再从寄存器写到存储器,就是流水操作总要4-8个时钟或更多,速度就差了几倍。 DSP的DMA传输的数据可以细分,一个总的传输块(BLOCK)里面,又可以分若干个帧(FRAME),每传完一帧都可以开启中断。而且在整个DMA传输期间,不管是循环模式或者是其他一次性的模式,都可以中途暂停,因为它的DMA控制器可以记录当前暂停时的传输大小,和传输地址索引,然后下次再次开启的时候,会紧接着上次中断后的地方来传输。 DMA都是为了成批传输数据的,不论单次DMA 和突发DMA。不同的是每次传输一个单元数据(比如使用32bit

使用8237A可编程DMA控制器实验目的 1、掌握8237A可编程DMA控制器和微机的接口方法。 2、学习使用8237A可编程控制器,实现数据直接快速传送的编程方法 1、实验内容 实验原理图如图5-26(见下页)所示,本实验学习使用8237A可编程DMA控制器进行RAM到RAM的数据传送方法。 实验中规定通道0为源地址,通道1为目的地址,通过设置0通道的请求寄存器产生软件请求,8237A响应这个软件请求后发出总线请求信号HRQ,图中8237HRQ直接连到8237A的HLDA上,相当于HRQ作为8237A的总线响应信号,进入DMA操作周期。 在8237A进行DMA传送时,当字节计数器减为0时,8237A的/EOP 引脚输出一个负脉冲,表示传送结束。/EOP可以作为系统的外部中断信号,通过8259A控制器使CPU 判断DMA传递是否结束。本实验中未用/EOP信号。 图中RAM 6264的地址为8000~9FFF,实验要求将RAM 6264中地址为8000~ 83FFH 的1KB数据传送到地址为9000H~93FFH的区域中去。为了验证传送的正确性,你可在源地址(8000H~83FFH)区首末几个单元填充标志字节,传送完再检查目的地址区的相应单元的标志字节是否与填入的一样。 2、实验步骤 (1)、将DMA扩展实验板按信号线的对应关系插入DVCC-8086H的Z5插座。 (2)、将DMA扩展实验板上的8237CS信号插孔和DVCC?8086H 的译码输出插孔00H-01FH相连。 (3)、打开DVCC-8086H电源,DVCC-8086H系统显示"DVCC -86H"。 (4)、运行实验程序 在系统显示"DVCC-86H"状态下,按任意键,系统显示命令提示符"-" 。 按GO键,显示器显示"1000 XX"。 输入F000 :B8C0 。 按EXEC键,显示器显示"8237-1"。 待数据传送结束,显示器显示"8237 good"。

AN2548 应用笔记 使用STM32F101xx和STM32F103xx DMA控制器 1 前言 这篇应用笔记描述了怎么使用STM32F101xx 和 STM32F103xx的直接存储器访问(DMA)控制 器。STM32F101xx和STM32F103xx的DMA控制器、Cortex TM-M3内核、高级微控制器总线架 构(AMBA)总线和存储器系统,使得STM32具有高的数据带宽,并能使用户开发出低延迟、快响 应的软件。 这篇文档也描述了怎样充分利用这些特性,以及对于不同的外设和子系统怎样保证正确的响应 时间。 在下文中STM32F101xx和STM32F103xx都记作STM32F10xxx,DMA控制器都记作DMA。 译注: 本应用笔记配套例程下载地址: https://www.doczj.com/doc/d8426632.html,/stonline/products/support/micro/files/an2548.zip 本译文的英文版下载地址为: https://www.doczj.com/doc/d8426632.html,/stonline/products/literature/an/13529.pdf

目录 1前言1 2DMA控制器3 2.1DMA的主要特性3 3性能分析5 3.1轮询优先级方案5 3.2多层结构和总线挪用5 3.3DMA延迟6 3.4数据总线带宽限制6 3.5通道优先级选择7 3.5.1应用需求7 3.5.2内部数据带宽8 4DMA编程示例9 4.1使用SPI传输获得ADC连续采样的数据9 4.2SPI直接传输实现ADC连续数据的获取9 4.3使用DMA实现GPIO快速数据传输9 2/9 参照2007年12月 AN2548 英文第2版