目录

1.设计任务及要求 (02)

2.设计原理 (02)

3. 设计过程 (02)

3.1. 设计思路 (02)

3.2. 数字钟的设计方案 (03)

3.2.1. 编码模块 (03)

3.2.2. 分频模块 (03)

3.2.3. 秒计时模块 (03)

3.2.4. 分计时模块 (03)

3.2.5. 小时计时模块 (03)

3.2.6. 报时模块 (03)

4. 源程序 (03)

4.1. 数字钟整体程序 (03)

4.2. VHDL 及波形分析 (03)

4.2.1. VHDL 程序 (03)

4.2.2. 仿真波形 (06)

5.硬件测试 (07)

5.1. 引脚设置 (07)

5.2. 配置文件下载 (08)

5.3. 硬件调试 (08)

6. 心得体会 (09)

数字钟的VHDL 设计

1. 设计任务及要求:

设计任务:设计一台能显示时、分、秒的数字钟。具体要求如下:

(1)

由实验箱上的时钟信号经分频产生秒脉冲; (2)

计时计数器用24进制计时电路; (3)

可手动校时,能分别进行时、分的校正; (4) 整点报时;

(5) 选做:可设置闹时功能,当计时计到预定时间时,扬声器发出闹铃信号,闹铃时间

为4s ,并可提前终止闹铃。

设计要求:

(6) 采用VHDL 语言描述系统功能,并在QUARTUS II 工具软件中进行仿真,下载到EDA

实验箱进行验证。

(7) 编写设计报告,要求包括方案选择、程序代码清单、调试过程、测试结果及心得体

会。

(8) 设计时间和地点:两个星期,信息楼4楼EDA 实验室。

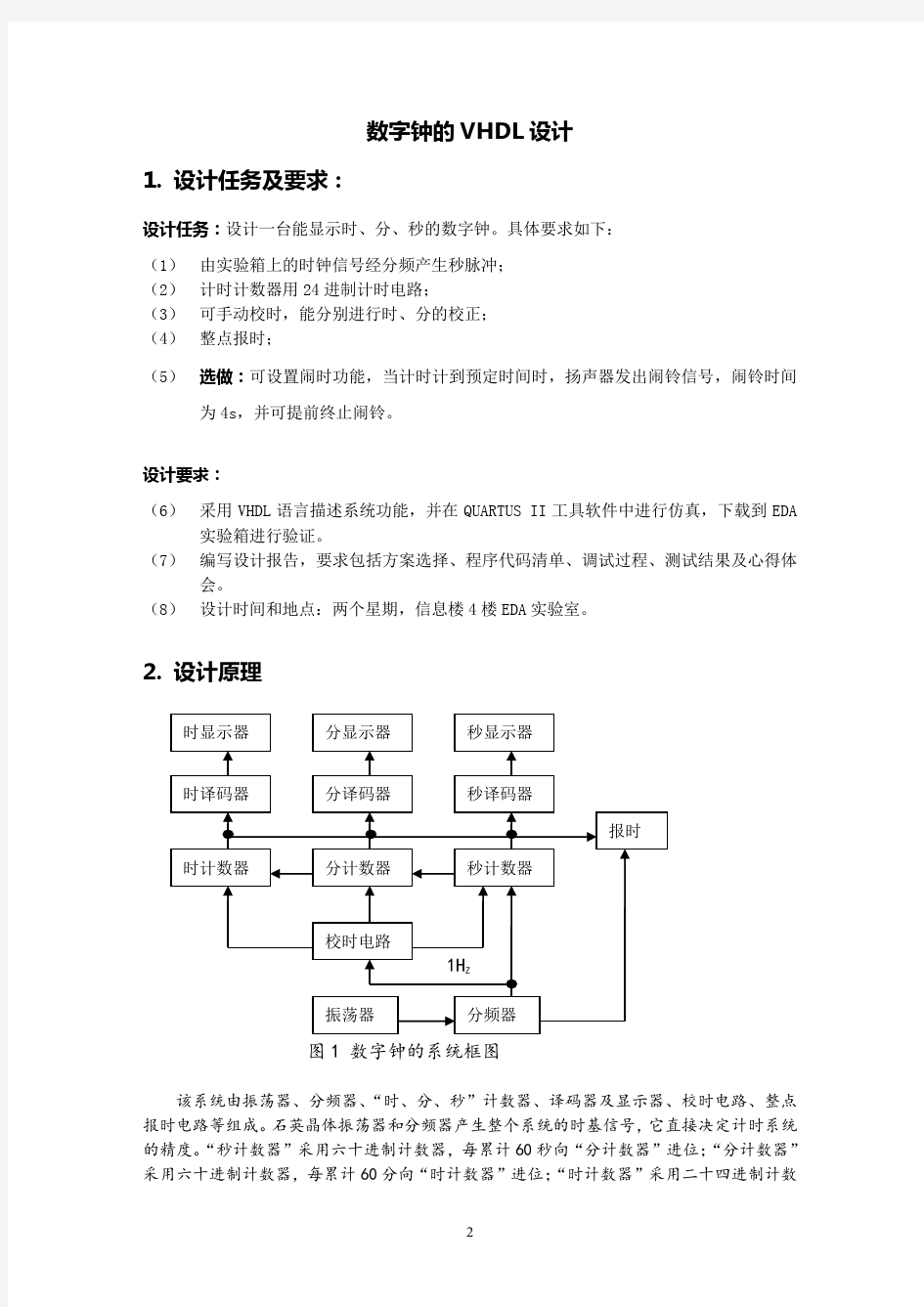

2. 设计原理

1H Z

图1 数字钟的系统框图

该系统由振荡器、分频器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路等组成。石英晶体振荡器和分频器产生整个系统的时基信号,它直接决定计时系统的精度。“秒计数器”采用六十进制计数器,每累计60秒向“分计数器”进位;“分计数器”采用六十进制计数器,每累计60分向“时计数器”进位;“时计数器”采用二十四进制计数

振荡器 分频器

校时电路

秒计数器 分计数器 分译码器 秒译码器

分显示器 秒显示器 时译码器 时计数器 时显示器 报时

器,按照“24翻1”规律计数。“时、分、秒”计数器的输出经译码器送显示器显示。校时电路用来当计时出现误差时对“时、分、秒”进行校对调整。整点报时电路是根据计时系统的输出状态产生一脉冲信号,然后去触发音频发生器实现报时。

3. 设计过程

3.1. 设计思路

时钟脉冲信号作为数字钟的时间基准,再经分频器输出标准秒脉冲。秒计数器计满60后向分计数器进位,分计数器计满60后向小时计数器进位,小时计数器是计满24后,系统自动复位重新开始计数。计数器的输出经译码电路后送到显示器显示。可以用校时电路进行校时。整点报时电路在每小时的最后50秒开始报时间隔一秒报一次时直至下一小时开始。

3.2. 数字钟的设计方案

数字钟的设计包括编码模块、分频模块、秒计时模块、分计时模块、小时计时模块和报时模块。该数字钟可以实现3个功能:计时功能、报时功能和设置时间功能。

3.2.1. 编码模块

编码模块主要是对时(sethour)、分(setmin)、秒(setsec)的设置输入。

3.2.2. 分频模块

在数字钟的设计中,外部输入时钟信号clk1的频率为8hz,其分频后的频率为clk,使其分频结果为1hz,用来提供给秒计时模块、分计时模块、小时计时模块。

3.2.3. 秒计时模块

将“秒计时脉冲”clk接信号源单元的1HZ脉冲信号,此时秒显示将从00计时到59,然后回到00,重新计时。在秒位进行计时的过程中。

秒计时器是由一个60进制的计数器构成的,具有置数和计数功能。其中rst为置数信号,当rst为1时,秒计时器置数。clk为驱动秒计时器的时钟,sec1、sec0为秒计时器的高位和低位输出。

3.2.

4. 分计时模块

分计时电路:将“分计时脉冲”clk接信号源单元的1HZ脉冲信号,此时分显示将从00计时到59,然后回到00,重新计时。在分位进行计时的过程中。分计时器是由一个60进制的计数器构成的,具有置数和计数功能。其中rst为置数信号,当rst为1时,分计时器置数。min1、min0为分计时器的高位和低位输出。

3.2.5. 小时计时模块

将“小时计时脉冲”clk接信号源单元的1HZ脉冲信号,此时小时显示将从00计时到24,然后回到00,重新计时。

时计时器是由一个24进制的计数器构成的,具有置数和计数功能。其中的rst为置数信号,当rst为1时,时计时器置数。hr1、hr0为时计时器的高位和低位输出。

3.2.6, 报时模块

当分位到59时,秒位计到51秒、53秒、55秒、57秒、59秒时报时一次,而后小时位

加1。

4. 源程序

4.1. 数字钟整体程序

整个程序分为六个部分,分别为分频部分、校时部分、秒部分、分部分、小时部分和报时部分。

4.2. VHDL程序及波形分析

4.2.1. VHDL程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity clock is

port(clk1,rst,setsec,setmin,sethour:in std_logic;

sec1,sec0,min1,min0,hr1,hr0:buffer std_logic_vector(3 downto 0);

speaker:out std_logic);

end entity;

architecture one of clock is

signal tmp,clk:std_logic;

begin

p0:process(clk) --分频注释见①

variable count :std_logic_vector(1 downto 0);

begin

if(clk1'event and clk1='1') then

if(count="10") then

count:=(others=>'0');

tmp<=not tmp;

else

count:=count+1;

end if;

end if;

end process p0;

clk<=tmp;

p1:process(clk,rst,setsec,setmin,sethour)--校时注释见②

variable s1,s0,m1,m0,h1,h0:std_logic_vector(3 downto 0);

begin

if clk'event and clk='1' then

if rst='1' then

if setsec='1'

then s0:=s0+1;

if s0="1010"

then s0:="0000";

s1:=s1+1;

if s1="0110"

then s1:="0000";

end if;

end if;

end if;

if setmin='1'

then

m0:=m0+1;

if m0="1010"

then m0:="0000";

m1:=m1+1;

if m1="0110"

then m1:="0000";

end if;

end if;

end if;

if sethour='1' then

h0:=h0+1;

if h0="1010" then

h0:="0000";

h1:=h1+1;

if h0="0100"and h1="0010"

then h0:="0000";h1:="0000";

end if;

end if;

end if;

else s0:=s0+1;--秒,分、时的计时注释见③ if s0="1010"

then s0:="0000";

s1:=s1+1;

if s1="0110"

then s1:="0000";

m0:=m0+1;

if m0="1010"

then m0:="0000";

m1:=m1+1;

if m1="0110"

then m1:="0000";

h0:=h0+1;

if h0="1010" then h0:="0000";

h1:=h1+1;

if h0="0100"and h1="0010"

then h1:="0000";h0:="0000";

end if;

end if;end if;

end if;

end if;

end if;

end if;

sec0<=s0;

sec1<=s1;

min0<=m0;

min1<=m1;

hr0<=h0;

hr1<=h1;

end if;

if clk1'event and clk1='1' then --报时注释见④

if m1="0101" and m0="1001" and s1="0101" then

if s0="0001" or s0="0011" or s0="0101" or s0="0111" or s0="1001"

then speaker<='1';

else speaker<='0';

end if;

end if;

end if;

end process;

end architecture one;

注释:

①分频模块:根据《EDA技术与VHDL》中的实验4—7《数控分频器的设计》设计,其功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,而本实验用count从00—10就使输入的时钟信号做一次翻转,从而到达了8分频的效果。

②校时功能:当将rst值1时,就可以通过外部按键对秒、分、时进行校准,setsec,setmin,sethour是分别实现校时的信号,可实现对秒、分、时的加1操作,且满足当秒计到59时分能进1,分计到59时小时能进1.

③计时部分:计时就是一个计数器,秒和分是从00到59,小时是从00到24,它们之间的计数是有前提的,即只有当秒计到59时分才能加1,分计到59时小时才能加1,当小时计时到24后,则回到00。

④报时功能:当分为59,秒到51开始每隔一秒让扬声器响一次。

4.2.2. 仿真波形

设置仿真时间为1ns,end time为50us,以使其有足够长的时间反应各个输出信号的变化。设置rst为低电平,即外部不能校时,可以看到秒低位sec0从0到9后,秒高位sec1加1,sec1从0加到5,分和小时类似。当51秒,53秒,55秒,57秒,59秒时speaker有一个高电平,即发声一次。

5. 硬件测试

5.1. 引脚设置

选择电路系统的电路模式7,引脚分配分别为:主频时钟clk1接clock2(第17引脚);setsec、setmin、sethour分别接键1、键4、键7、(PIO0、PIO3、PIO6分别对应第1、4、7脚);rst接键5(PIO4对应第5脚);sec1【3...0】由数码管2显示,分别接PIO23、PIO22、PIO21、PIO20(对应第50、49、48、47脚)、sec0【3..0】由数码管1显示,分别接PIO19、PIO18、PIO17、PIO16(对应第42、41、40、39脚);min1【3..0】由数码管5显示,分别接PIO31、PIO30、PIO29、PIO28(对应第72、71、70、69脚);min0【3..0】由数码4来显示,分别接PIO27、PIO26、PIO25、PIO24(对应第68、67、52、51脚);hr1【3..0】由数码管8显示,分别接PIO39、PIO38、PIO37、PIO36(对应第84,83、78、77脚);hr0【3..0】由数码管7显示,分别接PIO35、PIO34、PIO33、PIO32(对应第76、75、74、73脚);speaker 由D8显示,接PIO47(对应第106脚);

5.2 配置文件下载

将编译产生的SOF格式配置进FPGA中,打开编程窗和配置文件,将实验系统和并口通信线连接好,打开电源。

在菜单TOOL中选择programmer,单机下载标符start按钮,即进入对目标器件FPGA的配置下载操作。

5.3硬件调试

配置文件下载成功后,选择电路模式No.7,clock2选择8HZ。

上电后,秒满59向分进1后又从00开始计数,分满59向小时进1后从00开始计数,小时满24从00开始计数。

按键5(rst)后,计时停止,可以用键7、4、1分别对小时、分、秒进行重新设置时间数码管显示为设置的新时间,再按键5(rst)后,系统就再设置的时间上开始计数。当时间到59分51、53、55、55、59秒时,输出报时信号。

6、心得体会

实验分频部分由于在上学期学习时对这一实验的原理了解并不是很深,所以在设计分频