第一章.认识半导体和测试设备(1)

本章节包括以下内容,

●晶圆(Wafers)、晶片(Dice)和封装(Packages)

●自动测试设备(ATE)的总体认识

●模拟、数字和存储器测试等系统的介绍

●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温

度控制单元(Temperature units)

一、晶圆、晶片和封装

1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。

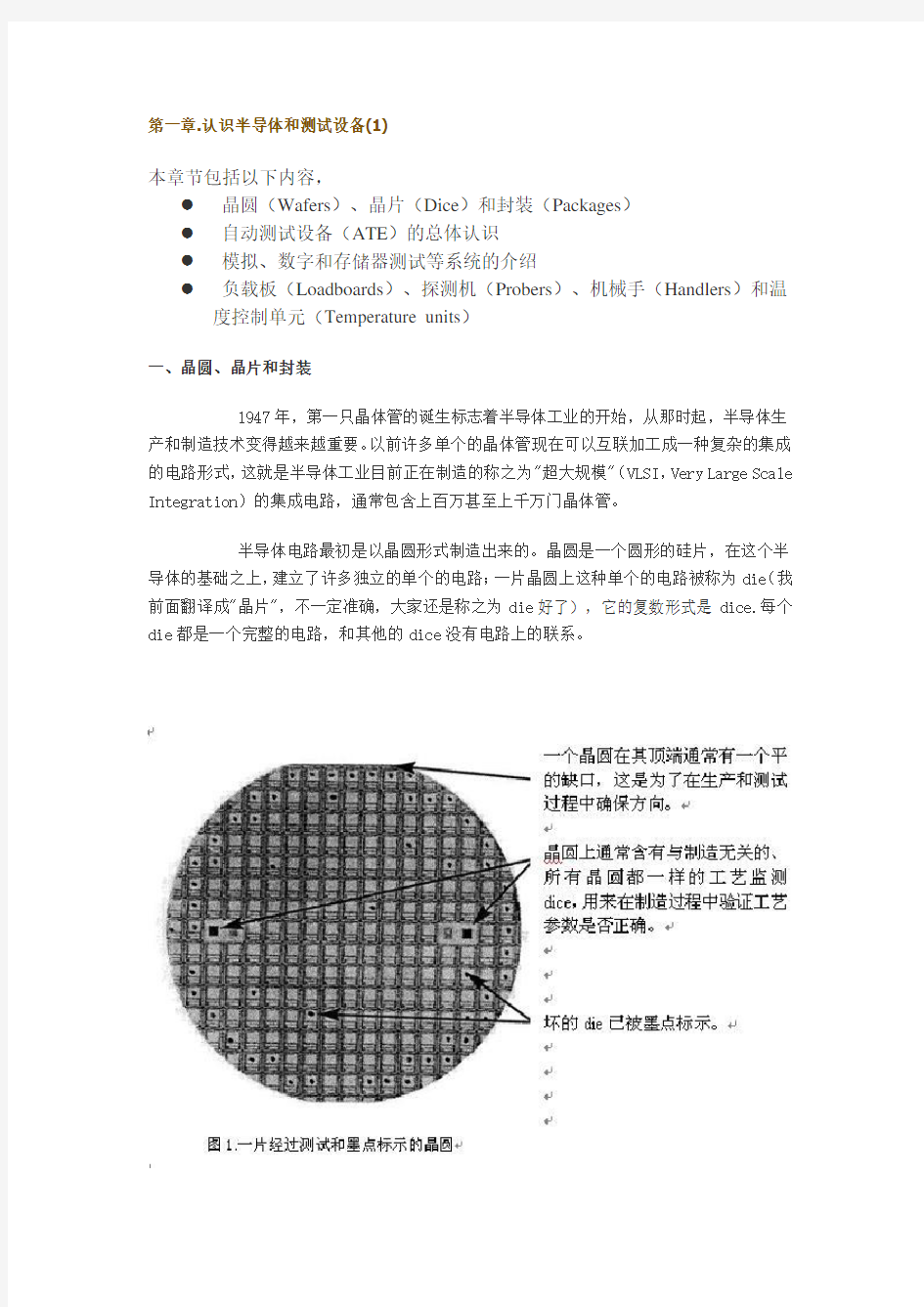

半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die 都是一个完整的电路,和其他的dice没有电路上的联系。

当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die

都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。

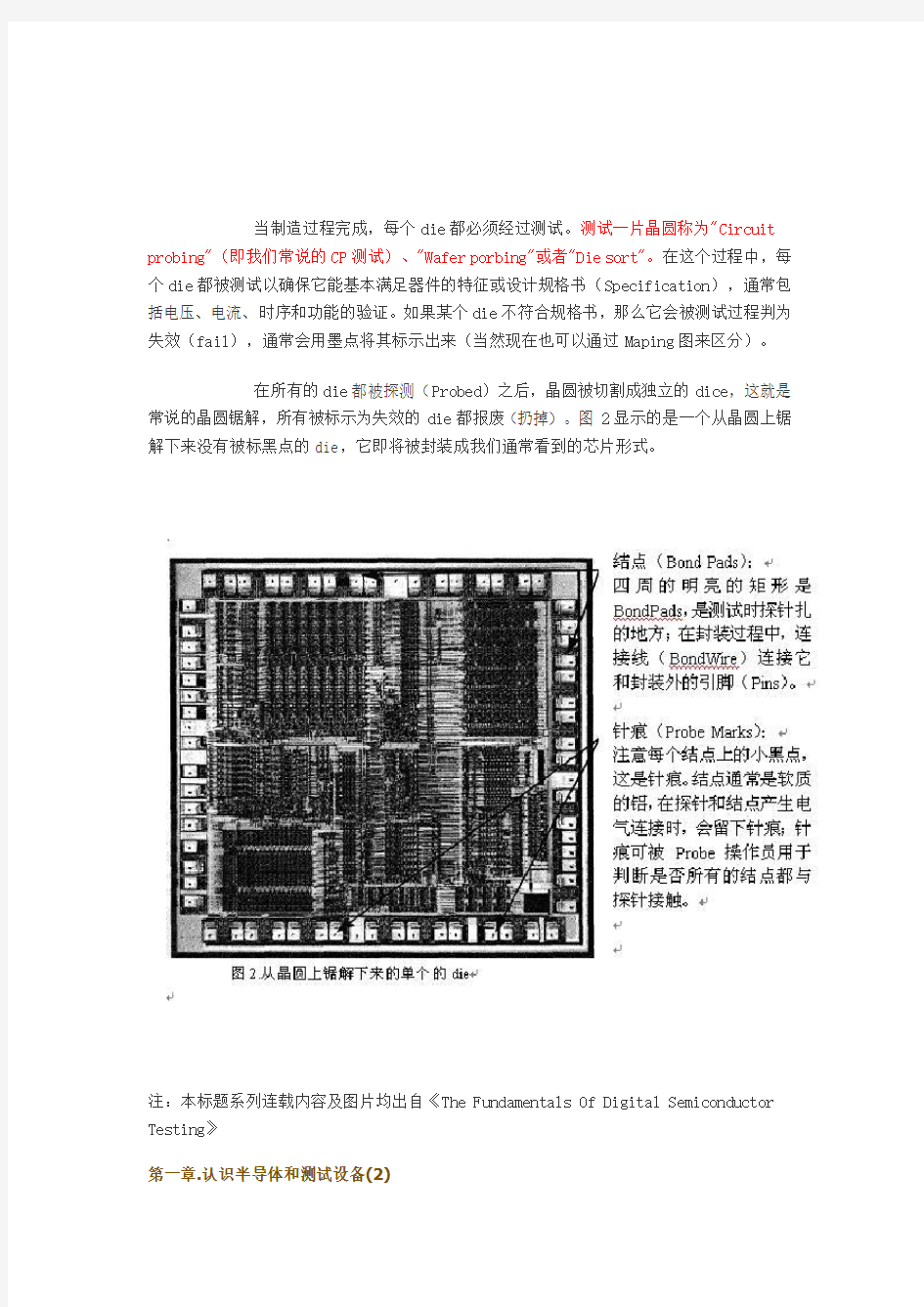

在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。

注:本标题系列连载内容及图片均出自《The Fundamentals Of Digital Semiconductor Testing》

第一章.认识半导体和测试设备(2)

在一个Die封装之后,需要经过生产流程中的再次测试。这次测试称为“Final test”(即我们常说的FT测试)或“Package test”。在电路的特性要求界限方面,FT测试通常执行比CP测试更为严格的标准。芯片也许会在多组温度条件下进行多次测试以确保那些对温度敏感的特征参数。商业用途(民品)芯片通常会经过0℃、25℃和75℃条件下的测试,而军事用途(军品)芯片则需要经过 -55℃、25℃和125℃。

芯片可以封装成不同的封装形式,图4显示了其中的一些样例。一些常用的封装形式如下表:

DIP:Dual Inline Package (dual indicates the package has pins on two sides) //双列直插封装CerDIP:Ceramic Dual Inline Package //陶瓷双列直插封装

PDIP:Plastic Dual Inline Package //塑料双列直插封装

PGA:Pin Grid Array //插针网格阵列封装

BGA:Ball Grid Array //球栅阵列封装

SOP:Small Outline Package //小外形封装, 表面贴装型封装之一

TSOP:Thin Small Outline Package

TSSOP:Thin Shrink Small Outline Package (this one is really getting small!)

SIP:Single Inline Package

SIMM:Single Inline Memory Modules (like the memory inside of a computer)

QFP:Quad Flat Pack (quad indicates the package has pins on four sides)

TQFP:Thin version of the QFP

MQFP:Metric Quad Flat Pack

MCM:Multi Chip Modules (packages with more than 1 die (formerly called hybrids)

第一章.认识半导体和测试设备(3)

二、自动测试设备

随着集成电路复杂度的提高,其测试的复杂度也随之水涨船高,一些器件的测试成本甚至占到了芯片成本的大部分。大规模集成电路会要求几百次的电压、电流和时序的测试,以及百万次的功能测试步骤以保证器件的完全正确。要实现如此复杂的测试,靠手工是无法完成的,因此要用到自动测试设备(ATE,Automated Test Equipment)。

ATE是一种由高性能计算机控制的测试仪器的集合体,是由测试仪和计算机组合而成的测试系统,计算机通过运行测试程序的指令来控制测试硬件。测试系统最基本的要求是可以快速且可靠地重复一致的测试结果,即速度、可靠性和稳定性。为保持正确性和一致性,测试系统需要进行定期校验,用以保证信号源和测量单元的精度。

当一个测试系统用来验证一片晶圆上的某个独立的Die的正确与否,需要用ProbeCard来实现测试系统和Die之间物理的和电气的连接,而ProbeCard和测试系统内部的测试仪之间的连接则通过一种叫做“Load board”或“Performance board”的接口电路板来实现。在CP测试中,Performance board和Probe card一起使用构成回路使电信号得以在测试系统和Die之间传输。

当Die封装出来后,它们还要经过FT测试,这种封装后的测试需要手工将一个个这些独立的电路放入负载板(Load board)上的插座(Socket)里,这叫手工测试(hand test)。一种快速进行FT测试的方法是使用自动化的机械手(Handler),机械手上有一种接触装置实现封装引脚到负载板的连接,这可以在测试机和封装内的Die之间提供完整的电路。机械手可以快速的抓起待测的芯片放入测试点(插座),然后拿走测试过的芯片并根据测试pass/fail的结果放入事先定义好的相应的Bin区。

三、半导体技术

有一系列的方法被用来生产和制造数字半导体电路,这些方法称为半导体技术或工艺,常用的技术或工艺包括:TTL (Transistor-Transistor Logic a.k.a. bipolar logic), ECL (Emitter Coupled Logic), SOS (Silicon on Sapphire), and CMOS (Complimentary Metal-Oxide Semiconductor)。不管什么技术或工艺,出来的产品都要经过测试,这里我们关注数字TTL和CMOS电路。

第一章.认识半导体和测试设备(4)

四、数字和模拟电路

过去,在模拟和数字电路设计之间,有着显著的不同。数字电路控制电子信号,表现为逻辑电平“0”和“1”,它们被分别定义成一种特殊的电压分量,所有有效的数字电路数据都用它们来表示,每一个“0”或“1”表示数据的一个比特(bit)位,任何数值都可以由按照一定顺序排列的“0”“1”比特位组成的二进制数据来表示,数值越大,需要的比特位越多。每8个比特一组构成一个Byte,数字电路中的数据经常以Byte为单位进行处理。

不同于数字信号的“0”“1”界限分明(离散),模拟电路是连续的——在任何两个信号电平之间有着无穷的数值。模拟电路可以使用电压或电流来表示数值,我们常见的也是最常用的模拟电路实例就是运算放大器,简称运放。

为帮助理解模拟和数字电路数值的基本差别,我们可以拿时钟来比方。“模拟”时钟上的指针连续地移动,因此所有的任一时间值可以被观察者直接读出,但是所得数值的准确度或者说精度取决于观察着认知的程度。

而在“数字”时钟上,只有最小增量以上的值才能被显示,而比最小增量小的值则无法显示。如果有更高的精度需求,则需要增加数据位,每个新增的数据位表示最小的时间增量。

有的电路里既有数字部分也有模拟部分,如AD转换器(ADC)将模拟信号转换成数字信号,DA转换器(DAC)则相反,我们称之为“混合信号电路”(Mixed Signal Devices)。另一种描述这种混合电路的方法则基于数字部分和模拟部分占到电路的多少:数字部分占大部分而模拟部分所占比例较少归于数字电路,反之则归于模拟电路。

第一章.认识半导体和测试设备(5)

五、测试系统的种类

一般认为测试系统都是通用的,其实大部分测试系统的设计都是面向专门类型的集成电路,这些专门的电路包括:存储器、数字电路、模拟电路和混合信号电路;每种类型下还可以细分成更多种类,我们这里只考虑这四种类型。

5.1存储器件类

我们一般认为存储器是数字的,而且很多DC测试参数对于存储类和非存储类的数字器件是通用的,虽然如此,存储器的测试还是用到了一些独特的功能测试过程。带内存的自动测试系统使用一种算法模式生成器(APG,algorithmic pattern generator)去生成功能测试模型,使得从

硬件上生成复杂的功能测试序列成为可能,这样我们就不用把它们当作测试向量来保存。存储器测试的一些典型模型包括:棋盘法、反棋盘法、走0、走1、蝶形法,等等…… APG在器件的每次测试时生成测试模型,而不带内存的测试系统将预先生成的模型保存到向量存储区,然后每次测试时从中取出数据。存储器测试通常需要很长的测试时间去运行所要求的测试模型,为了减少测试成本,测试仪通常同时并行测试多颗器件。

5.2模拟或线形器件类

模拟器件测试需要精确地生成与测量电信号,经常会要求生成和测量微伏级的电压和纳安级的电流。相比于数字电路,模拟电路对很小的信号波动都很敏感,DC测试参数的要求也和数字电路不一样,需要更专业的测试仪器设备,通常会按照客户的选择在设计中使用特殊的测试仪器甚至机架。模拟器件需要测试的一些参数或特性包括:增益、输入偏移量的电压和电流、线性度、通用模式、供电、动态响应、频率响应、建立时间、过冲、谐波失真、信噪比、响应时间、窜扰、邻近通道干扰、精度和噪声。

5.3混合信号器件类

混合信号器件包括数字电路和模拟电路,因此需要测试系统包含这两部分的测试仪器或结构。混合信号测试系统发展为两个系列:大部分数字电路测试结构、少量模拟测试结构的系列,被设计成用于测试以数字电路为主的混合信号器件,它能有效地进行DC参数测试和功能测试,但是仅支持少量的模拟测试;大部分模拟电路测试结构、少量数字测试结构的系列,相反,能够精确地测试模拟参数而在功能测试上稍逊风骚。

5.4数字电路器件类

仅含有数字逻辑的电路器件可使用数字电路测试系统来完成测试,这些测试系统之间在价格、性能、尺寸、可选项上有着明显的不同。

低端的测试机被用来测试低价格或者低性能的低端产品,通常是些管脚少、复杂度低的器件;一般运行于低于20MHz的时钟频率,且只能存储少量的测试向量;用于小规模(SSI)或中规模(MSI)集成电路的测试。

高端的测试机则是速度非常快(时钟频率高)、测试通道非常多的测试系统;时钟频率通常会达到400MHz,并能提供1024个测试通道;拥有高精度的时钟源和百万bit位的向量存储器。它们被用于验证新的超大规模(VLSI)集成电路,但是昂贵的成本阻碍了他们用于生产测试。

而半导体测试工业普遍使用的是中高端的测试设备,它们拥有较好的性价比,在对测试成本非常敏感的半导体测试行业,这无疑是非常重要的。这类测试设备多运行在50-100MHz,提供256个测试通道,通常带有一些可选的配置。

为了控制测试成本,谨慎地选择能满足器件测试需求的测试设备是非常重要的,选择功能相对于我们器件的测试要求过于强大的测试系统会使得我们的测试成本居高不下,而相反的选择会造成测试覆盖率不够;找到设备功能和成本之间的平衡是测试成本控制本质的要求。

第一章.认识半导体和测试设备(6)

六.测试负载板(LoadBoard)

测试负载板是连接测试设备的测试头和被测器件物理和电路接口,被固定在针测台(Probe)、机械手(Handler)或者其他测试硬件上,其上的布线连接测试机台内部信号测试卡的探针和被测器件的管脚。

在CP测试中,负载板连接ProbeCard;在手工测试中,我们将Socket固定在负载板上;而在FT的生产测试中,我们将其连接到Handler. 因为测试机在物理和电气上需要与多种类型的设备连接、锁定,因而Loadboard的类型和款式也是多种多样。

测试高速或者大功率的器件需要定制的Loadboard,为保证信号完整性,这种高性能的定制电路板必须完成阻抗匹配——这对于布局、布线及线长、线宽等都有特殊要求,因此通常需要数月的时间设计制作,并且价格非常昂贵。

七.探针卡(ProbeCard)

探针卡在CP测试用于连接测试机电路和Die上的Pad,通常作为Loadboard的物理接口,在某些情况下ProbeCard通过插座或者其它接口电路附加到Loadboard上。

测试机的信号通过弹簧针(pogo pins)连接到ProbeCard底部的Pad上,再由ProbeCard上的布线通往被测的Die上。

本章节我们来说说最基本的测试——开短路测试(Open-Short Test),说说测试的目的和方法。 一.测试目的 Open-Short Test也称为ContinuityTest或Contact Test,用以确认在器件测试时所有的信号引脚都与测试系统相应的通道在电性能上完成了连接,并且没有信号引脚与其他信号引脚、电源或地发生短路。 测试时间的长短直接影响测试成本的高低,而减少平均测试时间的一个最好方法就是尽可能早地发现并剔除坏的芯片。Open-Short测试能快速检测出DUT是否存在电性物理缺陷,如引脚短路、bond wire缺失、引脚的静电损坏、以及制造缺陷等。 另外,在测试开始阶段,Open-Short测试能及时告知测试机一些与测试配件有关的问题,如ProbeCard或器件的Socket没有正确的连接。 二.测试方法 Open-Short测试的条件在器件的规格数或测试计划书里通常不会提及,但是对大多数器件而言,它的测试方法及参数都是标准的,这些标准值会在稍后给出。 基于PMU的Open-Short测试是一种串行(Serial)静态的DC测试。首先将器件包括电源和地的所有管脚拉低至“地”(即我们常说的清0),接着连接PMU到单个的DUT 管脚,并驱动电流顺着偏置方向经过管脚的保护二极管——一个负向的电流会流经连接到地的二极管(图3-1),一个正向的电流会流经连接到电源的二极管(图3-2),电流的大小在100uA到500uA之间就足够了。大家知道,当电流流经二极管时,会在其P-N结上引起大约0.65V的压降,我们接下来去检测连接点的电压就可以知道结果了。 既然程序控制PMU去驱动电流,那么我们必须设置电压钳制,去限制Open管脚引起的电压。Open-Short测试的钳制电压一般设置为3V——当一个Open的管脚被测试到,它的测试结果将会是3V。 串行静态Open-Short测试的优点在于它使用的是DC测试,当一个失效(failure)发生时,其准确的电压测量值会被数据记录(datalog)真实地检测并显示出来,不管它是Open引起还是Short导致。缺点在于,从测试时间上考虑,会要求测试系统对DUT的每个管脚都有相应的独立的DC测试单元。对于拥有PPPMU结构的测试系统来说,这个缺点就不存在了。 当然,Open-Short也可以使用功能测试(Functional Test)来进行,我会在后面相应的章节提及。

更多企业学院: 《中小企业管理全能版》183套讲座+89700份资料 《总经理、高层管理》49套讲座+16388份资料 《中层管理学院》46套讲座+6020份资料 《国学智慧、易经》46套讲座 《人力资源学院》56套讲座+27123份资料 《各阶段员工培训学院》77套讲座+ 324份资料 《员工管理企业学院》67套讲座+ 8720份资料 《工厂生产管理学院》52套讲座+ 13920份资料 《财务管理学院》53套讲座+ 17945份资料 《销售经理学院》56套讲座+ 14350份资料 《销售人员培训学院》72套讲座+ 4879份资料 第一章.认识半导体和测试设备(1) 本章节包括以下内容, 晶圆(Wafers)、晶片(Dice)和封装(Packages) 自动测试设备(ATE)的总体认识

模拟、数字和存储器测试等系统的介绍 负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温度控制单元(Temperature units) 一、晶圆、晶片和封装 1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。 半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一个完整的电路,和其他的dice没有电路上的联系。 当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。 在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。

第一章 半导体器件基础 ⒈ 讨论题与思考题 ⑴ PN 结的伏安特性有何特点? ⑵ 二极管是非线性元件,它的直流电阻和交流电阻有何区别?用万用表欧姆档测量的二极管电阻属于哪一种?为什么用万用表欧姆档的不同量程测出的二极管阻值也不同? ⑶ 硅二极管和锗二极管的伏安特性有何异同? ⑷ 在结构上,三极管是由两个背靠背的PN 结组成的,那么,三极管与两只对接的二极管有什么区别? ⑸ 三极管是由两个背靠背的PN 结组成的,由很薄的基区联系在一起。那么,三极管的发射极和集电极是否可以调换使用? ⑹ 场效应管的性能与双极型三极管比较有哪些特点? ⒉ 作业题 题1.1 在硅本征半导体中掺入施主杂质,其浓度为3 17d cm 10 =N ,分别求出在250K 、300K 、350K 时电子和空穴的浓度。 题 1.2 若硅PN 结的317a cm 10 =N ,3 16d cm 10=N ,求T =300K 时PN 结的内建电位差。 题1.3 流过硅二极管的电流I D =1mA 时,二极管两端压降U D =0.7V ,求电流I D =0.1mA 和10mA 时,二极管两端压降U D 分别为多少? 题1.4 电路如图题1.4中二极管是理想的,t U u ωsin m i ?=: ① 画出该电路的传输特性; ② 画出输出电压波形。 题图 1.4 题1.5 题图 1.5中二极管是理想的,分别求出题图1.5(a)、(b)中电压U 和电流I 的值。 (a) (b) 题图1.5 题1.6 在图题1.6所示电路中,取5-V认识半导体和测试设备

认识半导体和测试设备 本章节包括以下内容, ●晶圆(Wafers)、晶片(Dice)和封装(Packages) ●自动测试设备(ATE)的总体认识 ●模拟、数字和存储器测试等系统的介绍 ●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温 度控制单元(Temperature units) 一、晶圆、晶片和封装 1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。 半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die 都是一个完整的电路,和其他的dice没有电路上的联系。

当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die 都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。 在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。 注:本标题系列连载内容及图片均出自《The Fundamentals Of Digital Semiconductor Testing》 第一章.认识半导体和测试设备(2)

第一章 半导体器件基础测试题(高三) 姓名 班次 分数 一、选择题 1、N 型半导体是在本征半导体中加入下列 ___________ 物质而形成的。 A 、电子; B 、空穴; C 、三价元素; D 、五价元素。 2、在掺杂后的半导体中,其导电能力的大小的说法正确的是 A 、掺杂的工艺; B 、杂质的浓度: C 、温度; D 、晶体的缺陷。 3、晶体三极管用于放大的条件,下列说法正确的是 _______________ 。 A 、发射结正偏、集电结反偏; B 、发射结正偏、集电结正偏; C 、发射结反偏、集电结正偏; D 、发射结反偏、集电结反偏; 4、晶体三极管的截止条件,下列说法正确的是 _____________________ 。 A 、发射结正偏、集电结反偏; B 、发射结正偏、集电结正偏; C 、发射结反偏、集电结正偏; D 、发射结反偏、集电结反偏; 5、晶体三极管的饱和条件,下列说法正确的是 A 、发射结正偏、集电结反偏; C 、发射结反偏、集电结正偏; 6、理想二极管组成的电路如下图所示,其 A 、一 12V ; B 、一 6V ; C 、+6V ; D 、+12V 。 7、要使普通二极管导通,下列说法正确的是 __________________ 。 A 、运用它的反向特性; B 、锗管使用在反向击穿区; C 、硅管使用反向区域,而锗管使用正向区域; D 、都使用正向区域。 8、对于用万用表测量二极管时,下列做法正确的是 _______________________ A 、 用万用表的R X 100或R X 1000的欧姆,黑棒接正极,红棒接负极,指针偏转; B 、 用万用表的R X 10K 的欧姆,黑棒接正极,红棒接负极,指针偏转; C 、 用万用表的R X 100或R X 1000的欧姆,红棒接正极,黑棒接负极,指针偏转; D 、用万用表的R X 10,黑棒接正极,红棒接负极,指针偏转; 9、电路如下图所示,则 A 、B 两点的电压正确的是 ________________ B 、发射结正偏、集电结正偏; D 、发射结反偏、集电结反偏; AB 两端的电压是 _____________

半导体C-V测量基础 作者:Lee Stauffer 时间:2009-07-29 来源:吉时利仪器公司 C-V测量为人们提供了有关器件和材料特征的大量信息 通用测试 电容-电压(C-V)测试广泛用于测量半导体参数,尤其是MOSCAP和MOSFET结构。此外,利用C-V测量还可以对其他类型的半导体器件和工艺进行特征分析,包括双极结型晶体管(BJT)、JFET、III-V族化合物器件、光伏电池、MEMS器件、有机TFT显示器、光电二极管、碳纳米管(CNT)和多种其他半导体器件。 这类测量的基本特征非常适用于各种应用和培训。大学的研究实验室和半导体厂商利用这类测量评测新材料、新工艺、新器件和新电路。C-V测量对于产品和良率增强工程师也是极其重要的,他们负责提高工艺和器件的性能。可靠性工程师利用这类测量评估材料供货,监测工艺参数,分析失效机制。 采用一定的方法、仪器和软件,可以得到多种半导体器件和材料的参数。从评测外延生长的多晶开始,这些信息在整个生产链中都会用到,包括诸如平均掺杂浓度、掺杂分布和载流子寿命等参数。在圆片工艺中,C-V测量可用于分析栅氧厚度、栅氧电荷、游离子(杂质)和界面阱密度。在后续的工艺步骤中也会用到这类测量,例如光刻、刻蚀、清洗、电介质和多晶硅沉积、金属化等。当在圆片上完全制造出器件之后,在可靠性和基本器件测试过程中可以利用C-V测量对阈值电压和其他一些参数进行特征分析,对器件性能进行建模。 半导体电容的物理特性 MOSCAP结构是在半导体制造过程中形成的一种基本器件结构(如图1所示)。尽管这类器件可以用于真实电路中,但是人们通常将其作为一种测试结构集成在制造工艺中。由于这种结构比较简单而且制造过程容易控制,因此它们是评测底层工艺的一种方便的方法。

? 第一章.认识半导体和测试设备(1) 本章节包括以下内容, ●晶圆(Wafers)、晶片(Dice)和封装(Packages) ●自动测试设备(ATE)的总体认识

●模拟、数字和存储器测试等系统的介绍 ●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温 度控制单元(Temperature units) 一、晶圆、晶片和封装 1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。 半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一个完整的电路,和其他的dice没有电路上的联系。 当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。 在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。

第一章半导体器件基础 1.试求图所示电路的输出电压Uo,忽略二极管的正向压降和正向电阻。 解: (a)图分析: 1)若D1导通,忽略D1的正向压降和正向电阻,得等效电路如图所示,则U O=1V,U D2=1-4=-3V。即D1导通,D2截止。 2)若D2导通,忽略D2的正向压降和正向电阻,得等效电路如图所示,则U O=4V,在这种情况下,D1两端电压为U D1=4-1=3V,远超过二极管的导通电压,D1将因电流过大而烧毁,所以正常情况下,不因出现这种情况。 综上分析,正确的答案是U O= 1V。 (b)图分析: 1.由于输出端开路,所以D1、D2均受反向电压而截止,等效电路如图所示,所以U O=U I=10V。

2.图所示电路中, E 解: (a)图 当u I<E时,D截止,u O=E=5V; 当u I≥E时,D导通,u O=u I u O波形如图所示。 u I ωt 5V 10V uo ωt 5V 10V (b)图 当u I<-E=-5V时,D1导通D2截止,uo=E=5V; 当-E<u I<E时,D1导通D2截止,uo=E=5V; 当u I≥E=5V时,uo=u I 所以输出电压u o的波形与(a)图波形相同。 5.在图所示电路中,试求下列几种情况下输出端F的电位UF及各元件(R、DA、DB)中通过的电流:( 1 )UA=UB=0V;( 2 )UA= +3V,UB = 0 V。( 3 ) UA= UB = +3V。二极管的正向压降可忽略不计。 解:(1)U A=U B=0V时,D A、D B都导通,在忽略二极管正向管压降的情况下,有:U F=0V mA k R U I F R 08 .3 9.3 12 12 = = - = 第一章.认识半导体和测试设备(1) 本章节包括以下内容, ●晶圆(Wafers)、晶片(Dice)和封装(Packages) ●自动测试设备(ATE)的总体认识 ●模拟、数字和存储器测试等系统的介绍 ●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温 度控制单元(Temperature units) 一、晶圆、晶片和封装 1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。 半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一个完整的电路,和其他的dice没有电路上的联系。 当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。 在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。 注:本标题系列连载内容及图片均出自《The Fundamentals Of Digital Semiconductor Testing》 半导体测试技术实践总结报告 一、实践目的 半导体测试技术及仪器集中学习是在课堂结束之后在实习地集中的实践性教学,是各项课间的综合应用,是巩固和深化课堂所学知识的必要环节。学习半导体器件与集成电路性能参数的测试原理、测试方法,掌握现代测试设备的结构原理、操作方法与测试结果的分析方法,并学以致用、理论联系实际,巩固和理解所学的理论知识。同时了解测试技术的发展现状、趋势以及本专业的发展现状,把握科技前进脉搏,拓宽专业知识面,开阔专业视野,从而巩固专业思想,明确努力方向。另外,培养在实际测试过程中发现问题、分析问题、解决问题和独立工作的能力,增强综合实践能力,建立劳动观念、实践观念和创新意识,树立实事求是、严肃认真的科学态度,提高综合素质。 二、实践安排(含时间、地点、内容等) 实践地点:西安西谷微电子有限责任公司 实践时间:2014年8月5日—2014年8月15日 实践内容:对分立器件,集成电路等进行性能测试并判定是否失效 三、实践过程和具体内容 西安西谷微电子有限责任公司专业从事集成电路测试、筛选、测试软硬件开发及相关技术配套服务,测试筛选使用标准主要为GJB548、GJB528、GJB360等。 1、认识半导体及测试设备 在一个器件封装之后,需要经过生产流程中的再次测试。这次测试称为“Final test”(即我们常说的FT测试)或“Package test”。在电路的特性要求界限方面,FT测试通常执行比CP测试更为严格的标准。芯片也许会在多组温度条件下进行多次测试以确保那些对温度敏感的特征参数。商业用途(民品)芯片通常会经过0℃、25℃和75℃条件下的测试,而军事用途(军品)芯片则需要经过-55℃、25℃和125℃。 芯片可以封装成不同的封装形式,图4显示了其中的一些样例。一些常用的封装形式如下表: DIP: Dual Inline Package (dual indicates the package has pins on two sides) 双列直插式 CerDIP:Ceramic Dual Inline Package 陶瓷 PDIP: Plastic Dual Inline Package 塑料 PGA: Pin Grid Array 管脚阵列 学校代码: 学号: HENAN INSTITUTE OF ENGINEERING 文献综述 题目仓储温湿度报警系统的设计 学生姓名 专业班级电气工程及其自动化二班 学号 系(部)电气信息工程系 指导教师(职称)蒋威(讲师) 完成时间 2011年 3 月 1日 仓储温湿度报警系统的设计综述 摘要:为保证日常工作的顺利进行,首要问题是加强仓库内温度与湿度的监测 工作,并及时报警提示。本文根据粮仓环境测试的特点,应用现代检测理论,对温室的温度、湿度等环境因子进行自动检测,并实现报警功能,首先介绍了粮仓自动监测系统的发展背景及现状,指出在控制监测方面存在的问题和需要进一步深入探讨、研究的各个方面。 关键词:粮仓、单片机、监测、传感器 目前,关于这类监测系统的研究,国内外公开发表的文献不多,下面是关于 单片机自动监测的一些主要文献: 文献[1] 这本书从应用角度出发,精选了国内外最新流行的智能仪器与数据采集系统中的一些有特色、功能很强的新型集成电路20多类100余种。内容涉及仪用放大器,运算放大器,隔离放大器,变送器,A/D、 D/A变换器, LED、LCD驱动器,看门狗定时器,UP电源监控器,数字电位器,闪烁存储器,实时时钟等器件。所优选的每一种器件除阐述其基本功能、电路特点、性能参数和管脚说明之外,更突出器件的使用方法和应用电路。对智能仪器设计、数据采集、自动控制、数字通信和计算机接口这部分设计具有很高的使用和参考价值。 文献[2] 这本书是"单片机应用技术丛书"中专门介绍单片机应用系统软件 设计的一本著作。书中总结了作者多年来在80C51系列单片机应用系统软件设计 中的实践经验,归纳出一整套应用程序设计的方法和技巧。在内容安排上,不仅 有实现功能要求的应用程序设计步骤、子程序、监控程序及常用功能模块设计方法,还以较大篇幅介绍了提高系统可靠性的抗干扰设计和容错设计技术以及程序测试的正确思想方法。附录中向读者提供了完整的系统程序设计样本和经过多年使用考验的定点运算子程序库与浮点运算子程序库的程序文本、注释及使用方法。对于本次设计主要参考的是应用程序设计步骤、子程序、监控程序及常用功能模块设计方法这一部分的内容。 文献[3] 提出MCS-51系列单片机应用系统的构成和设计方法。详细地阐述 了应用系统的前向通道(传感器通道接口)、后向通道(伺服驱动、控制通道接 口)、人机对话通道和相互通道(单片机应用系统之间的通信接口)的结构设计、 第一章.认识半导体和测试设备(1 本章节包括以下内容, ●晶圆(Wafers)、晶片(Dice)和封装(Packages) ●自动测试设备(ATE)的总体认识 ●模拟、数字和存储器测试等系统的介绍 ●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温度控制单元(Temperature units) 一、晶圆、晶片和封装 1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。 半导体电路最初是以晶圆形式制造出来的。晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die (我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一个完整的电路,和其他的dice没有电路上的联系。 当制造过程完成,每个die都必须经过测试。测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。在这个过程中,每个die都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、 电流、时序和功能的验证。如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。 在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。图2显示的是一个从晶圆上锯解下来没有被标黑点的die,它即将被封装成我们通常看到的芯片形式。 注:本标题系列连载内容及图片均出自《The Fundamentals Of Digital Semiconductor Testing》 第一章.认识半导体和测试设备(2 在一个Die封装之后,需要经过生产流程中的再次测试。这次测试称为“Final test”(即我们常说的FT测试)或“Package test”。在电路的特性要求界限方面,FT测试通常执行比CP测试更为严格的标准。芯片也许会在多组温度条件下进行多次测试以确保那些对温度敏感的特征参数。商业用途(民品)芯片通常会经过0℃、25℃和75℃条件下的测试,而军事用途(军品)芯片则需要经过 -55℃、25℃和125℃。 第一章半导体器件基础测试题(高三) 姓名班次分数 一、选择题 1、N型半导体是在本征半导体中加入下列____________ 物质而形成的。 A、电子; B、空穴; C、三价元素; D、五价元素。 2、在掺杂后的半导体中,其导电能力的大小的说法正确的是 ________________ 。 A、掺杂的工艺; B、杂质的浓度: C、温度; D、晶体的缺陷。 3、晶体三极管用于放大的条件,下列说法正确的是 A、发射结正偏、集电结反偏; C、发射结反偏、集电结正偏; 4、晶体三极管的截止条件,下列说法正确的是 A、发射结正偏、集电结反偏; C、发射结反偏、集电结正偏; 5、晶体三极管的饱和条件,下列说法正确的是 A、发射结正偏、集电结反偏; C、发射结反偏、集电结正偏; 9、电路如下图所示,则A、B两点的电压正确 的是 A、U A=3.5V , U B=3.5V , D 截止; B、发射结正偏、集电结正偏; D、发射结反偏、集电结反偏; B、发射结正偏、集电结正偏; D、发射结反偏、集电结反偏; B、发射结正偏、集电结正偏; D、发射结反偏、集电结反偏; 6、理想二极管组成的电路如下图所示,其AB两端的电压是 A、一12V ; C、+6V ;B、一6V ; D、 7、要使普通二极管导通,下列说法正确的是 A、运用它的反向特性; C、硅管使用反向区域,而锗管使用正向区域; 锗管使用在反向击穿区; D、都使用正向区 8、对于用万用表测量二极管时,下列做法正确的是 A、用万用表的 B、用万用表的 C、用万用表的 D、用万用表的R X 100 R X 10K R X 100 R X 10 , 或R X 1000的欧姆,黑棒接正极,红棒接负极,指针偏转; 的欧姆,黑棒接正极,红棒接负极,指针偏转; 或R X 1000的欧姆,红棒接正极,黑棒接负极,指针偏转; 黑棒接正极,红棒接负极,指针偏转; 半导体测试设备项目 可研报告 规划设计/投资方案/产业运营 半导体测试设备项目可研报告 半导体测试设备主要包括探针台、分选机、测试机等。其中测试功能由测试机实现,而探针台和分选机实现的则是机械功能,将被测晶圆/芯片拣选至测试机进行检测。探针台和分选机的主要区别在于,探针台针对的是晶圆级检测,而分选机则是针对封装的芯片级检测。 该半导体测试设备项目计划总投资20252.43万元,其中:固定资产投资15706.87万元,占项目总投资的77.56%;流动资金4545.56万元,占项目总投资的22.44%。 达产年营业收入42958.00万元,总成本费用33649.38万元,税金及附加393.69万元,利润总额9308.62万元,利税总额10986.26万元,税后净利润6981.47万元,达产年纳税总额4004.80万元;达产年投资利润率45.96%,投资利税率54.25%,投资回报率34.47%,全部投资回收期 4.40年,提供就业职位912个。 报告针对项目的特点,分析投资项目能源消费情况,计算能源消费量并提出节能措施;分析项目的环境污染、安全卫生情况,提出建设与运营过程中拟采取的环境保护和安全防护措施。 ...... 半导体测试设备项目可研报告目录 第一章申报单位及项目概况 一、项目申报单位概况 二、项目概况 第二章发展规划、产业政策和行业准入分析 一、发展规划分析 二、产业政策分析 三、行业准入分析 第三章资源开发及综合利用分析 一、资源开发方案。 二、资源利用方案 三、资源节约措施 第四章节能方案分析 一、用能标准和节能规范。 二、能耗状况和能耗指标分析 三、节能措施和节能效果分析 第五章建设用地、征地拆迁及移民安置分析 一、项目选址及用地方案 半导体检测设备项目 初步方案 规划设计/投资分析/实施方案 摘要 该半导体检测设备项目计划总投资2034.58万元,其中:固定资产投 资1785.60万元,占项目总投资的87.76%;流动资金248.98万元,占项目总投资的12.24%。 达产年营业收入2487.00万元,总成本费用1982.55万元,税金及附 加37.32万元,利润总额504.45万元,利税总额611.35万元,税后净利 润378.34万元,达产年纳税总额233.01万元;达产年投资利润率24.79%,投资利税率30.05%,投资回报率18.60%,全部投资回收期6.88年,提供 就业职位48个。 提供初步了解项目建设区域范围、面积、工程地质状况、外围基础设 施等条件,对项目建设条件进行分析,提出项目工程建设方案,内容包括:场址选择、总图布置、土建工程、辅助工程、配套公用工程、环境保护工 程及安全卫生、消防工程等。 半导体检测设备是半导体设备的一个重要分支,占半导体设备比重在15%左右。半导体检测从设计验证到最终测试都不可或缺,贯穿整个半导体 制造过程。按照电子系统故障检测中的“十倍法则”,如果一个芯片中的 故障没有在芯片测试时发现,则在电路板(PCB)级别发现故障的成本为芯 片级别的十倍。 报告主要内容:总论、建设必要性分析、市场调研分析、投资方案、 项目建设地研究、工程设计可行性分析、项目工艺原则、环境影响分析、 项目安全规范管理、风险应对说明、项目节能评价、项目实施进度计划、项目投资方案分析、项目经济效益可行性、综合评估等。 半导体检测设备项目初步方案目录 第一章总论 第二章建设必要性分析 第三章投资方案 第四章项目建设地研究 第五章工程设计可行性分析 第六章项目工艺原则 第七章环境影响分析 第八章项目安全规范管理 第九章风险应对说明 第十章项目节能评价 第十一章项目实施进度计划 第十二章项目投资方案分析 第十三章项目经济效益可行性 第十四章项目招投标方案 第十五章综合评估 工业大学 毕业实践实验报告 班级:061 学号: 姓名: MOS晶体管电学特性测量 一、实践目的 根据半导体器件基础和半导体物理的课程所学知识,利用相关测量设备完成MOS晶体管的测量工作。希望通过此器件的测量来器件的输入特性,输出特性,转移特性,并要求系统地学习测试设备的工作特性,工作要求以及测量范围,以期为未来工作时可以独立使用相关测试设备作准备。 二、实践要求 所完成的测试报告包括器件的选型,生产商提供的基本参数表,测量时的各种曲线图,和生产商提供的进行比较异同点。还要介绍所使用测量设备的特性:作用,型号,测量范围,基本工作特性和要求,注意事项。 要求: 1.MOS晶体管可选自己购置或向老师提出要求来选取,选取前先查阅基本测量范围。 2.厂商提供的基本参数表可上网或查阅相关资料获取。 3.注意保护好测量设备,一定要注意相关工作事项。 4.注意人身安全,根据要求进行测量工作。 5.有条件时可进行同型号或不同型号的多个MOS晶体管的测量,列出表单进行对比,作统计图。 6.注意是否需要其它元器件,如电容,电阻等。 7.进行电压或电流扫描测量,测量要求有输入特性曲线,输出特性曲线,转移特性曲线,根摩尔参数等。 三、实践平台 1.半导体特性系统,半导体图示仪, 2.不同型号的MOS晶体管 3.可参考《双极场效应晶体管原理》或《模拟电子》 四、时间:2周 五、方案 通过用keithley将MOS管各端设定不同的输入参数,测量不同型号MOS管的输入特性曲线,输出特性曲线,转移特性曲线等。 六、步骤 绝缘栅场效应管(MOS管) 1、场效应晶体管(field effect transistor缩写(fet))简称场效应管.由多数载流子参与导电,也称为单极型晶体管.它属于电压控制型半导体器件. 特点: 具有输入电阻高(100000000~1000000000ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者. 作用: 场效应管可应用于放大.由于场效应管放大器的输入阻抗很高,因此耦合电容可以容量较小,不必使用电解电容器. 场效应管可以用作电子开关. 场效应管很高的输入阻抗非常适合作阻抗变换.常用于多级放大器的输入级作阻抗变换.场效应管可以用作可变电阻.场效应管可以方便地用作恒流源.绝缘栅场效应管的分类:绝缘栅场效应管也有两种结构形式,它们是N沟道型和P沟道型。无论是什麽沟道,它们又分为增强型和耗尽型两种。 2、它是由金属、和半导体所组成,所以又称为金属—氧化物—半导体场效应管,简称MOS 场效应管。 3、绝缘栅型场效应管的工作原理(以N沟道增强型MOS场效应管)它是利用UGS来控制“感应电荷”的多少,以改变由这些“感应电荷”形成的导电沟道的状况,然后达到控制漏极电流的目的。在制造管子时,通过工艺使绝缘层中出现大量正离子,故在交界面的另一侧能感应出较多的负电荷,这些负电荷把高渗杂质的N区接通,形成了导电沟道,即使在VGS=0时也有较大的漏极电流ID。当栅极电压改变时,沟道内被感应的电荷量也改变,导电沟道的宽窄也随之而变,因而漏极电流ID随着栅极电压的变化而变化。 场效应管的式作方式有两种:当栅压为零时有较大漏极电流的称为耗散型,当栅压为零,漏极电流也为零,必须再加一定的栅压之后才有漏极电流的称为增强型。 特性曲线 场效应管的特性曲线分为转移特性曲线和输出特性曲线。 1) 转移特性 在u DS一定时, 漏极电流i D与栅源电压u GS之间的关系称为转移特性。 输出特性 型号2SK117 种类绝缘栅(MOSFET) (19)中华人民共和国国家知识产权局 (12)实用新型专利 (10)授权公告号 (45)授权公告日 (21)申请号 201920249247.5 (22)申请日 2019.02.27 (73)专利权人 南通捷晶半导体技术有限公司 地址 226000 江苏省南通市通州区兴东街 道紫星村洋兴公路881号 (72)发明人 翁晓升 (74)专利代理机构 北京联瑞联丰知识产权代理 事务所(普通合伙) 11411 代理人 黄冠华 (51)Int.Cl. H01L 21/66(2006.01) (54)实用新型名称 一种半导体封装检测设备 (57)摘要 本实用新型公开了一种半导体封装检测设 备,包括检测台、半齿轮、手动伸缩杆和检测头, 所述检测台的上方安装有安装板,且安装板的下 侧设置有齿块,所述齿块的前后两侧均设置有第 一滑块,且第一滑块的外侧设置有第一滑槽,所 述半齿轮位于安装板的下方,且半齿轮的前侧安 装有伺服电机,所述手动伸缩杆安装在安装板的 上方,且手动伸缩杆的上方连接有放置板,所述 放置板的前后两侧均开设有第二滑槽。该半导体 封装检测设备设置有放置板、安装板、齿块和半 齿轮,半齿轮与齿块的相互啮合带动安装板间歇 性运动,使得安装板带动放置板间歇性运动,从 而延长放置板上的封装半导体的检测时间,便于 检测头对封装半导体进行充分检测。权利要求书1页 说明书3页 附图3页CN 209785881 U 2019.12.13 C N 209785881 U 权 利 要 求 书1/1页CN 209785881 U 1.一种半导体封装检测设备,包括检测台(1)、半齿轮(6)、手动伸缩杆(8)和检测头(15),其特征在于:所述检测台(1)的上方安装有安装板(2),且安装板(2)的下侧设置有齿块(3),所述齿块(3)的前后两侧均设置有第一滑块(4),且第一滑块(4)的外侧设置有第一滑槽(5),所述半齿轮(6)位于安装板(2)的下方,且半齿轮(6)的前侧安装有伺服电机(7),所述手动伸缩杆(8)安装在安装板(2)的上方,且手动伸缩杆(8)的上方连接有放置板(9),所述放置板(9)的前后两侧均开设有第二滑槽(10),且第二滑槽(10)的内部开设有定位孔 (12),所述安装板(2)的前后两侧均安装有转杆(14),且转杆(14)的外侧焊接有连接杆 (13),所述连接杆(13)的上端连接有第二滑块(11),所述转杆(14)的前侧设置有转盘(16),所述放置板(9)内部的前后两侧均设置有固定板(18),且固定板(18)的外侧连接有移动杆(17),所述移动杆(17)的外侧连接有弹簧(19),所述检测头(15)安装在检测台(1)的后上方。 2.根据权利要求1所述的一种半导体封装检测设备,其特征在于:所述安装板(2)的下侧等间距的分布有齿块(3),且安装板(2)通过第一滑块(4)和第一滑槽(5)与检测台(1)滑动连接。 3.根据权利要求1所述的一种半导体封装检测设备,其特征在于:所述第一滑块(4)和第一滑槽(5)关于安装板(2)的中心线对称设置,且第一滑块(4)的侧剖面为“T”形结构。 4.根据权利要求1所述的一种半导体封装检测设备,其特征在于:所述放置板(9)的侧剖面为“U”形结构,且放置板(9)的最高点低于检测头(15)的最低点。 5.根据权利要求1所述的一种半导体封装检测设备,其特征在于:所述连接杆(13)的下端通过转杆(14)与安装板(2)构成转动机构,且连接杆(13)的上端与第二滑块(11)为铰接连接。 6.根据权利要求1所述的一种半导体封装检测设备,其特征在于:所述移动杆(17)设置有2组,且相邻2个移动杆(17)通过弹簧(19)构成弹性结构,并且移动杆(17)与放置板(9)和固定板(18)均为铰接连接。 2 半导体测试理论1 测量可重复性和可复制性(GR&R) GR&R是用于评估测试设备对相同的测试对象反复测试而能够得到重复读值的能力的参数。也就是说GR&R是用于描述测试设备的稳定性和一致性的一个指标。对于半导体测试设备,这一指标尤为重要。 从数学角度来看,GR&R就是指实际测量的偏移度。测试工程师必须尽可能减少设备的GR&R值,过高的GR&R值表明测试设备或方法的不稳定性。 如同GR&R名字所示,这一指标包含两个方面:可重复性和可复制性。可重复性指的是相同测试设备在同一个操作员操作下反复得到一致的测试结果的能力。可复制性是说同一个测试系统在不同操作员反复操作下得到一致的测试结果的能力。 当然,在现实世界里,没有任何测试设备可以反复获得完全一致的测试结果,通常会受到5个因素的影响: 1、测试标准 2、测试方法 3、测试仪器 4、测试人员 5、环境因素 所有这些因素都会影响到每次测试的结果,测试结果的精确度只有在确保以上5个因素的影响控制到最小程度的情况下才能保证。 有很多计算GR&R的方法,下面将介绍其中的一种,这个方法是由Automotive Idustry Action Group(AIAG)推荐的。首先计算由测试设备和人员造成的偏移,然后由这些参数计算最终GR&R 值。 Equipment Variation (EV):代表测试过程(方法和设备)的可重复性。它可以通过相同的操作员对测试目标反复测试而得到的结果计算得来。 Appraiser Variation (AV):表示该测试流程的可复制性。可以通过不同操作员对相同测试设备和流程反复测测试所得数据计算得来。 GR&R的计算则是由上述两个参数综合得来。 必须指出的是测试的偏移不仅仅是由上述两者造成的,同时还受Part Variation(PV)的影响。PV表示测试目标不同所造成的测试偏差,通常通过测试不同目标得到的数据计算而来。 现在让我们来计算总偏差:Total Variation (TV),它包含了由R&R和PV所构成的影响。 TV = sqrt((R&R)**+ PV**) 在一个GR&R报表中,最终的结果往往表示成:%EV, %AV, %R&R,和 %PV。他们分别表示EV,AV,R&R 和PV相对TV的百分比。因此 %EV=(EV/TV)x100% %AV=(AV/TV)x100% %R&R=(R&R/TV)x100% %PV=(PV/TV)x100% %R&R如果大于10%,则此测试设备和流程是良好的;%R&R在10%和30% 之间表示可以接受;如果大于30%则需要工程人员对此设备和流程进行改良。 电气测试可信度(Electrical Test Confidence)(设备管理)半导体和测试设备介绍

半导体测试技术实践

温湿度文献综述

半导体和测试设备介绍_图文(精)

电学半导体器件基础测试题

半导体测试设备项目可研报告

半导体检测设备项目初步方案

MOS晶体管电学特性测量毕业论文,绝对精品

【CN209785881U】一种半导体封装检测设备【专利】

半导体测试理论