第44卷 第1期

复旦学报(自然科学版) V o1.44, N o.12005年2月Journal of Fudan University (Natural Science ) Feb., 2005

文章编号:042727104(2005)0120021205

ΞJPEG 2000高速MQ 编解码器的V LSI 实现

鲁则瑜,华 林,朱 柯,程君侠

(复旦大学专用集成电路与系统国家重点实验室,上海200433)摘 要:提出了一种应用于J PEG 2000标准的高速M Q 编解码器的V LSI 架构.该架构对J PEG 2000中的标准M Q 编解码流程进行了优化,采用条件判断归纳化简、零检测和整体移位等方法来达到高速编解码的目的.采用3级流水线结构的M Q 编解码器架构,编解码器的工作效率可以达到1bit/cycle ,并且在速度与面积之间达到了很好的平衡.

关键词:半导体技术;M Q 编解码器;J PEG 2000;流水线;超大规模集成电路

中图分类号:T N 492 文献标识码:A

J PEG 2000标准是IS O/IEC 制定的静止图像编码新标准,在主观图像质量、支持渐进图像传输、感兴趣图像编码和抗误码性能上优于传统的J PEG 标准1.

J PEG 2000标准采用自适应算术编码而非传统J PEG 标准所使用的霍夫曼编码.自适应算术编码与霍夫曼编码最大的不同在于它并不是对每个信号产生一个码值,而是对一个信号序列产生一个码值;除了需要获得信号序列外,还要获得其中每个信号的预测概率,根据这个概率将0,1)区间不断分割,最后得到的码值就是最后分割得到的子区间所对应的一个二进制表示,自适应性的获得在于不断更新信号的预测概率,使之总是趋近于实际2.

M Q 编码器继承了I BM 的ABIC (自适应双层图像压缩)中Q 编码器无乘法的近似和位缓存的策略,增加了条件交换和概率估计状态机中的贝叶斯学习过程.虽然M Q 编码器省略了乘法运算,但频繁的区间重整和复杂的字节输出使得J PEG 2000标准中基于软件执行的M Q 编解码流程效率很低.

为了提高硬件实现的M Q 编解码器的执行效率,对M Q 编解码器编码和解码的流程进行了优化,对条件判断进行了归纳和简化,采用了零检测和整体移位的方法,并且采用了流水线的V LSI 架构,从而达到高速编码和解码的目的.

1 J PEG 2000标准MQ 编解码的原理

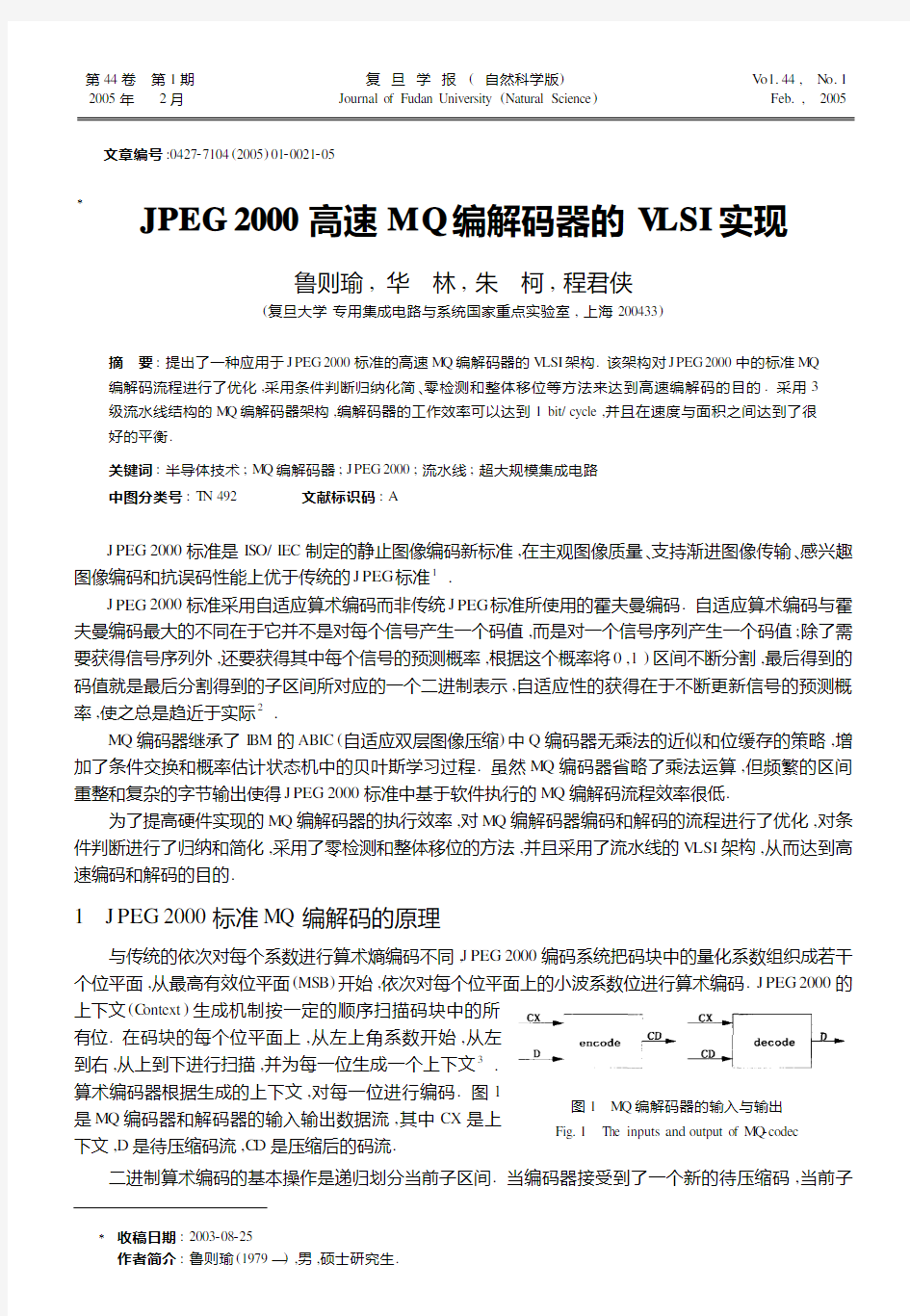

与传统的依次对每个系数进行算术熵编码不同,J PEG 2000编码系统把码块中的量化系数组织成若干个位平面,从最高有效位平面(MS B )开始,依次对每个位平面上的小波系数位进行算术编码.J PEG 2000的图1 M Q 编解码器的输入与输出Fig.1 The inputs and output of M Q 2codec

上下文(C ontext )生成机制按一定的顺序扫描码块中的所

有位.在码块的每个位平面上,从左上角系数开始,从左

到右,从上到下进行扫描,并为每一位生成一个上下文3.

算术编码器根据生成的上下文,对每一位进行编码.图1

是M Q 编码器和解码器的输入输出数据流,其中CX 是上

下文,D 是待压缩码流,C D 是压缩后的码流.二进制算术编码的基本操作是递归划分当前子区间.当编码器接受到了一个新的待压缩码,当前子Ξ

收稿日期:2003208225

作者简介:鲁则瑜(1979—),男,硕士研究生.

区间会被划分成更小的2个子区间.子区间的左界值被更新,并且指向由待压缩码流所选定的新子区间的低边界;子区间的间隔值也更新为新子区间的间隔.

M Q编解码器用寄存器A来记录当前子区间的间隔值,用寄存器C来记录当前子区间的左界值.M Q 编解码器子区间的宽度取值范围限定在0.75,1.5),用ox8000来代表0.75.当编码器接受到了一个新的待压缩码,编码器从概率估值表查找相应的概率Qe.根据接受的待压缩码的类型,寄存器A的值和寄存器C的值被进行更新,更新情况如下:当接受大概率符号MPS:A=A-Qe,C=C+Qe;当接受小概率符号LPS:A=Qe,C=C.

M Q编解码器所使用的概率估值表是一个可以对原始数据快速适应的复杂概率自动估计模型.该模型是一个具有47个状态的有限状态机.每个状态包含小概率符号LPS的概率Qe、下一个状态的索引NMPS和N LPS、是否需要交换MPS和LPS所代表符号的标志SWITCH.具体的概率估值表见文献4.

M Q编解码过程的当前区间可以表示为[C,C+A).随着编码次数的增加,这一子区间的精度会不断提高,意味着C和A的有效位数不断增加.由于实际可操作的寄存器位数是有限的,因此引入区间重整的概念,既当满足一定条件时,将C和A进行左移操作,同时将C寄存器不再变化的高位送入存储区.对于M Q编解码器来说,进行区间重整的条件是A<0.75.当该条件满足时,将C和A都乘以2(左移1位),直到0.75=A<1.5.

同时,由于M Q算法在进行区间计算时省略了乘法的近似5,使得可能发生LPS子区间大于MPS子区间的情况.为了避免这种情况,采用区间条件交换,即将MPS与LPS互换.

2 MQ编解码流程的改进

J PEG2000标准中的M Q编码和解码的流程基于串行,适合软件的实现.为了体现硬件实现在并行性上的优势,提高编码和解码的效率,对编码和解码的流程进行相应的优化.

2.1 编码区间计算的化简

J PEG2000标准对于编码的区间计算的条件判断是通过C ODE1、C ODE0、C ODE LPS以及C ODE MPS等步骤进行的6,判断条件及步骤比较复杂,因此为了方便编码器区间计算的实现,对条件判断进行了归纳和化简,得到的区间计算判别条件如图2所示.

2.2 解码区间交换及区间重整判断的化简

J PEG2000标准的标准解码流程对于解码过程中的区间交换和区间重整判断通过MPS EXCH ANGE 和LPS EXCH ANGE过程分别表示,同样可以对解码区间交换和区间重整的条件判断进行归纳和化简.简

化后的解码区间交换和区间重整判断过程如图3所示

.

图2 化简的编码区间计算流程

Fig.2 Improved encoder interval subdivision update 图3 化简的解码区间交换及区间重整判断Fig.3 Improved decoder conditional

exchange and renormalization judgment

22复旦学报(自然科学版) 第44卷

2.3 区间重整和字节输出/输入的加速

图4 编码和解码区间重整流程Fig.4 Encoder and decoder renormalization procedure J PEG 2000标准中的M Q 编码和解码流程中的

区间重整和字节输出/输入是一个循环执行的过程

(见图4).

从J PEG 2000标准中的概率估值表中可以发

现,编码和解码的区间重整流程最坏情况是循环15

次.这造成编码和解码的效率极其低下.为此,需

要对区间重整及字节输入/输出的流程进行优化.

观察图4的流程,可以发现流程循环的次数取

决于寄存器A 从最高位到第一个非0位为止,共有

多少个0,如从最高位开始有连续n 个0,则表示需

要循环n 次.

基于以上的观察,引入了零检测和整体移位的

方法.通过专门的硬件,来检测A 寄存器的高位中0

的数目,然后通过移位寄存器一次移到位.

同样通过观察可以发现,编解码器区间重整的过程夹杂着字节输入/输出的操作.在进行区间重整的移位操作的过程中,可能不需要进行字节输入/输出,但也可能需要进行1字节或2字节的字节输入/输出.因此,也需要对字节输入/输出的机制做出调整.

将流程中的CT 减法计数调整为加法计数,设定5位的OT ,CT 寄存器,其中3位CT 寄存器用于计数,2位OT 溢出寄存器用于记录溢出次数.OT 溢出寄存器共有0,1,2三种情况,分别代表没有字节输入/输出、1字节输入/输出、2字节输入/输出,由此达到了加速区间重整和字节输入/输出的目的.3 MQ 编解码器的V LSI 架构

3.1 MQ 编码器的架构

M Q 编码器的架构是一个3级流水线结构,分别负责概率估计和区间交换、区间计算和区间重整、字节输出,如图5所示

.

图5 M Q 编码器架构

Fig.5 M Q encoder architecture

3

2第1期 鲁则瑜等:J PEG 2000高速M Q 编解码器的V LSI 实现

外界输入上下文信息CX 和待压缩码D ,上下文CX 从上下文寄存器组选中查找概率估值表所需的in 2dex 信息,然后根据index 信息从概率估值表查找LPS 概率Qe 、NMPS 、N LPS 信息,以及交换标值switch.概率估计查找到的信息被送给第2级进行区间计算和区间重整.用专门的硬件进行区间计算所需的加法和减法运算,同样用专门的数零译码器和专用移位寄存器进行区间重整所需的零检测和整体移位.第2级区间重整过程产生的字节输出被送给第3级.由于每次译码过程产生的输出字节数不同,在第3级设置了4字节的FIFO.前级送入的字节被存放在FIFO 中,然后再通过FIFO 向外输出已压缩的字节.

3.2 MQ 解码器的架构

M Q 解码器的架构也是3级流水结构,分别为概率估计和区间交换、区间计算和区间重整、字节输入,如图6所示

.

图6 M Q 解码器架构

Fig.6 M Q decoder architecture

上下文寄存器组根据输入的上下文信息CX 查找相应的概率估值表索引index.根据所得信息查找对应的N LPS 概率Qe 和区间交换所需的N LPS 、NMPS 信息以及交换标志switch.在向后级送出Qe 信息的同时,在第1级完成区间交换的过程.第1级还根据相应的条件判断产生解压缩码D.

与编码器相类似,负责区间计算和区间重整的第2级包括专用于区间计算的2个减法器和用于区间重整的2个专用移位寄存器.除了包括以上专用硬件,区间计算和区间重整级还包含专用的加法器,用于进行字节输入过程所需的C 寄存器加法.

字节输入级从外界读入已压缩的字节,存放在FIFO 中,根据区间重整过程产生的信息,将需要读入的1字节或2字节数据用专用的移位寄存器进行相应位数的移位,移位后的数据送入第2级和相应的C 寄存器数据在专用的加法器执行加法操作.

从该框架图可以看出,解码器所需要的硬件比编码器略多,因此规模也比编码器略大.

4 V LSI 实现结果及性能分析

文中所描述的M Q 编解码器用Verilog H D L 语言进行RT L 级描述,并且在Verilog 2X L 环境下进行仿真.仿真结果与标准算法软件计算结果相比较以保证其正确性.

将实现的代码在synopsys 公司的design com piler 中用TS MC 0.25μm 工艺进行综合.综合考虑M Q 编解码器在速度和面积两方面的因素,设置在100MH z 时钟的环境下工作.结果表明,该M Q 编解码器可以在100MH z 时钟频率下正常工作,由于该编解码器的工作效率η为1bit/cycle ,因此,该编解码器的工作速度

42复旦学报(自然科学版) 第44卷

可以达到100Mbit/s.编码器的集成度是3600门,解码器的集成度是4000门.这一结果在速度与面积上达到了很好的平衡.

文献5描述了一种基于动态流水线结构的自适应二进制编码器;文献6描述了一种专用于J PEG 2000标准的带有by 2pass 模式加速功能的算术编码器,该编码器基于状态机设计,编解码的执行效率取决于当前状态.编码器共有36个状态,执行编码过程需要1~12个状态;解码器共有28个状态,执行解码过程需要3~7个状态.将本文所描述的编解码器与上述类似算术编解码器比较,结果见表1.

表1 性能比较

T ab.1 Performance comparis on

来源

设计方案工艺/μm f /MH z 编码器面积/k 门η/(bit ?cycle -1)解码器面积/k 门η/(bit ?cycle -1)本文

3级流水线M Q 编解码器0.25100 3.6141文献5]

动态流水自适应二进制算术编码器0.850NA 0.25NA NA 文献6]by 2pass 模式的二进制算术编解码器

0.18200 3.20.09~1 2.50.14~0.33从比较结果可以看出,本文描述的算术编解码的优点在于改进了算法,提高了编解码器的工作效率. 参考文献:

1

杜伟娜,孙 军.新一代静止图像编码系统—J PEG 2000J .电路与系统学报,2002,7(3):73276.2

刘芳敏,吴永辉,俞建新.J PEG 2000图像压缩过程及原理描述J .计算机辅助设计与图形学报,2002,14(10):9052916.3

周 宁,汤晓军,徐维朴.J PEG 2000图像压缩标准及其关键算法J .现代电子技术,2002,(12):125.4

IS O/IEC.FC D 1544421,Final C ommittee Draft ,J PEG 2000Image C oding System S.5

K uang S R ,Jou J M ,Chen R D.Dynamic pipeline design of an adaptive binary arithmetic coder J .IEEE Trans on Circuits and System 2Ⅱ,2001,48(9):8132825.6 Andra K.Wavelet and entropy coding accelerators for J PEG https://www.doczj.com/doc/e617455032.html, A :Arizona S tate University ,2001.

A V LSI Implementation of a High 2Speed

MQ 2Codec for JPEG 2000

LU Ze 2yu ,HUA Lin ,ZHU K e ,CHEN G J un 2xia

(ASIC &System State K ey Laboratory ,Fudan Univer sity ,Shanghai 200433,China )

Abstract :A high 2speed M Q 2codec V LSI architecture for J PEG2000standard is presented.The architecture optimizes the stan 2dard J PEG 2000M Q encoding and decoding flow ,accelerating the encoding and decoding with simplified conditional judgment ,zero detection and whole shifting.The M Q 2codec presented adopts a 32stage pipeline architecture.Its speed is up to 1bit/cy 2cle.A g ood trade 2off between speed and area is achieved.

K eyw ords :semiconductor technology ;M Q 2codec ;J PEG 2000;pipeline ;V LSI 52第1期 鲁则瑜等:J PEG 2000高速M Q 编解码器的V LSI 实现