基于FPGA的高效FIR滤波器的设计与实现

Data

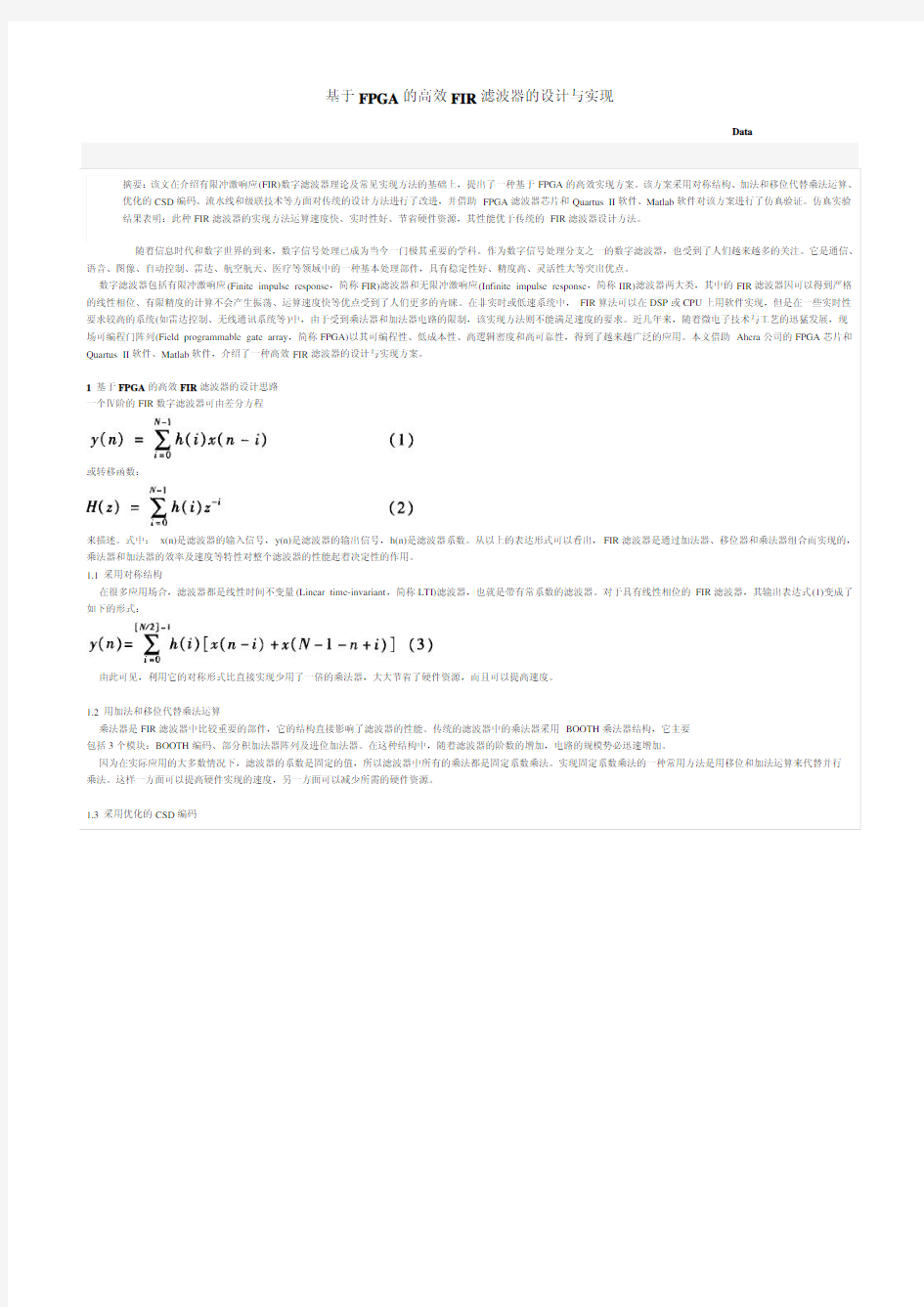

摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。该方案采用对称结构、加法和移位代替乘法运算、优化的CSD编码、流水线和级联技术等方面对传统的设计方法进行了改进,并借助FPGA滤波器芯片和Quartus II软件、Matlab软件对该方案进行了仿真验证。仿真实验结果表明:此种FIR滤波器的实现方法运算速度快、实时性好、节省硬件资源,其性能优于传统的FIR滤波器设计方法。

随着信息时代和数字世界的到来,数字信号处理已成为当今一门极其重要的学科。作为数字信号处理分支之一的数字滤波器,也受到了人们越来越多的关注。它是通信、语音、图像、自动控制、雷达、航空航天、医疗等领域中的一种基本处理部件,具有稳定性好、精度高、灵活性大等突出优点。

数字滤波器包括有限冲激响应(Finite impulse response,简称FIR)滤波器和无限冲激响应(Infinite impulse response,简称IIR)滤波器两大类,其中的FIR滤波器因可以得到严格的线性相位、有限精度的计算不会产生振荡、运算速度快等优点受到了人们更多的青睐。在非实时或低速系统中,FIR算法可以在DSP或CPU上用软件实现,但是在一些实时性要求较高的系统(如雷达控制、无线通讯系统等)中,由于受到乘法器和加法器电路的限制,该实现方法则不能满足速度的要求。近几年来,随着微电子技术与工艺的迅猛发展,现场可编程门阵列(Field programmable gate array,简称FPGA)以其可编程性、低成本性、高逻辑密度和高可靠性,得到了越来越广泛的应用。本文借助Ahera公司的FPGA芯片和Quartus II软件、Matlab软件,介绍了一种高效FIR滤波器的设计与实现方案。

1 基于FPGA的高效FIR滤波器的设计思路

一个Ⅳ阶的FIR数字滤波器可由差分方程

或转移函数:

来描述。式中:x(n)是滤波器的输入信号,y(n)是滤波器的输出信号,h(n)是滤波器系数。从以上的表达形式可以看出,FIR滤波器是通过加法器、移位器和乘法器组合而实现的,乘法器和加法器的效率及速度等特性对整个滤波器的性能起着决定性的作用。

1.1 采用对称结构

在很多应用场合,滤波器都是线性时间不变量(Linear time-invariant,简称LTI)滤波器,也就是带有常系数的滤波器。对于具有线性相位的FIR滤波器,其输出表达式(1)变成了如下的形式:

由此可见,利用它的对称形式比直接实现少用了一倍的乘法器,大大节省了硬件资源,而且可以提高速度。

1.2 用加法和移位代替乘法运算

乘法器是FIR滤波器中比较重要的部件,它的结构直接影响了滤波器的性能。传统的滤波器中的乘法器采用BOOTH乘法器结构,它主要

包括3个模块:BOOTH编码、部分积加法器阵列及进位加法器。在这种结构中,随着滤波器的阶数的增加,电路的规模势必迅速增加。

因为在实际应用的大多数情况下,滤波器的系数是固定的值,所以滤波器中所有的乘法都是固定系数乘法。实现固定系数乘法的一种常用方法是用移位和加法运算来代替并行乘法。这样一方面可以提高硬件实现的速度,另一方面可以减少所需的硬件资源。

1.3 采用优化的CSD编码

众所周知,二进制数在实现乘法或加法时,数值为0的位是不参与运算的。因此,对输入信号进行编码时,如果能使0位的数量最多,则完成相应的运算所需要的硬件将会大大减少,运算的速度也会相应地提高很多。正则有符号数字量(Canonic signed digit,简称CSD)正是基于此思想而提出来的一种新型编码方法,它是具有最少非0元素的表示法。

CSD码的特性是最终表达式在两个数位之间至少有一个0。它的算法是从最低有效位开始,用10…01取代所有大于2的一序列,用1101

取代1011;然后从最高有效位开始,用011代替101。例如十进制数231的CSD码为100101001,可以看出,在实现其乘法时,只需要4个加法器(如图1所示)。若采用普通的二进制代码实现,因(231)10=(11100111)2,需要5个加法器。可见,采用CSD码节省了加法器的数量。

为了进一步提高效率,对于某些数据,还可以采用优化的CSD编码,即首先将系数拆分成几个因子,再实现每一个因子。如对231,首先拆分成7×33,然后分别实现因子7和33。7和33每个因子都只需要1个加法器(如图2所示),即实现231的乘法时只需要2个加法器,因此效率得到了更大的提高。

图1 231的CSD码的实现

图2 231的优化CSD码的实现

1.4 采用流水线技术

在滤波器的加法运算中,根据内部的数据流规则,可以采用流水线技术将一个运算操作分解成一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算。对于FPGA器件来说,采用流水线式的设计,可以在不增加电路成本和规模的基础上提高运算处理的实时性。

1.5 采用级联技术

设计高阶的滤波器时,可以采用多个低阶滤波器级联而成,如n个10阶的FIR滤波器可以级联成一个10n阶的滤波器,级联后的滤波器可以

是对称的,也可以是非对称的。实践证明,采用分布式算法,级联后的滤波器不会因为长度的增加而使性能明显下降。

2 高效FIR滤波器的FPGA实现

在实际的数字传输系统中,接收端和发送端为了达到最小的误码率,一般采用平方根升余弦滤波器。该滤波器的系统函数是:

式中:α是滚降系数,0≤α≤1,T为码元周期。

若取滚降系数α=1,滤波器长度为31,每个码元取4个样点,滤波器的系数采用10位量化,则可得到平方根升余弦滤波器的系数为h(n)=

{4,7,2,-7,9,4,22,25,-3,-53,-83,-43,88,277,445,512,445,277,88,-43,-83,-53,-3,25,22,4,-9,-7,2,7,4}。

根据以上思路,采用Altera公司Cyclone系列的EP1C3T100C6芯片,在Quartuas II开发软件下对此FIR滤波器进行设计及仿真。首先利用

VHDL语言完成设计输入,然后用Compiler进行编译调试。编译通过后,再利用该软件所提供的Waveform Editor进行时序仿真,得到的时序仿真波形如图3所示。其中,cP是控制输入的时钟信号,时钟频率为50 MHz,clr是加法器及锁存器的清零信号,低电平0有效,X是外部的输入信号,Y是最终的外部输出信号。

图3 FIR滤波器时序仿真图

用Waveform Editor仿真后,将生成的波形转化为tbl文件,提取出波形数据。通过Matlab软件可以画出这些数据对应的图形,即滤波结果图,如图4中的虚线所示,图中横坐标是采样点数,纵坐标代表的是采用10位二进制数量化后的幅值,图4中的实线是FPGA滤波结果。从图4可以看出.用本文提出的设计方案实现的基于FPGA的FIR滤波器的滤波结果与理想滤波结果是非常接近的,对比图中FPGA滤波结果比理想值稍低,原因是由于在FPGA滤波器实现的过程中,为了节省硬件资源,将数据做了截掉低6位的处理,从而产生了一点误差。但是,从仿真结果来看,该截掉低位的处理并不影响滤波器的性能。

图4 FPGA仿真滤波结果与理想FIR滤波结果对比图

利用软件所提供的Timing Analyzer进行时间分析,可知此FIR设计方案的信号输出延迟在6.8 ns左右。即系统的最高工作频率为147 MHz。

从仿真结果中还可得到硬件资源的占用情况及利用率情况,实现该FIR滤波器共占用961个逻辑单元,逻辑单元利用率为33%。

由以上分析可以看出,该设计方案不管是在速度及实时性方面还是在资源利用率上,都具有很大的优势。将其应用至通信系统或信号处理领域中均可满足实际的需要。

3 结论

FIR滤波器在数字信号处理的各个领域中起着举足轻重的作用,它的性能优劣对信号处理的结果有很大的影响。本文采用对称结构、加法和移位代替乘法运算、优化的CSD编码、流水线技术、级联技术几个方面,对传统的FIR滤波器的设计进行了改进,并借助Altera公司的FPGA芯片和Quartuas II软件以及Matlab软件对设计方案进行了仿真验证。仿真实验结果表明,该FIR滤波器的实现方案,具有工作速度快、实时信号好、节省硬件资源等特点,能够满足实际的数字系统的要求。

开题报告 电子信息工程 基于FPGA的CIC滤波器的设计与仿真 一、综述本课题国内外研究动态,说明选题的依据和意义 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现。滤波器的结构简单, 需要的存储量小, 是被证明在高速抽取和插值系统中非常有效的单元。 随着数字信号处理算法的不断优化,数字信号处理器(Digital Signal Processors, DSPs)性能的不断提高,数字信号处理技术越来越被广泛地应用在各个领域。数字信号处理技术正朝着高速高性能方向发展,因此这对数字信号处理的手段和工具也提出了更高的要求。 随着现场可编程门阵列(Field Programmable Gate Array, FPGA)制造工艺的不断改进,其集成度和性能的不断提高,采用FPGA对数字信号进行处理越来越受到重视。与DSP相比,FPGA有着不可比拟的优势。一方面,与DSP靠程序指针来运行程序相比,FPGA执行算法的本质是靠电路并行执行的,因此在同样的时钟频率下,使用FPGA完成数字信号处理算法要比使用DSP快得多。另一方面,由于FPGA编程灵活,资源可重新配置,使得在实现数字信号处理时更加灵活,成本更低。因此,FPGA性能的不断提高,能够满足未来复杂数字信号高速实时处理的要求。 用FPGA设计滤波器,无非是是设计一些乘累加单元,其滤波器的各种特性即滤波参数可以通过MATLAB仿真获得。所以首先要做的是确定你滤波器的设计要求,在MATLAB中仿真设计出该滤波器,从而导出滤波器系数,才能在FPGA中使用。 CIC滤波器由于其无需乘法器以及结构特殊,在移动电视直放站的数字信号处理中,可以高效地胜任抽取滤波的任务。然而C1C滤波器也有缺陷,一者通带下垂严重,二者信号折叠带衰减不充分,而且此两者难以兼顾。RS修正法和Kaiser—Hamming补偿法联合使用于CIC滤波器的改进技术中,有效地解决了该问题。 在移动通信系统中,软件无线电的概念已显得越来越重要。众所周知SRC滤波部分的一个重点就是抑制潜在的混叠部分,有一种时变CIC滤波器,他同样是通过先A倍内插再B倍抽样来实现采样率的转换。因此,改进的CIC滤波器在软件无线电中有大的重

FPGA实现FIR抽取滤波器的设计FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。随着可编程逻辑器件的发展,使用FPG A来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR滤波器。 1 FIR滤波器工作原理 在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不论采用乘累加方法还是分布式算法设计FIR滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构 在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。在数字系统中采用拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式: 乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。 3 滤波器系数的求取 使用Matlab集成的滤波器设计工具FDAtool,可以完成多种滤波器的数值设计、分析与评估,设计16阶低通滤波器参数如下:

cic滤波器的FPGA实现 发布时间:2016-01-26 15:07:21 技术类别:CPLD/FPGA 一、关于多采样率数字滤波器 很明显从字面意思上可以理解,多采样率嘛,就是有多个采样率呗。前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号,具体例子我也不解释了,我们大学课本上多速率数字信号处理这一章也都举了不少的例子。 按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换 但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。 二、抽取 先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素 下面来具体来介绍 如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8 Khz ,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。 上面是采样频率为8K的数字信号频域图,现在我要对这个数字信号进行时域抽取,从而来降低信号的采样率,我们知道,一旦我们对数字信号进行时域抽取,那么采样率下降,而采样率就是数字信号频域的波形周期,那么也就是周期下降,所以,我们对信号进行抽取要有个度,要在满足抽样定理的条件下对信号进行抽取,否则就会发生频谱混叠。

目录 引言 (4) 第一章FPGA的设计流程 (5) 1.1 FPGA概述 (5) 1.2 FPGA设计流程 (9) 1.3硬件描述语言HDL(Hardware Description Language) (10) 1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (13) 第二章有限冲激响应(FIR)滤波器的原理及设计 (16) 2.1数字信号处理基础原理 (16) 2.2 FIR滤波器背影知识 (19) 2.3 FIR数字滤波器原理 (21) 2.4 利用窗函数法设计FIR滤波器 (26) 第三章FIR 数字滤波器的FPGA实现 (31) 3.1串行FIR滤波器原理 (31) 3.2分布式算法基础 (32) 3.3直接型FIR滤波器的原理结构图 (34) 3.4具有转置结构的FIR滤波器 (36) 第四章结论与总结 (40) 谢辞 (42) 参考文献 (43)

摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。因此在许多应用领域都显示了强大的生命力,具有重要应用意义。本文介绍了用VHDL实现线性相位FIR(有限长单位冲激响应)滤波器。提出了一种基于FPGA的FIR滤波器设计方案。介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus Ⅱ

基于FPGA的CIC数字滤波器的设计 摘要:级联积分梳状(Cascade Integrator Comb,CIC)滤波器是数字系统中实现大采样率变化的多速率滤波器,已经证明是在高速抽取和插值系统中非常有效的单元,在数字下变频(DDC)和数字上变频(DUC)系统中有广泛的应用。它不包含乘法器,只是由加法器,减法器和寄存器组成,而且需要的加法器的数目也减少了许多,因此CIC滤波器比FIR和IIR滤波器更节省资源,并且实现简单而高速。本文主要讨论了CIC滤波器的基本原理和基于FPGA的仿真实现方法,具体是采用Verilog HDL语言编程,将滤波器分为积分器模块和梳状器模块2个部分,对每个模块进行具体的功能分析和设计实现,最后通过Modelsim 仿真对滤波器的性能进行分析,验证了设计的正确性。 关键词:CIC滤波器;抽取;FPGA;Verilog HDL the Design of Cascade Integrator Comb Filter Based on FPGA Abstract:CIC (Cascade Integrator Comb, CIC) filter is a digital system to achieve large changes in multi-rate sampling rate filter, which has been proven to be a very effective unit in the high-speed extraction and interpolation system. It is widely used in the digital down conversion (DDC ) and digital up conversion (DUC) systems. It does not contain the multiplier, but just composes by adders, subtractors and registers, and the number of needing adders is reduced a lot. So it takes fewer resources than FIR filter and IIR filter. And the speed of CIC filter is very high and it is also very convenient to realize.This article discusses the basic principles of CIC filter and the simulation way based on FPGA. The modules were described with Verilog HDL. Firstly, the filter was divided into two parts which were integration module and the comb module. Then the function of each module were analyzed and designed. Finally the performance of the filter was analyzed under ModelSim and the correctness of the design was verified. Keywords:CIC filter; Decimation; FPGA; Verilog HDL 1. 引言: 数字滤波是数字信号分析中最重要的组成部分之一,数字滤波与模拟滤波相比,具

FIR带通滤波器的FPGA实现 时间:2009-11-11 09:14:40 来源:现代电子技术作者:石兴华,吴光敏引言 在FPGA应用中,比较广泛而基础的就是数字滤波器。根据其单位冲激响应函数的时域特性可分为无限冲击响应(Infinite Impulse Response,IIR)滤波器和有限冲击响应(Finite Impulse Response,FIR)滤波器。DSP Builder集成了Altera和Matlab/Simulink基于FPGA的信号处理的建模和设计。该工具可以将数字信号处理算法(DSP)系统表示成为一个高度抽象的模块,在不降低硬件性能的前提下,自动将系统映射为一个基于FPGA的硬件设计方案。即支持设计者在Matlab中完成算法设计,在Simulink软件中完成系统集成,然后通过SignalCompiler(模块名)生成在QuartusⅡ软件中可以使用的硬件描述语言,最终实现硬件系统的设计。FIR滤波器是DSPBuilder应用中最为常用的模块之一,在此基于上述基础,设计实现了基于模块的FIR数字带通滤波器。 1 基于DSP Builder的滤波系统设计 1.1 FIR滤波器原理 有限冲激响应(Finite Impulse Response,FIR)滤波器是由有限个采样值组成,实现的方式是非递归、稳定的,在满足幅频响应要求的同时,可以获得严格的线性相位特性,因此在高保真的信号处理等领域得到广泛应用。 对于一个FIR滤波器系统,它的冲击相应总是有限长的,其系统函数可记为: 最基本的FIR滤波器可表示为: 式中:z(n)是输入采样序列;h(n)是滤波器系数;L是滤波器阶数;y(n)表示滤波器输出序列,为x(n)和h(n)的卷积。FIR滤波器基本结构如图1所示。 对于一个4阶滤波器子系统其输出可表示为: 可见在这个子系统中共需要4个延时器,4个乘法单元和一个4输入的加法器,并可以根据实际需要选择调用子系统构成多阶滤波器。 1.2 滤波的总体要求及实现

CIC插值滤波器的FPGA设计与实现 摘要:基于多速率信号处理原理,设计了用于下变频的CIC插值滤波器,由于CIC 滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影响参数,借助MATLAB设计符合系统要求CIC 滤波器,并利用Modelsim软件建模仿真,验证CIC滤波器性能是否达到要求。(一)CIC滤波器基本原理 A.CIC滤波器的基本单元 CIC滤波器主要由积分滤波Integrator和梳状滤波Comb两个基本单元部分构成。 典型的CIC滤波器的结构,它由两个基本单元I(积分滤波器)和C(梳状滤波器)级联构成。本设计主要针对插值滤波器,所以插值滤波器的结构示意图如图1-1所示: 图 1-1 3级级联的CIC插值滤波器结构示意图 积分器和梳状滤波器之间是一个采样率转换器,对于CIC插值器而言,它完成在每一个样值后补上R-1个0值的工作,,对于CIC抽取器来说,它完成在实际的抽取工作,每R个样值中取样一个。 R(插值倍数),M(延迟因子,一般取1或者2)以及N(级联级数)是影响CIC 滤波器的三个参数,它们的值需根据通带性能的需求而设定。 (二)CIC插值滤波器的设计流程 根据CIC滤波器的原理,本设计的流程如图2-1所示:

图2-1 CIC 插值滤波器的设计流程图 (三)模型的建立和测试 A .位宽策略 对于数字滤波器,一个不得不考虑的问题是为防止溢出每一级所需的位宽。对于抽取器来说,CIC 滤波器的输出增益为 (*)N G R M = (3-1) 所以,在全精度的情况下,最后一级输出的位宽为 2log (*)out in B B N R M =+ (3-2) 其中in B 表示输入数据的宽度,为了保证精度,每一个积分器和梳状滤波器的输入输出位宽都为out B 。 对于插值器而言,输出增益为 212,1,2,....2(*)/,1, 2......2i i N i N i N G R M R i N N N --?? == ? ? =++?? (3-3) 因此,第i 级为避免溢出所需要的位宽为 2log ()i in i W B G =+ (3-4) 最后一级输出位宽为 22log (*)log out in B B N R M R =+- (3-5) 在实际当中,当差分延时M=1时,为保证稳定,所有积分器的位宽在理论值的基础上加一。 max B 不仅是滤波器输出的最大可能的位数,也是每一级滤波器的最大可能位

长春理工大学毕业设计 摘要 在现代电子系统中,FIR数字滤波器以其良好的线性特性被广泛使用, 随着可编程逻辑器件和EDA技术的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采用FPGA器件来实现FIR 滤波器。 本论文对基于FPGA的FIR数字滤波器实现进行了研究,以FIR数字滤波器的基本理论为依据,并且采用查找表以及线性FIR波器的对称性特点使得硬件规模极大的减小。为了验证仿真结果的正确性,文中应用了MATLAB和VHDL联合仿真方法对设计的电路进行仿真测试,结果达到设计指标。并用MATLAB对仿真结果进行了分析,证明了所设计的FIR数字滤波器功能正确。 关键词: 有限脉冲响应现场可编程门阵列查找表窗函数仿真 ABSTRACT In the modern electrical system, the FIR digital filter is used for many practical applications for its good linear phase character, Along with the development of PLD device and EDA technology, more and more electrical engineers use FPGA to implement FlR filter, as it not only meet the real-time requirement, but also has some flexibility. In this paper, a method to implement the FIR filter using FPGA is proposed. According to the basic theory of FIR filters, the thesis reduces it with the use of multiple coefficient memory banks and the symmetry characteristic of linear FIR filter. In order to make the verification more available, the complex simulation with Matlab and VHDL is used to testify the design whether fulfills the requirement. And also the result of the simulation is analyzed with the use of MATLAB, and it proved that the function of the design is correct. KEYWORDS: FIR FPGA Windows Function Simulation

FIR滤波器的FPGA实现方法 关键字::FIR FFT FPGA 关键字 在数字信号处理系统中,有限脉冲响应(finite impulse response,FIR)数字滤波器是一个非常重要的基本单元。近年来,由于FPGA具有高速度、高集成度和高可靠性的特点而得到快速发展。随着现代数字通信系统对于高精度、高处理速度的需求,越来越多的研究转向采用FPGA来实现FIR滤波器。而对于FIR滤波器要充分考虑其资源与运行速度的合理优化,各种不同的FIR滤波结构各具优缺点,在了解各种结构优缺点后才能更好地选择合适结构来实现FIR滤波。 1FIR数字滤波器 FIR数字滤波器由有限个采样值组成,设计中在满足幅值特性时,还能保证精确、严格的相位特性,因此在信号处理等领域得到广泛的应用。 对于FIR滤波器,其输出y(n)表示为如下形式: 式中:N为滤波器的阶数(或抽头数);x(i)表示第i时刻的输入样本;h(i)为FIR滤波器的第i级抽头系数。 由于FIR滤波器的冲击响应为一个有限序列,其系统函数可表示为: FIR滤波器的基本结构如图1所示。FIR滤波器只在原点处存在极点,所以这使得FIR 滤波器具有全局稳定性。同时FIR滤波器满足线性相位条件,其冲击响应序列为实数且满足奇对称或偶对称条件,即: 2实现方法 运用FPGA来实现FIR数字滤波器的结构多种多样,但是主要有以下几类:串行结构、并行结构、转置型结构、基于FFT算法结构、分布式结构。其他类型的FIR滤波器结构都可以由以上几种结构衍生而来。 2.1串行结构

由表达式(1)可知,FIR滤波器实质是做一个乘累加运算,其滤波器的阶数决定了一次乘累加的次数,其串行结构如图2所示。 串行结构的FIR滤波器结构简单,硬件资源占用少,只需要复用1个乘法器和1个加法器,所以成本较低。但是,这种结构的FIR滤波器要经过多个时钟周期才有输出,同时,内部时钟周期还受到乘法器运算速度的影响,所以该结构的FIR滤波器处理速度慢,只适用于滤波阶数较低且处理速度要求低的系统。 2.2并行结构 将串行结构的FIR滤波器展开就可以得到并行结构的FIR滤波器,并行FIR滤波器结构又称作直接型FIR滤波器结构,这种结构是直接根据图1的滤波器结构,用多个乘法器和加法器并行实现。通常考虑到其滤波器系数的对称性,先对输入值进行加法运算,再进行乘法运算,最后累加输出,以此来减少乘法器的个数,其结构如图3所示。 并行结构的FIR滤波器在1个周期内可以完成1次滤波,运行速度快,虽然利用滤波系数对称性,但仍要占用大量的乘法器和加法器,特别对于滤波阶数高的滤波器,其资源占用较多,如对于256阶的滤波器,其需要128个乘法器来实现。为提高滤波器速度,常引入流水线结构,即在每次加法或者乘法运算后加入1个寄存器存储数据,使得滤波器可以运行在更高的频率上。 2.3转置型结构 根据转置定理,如果将网络中所有的支路方向倒转,并将输入x(n)和输出y(n)相互交换,则其系统函数H(z)不变。通过转置定理,将并行结构的FIR滤波器变换就可以得到转置型FIR滤波器,其结构如图4所示。

32阶FIR滤波器的FPGA实现 随着软件无线电的发展。对于滤波器的处理速度要求越来越高。传统的FIR滤波器一般采用通用DSP处理器,但是DSP处理器采用的是串行运算,而FPGA是现场可编程阵列,可以实现专用集成电路,另外还可以采用纯并行结构及考虑流水线结构,因此在处理速度上可以明显高于DSP处理器。本文采用并行分布式算法在FPGA上设计并实现了高速处理的32阶FIR 低通滤波器,在此过程中利用Matlab的数值计算与分析功能来提高设计效率。 1 FlR低通滤波器的窗函数实现 理想的滤波器频率响应中傅里叶反变换ha(n)一定是无限长的序列,而且是非因果的,而实际要设计的滤波器h(n)是有限长的,因此要用有限长来逼近无限长的,其方法就是用一个有限长度的窗口函数序列ω(n)来截取,即:常见的窗函数有矩形窗、巴特利特窗、汉宁窗、哈明窗、布莱克曼窗、凯泽窗。其中,凯泽窗提供了可变的过渡带宽。本文采用凯泽窗对FIR滤波器进行设计,其窗函数表达式为: I0[·]为第一类变形零阶贝赛尔函数,形状参数β为依赖于滤波器阶数M的参数,用来调整主瓣宽度与旁瓣衰减,选择M可产生各种过渡带宽和接近最优的阻带衰减。给定通带截止频率ωp,阻带起始频率ωs,阻带衰减As,凯泽窗设计中有经典公式可供使用,如下:过渡带宽:滤波器阶数:形状参数:假设低通数字滤波器设计指标如下: 采用上面介绍的凯泽窗,利用Matlab编程计算得到32阶FIR低通滤波器参数如下: 32阶FIR低通滤波器幅频特性图。 上述求得的系数是浮点型的,而在FPGA设计中使用的数据是定点型的,所以在设计滤波器之前要将系数转化为定点型,即系数的量化。在本文中采用数字信号处理(DSP)技术中的Q 值法对系数进行量化。为了兼顾精度和所占用的资源,本文的系数用12位二进制来量化,得到的整数系数结果如下: 2 并行分布式算法原理及FPGA设计 32阶FIR滤波器的差分方程表达式为: 式中:x(n)为输入;y(n)为输出;h(n)为滤波器系数。设x(n)用二进制可表示为: 其中,最高位为符号位。则式(7)可写为: 式(10)为并行分布式算法,由上可以看出并行分布式算法是将滤波器表达式重新排列,分别加权求和。与传统算法最大的不同之处是在FPGA设计过程中以查找表代替乘法器,即根据输入数据的不同,将对应的滤波器系数预先求和保存在ROM中,也就是将每一项的乘法求和通过并行结构查表寻值完成,提高运行速度。具体FPGA实现时,首先将12位的输人数据并行输入到12列32位移位寄存器分别寄存,然后以寄存器中的值为地址,对应于查找表的结果,按照式(10),每列进行相应二次幂加权,最后各列累加,在第32个数据完全输入之后得到正确的滤波器输出。由于输入数据的延迟,在此之前滤波器输出会延迟或者产生不正确的结果,可以在实现过程中加入控制信号进行输出控制。由于查找表的规模是随着地址的增加呈指数增加的,可以将32位的查找表划分为四个8位的查找表,从而降低对ROM的需求。在本设计中可采用多级流水线技术,也就是将在明显制约系统速度的长路径上插入几级寄存器,虽然流水线会影响器件资源的使用量,但它降低了寄存器间的传播时延,允许

www.cismag.com.cn 前沿技术 CIC滤波器的FPGA实现 摘要:本文总结了CIC滤波器理论要点,介绍了采用FPGA设计CIC滤波器的基本方法,使滤波器的参数可以按实际需要任意更改,给出了仿真结果,验证了设计的可靠性和可行性。采用该方法设计的CIC滤波器已用于DDC芯片,也适合下一代高频雷达系统的要求。 上海交通大学电子信息与电气工程学院 石 蔚 黄佩伟 引 言 CIC滤波器是数据通讯中的常用模块,一般用于数字下变频(DDC)和数字上变频(DUC)系统,随着数据传输率的增加,级联梳状滤波器(CIC)的应用变得尤为重要。CIC滤波器的结构简单,没有乘法器,只有加法器、积分器和寄存器,适合工作在高采样率。 工作原理

信息安全与通信保密?2005.6 前沿技术 29

www.cismag.com.cn 前沿技术 参考文献 [1] 杨小牛,楼才义,徐建良。软件无线电原理与应用。电子工业出版社 2001 [2] E.B.Hogenauer.An economical class of digi-tal filters for decimation and interpolation.IEEETransactions on Acoustics,Speech and SignalProcessing,ASSP-29(2):155-162,1981 [3] Sophocles J.Orfanidis.。信号处理导论。影印版 清华大学出版社 [4] 袁俊泉,孙敏琪,曹瑞。Verilog HDL数字系统设计及其应用。西安电子科技大学出版社 2002 [5] 宋千,陆必应,梁甸农。基于FPGA的FIR滤波器高效实现。信号处理 2001,17(5):385-391 [6] 郭继昌,李香萍,腾建辅。基于位串行分布式算法和FPGA实现FIR电路的研究。电子测量与仪器学报 200115 (2):15-21 Xilinx Inc.,Spartan-II 2.5v FPGA Family:Func-tional Description.2001

目录 引言 (5) 第一章 FPGA的设计流程 (6) 1.1 FPGA概述 (6) 1.2 FPGA设计流程 (8) 1.3硬件描述语言HDL(Hardware Description Language) (10) 1.4 FPGA开发工具Quartus Ⅱ软件设计流程 (11) 第二章有限冲激响应(FIR)滤波器的原理及设计 (14) 2.1数字信号处理基础原理 (14) 2.2 FIR滤波器背影知识 (17) 2.3 FIR数字滤波器原理 (18) 2.4 利用窗函数法设计FIR滤波器 (22) 第三章 FIR 数字滤波器的FPGA实现 (27) 3.1串行FIR滤波器原理 (27) 3.2分布式算法基础 (27) 3.3直接型FIR滤波器的原理结构图 (30) 3.4具有转置结构的FIR滤波器 (31) 第四章结论与总结 (36) 辞 (37) 参考文献 (38)

摘要:本论文课题是《基于FPGA的FIR滤波器设计与实现》。数字滤波器是语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中的一种基本的处理部件,它能满足滤波器对幅度和线性相位的严格要求,避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。有限冲激响应(FIR)滤波器能在设计任意幅频特性的同时保证严格的线性相位特性。因此在许多应用领域都显示了强大的生命力,具有重要应用意义。本文介绍了用VHDL 实现线性相位FIR(有限长单位冲激响应)滤波器。提出了一种基于FPGA 的FIR滤波器设计方案。介绍了基于FPGA的FIR滤波器的数字信号处理的算法设计,采用直接型和转置型的基本结构来设计,其运算效率明显提高,并结合先进的EDA软件进行高效的设计和实现,并给出了用Quartus Ⅱ运行的仿真结果。该设计对FPGA硬件资源的利用高效合理,用VHDL编程,在PFGA中实现了高采样率的FIR滤波器。 关键字:FIR滤波器;FPGA;VHDL;MATLAB;Quartus Ⅱ

目录 摘要................................................................ I Abstract ............................................................ X 1 绪论.. (1) 1.1 课题的目的和意义 (1) 1.2 FPGA技术的发展及应用 (2) 1.3 FPGA软件设计工具Quartus II (3) 2 FIR数字滤波器的理论研究及分析 (5) 2.1 数字滤波器的理论基础 (5) 2.2 数字滤波器的分类 (5) 2.3 FIR数字滤波器的设计方法 (6) 3 FPGA DSP系统设计分析 (7) 3.1 DSP的基本概念 (7) 3.2 FPGA实现DSP的特点 (8) 3.3 DSP Builder设计工具及设计规则 (9) 4 基于FPGA的FIR低通滤波器设计 (12) 4.1设计方案 (12) 4.2 FDATool滤波器设计 (12) 4.3 FPGA定点数的确定 (14) 4.3.1导出系数文件 (14) 4.3.2 FPGA定点数转换 (15) 4.4 FIR滤波器模型的建立 (17) 4.4.1乘加子系统的搭建 (17) 4.4.2 滤波器模块的添加和模块参数设置 (21)

4.4.3各模块的连接 (27) 5 Simulink仿真 (29) 5.1 仿真时间设定 (29) 5.2 示波器模块显示 (29) 5.3 仿真结果分析 (31) 6 总结 (33) 参考文献 (34) 致谢 (35) 附录 (36) 附录1 FIR滤波器仿真模型图 (36) 附录2 FIR滤波器测试模型图 (37) 附录3 FPGA定点数转换程序 (37)

如何用用FPGA实现FIR滤波器 你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重要的?做这个设计的最佳方法是什么?还有这个设计 应该怎样在FPGA中实现?现在有大量的低成本IP核和工具来帮助你进行设计,因为FIR 是用FPGA实现的最普通的功能。 基础和主要参数 也许你在听FIR滤波器课时不够专注。这里做一个快速的复习,最简单的形式是,FI R 滤波器的输出y(n)是求采样数据x(n) 的N个输入的平均值。存储的每个采样称为抽头。当然大多数设计都比这个复杂,要提供优化的滤波器特性,要用系数乘每个抽头,或者对h(i) 进行加权。

图1 典型的FIR滤波器结构(完全并行) 用于FIR滤波器的主要参数是通带、阻带、阻带衰减和通带波纹。对于某些应用,阻带波纹也许是重要的和规定的。然而对大多数应用,阻带衰减是适当的。还有输入采样率,以及与输入数据分辨率一起的所要求的输出采样率。 图2 低通滤波器规范 你也许只是接受任务,而由你自己选择设计规范。当然应用项目定义了许多规范。这里有一些指导意见,帮助你缩小各种可能性,评估权衡设计。 通常通带越接近阻带,设计就越具挑战性。同样,指定通带很低的波纹,或者很高的阻带衰减增加了设计的复杂性。必须牢记,指定波纹和衰减为数据的分辨率,你必须满足设计

要求。指定衰减的要点是小于输入数据的最低位。同样在满标度中指定小于1位的通带波纹是不必要的。如同其它的滤波器,FIR滤波器可构成低通、高通和带通滤波器。 表1 数据宽度相对于阻带衰减和通带波纹 输入至输出的采样率也会影响你的设计。在简单的设计中,输入速率和输出速率是相等的。然而,在许多低通滤波器设计中,输出以输入的速率运行是不经济的,因为传输信息不要求高的输出率。取十分之一速率的FIR是合适的。其它要求较高输出率的设计,则采样内插F IR。 进行设计 选择FIR滤波器的系数有两种方法。Parks-McClellan方法(执行Remez算法)和进行冲击响应的窗口操作。窗口方法依赖于一个事实,要求频率响应的离散Fourier反变换代表FI R滤波器的系数。理想的频率响应用作起始点,于是应用窗功能减少系数的数目,成形频率响应。通用的窗功能包括矩形、三角、Hanning、Hamming、Kaiser 和Blackman。

基于FDAtool及FPGA的FIR滤波器设计 首先fdatool是Matlab自带的一个数字滤波器的设计分析软件,里面提供了丰富的参数供调整(具体的参阅Matlab的教材),大大降低了数字滤波器的设计难度,同时又可以设计出高质量的滤波器。fdatool虽然不是最好的滤波器设计软件,但是在Matlab响亮的名号下,得到了广泛的使用。FIR Megacore是Altera针对其主流FPGA推出的一款商业化的数字滤波器设计软件,可以直接生成HDL代码(可综合的,但是加密了),同时其结构针对Altera自己的FPGA 做了各种各样的优化。尽管fdatool也可以生成可综合的HDL代码,但是没有针对FPGA的M4K、DSP Block做出相应的优化,所以性能和FIR Megacore生成的FIR滤波器有相当的差距。然而,FIR Megacore的滤波器设计工具相当的简单,只提供了窗函数法,用户只能定义有限的几个参数。而其他的设计方法,比如矩形系数更好的等纹波法则只能在fdatool里面找到。所幸的是,FIR Megacore提供了滤波器的Coefficients导入的选项,可以使用第三方工具生成的Coefficients。这使得我们能够用FIR Megacore来实现fdatool生成的滤波器。简要流程如下: Step-1:在Matlab的命令行上输入:fdatool,启动Filter Design & Analyze Tool;

Step-2:Filter Design & Analyze Tool(fdatool)的主界面;

Step-3:基于等纹波法设计一个FIR滤波器;

附件B: 基于FPGA的数字滤波器设计 毕业设计(论文)开题报告 1.课题的目的及意义(含国内外的研究现状分析或设计方案比较、选型分析等) 随着信息时代和数字世界的到来,数字信号处理已成为当今一门极其重要的学科。数字信号处理在通信、语音、图像、自动控制、雷达、军事、航空航天、医疗和家用电器等众多领域得到了广泛的应用。在数字信号处理应用中,数字滤波器显得尤为重要。在很多应用场合,数字滤波器逐渐取代了模拟滤波器。 数字滤波器是对数字信号实现滤波的离散时间系统,它将输入的数字序列通过特定运算转变为所需的数字序列。根据冲激响应函数的时域特性,可将数字滤波器分为两种,即无限长冲激响应IIR滤波器和有限长冲激响应FIR滤波器。数字滤波器一般由数字乘法器、加法器和延时单元组成的一种算法或装置。它可用计算机软件实现,也可用大规模集成数字硬件实现。本文所述是基于FPGA的设计方法。模拟滤波器分为有源和无源的,有源滤波器主要由集成运放、电阻、电容构成。无源的滤波器主要由R,L,C构成[1]。其物理构成导致存在电压漂移、温度漂移和噪声等问题。模拟滤波器还存在一个严重的问题,当技术指标改变时,其常常要更换电容、电感等元件,相当繁琐。相比于模拟滤波器,数字滤波器有以下优点:①数字滤波器对外界环境不太敏感,具有更高的可靠性;②可以实现精确的线性相位和多速率处理等模拟滤波器无法实现的功能;③提高字长,可以实现任意精度的信号处理;④数字滤波器实现更加灵活,并能同时进行信号的存储[2]。 FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[3]。 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA 具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑

一、概述 在通信与信息技术领域,数字信号处理显得越来越重要了,数字滤波器在数字信号处理中起到重要作用并能够获得广泛应用。数字滤波器根据频域特性可以分为低通、高通、带通和带阻四种基本类型,根据时域特性可以分为无限脉冲响应IIR(Infinte Impulse Response)和有限脉冲响应FIR(Finite Impulse Response)。FIR滤波器具有良好的线性相位特性,因此在数据通信、图像处理方面有广泛的应用。 FPGA(Field Programmable Gate Array),即现场可编程门阵列,由于具有用户可编程性,能够实现用户规定的各种用途,因此又被称为可编程专用集成电路,在电子系统的设计中得到广泛的应用。利用FPGA实现FIR数字滤波器的设计,是本次课程设计需要解决的问题,利用学过的知识实现FIR数字滤波器是本次课程设计的主要内容。 二、方案论证 1.FIR数字滤波器是一种线性时不变系统(LTI),如果FIR数字滤波器的单位脉冲响应h(n)的长度为N,其传递函数和差分方程分别为: H(z) = ∑ =- 1- 0 n 1 ) ( N z n h y(n) = x(n)*h(n) =∑- =- 1 ) ( ) ( N m m n x m h 其中,x(n)和y(n)分别为输入和输出序列。如果FIR数字滤波器的单位脉冲响应h(n)是实数序列,而且满足偶对称或者奇对称条件,即 h(n) = h(N-1-n) 或者 h(n) = -h(N-1-n) 则滤波器具有严格的线性相位特点。正是因为这种特点,在滤波器的设计过程中,可使乘法器的数量减半。对于n阶滤波器,当n是偶数时,乘法器的个数为n/2个,当n 为奇数时,乘法器的个数为(n+1)/2个。 由传递函数和差分方程可以直接画出FIR滤波器的直接型结构如图1所示。 1-1-1-1- y(n) 图1 FIR滤波器的直接型结构

福建电脑 2006年第3期2并行快速FIR滤波器的FPGA实现 张海波,陈新华 (山东科技大学信息科学与工程学院山东青岛271019) 【摘要】基于对传统的2并行FIR滤波器算法的分析,对2并行FIR滤波器结构的比较,利用以加法数量的增加来减少乘法数量来实现低复杂度的2并行FIR滤波器,用ALTERA公司的QuartusII软件进行仿真。 【关键词】FIR;滤波器;QuartusII;FPGA在任何数字信号处理系统中,FIR滤波器是最基本的处理单元之一。FIR滤波器本用于DSP应用中,其范围覆盖从视频,图象处理到无线通信的应用。将并行处理用于数字FIR滤波器,可以提高原始滤波器的有效吞吐量。通常,并行处理应用于FIR滤波器将涉及原始滤波器的硬件单元的重复使用,由于并行处理带来的硬件开销是无法容忍的。因此,实现比传统并行FIR滤波器结构面积消耗更小的并行FIR滤波器结构是非常有益的。 1传统的2并行FIR滤波器 在时域,一个N抽头的FIR滤波器可表示为: y(n)=h(n)*x(n)=N-1 i=0 !h(i)X(n-i),n=0,1,2... x(n)是一个无限长的输入序列,序列{h(n)}包含了长度为N的FIR滤波器的系数 在z域中可以表示为: Y(z)=H(z)*X(z)=N-1 n=0!h(n)z -n ∞ n=0 !x(n)z -n 输入序列{x(0),x(1),x(2)……}可以分为奇数和偶数部分:X(z)=x(0)+x(1)z-1+x(2)z-2+......=x(0)+x(2)z-2+x(4)z-4+......+x(1)z-1+x(2)z-3+x(4)z-5+......=X0(z2)+z-1X1(z2) 其中,X0(z2)和X1(z2)分别是x(2k)和x(2k-1)的z变换。同样H(z)=H0(z2)+z-1H1(z2)则Y(z)=Y0(z2)+z-1Y1(z2)= (X0(z2)+z-1X1(z2))(H0(z2)+z-1H1(z2))=X0(z2)H1(z2)+z-1X0(z2)H1(z2)+X1(z2)H0(z2)+z-2X2(z2)H2(z2) Y0(z2)=X0(z2)H0(z2)+z-2X1(z2)H1(z2) Y1(z2)=X0(z2)H1(z2)+z-2X1(z2)H1(z2) (1)其中,Y0(z2)和Y1(z2 )分别对应时域里的y(2k)和y(2k+1) 图1传统的2并行FIR滤波器 Fig.12parallelFIRwavefilter 22并行快速FIR算法 (1)式可以写为Y0=H0X0+z-2H1X1 Y1=(H0+H1)(X0+X1)-H0X0-H1X1 可以看到,这个2并行滤波器包括5个子滤波器,H0X0和 H1X1是公共项。 图2低复杂度2并行FIR滤波器 Fig.2lowcomplexity2parallelFIRfilter 33并行快速FIR滤波器 对于3并行快速FIR滤波器算法可以通过递归为2并行FIR滤波器算法来实现。4实例分析 当N=6,H={h0,h1,h2,h3,h4,h5},它的子滤波器为:H0={h0,h2,h4},H1={h1,h3,h5} H0+H1={h0+h1,h2+h3,h4+h5}是可以先计算出来的,这个2并行滤波器需要9次乘法和10次加法,而传统的2并行滤波器则需要12次乘法和10次加法。而且随着N的增加,需要的乘法器 和加法器会明显减少。5ALTERAFPGA简介 现场可编程门阵列FPGA是有许多微小的逻辑单元组成的内部阵列,单元间的连接通过其周围的布线通道互连实现,逻辑单元及布线通道可由用户现场配置。近几年来,由于微电子技术的迅猛发展,使得FPGA的性能指标也大大改进,规模越来越大,功能越来越全,时间性能越来越好。因而FPGA在数字系统设计中占据了越来越重要的位置。6QuartusII简介 ALTERA公司的QuartusII软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。它根据设计者的需要提供了一个完整的多平台开发环境,包括了整个FPGA的设计阶段的解决方案。 图3QuartusII软件开发流程 Fig.2QuartusIISoftwaredevelopmentprocedure7 算法的verilog描述及其仿真结果 modulezhb(clk,clk2,x_in,y_out);inputclk;input[7:0]x_in;output[7:0]y_out;outputclk2; 167