多谐振荡器-非门

一、原理

与非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。

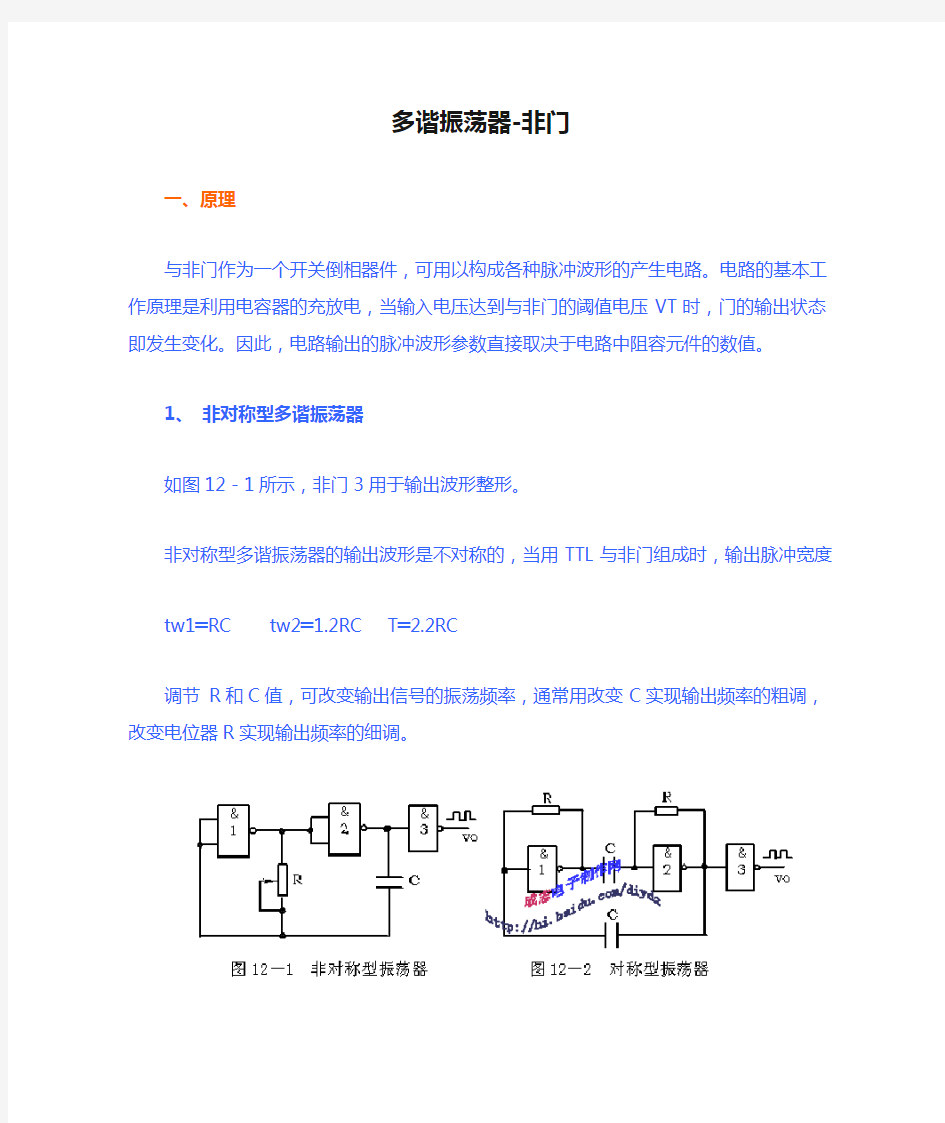

1、非对称型多谐振荡器

如图12-1所示,非门3用于输出波形整形。

非对称型多谐振荡器的输出波形是不对称的,当用TTL与非门组成时,输出脉冲宽度

tw1═RC tw2═1.2RC T═2.2RC

调节 R和C值,可改变输出信号的振荡频率,通常用改变C实现输出频率的粗调,改变电位器R实现输出频率的细调。

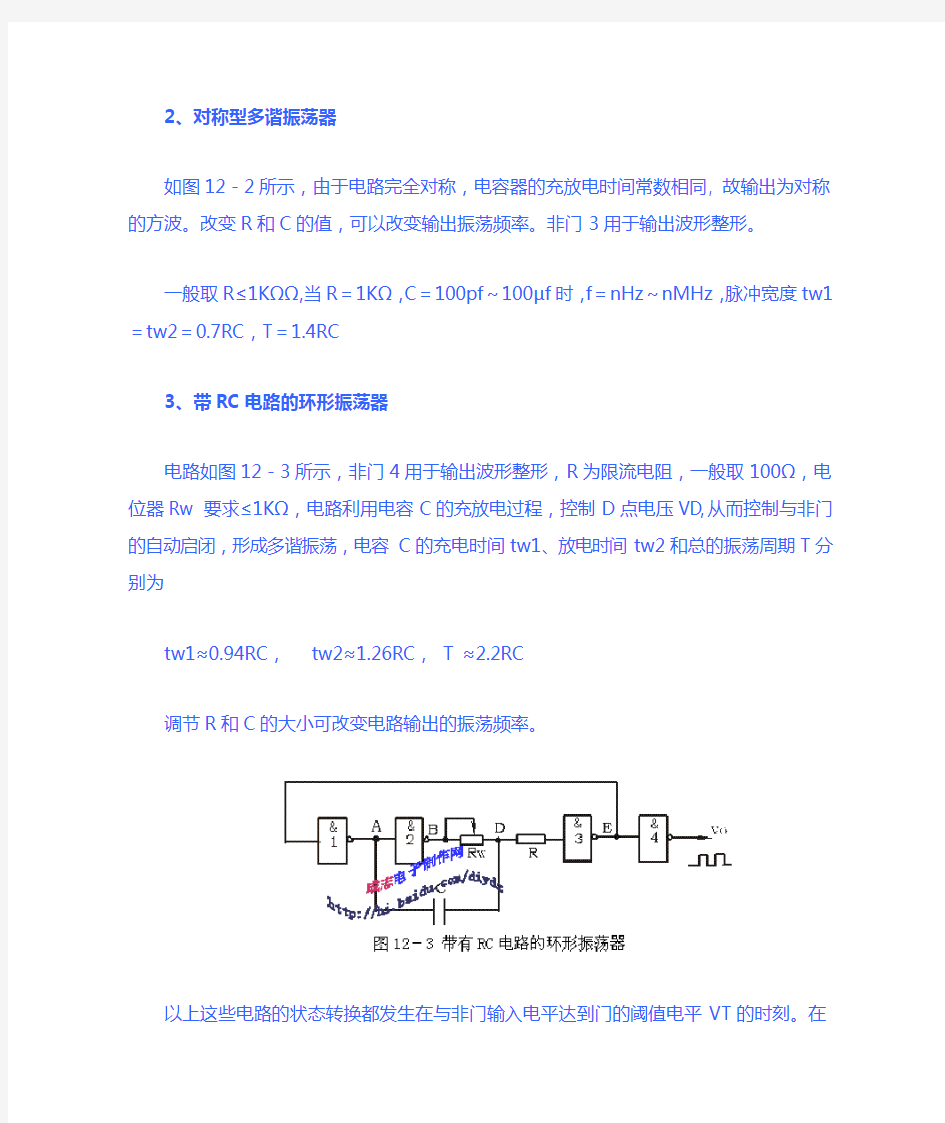

2、对称型多谐振荡器

如图12-2所示,由于电路完全对称,电容器的充放电时间常数相同, 故输出为对称的方波。改变R和C的值,可以改变输出振荡频率。非门3用于输出波形整形。

一般取R≤1KΩ?,当R=1KΩ,C=100pf~100μf时,f=nHz~nMHz,脉冲宽度tw1=tw2=0.7RC,T=1.4RC

3、带RC电路的环形振荡器

电路如图12-3所示,非门4用于输出波形整形,R为限流电阻,一般取100Ω,电位器Rw 要求≤1KΩ,电路利用电容C的充放电过程,控制D点电压VD,从而控制与非门的自动启闭,形成多谐振荡,电容C的充电时间tw1、放电时间tw2和总的振荡周期T分别为

tw1≈0.94RC,tw2≈1.26RC,T ≈2.2RC

调节R和C的大小可改变电路输出的振荡频率。

以上这些电路的状态转换都发生在与非门输入电平达到门的阈值电平VT的时刻。在VT附近电容器的充放电速度已经缓慢,而且VT本身也不够稳定,易受温度、电源电压变化等因素以及干扰的影响。因此,电路输出频率的稳定性较差。

4、石英晶体稳频的多谐振荡器

当要求多谐振荡器的工作频率稳定性很高时,上述几种多谐振荡器的精度已不能满足要求。为此常用石英晶体作为信号频率的基准。用石英晶体与门电路构成的多谐振荡器常用来为微型计算机等提供时钟信号。

图12-4所示为常用的晶体稳频多谐振荡器。

(a)、(b)为TTL器件组成的晶体振荡电路;

(c)、(d)为CMOS器件组成的晶体振荡电路,一般用于电子表中,其中晶体的f0=32768Hz。

图12-4(c)中,门1用于振荡,门2用于缓冲整形。Rf是反馈电阻,通常在几十兆欧之间选取,一般选22MΩ。R起稳定振荡作用,通常取十至几百千欧。C1是频率微调电容器,C2用于温度特性校正。

多谐振荡器双闪灯电路设计与制作 南昌理工学院张呈张海峰 我们主张,电子初学者要采用万能板焊接电子制作作品,因为这种电子制作方法,不仅能培养电子爱好者的焊接技术,还能提高他们识别电路图和分析原理图的能力,为日后维修、设计电子产品打下坚实的基础。 上一篇文章《电路模型设计与制作》我们重点介绍了电路模型的概念以及电流、电压、电阻、发光二极管、轻触开关等基本知识,并完成了电路模型的设计与制作,通过成功调试与测试产品参数,进一步掌握了电子基础知识。 本文将通过设计与制作多谐振荡器双闪灯,掌握识别与检测电阻、电容、二极管、三极管。掌握识别简单的电路原理图,能够将原理图上的符号与实际元件一一对应,能准确判断上述元件的属性、极性。

一、多谐振荡器双闪灯电路功能介绍 图1 多谐振荡器双闪灯成品图

多谐振荡器双闪灯电路,来源于汽车的双闪灯电路,是经典的互推互挽电路,通电后LED1和LED2交替闪烁,也就是两个发光二极管轮流导通。 完成本作品的目的是为了掌握识别与检测电阻、电容、二极管、三极管。掌握识别简单的电路原理图,能够将原理图上的符号与实际元件一一对应,能准确判断上述元件的属性、极性。。 该电路是一个典型的自激多谐振荡电路,电路设计简单、易懂、趣味性强、理论知识丰富,特别适合初学者制作。 二、原理图 图2 多谐振荡器双闪灯原理图 三、工作原理 本电路由电阻、电容、发光二极管、三极管构成典型的自激多谐振荡电路。在上篇文章中介绍了电阻、和发光二极管,本文只介绍电容和三极管。 1、电容器的识别

电容器,简称电容,用字母C表示,国际单位是法拉,简称法,用F表示,在实际应用中,电容器的电容量往往比1法拉小得多,常用较小的单位,如微法(μF)、皮法(pF)等,它们的关系是: 1法拉(F)=1000000微法(μF),1微法(μF)=1000000皮法(pF)。 本的套件中使用了2个10μF的电解电容,引脚长的为正,短的为负;旁边有一条白色的为负,另一引脚为正。电容上标有耐压值上25V,容量是10μF。 2、三极管的识别 三极管,全称应为半导体三极管,也称双极型晶体管,晶体三极管,是一种电流控制电流的半导体器件。其作用是把微弱信号放大成幅值较大的电信号, 也用作无触点开关,俗称开关管。套件中使用的是NPN型的三极管9013,当把有字的面向自己,引脚朝下,总左往右排列是发射极E,基极B,集电极C。如图3所示。 图3 三极管的引脚图 晶体三极管具有电流放大作用,其实质是三极管能以基极电流微小的变化量来控制集电极电流较大的变化量。这是三极管最基本的和最重要的特性。我们将ΔIc/ΔIb的比值称为晶体三极管的电流放大倍数,用符号“β”表示。电流放大倍数对于某一只三极管来说是一个定值,但随着三极管工作时基极电流的变化也会有一定的改变。 晶体三极管的三种工作状态: (1)截止状态 当加在三极管发射结的电压小于PN结的导通电压,基极电流为零,集电极电流和发射极电流都为零,三极管这时失去了电流放大作用,集电极和发射极之间相当于开关的断开状态,我们称三极管处于截止状态。

课程设计任务书 学生姓名:专业班级:电子1003班 指导教师:封小钰工作单位:信息工程学院 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15)

多谐振荡器双闪灯电路设计与制作 一、电路设计功能介绍 这是电子技术入门者要做的第一个电子产品,做这个产品的主要目的是为了学会识别与检测电阻、电容、二极管、三极管。学会识别简单的电路原理图,能够将原理图上的符号与实际元件一一对应,能准确判断上述元件的属性、极性。 分立元件双闪灯电路,来源于汽车的双闪灯电路,是经典的互推互挽电路,通电后LED1和LED2交替闪烁也就是两个发光二极管轮流导通。 二、多谐振荡器双闪灯电路原理图

三、多谐振荡器双闪灯电路工作原理 该电路是一个典型的自激多谐振荡电路,套件电路简单、易懂、趣味性强、理论学习知识丰富,特别适合初学者制作。 工作原理:当接通电源后,两只三极管就要争先导通,但由于元器件的差异性,只有某一只管子最先导通。然后电路中两只三极管便轮流导通和截止,两只发光二极管就不停地循环发光。改变阻值或电容的容量可以改LED闪烁的速度。 电路通电时,假设V1优先导通,则C1通过R1开始充电,由于充电时电容相当于短路,所以V2基极近似接地,故V2截止。此时LED1点亮,LED2熄灭。当C1充电毕,V2基极为高点平,故导通,LED被点亮,同时C1上电荷被泄放,V1截止,LED1熄灭。C2通过R2充电,充电毕V1又导通,电路如此循环,两个LED交替闪烁。四、多谐振荡器双闪灯电路元件清单及实物图

双闪灯元件清单实物图 五、调试技巧及成品图 双闪灯电路安装成功后,接上5V直流电压,或者用三节5号电池供电。如下图所示:

正常情况下,可以观察到二只LED发光二极管轮流闪烁,如果没有出现我们需要的功能,应该从以下几个方面调试、检修。 1、检测焊接线路是否正常连通,可用万用表检测每条线路是否导通。因为初次焊接的时候,经常出现虚焊、假焊、漏焊等焊接故障。 2、检测每个元件是否安装正确,特别是发光二极管的正负极性是否正确。 3、用万用表测试电源电压是否正常。 4、发光二极管的限流电阻是否用错,初学者容易把220欧姆的电阻与100K欧的电阻搞混了。 5、测试下电容C1、C2的正极的电压是否改变,如果没有改变要检测三极管是否焊接正确。 经过上面几个步骤的检测,相信一定能排除故障,实现我们需要的目的。 主要焊接毛病有: 1、堆积 2、虚焊 3、尖角

成绩评定表

课程设计任务书

目录 1 绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2 四输入与非门电路 (2) 2.1电路原理图 (2) 2.2四输入与非门电路仿真观察波形 (2) 2.3四输入与非门电路的版图绘制 (3) 2.4四输入与非门版图电路仿真观察波形 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:电路原理图网表 (9) 附录二:版图网表 (10)

1 绪论 1.1 设计背景 tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。 2.用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。 3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。 4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

四位与非门的电路设计 一、课程设计的目的 1、学会使用电路设计与仿真软件工具Hspice ,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice 内部元件库。通过该实验,掌握Hspice 的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2、本次课程设计是用Hspice 软件来实现对四位与非门电路的设计与仿真,熟悉用MOS 器件来设计四位逻辑输入与非门电路,了解用MOS 器件设计与TTL 与非门的优缺点。 二、课程设计的内容和要求 1、内容:用仿真软件HSPICE ,用网表文件来描述模拟电路; 2、要求:用MOS 器件来设计四位逻辑输入与非门电路。 三、设计的原理 1、四输入与非门符号图及原理 A OUTPUT NAND4 1 2 3 45 D C B 真值表如下所示

A B C D Y 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。每个输入端连到一个N沟道和一个P沟道MOS管的栅极。当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。设计电路图如下图所示:

目录 1绪论 (2) 1.1 设计背景 (2) 1.2设计目标 (2) 2与门电路设计 (3) 2.1电路原理 (3) 2.2电路结构 (3) 2.3与门电路仿真波形 (4) 2.4与门电路的版图绘制及DRC验证 (5) 2.5与门电路版图仿真 (6) 2.6 LVS检查匹配 (6) 总结 (8) 参考文献 (9) 附录一版图网表: (10) 附录二电路图网表 (12)

1绪论 1.1 设计背景 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用MOS场效应管实现二输入与门电路。 2.用tanner软件中的原理图编辑器S-Edit编辑反相器电路原理图。 3.用tanner软件中的W-Edit对反相器电路进行仿真,并观察波形。 4.用tanner软件中的L-Edit绘制反相器版图,并进行DRC验证。 5.用W-Edit对反相器的版图电路进行仿真并观察波形。 6.用tanner软件中的layout-Edit对反相器进行LVS检验观察原理图与版图的 匹配程度。

多谐振荡器设计报告 一、实验要求 产生矩形波的频率可以通过电压控制,实现压控振荡。并且在电压调整的过程中波形不会出现振荡、过冲、毛刺等不稳定现象,能够稳定地产生方波。设计报告中应该包括电路截图、仿真截图、仿真分析等实验数据。 二、多谐振荡器相关简介 随着电子产业的发展以及要求,各种稳定的波形产生器成为不可缺少的一部分,而方波是其中比较有代表性的一个波形。方波在各个行业及日常生活中得到了广泛的应用,如电路中的定时器、分频器、脉冲信号发生器等都需要方波产生电路。而多谐振荡器则是一种在接通电源后,就能产生一定频率和一定幅值矩形波的自激振荡器,常作为脉冲信号源。由于多谐振荡器在工作过程中没有稳定状态,故又称为无稳态电路。尽管多谐振荡器有多种电路形式,但它们都具有以下结构特点:电路由开关器件和反馈延时环节组成。开关器件可以是逻辑门、电压比较器、定时器等,其作用是产生脉冲信号的高、低电平。反馈延时环节一般为RC电路,RC电路将输出电压延时后,恰当地反馈到开关器件输入端,以改变其输出状态。 三、实验方案确定 本次实验是通过施密特触发器与晶体管来构成多谐振荡器电路的开关器件,RC电路来构成反馈延时环节,再加入电压控制部分实现振荡频率的控制。

四、实验内容 1、施密特触发器的制作 a、原理图简要分析。电路主要部分为Q2管与Q3管两个导向器相连,再在输入与输出两个端口加上Q1管与Q4管构成的射极跟随器进行隔离,从而得到更好的频率特性,使输出的波形不会出现毛刺、过冲、振荡等不稳定现象,并且在压控电路中不会对其它部分有较大影响。其电路图如下: b、施密特电路调试。为了使电路能够很好地工作,分析原理图可知,电路的上下门限电压由电阻RC1、RC2、RE决定,而射极跟随器的射极电阻RE1与RE2主要影响电路的输入与输出阻抗,同时对电路的频率特性也有一定的影响。因此,在电路仿真调试的过程可以有目的性的进行元器件参数设置。电路调试的截图如下:

多谐振荡器的研究与仿真 时间:2009-05-05 13:33:30 来源:电子技术作者:何香玲青岛理工大学 O 引言 在数字系统电路中经常用到多谐振荡器。多谐振荡器是一种自激振荡器,在接通电源以后,不需要外加触发信号便能自行产生一定频率和一定宽度的矩形波,这一输出波形用于电路中的时钟信号源。由于矩形波中含有丰富的高次谐波分量,所以习惯上又将矩形波振荡器称为多谐振荡器。按照电路的工作原理,多谐振荡器大致分为无稳态多谐振荡器和单稳态多谐振荡器。 1 无稳态多谐振荡器 1.1 采用TTL门电路构成的对称式无稳态多谐振荡器 对称式多谐振荡器的典型电路如图1所示,它是由两个反相器Gl、G2经耦合电容C1、C2连接起来的正反馈振荡电路。电路中G1和G2采用SN74LS04N反相器,RFl=RF2=RF, C1=C2=C,振荡周期T≈1.3RFC,输出波形的占空比约为50%。RF1、RF2的阻值对于LSTTL 为470 Ω~3.9kΩ,对于标准TTL为0.5~1.9kΩ之间。 1.2 采用CMOS门电路构成的非对称式无稳态多谐振荡器 如果把对称式多谐振荡器电路进一步简化,去掉C1和R2,在反馈环路中保留电容C2,

电路仍然没有稳定状态,只能在两个暂稳态之问往复振荡,电路如图2所示。 假定G2输出为1,电容C充电,在充电开始VI1也为1。因此,该电压经Rp力口到G1输入端,Gl输出为O,电路稳定工作,C继续充电。充电电流随着充电时间延长而减小,RF 两端电压下降,若降到Gl的阈值电压以下,则G1输出变为1,G2输出变为0,C反向充电。随着充电的进行,VI1达到Gl的阈值电压时,G1输出变为0,G2的输出变为1,该动作重复进行而产生振荡。电容C的充放电时间分别为T1=RfC1h3,T2=RfC1n3,振荡周期T=T1+T2=2RFC1h3≈2.2 RFC,输出波形的占空比为50%。 在电路的G1输入端串接的保护电阻RP是为了减少电容C充放电过程中CMOS门电路输入保护电路承受较大的电流冲击,且Rp>>RF。 1.3 门电路无稳态环形振荡器 利用门电路地传输延迟时间将奇数个反相器首尾相接可构成一个基本环形振荡器,电路的振荡周期为T=2ntpd,n为串联反相器的个数。作为数字系统的时钟信号源,由CMOS 反相器构成的环形振荡器具有结构简单、集成度高、功耗低的优点,因此得到了广泛地应用。随着CMOS集成电路工艺技术的发展,当前,其振荡频率已达到数+GHz。但是,这种利用反相器的延时特性构成的环形振荡器,只能产生高频信号。为了构成低频和超低频环形振荡器,一种解决方法是在此电路的基础上附加RC延迟环节,组成带有RC延迟电路的环形振荡器,电路如图3(a)所示。另一种解决方法是根据单稳态触发器的延时作用,运用环形振荡

实验一二输入端与非门的设计 利用EDA-V+板,使用Quartus II 9.0软件,完成实验内容。 二输入端与非门有2个输入端,1个输出端。在 EPM7128SLC84-15芯片内实现功能,选择合适的引脚。1. 实验目的 掌握Quartus II 9.0软件的使用; 学会实验箱EDA-V+资源的使用。 2. 实验原理 2二输入端与非门有2个输入端:A、B;1个输出端Y。其真值表如表1所示。 表1 4选1二输入端与非门真值表 地址输入输出 A B Y 0 0 1 0 11 10 1 110 3. 实验步骤

(1 建立工程项目: 确定具有合法的密码文件后,安装进入如下提示: 图1 点击NEXT进入建立工程对话窗口: 图2

或者,从主菜单选取File→New Project Wizard,同样出现图 2。来创建工程。 图3 从主下拉菜单主选择路径新建工程项目 出现对话框如图4所示。 图4 新建工程

更改工程保存的路径为D:\EDA_test\2nand,工程名称为2nand,文件名称为2nand,点击Next,提示是否创建“D:\EDA_test\2nand”? 选择“是”,出现: 在上图中的File name对话框内输入2nand.bdf,

然后,点击右侧的Add。 图3 添加文件到工程中 接着点击Next,在下图中选择所使用的器件。在 Family“系列”下拉窗口中选择MAX7000S,在Available devices 下选择EPM7128SLC84-15具体器件。

图4 选择器件 在图4中,点击Next进入图5。 图5 选择第三方工具 在图5中取默认值,直接点击Next进入图6。

数字电路设计报告 设计课题:使用门电路产生脉冲信号——自激多谐振荡器 专业班级:13电信卓越班 学生姓名:陈军波 学号:130807002 指导教师:许粮老师 设计时间:2014年12月27日

自激多谐振荡器 一、设计任务与要求 1. 掌握使用门电路构成信号脉冲信号产生电路的基本方法; 2. 掌握影响输出脉冲波形参数的定时原件数值的计数方法; 3. 学习石英晶体稳频原理和使用石英晶体构成振荡器的方法; 4.掌握555集成时基电路的基本应用。 二、方案设计与论证 1.方案一、对称型多谐振荡器 2. 两个反相器G1,G2

非称型多谐振荡器设计 3.方案三、石英晶体稳频的多谐振荡器 图3 石英晶体稳频多谐振荡器 4.方案四 使用555定时器接成的多谐振荡器 方波

图4555构成的多谐振荡器三、单元电路设计与参数计算

如图3所示。当要求多谐振荡器的工作频率稳定性很高时,上述几种多谐振荡器的精度已不能满足要求。为此常用石英晶体作为信号频率的基准。用石英晶体与门电路构成的多谐振荡器常用来为微型计算机等提供时钟信号。石英晶体具有很好的选频特性。当振荡信号的频率和石英晶体的固有谐振频率相同时,石英晶体呈现很低的阻抗,信号很容易通过,而其它频率的信号则被衰减掉。因此,将石英晶体串接在多谐振荡器的回路中就可组成石英晶体振荡器,这时,振荡频率只取决于石英晶体的固有谐振频率f0,而与RC无关。另外,石英晶体不但频率特性稳定,而且品质因数Q很高,有极好的选频特性。石英晶体的频率稳定度可达,可满足大多数数字系统对频率稳定度的要求。 所以,石英晶体振荡器的周期为:T=RC 取fo=32768HZ,R=1K,电容C=0.05uf

课程名称Course 集成电路设计技术 项目名称 Item 二输入与非门、或非门版图设 计 与非门电路的版图: .spc文件(瞬时分析): * Circuit Extracted by Tanner Research's L-Edit / Extract ; * TDB File: E:\cmos\yufeimen, Cell: Cell0 * Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:03 .include H:\ VPower VDD GND 5 va A GND PULSE (0 5 0 5n 5n 100n 200n) vb B GND PULSE (0 5 0 5n 5n 50n 100n) .tran 1n 400n .print tran v(A) v(B) v(F) * WARNING: Layers with Unassigned AREA Capacitance. *

*

* * WARNING: Layers with Unassigned FRINGE Capacitance. * * * 目录 摘要 (1) 第一章电路设计 (1) 1.1电路设计方案 (1) 1.1.1 原理图 (1) 1.1.2 工作原理 (6) 第二章数字时钟功能要求及元器件介绍 (7) 2.1 基本功能 (7) 2.2 元器件介绍和清单 (9) 2.2.1 555多谐振荡器 (9) 2.2.2 74LS160芯片 (9) 2.2.3 74LS248芯片 (10) 2.2.4 数码管 (11) 2.2.5 74LS00芯片 (12) 2.2.6 CD4081芯片 (13) 第三章proteus仿真 (13) 3.1 proteus整体仿真 (13) 第四章PCB板的制作 (14) 4.1PCB板的制作 (14) 4.2电路板制作的基本步棸 (14) 4.2.1 protel软件来画好原理图 (14) 4.2.2 封装并画好PCB图,布好线 (14) 4.2.3 将PCB图打印出来,并压制好电路板 (15) 4.2.4 制作电路板,腐蚀好电路导航的铜,钻孔 (16) 4.2.5 安装元器件,焊接 (16) 4.2.6 手工焊接的步骤 (16) 4.3 注意事项 (18) 第五章电路板的调试 (18) 5.1 555多谐振荡器的调试 (18) 5.2 74LS160计数器的调试 (18) 5.3 数字时钟的整体调试 (19) 第六章总结 (19) 6.1 电路的特点及改进意见 (19) 6.2 心得体会 (19) 附录A 电路原理图 (20) 附录B 元件清单 (21) 附录C 装配图 (22) 任务书 设计题目:基于555多谐振荡器数字时钟设计 设计要求: 1. 设计内容:设计一个数字时钟,可以手动设定时间和清零。 2、性能要求: 1)通电后能自动从零开始计时。 2)时间可调。 3)24进制计时 3、每人撰写一份设计报告,根据个人分工情况有所侧重,页面数目不少于15页。 每位成员应参与设计与制作的每个过程,要了解整机设计的相关知识、掌握安装与调试等相关技能。在提交电路板和设计报告时,能够回答老师所提的问题。小组分工: 根据个人擅长及相关专业技能,我们三个分工如下: 方案设计: 绘图: 安装与调试: 摘要: 本系统是基于555多谐振荡器的数字时钟。通过555多谐振荡器产生1Hz的脉冲给74LS160计数器,使74LS160计数。再把通过74LS248数据锁存器锁存,再由译码器把数据显示出来。 基于对称 式多谐振 荡 器的矩形波发生器的设计 一多谐振荡器 1.多谐振荡器没有稳定状态,只有两个暂稳态。 2.通过电容的充电和放电,使两个暂稳态相互交替,从而产生自激振荡,无需外触发。 3.输出周期性的矩形脉冲信号,由于含有丰富的谐波分量,故称作多谐振荡器。二对称式多谐振荡器 1. 电路组成 由两个TTL反相器经电容交叉耦合而成。 通常令C1=C2=C,R1=R2=RF。 为了使静态时反相器工作在转折区,具有较强的放大能力,应满足ROFF<RF<RON的条件。 图1对称式多谐振荡器 2.工作原理 假定接通电源后,由于某种原因使uI1有微小正跳变,则必然会引起如下的正反馈过程: 原理示意图2 图3 使uO1迅速跳变为低电平、uO2迅速跳变为高电平,电路进入第一暂稳态。 此后,uO2的高电平对C1电容充电使uI2升高,电容C2放电使uI1降低。由于充电时间常数小于放电时间常数,所以充电速度较快,uI2首先上升到G2的阈值电压UTH,并引起如下的正反馈过程: 图4 图5 使u O2迅速跳变为低电平、u O1迅速跳变为高电平,电路进入第二暂稳态。 使uO2迅速跳变为低电平、uO1迅速跳变为高电平,电路进入第二暂稳态。 此后,C1放电、C2充电,C2充电使uI1上升,会引起又一次正反馈过程,电路又回到第一暂稳态。 这样,周而复始,电路不停地在两个暂稳态之间振荡,输出端产生了矩形脉冲。 3 实验波形图 图6对称式多谐振荡器的工作波形 图7 4 主要参数 矩形脉冲的振荡周期为 T ≈1.4RFC 当取RF =1k Ω、C =I00 pF ~100 μF 时,则该电路的振荡频率可在几赫到几兆赫的范 围内变化 例如:Hz f 14 5= R=2K Ω时 则C=1000μF 五 组长评语 在本次的课程设计过程中,我们六个人分工明确合理,每个人都提前完成了自己所分得 任务,才能使这次课程设计提前完成!回顾起此次课程设计,至今我仍感慨颇多,的确,从 选题到定稿,从理论到实践。可以说得是苦多于甜,但是可以学到很多很多的的东西,同时 MOS 管集成电路设计》期中论文CMOS 二输入与非门设计 日期:2015 年 5 月21 日 目录 一电路设计 1.1与非门基础 (3) 1.2 CMOS二输入与非门 (4) 二版图设计 2.1 LASI7软件介绍 (5) 2.2版图设计过程 (5) 三规则检查 (8) 四LTspice 仿真 (10) 4.1电路仿真分析软件简介 (10) 4.2 LTspice仿真过程 (11) 五总结 (15) 六参考文献 (15) 摘要 MOS(Metal-Oxide-Semiconductor )晶体管是一种金属- 氧化物半导体硅场效应管,分为PMO管和NMO管两种,由NMO和PMOS共同构成的电路即为CMO电路。和传统的TTL电路相比,MOS H成电路具有功耗较低,速度较快,输入阻抗高,热稳定性好等优点,因而在目前有着广泛的应有,可以预见的是,MOS集成电路代替TTL电路已是大势所趋。 与非门是一种数字电路的基本逻辑电路,可以看做是与门与非门的结合,若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1),在数字电路中有着非常重要的作用。 本设计旨在采用CMO设计一个二输入的与非门,根据需要,它由两个PMO(M3和M4和两个NMO(M1和M2构成。其中,两个PMO作为上拉管,两个NMO作为下拉管,两个输入信号A和B分别加在两对互补的NMO管和PMO管的栅极上,输出从他们的漏极引出。设计完之后,用LASI7 软件画出版图并进行规则检查。 关键词:CMO、S 与非门、逻辑电路、LASI7 一电路设计 1.1与非门基础 与非门是数字电路中一种重要的逻辑电路,本设计设计的是二输入与非门,它有两个输入端和一个输出端,当输入均为高电平,输出为低电平;若输入中至少有一个为低电平,贝揃出为高电平,其逻辑符号如图1所示 图1二输入与非门逻辑符号 由于有两个输入,所以真值表中它的组合共有4种形式,如表1 所示 表1二输入与非门真值表 1.2 CMOS二输入与非门 正弦波振荡电路设计 1 技术指标 设计一个正弦波振荡电路,使它能输出频率一定的正弦波信号,振荡频率测量值与理论值的相对误差小于±5%,电源电压变化±1V 时,振幅基本稳定,振荡波形对称,无明显非线性失真。 2 设计方案及其比较 通过查阅资料可以知道所谓的正弦波振荡电路是指一个没有输入信号,依靠自激振荡产生正弦波输出信号的电路。正弦波电路由放大电路,正反馈电路和选频网络组成。正弦波振荡电路的实质是放大器引正反馈的结果。 正弦波振荡电路主要有RC 振荡电路,LC 振荡电路和石英晶体振荡电路。本次试验中我主要设计的方案是RC 正弦波振荡电路。RC 正弦波振荡电路是由电阻R 和电容C 元件作为选频和正反馈网络的振荡器,RC 作为选频网络的正弦波振荡器有桥式振荡电路,双T 网络和相移式振荡电路。 根据桥式振荡电路和相移式振荡电路的工作原理,我设计了如下三个方案。 2.1 方案一 COMPI R1 10k R210k R3 10k R510k R410k C1 1nF C2 1nF D1 DIODE D2 DIODE 图一 文式桥式振荡电路 本方案主要采用一个文式桥式振荡电路作为正反馈,一个由两个二极管反相并联组成的稳幅电路作为负反馈。其中当w=w0=1/RC 时,RC 选频网络的相移为零,这样,RC 串并联选频网络送到运算放大器同向输入端的信号电压与输出电压同相。满足相位平衡条件有可能发生震荡。 2.2 方案二 U1COMPI U2 COMPI C1C2C3 R1R2R3 R4R5 图二 RC 相移式电路 这是一个RC 相移式电路,正弦波信号发生器由反相输入比例放大器,电压跟随器和三节RC 相移网络构成。对于三节RC 电路,其最大相移可以接近于二百七十度。有可能在某一特定的频率下使其相移为一百八十度,满足相位平衡条件,合理的选取元件及元件参数,满足产生振荡条件和幅度平衡条件的电路就会产生振荡。 2.3 方案三 U1 COMPI R1 R2 R3R4 C1C2 图三 RC 文式桥正弦波振荡电路 三极管变色闪光灯电路图与多谐振荡器原理 在多谐振荡器两只三极管得集电极分别接上发光管,发光管就能够依多谐振荡器得周期进行交替闪烁,此电路用途广泛,可用与家居装饰 等! 电路工作原理 本电路采用高增益pnp型锗管vt3, vt4组成多谐振荡器,有两级反相器首尾连接,级间利用电容c3, c4耦合,其工作周期为1s! 元件选择与调试 三极管应选择集电极电流大于50ma得 9012或9015,发光管应选择高亮度得管子! 若想改变闪烁得速度,可以调整c3, c4得容量,也可以用微调代替r3, r4,条好后换上相应数值得电阻即可! 无稳态多谐振荡器是一种简单的振荡电路。它不需要外加激励信号就便能连续地、周期性地自行产生矩形脉冲.该脉冲是由基波和多次谐波构成,因此称为多谐振荡器电路。多谐振荡器可以由三极管构成,也可以用555或者通用门电路等来构成。用两只三极管组成的多谐振荡器,通常叫做三极管无稳态多谐振荡器。 在本例中我们将用两只三极管制作一个多谐振荡器,并用它驱动两只不同颜色的发光二极管。在制作完成时,我们能看到两只发光二极管交替点亮,并且我们可以通过调整电路的参数来调整发光管点亮的时间。 三极管多谐振荡器的电路原理图: 下面我们将简要分析该电路的工作原理: 上图所示为结型晶体管自激或称无稳态多谐振荡器电路。它基本上是由两级RC 藕合放大器组成,其中每一级的输出藕合到另一级的输入。各级交替地导通和截止,每次只有一级是导通的。 从电路结构上看,自微多谐振荡器与两级Rc正弦振荡器是相似的,但实际上却不同。正弦振荡器不会进入截止状态.而多谐振荡器却会进入截止状态。这是借助于Rc耦合网络较长的时间常数来控制的。尽管在时间上是交替的,可是这两级产生的都是矩形波输出。所以多谐振荡器的输出可取自任何一级。 电路上电时,Vcc加到电路,由于两只三极管都是正向偏置的故他们处于导通状态,此外,还为藕合电容器Cl和C2充电到近于Vcc电压。充电的路径是由接地点经过晶体管基极,又通过电容器而至Vcc电源。还有些充电电流是经过R1和R2的,从而导致正电压加在基极上,使晶体管导电量更大,因而使两级的集电极电压下降。 两只晶体管不会是完全相同的,因此,即使两级用的是相同型号的晶体管和用相同的元件值,一个晶体管也会比另一个起始导电量稍微大些。 假定Ql的导电量稍大些,由于Ql的电流大,它的集电集电压下降就要比Q2的快些。结果,被通过电阻器R2放电的电容器C2藕台到Q2基极的电压就要比由C1和Rl藕合到Ql基极的电压负值更大些。这就使得Q2的导电量减少,而它的 目录 摘要 (2) 1 设计任务和要求 (4) 1.1:设计任务 (4) 1.2 :设计要求 (4) 2 方案比较与论证 (4) 2.1:稳压电源通常由 (4) 2.2 :方案论证 (8) 3 硬件设计................................................................................................................... 错误!未定义书签。 3.1 :设计思想................................................................................................... 错误!未定义书签。 3.2 :称功能模块............................................................................................... 错误!未定义书签。 4 系统仿真 (8) 4.1 :仿真原理图如下: (8) 5系统的组装................................................................................................................ 错误!未定义书签。 5.1 :PCB版板图................................................................................................ 错误!未定义书签。 6 结论: (9) 参考文献:................................................................................................................... 错误!未定义书签。附录一:电路原理图................................................................................................... 错误!未定义书签。:元件列表................................................................................................................... 错误!未定义书签。 课程名称 Course 集成电路设计技术项目名称 Item 二输入与非门、或非门版图 设计 与非门电路的版图: .spc文件(瞬时分析): * Circuit Extracted by T anner Research's L-Edit V7.12 / Extract V4.00 ; * TDB File: E:\cmos\yufeimen, Cell: Cell0 * Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03 .include H:\ml2_125.md VPower VDD GND 5 va A GND PULSE (0 5 0 5n 5n 100n 200n) vb B GND PULSE (0 5 0 5n 5n 50n 100n) .tran 1n 400n .print tran v(A) v(B) v(F) * WARNING: Layers with Unassigned AREA Capacitance. * * * WARNING: Layers with Unassigned FRINGE Capacitance. * * * 基于555多谐振荡器数字时钟设计

对称式矩形波

CMOS二输入与非门设计

正弦波振荡电路设计课程设计

双三极管多谐振荡器原理

NE555多谐振荡电路课程设计

二输入与非门,或非门版图设计