The Use of the No-Instruction-Set Computer (NISC) for Acceleration in

WISHBONE-Based Systems

Roko Grubi?i?, Vlado Sruk

Technical Report 11-14-2008

Department of Electronics, Microelectronics, Computer and Intelligent Systems Faculty of Electrical Engineering and Computing, Zagreb, Croatia

{roko.grubisic, vlado.sruk}@fer.hr

Abstract:General-purpose processors are often unable to exploit the parallelism inherent to the software code. This is why additional hardware accelerators are needed to enable meeting the performance goals. NISC (No-Instruction-Set Computer) is a new approach to hardware-software co-design based on automatic generation of special-purpose processors. It was designed to be self-sufficient and it eliminates the need for other processors in the system. This work describes a method for expanding the application domain of the NISC processor to general-purpose processor systems with large amounts of processor-specific legacy code. This coprocessor-based approach allows application acceleration by utilizing both instruction-level and task-level parallelism by migrating performance-critical parts of an application to hardware without the need for changing the rest of the program code. For demonstration of this concept, a NISC coprocessor WISHBONE interface was designed. It was implemented and tested in a WISHBONE system based on Altium’s TSK3000A general-purpose RISC soft processor and an analytical model was proposed to provide the means to evaluate its efficiency in arbitrary systems.

Keywords: NISC, WISHBONE, coprocessor, bus, interface

1Introduction

Embedded computer systems are no longer used only as simple control devices. Instead, today’s embedded systems have to efficiently perform complex tasks and algorithms despite increasingly stringent design constraints and shrinking time-to-market. Traditional software-centered design approach offers high designer productivity, but low design quality in terms of performance and logic utilization. The key for increasing the design quality is the migration of computationally-intensive parts of the system’s task to hardware. Since general-purpose processors are often unable to exploit the parallelism inherent in the software code, these hardware accelerators provide an effective way to meet the design’s performance goals for certain classes of applications.

Hardware acceleration can be accomplished by adding application-specific coprocessors to the system or by customizing existing processors. Custom hardware is conventionally designed at the register transfer level (RTL), which entails manually coding the RTL model in a hardware description language (HDL), such as VHDL or Verilog. This process is often tedious and error-prone and limits the designer productivity. To overcome this problem, it is necessary to raise the level of abstraction for the hardware design and use special tools to synthesize the actual circuitry. Such design approaches include High-level synthesis (HLS), Application-specific instruction set processors (ASIPs) and the No Instruction Set Computer (NISC).

HLS and ASIP techniques are commonly used to design custom hardware, but their effectiveness and scope of use are limited. HLS usually supports only a subset of a high-level programming language and is only effective for small-size problems. Also, synthesis results tend to be unpredictable and so the designer can only try to meet the design constraints by trial-and-error methods. AISPs, on the other hand, rely on a limited number of custom instructions to increase the system’s performance. The number of custom instructions is limited by the instruction decoder and some ASIPs even limit this number to a single custom instruction. Design of special datapath extensions is also required and it faces the same productivity vs. performance problems as designing any custom hardware.

NISC [1][2] addresses these limitations by eliminating the instruction abstraction and compiling programming language code directly to datapath control words using a special cycle-accurate compiler [3]. In this way, this approach keeps the best of both the world of general purpose processors and the world of custom hardware design. NISC processor’s architecture can be manually modeled in an Architecture Description Language (ADL) called Generic Netlist Representation (GNR) [4], automatically generated or selected from a library of standard or previously designed architectures. NISC Toolset [5] generates the RTL model of the processor and control words for the desired application to be implemented in the desired technology, whether FPGA or ASIC.

NISC approach utilizes instruction-level parallelism (ILP) to speed up the execution of an algorithm and the generated processor is capable of executing several equivalent RISC instructions in a single clock

cycle. The additional prebinding mechanism enables simple I/O and interrupts [6] and in this way the scope of applications for which a NISC processor can be used is extended to control tasks of a classical microcontroller. The communication interface for the NISC processor [7] enables the use of multiple NISC processors in the system. It enables exploiting the system’s available task-level parallelism by parallel execution of the system’s tasks on different NISC processors which further accelerates the application.

NISC approach was designed to be self-sufficient and it eliminates the need for other processors in the system. However, that represents a problem when attempting to integrate a NISC processor into an existing system. In the case when a large base of non-portable legacy code optimized for a particular general purpose processor exists, we suggest a coprocessor-based approach to take advantage of the NISC technology and accelerate desired applications. This approach allows utilizing both instruction-level and task-level parallelism by migrating performance-critical parts of the application to hardware without the need for significant changes to the rest of the program code.

One of the major design challenges of the coprocessor approach is the integration of the NISC processor with other IP cores in the system. When designing SoCs, standard bus architectures are usually used, but the NISC processor itself isn’t compatible with any of the specifications. Standard bus architectures simplify the process of system integration, shorten time to market and support portability and reuse of IP cores. Renowned SoC bus architectures of the day include ARM Advanced Microcontroller Bus Architecture (AMBA), IBM CoreConnect, WISHBONE and Altera Avalon. The use of standard bus architectures also provides the opportunities for using special tools that automatically generate bus interfaces and interconnections, in this way further shortening time to market and reducing the possibility of human error. A standard bus interface for the NISC processor enables its simple integration in a wide variety of systems with different processors and peripherals.

In this paper we present the WISHBONE bus interface for the NISC processor [8] and propose the use of the NISC processor as a loosely-coupled application-specific coprocessor in WISHBONE-based systems. The NISC WISHBONE Interface was designed, implemented and tested in a WISHBONE system based on Altium’s TSK3000A general-purpose RISC soft processor using an Altium LiveDesign Evaluation Board with a Spartan3 FPGA and a Xilinx ML506 board with a Virtex-5 FPGA.

2WISHBONE bus architecture

The WISHBONE System-on-chip (SoC) architecture for portable IP cores [8] is a flexible design methodology developed by Silicore Corp. targeted at SoC integration and design reuse. This is accomplished by defining a standard interconnection scheme and data exchange protocols. WISHBONE specification defines a single, simple, logical, fully synchronous MASTER/SLAVE bus and IP core interfaces that require very few logic gates. It supports different technology-independent interconnection topologies ranging from simple point-to-point and shared bus interconnections to data flow interconnections and complex switch fabrics. It also supports a full range of standard data transfer protocols including SINGLE READ/WRITE cycles, BLOCK READ/WRITE cycles and read-modify-write

(RMW) cycles with various data sizes and byte ordering. A handshake mechanism enables flow control and communication between different-speed cores.

WISHBONE bus architecture was chosen for the implementation of the NISC coprocessor interface mainly because of its flexibility and the fact it imposes no licensing and application restrictions. WISHBONE specification is currently maintained by https://www.doczj.com/doc/f37868242.html, and today it represents a de facto standard for open-source hardware. It is also offers CAD tool support and a large library of free processors and other IP cores. Besides free processor IP, many popular commercial soft processors (e.g. Xilinx MicroBlaze and Altera Nios) have a WISHBONE-compatible variant available.

3NISC WISHBONE Interface

In this section we introduce our approach to enabling the use of the NISC processor in a WISHBONE-based system. To make the connection of the NISC processor to the WISHBONE bus possible, we designed and implemented a NISC WISHBONE Interface IP. This IP enables the connection of the NISC processor to the WISHBONE bus, but for the NISC processor to be used as a coprocessor which performs useful tasks in the system, some changes in the NISC processor’s architecture are required. We describe these architectural additions together with the software necessary to enable the communication from both the side of the NISC processor and the side of the main processor. We also propose an appropriate communication scheme, designed to ease the migration of application’s functions between hardware and software and thus ease the process of design space exploration. The NISC WISHBONE Interface is compatible with the existing NISC design flow and requires no changes in the NISC Toolset.

The NISC WISHBONE Interface IP and the software communication scheme enable control and data transfer which are necessary for the use of the NISC processor as a coprocessor in WISBONE-based systems. The main processor can transfer the data to be processed (the function’s arguments) to the coprocessor, start the execution of the coprocessor function, detect when the data processing is completed (either by pooling the coprocessor’s status or by means of an interrupt) and retrieve the results.

The designed NISC WISHBONE Interface is targeted at fully synchronous WISHBONE systems and supports word size (32-bit), word granularity SINGLE READ/WRITE WISHBONE classic bus cycles. We describe two different methods for exchanging the data between the general-purpose processor and the NISC coprocessor. One method is suitable for simple general-purpose data transfer and the other for custom special-purpose data transfers tailored for a specific application. A design approach with two distinct parts of the WISHBONE interface was followed to enable this kind of flexibility. The first part is NISC Basic WISHBONE Interface which is responsible for control functions and special-purpose data transfers. The other part of the interface is the NISC Data Memory WISHBONE Interface and this one is responsible for general purpose data transfers, i.e. transferring large amounts of data directly to and from the data memory of the NISC processor.

3.1NISC Basic WISHBONE Interface

The NISC Basic WISHBONE Interface enables coprocessor control control, i.e. starting or stopping data processing and detecting when the data processing is completed, and transferring smaller amounts of special purpose data directly into the NISC processor’s datapath. This is the main part of the NISC WISHBONE Interface and it is necessary for the communication since it enables coprocessor control and interrupt capabilities. It is designed for seamless integration with the RTL model generated by the NISC Toolset.

The advantage of using the NISC Basic WISHBONE Interface for data transfers is fast communication (one-cycle transfers) and the ability to bring the data directly to the input of the desired functional unit, in this way speeding up the execution of the algorithm. The disadvantage of this part of the interface is that it is only suitable for transferring small amounts of data, since this approach doesn’t scale well beyond a few arguments and results.

3.1.1NISC-side communication requirements

The accessible external signals of the NISC processor’s RTL model are the clock signal, the reset signal, the halt signal and the configurable I/O ports. The NISC Basic WISHBONE Interface uses only these external signals to connect the NISC processor to the WISHBONE bus. Data transfer from the main processor to the NISC processor is achieved using input ports which can be read by the NISC’s application using the prebinding mechanism. Starting the NISC’s application execution is accomplished by resetting the NISC processor, i.e. by generating a falling edge on the reset pin. Completion detection is achieved by reading the halt signal which NISC automatically sets upon completing its task. The results are retrieved using output ports, also using the prebinding mechanism. After the NISC coprocessors completes, it writes the results to its output ports’ registers to be read by the main processor using the WISHBONE interface. The output ports have an internal register inside the NISC processor’s datapath, but because the input ports function only as proxies for external registers, it was necessary to provide additional registers as a part of the WISHBONE interface. These input and output registers represent the shared resources that enable the transfer of data between the main processor and the NISC coprocessor.

The designer’s task is to add the external I/O ports to the desired datapath units as a part of the process of designing the architecture using the GNR ADL. A simple architecture with two input ports for the arguments and one output port for the result shown on Figure 1. This method of communication is convenient when the application requires intensive calculations with some of the arguments or when only simple argument exchange is required. In this case arguments can be brought directly to the input of the desired functional unit and selected when needed, using input multiplexers. This eliminates the need for the sequential transfer of the arguments to the register file for later use and thus eliminates unnecessary transfer of the data. One sequential transfer is already done when the main processor transfers the data to the interface’s registers, so another transfer from the interface’s registers to the NISC processor’s register file or internal registers would double the communication expenses and thus limit the efficiency of the coprocessor. This approach also avoids register spilling for often-used values, which is especially important in area-limited systems with small register files. Output registers for the

results are used in a similar manner and can also be connected to the datapath in such a way to minimize communication expenses.

Figure 1: Simple architecture with argument inputs and a result output

Datapath connections for external inputs and external outputs enable NISC’s hardware to access shared registers for communication, while the NISC Basic WISHBONE Interface enables the same access for the main processor. To enable the NISC’s application to actually read these shared resources or write them, appropriate prebound functions for reading or writing shared registers are used. Listing 1 illustrates this concept for a simple application with two arguments and one result. First, the arguments are read from the external input ports into temporary variables and then they are used in a function to compute the result. The result is then written to the external output register to be read by the main processor when the application terminates and the halt signal is asserted.

Listing 1: Sample NISC application

3.1.2 NISC Basic WISHBONE Interface implementation

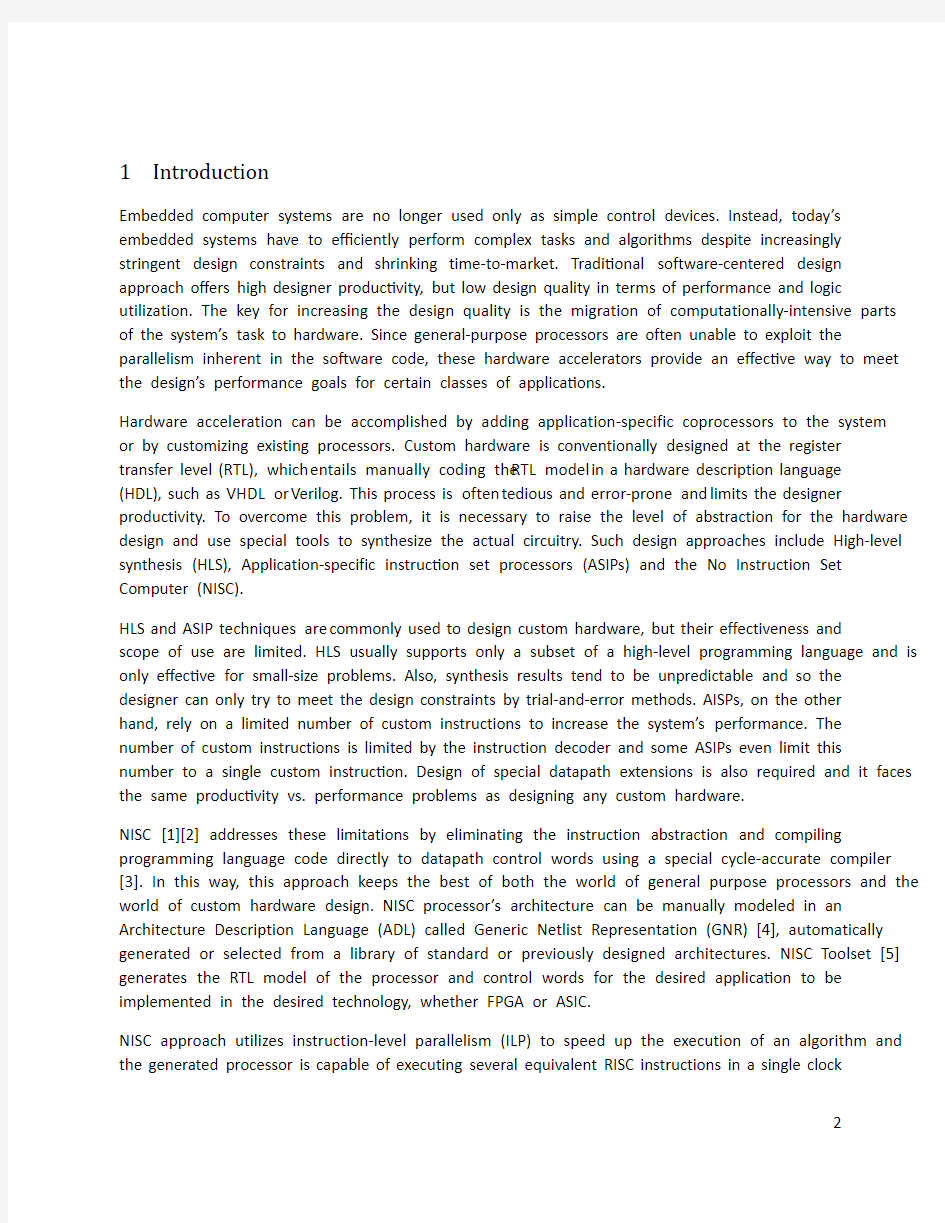

To enable the transfer of the data and control flow, the NISC Basic WISHBONE Interface’s provides registers for input arguments and special control registers. Control registers are used to set the state of the NISC processor’s reset signal and to read the state of the halt signal. The result output ports are simply routed to the interface’s output multiplexer to enable the main processor to read the results. A simplified block schematic of the interface is shown in Figure 2. The figure shows the internal registers of the interface and the simplified circuitry to illustrate the path of data to and from the NISC processor’s top module NiscSystem.

Figure 2: NISC Basic WISHBONE Interface

In a typical WISHBONE system, the most significant bytes of the address are decoded in the interconnect module (the so called WISHBONE Intercon), which enables the desired peripheral using the active cycle (CYC_I) and strobe (STB_I) signals, and only the required number of address bits is forwarded to the peripheral’s ADDR_I inputs. The internal address decoding of the peripheral then determines which of its internal memory locations is addressed, and this is also the way the NISC Basic WISHBONE Interface operates. Reading the data from the interface is implemented using a multiplexer which is controlled by the WISHBONE address lines. The write operation is implemented using register enable signals controlled by the address decode logic and the write enable qualifier signal (WE_I). The WISHBONE clock signal CLK_I is routed to the NISC processor and the interface to create a fully synchronous system. The WISHBONE handshake mechanism is implemented using only combinatorial logic, as there are no slow modules in the design. I.e. none of the modules requires more than one cycle for read or write operations so no memory elements for delay are required. WISHBONE reset signal RST_I resets the NISC processor and the interface’s internal registers.

W I S H B O N E

Interrupt mechanism is implemented in such way that setting the interrupt signal INT_O only occurs when the interrupt enable (INT_EN) flag is set and the halt signal is set. INT_O is not a standard WISHBONE signal, but it can easily be connected directly to the main processor and several commercial tools (e.g. Altium Designer) even provide interrupt connections as a part of the WISHBONE interconnect module.

3.1.3NISC Basic WISHBONE Interface programming model

Using the NISC coprocessor attached to the WISHBONE bus in this way is very straightforward. First, the value ‘1’ is written to the reset register to put the NISC processor in reset state and to insure that only the main processor has access to the shared registers. Then, the arguments are written to appropriate registers and the value ‘0’ is written to the reset register to start the NISC’s application execution. After that, the main processor can pool the value of the halt signal until it becomes active and then retrieve the results by reading appropriate registers. The reset register and the halt signal are mapped to the same memory location (location 0), and one is accessed when writing and the other when reading that memory address.

The interface’s full memory map is shown on Table 1. The first memory location, at address 0 (plus the base address displacement) is reserved for the already mentioned reset/halt pair, the control register. Because 32-bit addressing is used, the address difference between two adjacent memory locations is 4 bytes. So, the next location’s address is 4 and this is the location of the interrupt enable register. After that follow the argument and result registers. The example register address layout shown in Table 1 enables simple implementations of traditional C functions with arbitrary number of arguments and one return value. Of course, for different applications with additional result values and matching result registers, different address layouts are possible with differently laid-out interface datapath and NISC I/O ports.

Table 1: NISC Basic WISHBONE Interface memory map

Address Name Width [bit] Description

00 RESET

HALT

!(INT_FLAG) 1 Bit0:

read: status of the halt signal is read

write: reset register is written to – '1' sets the NISC to reset state, '0' initializes the execution

('0' also serves as the interrupt acknowledge)

04 INT_EN 1 Bit0: reads/writes the interrupt enable flag – '1'

enables the interrupts, '0' disables them

08 RESULT 32 Read/Write – result

12 ARG 1 32 Read/Write – 1st argument

16 ARG 2 32 Read/Write – 2nd argument

... ... ... ...

(N+2)*4 ARG N 32 Read/Write – N th argument

Listing 2 shows an example C function offloaded to the NISC coprocessor to illustrate the designed communication scheme. The function call is inlined to eliminate the need for copying the arguments to local variables. This example function is blocking, i.e. it doesn’t return until the coprocessor’s task is completed and in that way the coprocessor’s task behaves as a regular C function. Because of that, the programmer can use it from the calling function as though it is a software, rather than hardware, implementation of the algorithm. When using this communication scheme, only the body of the function needs to be replaced and the calling functions remain unchanged when migrating the desired function’s implementation between hardware and software. In this way, it is very simple to experimentally evaluate design options and thus explore the design space.

For exploiting the task-level, data and function parallelism, more complex non-blocking versions of NISC coprocessor function calls should be used. In this way, the main processor can send the data to the NISC coprocessor, initialize the data processing and carry on with its own tasks. These tasks could include control functions, processing a part of the data (data parallelism), or performing a part of the processing on all the data (function parallelism).

Listing 2: Communication with the NISC processor

Interrupt-driven communication with the NISC coprocessor requires enabling the interrupts using the interrupt enable flag. When the arguments are sent to the coprocessor registers and the execution is started, the main processor can carry on with its regular tasks and retrieve the results in the interrupt service routine (ISR). As a part of the ISR, the main processor must also acknowledge the interrupt by clearing the NISC WISHBONE Interface’s interrupt flag which is achieved by writing the value ‘0’ to the NISC control register. Other standard interrupt acknowledge procedures must be followed depending on the processor’s interrupt system architecture and whether the interrupts are level or edge triggered. The next batch of data to be processed can be sent in the ISR and the next execution can also be initiated.

3.2NISC Data Memory WISHBONE Interface

The NISC Basic WISHBONE Interface was designed for applications which need to exchange a small amount of special purpose data with the main processor. The problem is that this approach doesn’t scale well for applications that have a large amount of arguments and/or results. This approach would then require a large number of registers and large multiplexers, which would require a lot of chip area and would also limit the maximum frequency, especially when considering the negative implications of using large multiplexers in FPGAs.

A further drawback of the NISC Basic WISHBONE Interface is the inability to perform indexed addressing on the arguments and results without the need for data transfer between shared registers and the data memory. E.g. to perform indexed addressing on the arguments, NISC processor must copy the data from the interface’s argument registers to internal arrays in the data memory and every piece of data thus has to be copied twice which imposes a large communication overhead when transferring large amounts of data. This especially represents an issue with algorithms that involve matrix calculations and the like.

3.2.1NISC Data Memory Access Multiplexer/Arbiter

A simple solution for the problem of transferring large amounts of data to and from the NISC processor is the direct transfer of data to and from the NISC processor’s data memory. To achieve this, a special module that enables external access to NISC’s data memory was added to the design. The role of this data memory access multiplexer is to provide access to the NISC processor’s data memory from the WISHBONE bus and to arbitrate access to the memory between the interface and the main processor. The data memory multiplexer is connected between the NISC processor’s core (controller and datapath) and the data memory and it provides an additional set of pins that are connected outside of the NISC processor itself, as shown in Figure 3.

Figure 3: Multiplexing the access to the data memory

The data memory multiplexer’s arbitration scheme is quite simple: if the NISC processor’s reset or halt signals are active, then the main processor has control over the data memory. Otherwise, the control is left to the NISC processor and the main processor has no means of writing to the data memory and reads the value of all data bits as zeroes. The implementation of the data memory multiplexer is shown in Figure 4.

Figure 4: Data memory multiplexer implementation

N I S C E X T E R N A L Memory

3.2.2 NISC Data Memory WISHBONE Interface implementation

NISC Data Memory Access Multiplexer/Arbiter provides the means for external access to the data memory of the NISC processor and the NISC Data Memory WISHBONE Interface is connected to these external access pins. Its role is to handle the appropriate data conversion and handshaking to enable correct data memory access operations from the WISHBONE bus. NISC’s data memory module encompasses FPGA block RAM’s (BRAMs) and a memory controller module (namely, ByteAddressableDMemLogic Verilog module). The data memory module’s ports are actually the memory controller’s ports so the NISC Data Memory WISHBONE Interface is designed in such a way to operate with the memory controller and internal BRAMs.

Figure 5 shows the internal organization of the NISC Data Memory WISHBONE Interface. The address bits are forwarded directly from the WISHBONE address lines to data memory’s address lines. Since NISC’s memory controller doesn’t require word access addresses aligned on 4 byte borders and requires the data with width less than 32-bits to be aligned to the lower data bits (unlike WISHBONE mechanism with byte-enables), special alignment logic was designed to handle the translation. Also, depending on the access type, WISHBONE byte enable lines are translated to appropriate type codes for the NISC memory controller. Write and read enable signals are derived from the WISHBONE write enable qualifier WE_I. The handshaking mechanism is implemented with 1 cycle acknowledge delay to allow for the BRAM latency, since FPGA BRAMs are synchronous.

Figure 5: NISC Data Memory WISHBONE Interface

3.3 The complete NISC WISHBONE Interface and its programming model

The complete NISC WISHBONE Interface, as shown of Figure 6, consists of the NISC Basic WISHBONE Interface and the NISC Data Memory WISHBONE Interface. This approach with two distinct interfaces eliminates the need for address translations inside of the interface to differentiate between the shared registers space and the data memory space and thus simplifies the design. The simplest way to use the

W I S H B O N E NISC dmem external access

complete interface is to first put the NISC processor in the reset state using the NISC Basic WISHBONE Interface and then send the data through the NISC Data Memory WISHBONE Interface. After that, NISC is taken out of reset state and the main processor waits for the application to complete and retrieves the results from the data memory. Special-purpose data could be also sent or retrieved using the NISC Basic WISHBONE Interface. It’s also important to point out that the lack of hardware or software reset of NISC’s data memory is vital for this sort of communication because the sent arguments would otherwise be lost when the NISC processor is reset.

To enable the main processor to read or write a particular bit of data in the NISC’s data memory, its address must be known and it is used as an offset from the base address of the NISC Data Memory WISHBONE Interface in the main processor’s memory map. NISC Toolset’s Storage Bindings outputs are used to determine the address of a particular global variable or a global array in the data memory. Storage Bindings provide this information in the form of a table and the required information can be found in this table and used in the program code. The whole data memory of the NISC processor is mapped to a contiguous external memory block in the main processor’s address space and is thus easily accessible through pointer manipulation. After the main processor writes the arguments to the global data structures in the NISC processor’s data memory, the NISC processor operates on this data. The NISC processor then writes the results to designated global data structures which are afterwards read by the main processor. This approach requires no changes in the NISC’s algorithm, provided that it uses global variables or global arrays. Global structures can also be passed to the functions as arguments, which eliminates the need for any changes in the code of any of the functions.

Figure 6: NISC WISHBONE Interface architecture

Listing 3 shows an example implementation of the communication using the NISC Data Memory WISHBONE Interface. After asserting NISC’s reset signal to ensure access to the data memory, arguments are copied to the data memory using pointers and the data processing is started by deasserting the NISC reset signal. After completion detection, using pooling in this example, results can be retrieved for further processing. If there is no need to immediately start processing the next batch of data, the data can be used directly from NISC’s data memory, thus eliminating the need for copying. If, however, we want to utilize task-level parallelism and process another batch of data in parallel with the task of the general-purpose processor, copying becomes necessary.

Listing 3: Communication using the NISC Data Memory WISHBONE Interface

3.4TSK3000A WISHBONE System with a NISC coprocessor

The complete NISC WISHBONE Interface was implemented using VHDL and integrated with a generated NISC processor in a self-sufficient WISHBONE compatible module which can be used as a coprocessor in systems based on the WISHBONE bus architecture. The generated NISC processor was based on a generic NISC architecture with necessary I/O datapath extensions and simple applications designed to test the communication capabilities. As a proof-of-concept for the presented coprocessor-based approach, we implemented and tested a WISHBONE system based on Altium’s TSK3000A general-purpose 32-bit RISC soft processor. TSK3000A is based on the MIPS/DLX instruction set and is FPGA vendor independent (unlike FPGA vendors’ proprietary processors, such as Xilinx MicroBlaze and Altera Nios). It is designed for seamless integration with Altium’s configurable Wishbone Interconnect module which was also used in this proof-of-concept system. Main processor-side communication routines were developed as presented earlier in this chapter and then tested in conjunction with the hardware using the Altium LiveDesign Evaluation Board with a Spartan3 FPGA and Xilinx ML506 with a Virtex-5 FPGA. The schematic for the complete system is shown in Figure 7.

Figure 7: TSK3000A with a NISC coprocessor

4Performance analysis

The designed NISC WISHBONE Interface provides the means for using the NISC processor as a loosely-coupled coprocessor in WISHBONE-based systems. To justify the use of the NISC coprocessor in the system, the speedup of the algorithm must justify the cost of the extra hardware. Furthermore, the speedup of the NISC implementation of the algorithm in question must be such to cancel the negative effect on the performance imposed by the main processor to coprocessor communication overhead and still provide overall system speedup. Of course, what is actually justified also depends on the achieved speedup rate and design constraints. E.g. for area-constrained systems a small achieved speedup would not justify the use of a NISC coprocessor, but it could be justified in systems where area is not an issue and every bit of performance improvement counts.

To ease the design space exploration and provide the means of estimating the system’s performance and the margins of the speedup required by the NISC processor in the early stages of the project, an analytical model of the system’s performance was devised. This model is intended to be used together with the profiling information and it enables the designer to estimate the benefits of using a NISC coprocessor for a particular part of the system’s task and quickly explore the design space before the actual system is built. It also predicts the minimum performance limit for the NISC processor which can be used to quickly eliminate unsuitable architectures and thus drive the hardware-software co-optimization process in the right direction considering the system-level requirements.

The NISC WISHBONE Interface was designed in such a way as to extract maximum performance in systems with a general-purpose processor which uses WISHBONE classic bus cycles, like the Altium TSK3000A. This means that an access to the interface’s register takes one clock cycle and an access to

the data memory takes two clock cycles (because of BRAM latency). WISHBONE classic bus cycles don’t allow for distinct address and data transfer phases and any sort of bus transaction pipelining to improve performance. Because of that, there are no means for further acceleration of the data transfer according to the WISHBONE classic specification, not even with additional circuitry. The number of clock cycles required for the communication is defined by the number of cycles required for the transfer of arguments, the number of cycles required for the transfer of results and the number of cycles required for the control operations. The control overhead consists of only two cycles, one for stopping the NISC processor (i.e. putting it into reset state) and one for starting it (i.e. taking it out of reset state).

To estimate the performance impact of the communication overhead, we use the worst-case scenario for the transfer of the arguments and results, i.e. we use the slower mode of data transfer, the transfer of data to and from the data memory of the NISC processor. The communication time is defined by the cycle count for the communication and the frequency of the communication clock, i.e. the bus frequency, which is the same as the system frequency in fully synchronous systems.

Fully synchronous systems offer the advantage of easier design process and simpler verification. The drawback of using a single clock in the system is the negative impact on performance. The only way to extract the maximum performance is to use asynchronous clock domains for different parts of the systems, each running at its maximum frequency and use synchronization logic and FIFOs for crossing the clock domains, which often leads to design problems and difficult-to-track timing issues. The fully synchronous approach eliminates timing problems inside of the system and it was our intent to analyze and determine the boundaries of this design approach when using NISC coprocessors. The major speedup should be achieved by the means of parallelism and architecture optimizations with cores sharing the same clock and asynchronous design should only be considered when this approach fails to meet the design constrains.

Since the designed NISC WISHBONE Interface is 32 bits wide, the model presumes 32-bit arguments and results but this reasoning is, of course, valid for the arguments with widths of less than 32 bits. Transfer of data wider than 32 bits can be split up in 32 bit data transfers with some software support and can thus also be modeled. It is also important for the model to include additional software overheads for the communication, e.g. loop overhead. There are different approaches to accelerating this sort of communication, using both software and hardware. These approaches include loop unrolling, using custom loop instructions with zero control overhead (depending on the processor architecture and configurability) or using additional DMA engines to drive the data transfer. To model these additional parameters, a scaling factor for the number of transfers was added together with a constant that includes any additional control overheads (such as DMA setup) to better estimate the system’s performance. The basic expression for estimating the communication time is given by the equation (1).

BUS BUS

comm comm f ad CtrlOverhe SWOverhead sCount ArgCount f CycleCount T ++×+===)2()Re ( (1)

To analyze the benefits of the NISC implementation of a particular function, we must compare the execution time of the algorithm for a general-purpose processor and the execution time when using the NISC processor. The execution time for the general-purpose processor is defined by the processor architecture and clock frequency. The processor architecture defines the number of instructions for the algorithm and the number of cycles required to execute an instruction (Cycles Per Instruction – CPI) and these define the total number of clock cycles for an algorithm. Equation (2) shows the expression for the execution time. CPU CPU CPU f CycleCount T = (2)

Similarly, the execution time for the NISC processor is defined by the number of cycles required for the particular application and the NISC processor’s clock frequency, as equation (3) shows. The number of cycles is determined by the application itself and the NISC processor’s architecture. NISC NISC NISC f CycleCount T = (3)

The total execution time when using the NISC processor as a coprocessor is defined by the sum of the execution time for the application itself and the time required for communication:

comm NISC COP T T T += (4)

All these expressions depend on the frequency of a particular module. Since the NISC WISHBONE Interface is targeted at fully synchronous systems, the frequencies of all modules must be the same. Therefore, the maximum frequency of the system is determined by the minimum of all the core’s frequencies, as shown in equation (5). This expression can be easily extended to systems with multiple NISC coprocessors.

{}max ,max ,max ,,,min BUS NISC CPU SYS f f f f = (5) The execution time for the general-purpose processor can be expressed using (2) and (5), as follows:

{}max ,max ,max ,,,min BUS NISC CPU CPU SYS

CPU CPU f f f CycleCount f CycleCount T === (6)

Similarly, the execution time for the NISC coprocessor can be expressed using (1), (3), (4) and (5), as follows:

{}max ,max ,max ,,,min )2()Re ()2()Re (BUS NISC CPU NISC SYS NISC comm NISC COP f f f ad

CtrlOverhe SWOverhead sCount ArgCount CycleCount f ad CtrlOverhe SWOverhead sCount ArgCount CycleCount T T T ++×++==++×++=

=

+= (7)

To determine the borderline of the coprocessor’s effectiveness, we again turn to the worst-case scenario, which in this case is the blocking communication. When using blocking communication, there is no parallel execution of the algorithm on the main processor and the NISC coprocessor and because of that, this represents the worst case for the processor-coprocessor communication. For the hardware implementation of a function to be efficient, the obvious and necessary condition is for the function’s execution time on the coprocessor to be shorter than the execution time on a general-purpose processor:

CPU COP T T < (8) If the coprocessor’s implementation doesn’t limit the system’s maximum frequency (i.e. f NISC,max > f CPU,max holds true) then the speedup of a part of an algorithm (taking into account communication and control overheads) certainly speeds up the execution of the whole program. From (6), (7) and (8), follows: ad CtrlOverhe SWOverhead sCount ArgCount CycleCount CycleCount CPU NISC ?+×+?<)2()Re ( (9) The equation (9) defines the maximum number of clock cycles for the NISC coprocessor in order for that implementation not to reduce the effectiveness of the whole system. Using this expression, it is possible to eliminate unacceptable designs in the early stages of the project. For the coprocessor implementation to be truly effective, it must provide suitable speedup to justify the additional hardware expense. To quantify this, we must analyze the overall speedup factor. To do this, the program must be divided into two parts. One part will always be executed on the main processor. The other part can migrate between hardware and software implementations and it is for this part that we evaluate the effectiveness of the coprocessor implementation.

SW HW SW PROGRAM CycleCount CycleCount CycleCount /+= (10)

The speedup is defined as the ratio of execution times when using software or hardware implementation of the function in question. T CPU is the execution time of a purely software implementation and T CPU +C OP is the execution time when a part of the system’s task is implemented in hardware, using the NISC coprocessor. ad

CtrlOverhe SWOverhead sCount ArgCount CycleCount CycleCount CycleCount CycleCount CycleCount CycleCount CycleCount CycleCount CycleCount T T Speedup NISC SW HW SW CPU

SW HW SW comm NISC SW HW SW CPU SW HW SW COP CPU CPU ++×++++==+++=

==

+)2()Re (,/,/,/,/ (11) If the NISC coprocessor’s implementation limits the system’s maximum frequency then the speedup should be analyzed in this context. The NISC processor’s implementation is in this case only effective if the overall execution time is shorter than that of a purely software implementation despite the lower overall system frequency.

CPU COP CPU T T <+

max

,,/max ,,/CPU CPU SW HW SW NISC comm

NISC SW HW SW f CycleCount CycleCount f CycleCount CycleCount CycleCount +<++ comm

SW CPU SW HW SW CPU NISC NISC SW HW CycleCount CycleCount CycleCount CycleCount f f CycleCount ???+<)(,/max ,max

,,/ ad

CtrlOverhe SWOverhead sCount ArgCount CycleCount CycleCount CycleCount f f CycleCount SW CPU SW HW SW CPU NISC NISC SW HW ?+×+???+<)2()Re ()(,/max ,max

,,/

(12)

The equation (12) defines the maximum number of clock cycles for the coprocessor for it not to degrade the system’s performance and insure speedup, given the overall frequency of the system. If we’re interested in the minimum frequency for the system that would insure speedup, (12) can be rewritten as follows: ()CPU SW HW SW comm NISC SW HW SW CPU NISC CPU CPU SW HW SW NISC comm

NISC SW HW SW CycleCount CycleCount CycleCount CycleCount CycleCount f f f CycleCount CycleCount f CycleCount CycleCount CycleCount ,/,/max ,max ,max ,,/max ,,/+++×>+<++ ()CPU

SW HW SW NISC SW HW SW CPU NISC CycleCount CycleCount ad CtrlOverhe SWOverhead

sCount ArgCount CycleCount CycleCount f f ,/,/max ,max ,)2()Re (+++×+++×> (17)

The system’s speedup in the case when the NISC coprocessor limits the system’s maximum frequency is as follows:

max ,,/max ,,/max

,,/max ,,/)2()Re (NISC NISC SW HW SW CPU CPU

SW HW SW NISC comm

NISC SW HW SW CPU CPU

SW HW SW COP CPU CPU

f ad

CtrlOverhe SWOverhead sCount ArgCount CycleCount CycleCount f CycleCount CycleCount f CycleCount CycleCount CycleCount f CycleCount CycleCount T T Speedup ++×++++==+++==+ (18) Similar reasoning applies to the case then the bus interconnect module limits the maximum frequency, e.g. due to its complexity increasing when introducing the NISC coprocessor in the system.

5 Conclusion

In this paper we presented our solution for using the No-Instruction-Set Computer (NISC) as an application-specific coprocessor in systems based on the WISHBONE open bus specification. This approach allows designers to easily use the NISC technology in existing systems with large amounts of unportable legacy code. We defined and explained the hardware and software extensions necessary for the integration of the NISC coprocessor in an arbitrary WISHBONE system. The flexibility of these extensions enables different ways of using the NISC coprocessor to accelerate the system’s application. As a result, we enabled quick and easy integration of a hardware accelerator generated using the NISC Toolset into a given system to improve overall performance. With the previously designed interface and memory multiplexer hardware, the manual interface parameterization and integration process can’t take more than an hour. This process is also a good candidate for automation using a simple software tool which can further simplify and speed-up the whole design process.

We also analyzed the performance implications of using such a coprocessor in a fully synchronous WISHBONE system. The effectiveness of using the NISC coprocessor and the borderline performance values required to achieve overall system speed-up were evaluated. We proposed an analytical performance model that could help quick exploration of the design space, elimination of unacceptable designs and setting the design targets even in early stages of the project. In this way, the hardware-software co-development and co-optimization process could converge more quickly towards the desired goal. Since the model requires only simple arithmetic calculations, it can easily be used to build a tool to help automate design space exploration.

6 Acknowledgements

The authors wish to thank the Unity through Knowledge Fund (UKF), Kon?ar and SYSTEMCOM for supporting the project. This work builds on many years of NISC processor research at the Center for

教育资料 《短歌行》 《短歌行》赏析(林庚) 曹操这一首《短歌行》是建安时代杰出的名作,它代表着人生的两面,一方面是人生的忧患,一方面是人生的欢乐。而所谓两面也就是人生的全面。整个的人生中自然含有一个生活的态度,这就具体地表现在成为《楚辞》与《诗经》传统的产儿。它一方面不失为《楚辞》中永恒的追求,一方面不失为一个平实的生活表现,因而也就为建安诗坛铺平了道路。 这首诗从“对酒当歌,人生几何”到“但为君故,沉吟至今”,充分表现着《楚辞》里的哀怨。一方面是人生的无常,一方面是永恒的渴望。而“呦呦鹿鸣”以下四句却是尽情的欢乐。你不晓得何以由哀怨这一端忽然会走到欢乐那一端去,转折得天衣无缝,仿佛本来就该是这么一回事似的。这才是真正的人生的感受。这一段如是,下一段也如是。“明明如月,何时可掇?忧从中来,不可断绝。越陌度阡,枉用相存。契阔谈宴,心念旧恩。月明星稀,乌鹊南飞。绕树三匝,何枝可依。”缠绵的情调,把你又带回更深的哀怨中去。但“山不厌高,海不厌深”,终于走入“周公吐哺,天下归心”的结论。上下两段是一个章法,但是你并不觉得重复,你只觉得卷在悲哀与欢乐的旋涡中,不知道什么时候悲哀没有了,变成欢乐,也不知道什么时候欢乐没有了,又变成悲哀,这岂不是一个整个的人生吗?把整个的人生表现在一个刹那的感觉上,又都归于一个最实在的生活上。“我有嘉宾,鼓瑟吹笙”,不正是当时的情景吗?“周公吐哺,天下归心”,不正是当时的信心吗? “青青子衿”到“鼓瑟吹笙”两段连贯之妙,古今无二。《诗经》中现成的句法一变而有了《楚辞》的精神,全在“沉吟至今”的点窜,那是“青青子衿”的更深的解释,《诗经》与《楚辞》因此才有了更深的默契,从《楚辞》又回到《诗经》,这样与《鹿鸣》之诗乃打成一片,这是一个完满的行程,也便是人生旅程的意义。“月明星稀”何以会变成“山不厌高,海不厌深”?几乎更不可解。莫非由于“明月出天山”,“海上生明月”吗?古辞说:“枯桑知天风,海水知天寒”,枯桑何以知天风,因为它高;海水何以知天寒,因为它深。唐人诗“一叶落知天下秋”,我们对于宇宙万有正应该有一个“知”字。然则既然是山,岂可不高?既然是海,岂可不深呢?“并刀如水,吴盐胜雪”,既是刀,就应该雪亮;既是盐,就应该雪白,那么就不必问山与海了。 山海之情,成为漫漫旅程的归宿,这不但是乌鹊南飞,且成为人生的思慕。山既尽其高,海既尽其深。人在其中乃有一颗赤子的心。孟子主尽性,因此养成他浩然之气。天下所以归心,我们乃不觉得是一个夸张。 .

The way 的用法 Ⅰ常见用法: 1)the way+ that 2)the way + in which(最为正式的用法) 3)the way + 省略(最为自然的用法) 举例:I like the way in which he talks. I like the way that he talks. I like the way he talks. Ⅱ习惯用法: 在当代美国英语中,the way用作为副词的对格,“the way+ 从句”实际上相当于一个状语从句来修饰整个句子。 1)The way =as I am talking to you just the way I’d talk to my own child. He did not do it the way his friends did. Most fruits are naturally sweet and we can eat them just the way they are—all we have to do is to clean and peel them. 2)The way= according to the way/ judging from the way The way you answer the question, you are an excellent student. The way most people look at you, you’d think trash man is a monster. 3)The way =how/ how much No one can imagine the way he missed her. 4)The way =because

孩子。 Does your throat hurt you? Added the mother to the child. 女孩的表情没有任何变化,而她的目光却一直没有从我的脸上移开。 But the little girl’s expression didn’t change nor did she move her eyes from my face. 你看过她的嗓子了吗? Have you looked? 我想看,孩子的母亲说,但看不见。 I tried to, said the mother but II couldn’t see. 这个月碰巧她上学的那个学校已经有好几例白喉病。虽然到目前为止没有人说出这件事,但很显然,我们心里都想到了。 As it happens we had been having a number of cases of diphtheria in the school to which this child went during that month and we were all, quite apparently, thinking of that, though no one had as yet spoken of the thing. 好了,我说,我们先看看嗓子吧。 Well, I said, suppose we take a look at the throat first. 我以医生特有的职业方式微笑着,叫着孩子的名字。我说,来吧,玛蒂尔达,张开嘴,让我看一下你的嗓子。 I smiled in my best professional manner and asking for the child’s first name I said, come on, Mathilda, open your mouth and let’s take a look at your throat.没有任何反应。 Nothing doing. 哦,来吧,我劝道,张大你的嘴,让我看看。看,我说着把两只手伸开,我的手里没有东西,张大嘴,让我看看。 Aw, come on, I coaxed, just open your mouth wide and let me take a look. Look, I said opening both hands wide, I haven’t anything in my hands. Just open up and let me see.

曹操《短歌行【对酒当歌】》原文、翻译、赏析译文 原文 面对美酒应该高歌,人生短促日月如梭。对酒当歌,人生几何? 好比晨露转瞬即逝,失去的时日实在太多!譬如朝露,去日苦多。 席上歌声激昂慷慨,忧郁长久填满心窝。慨当以慷,忧思难忘。 靠什么来排解忧闷?唯有狂饮方可解脱。何以解忧?唯有杜康。 那穿着青领(周代学士的服装)的学子哟,你们令我朝夕思慕。青青子衿,悠悠我心。 正是因为你们的缘故,我一直低唱着《子衿》歌。但为君故,沉吟至今。 阳光下鹿群呦呦欢鸣,悠然自得啃食在绿坡。呦呦鹿鸣,食野之苹。 一旦四方贤才光临舍下,我将奏瑟吹笙宴请宾客。我有嘉宾,鼓瑟吹笙。 当空悬挂的皓月哟,你运转着,永不停止;明明如月,何时可掇? 我久蓄于怀的忧愤哟,突然喷涌而出汇成长河。忧从中来,不可断绝。 远方宾客踏着田间小路,一个个屈驾前来探望我。越陌度阡,枉用相存。 彼此久别重逢谈心宴饮,争着将往日的情谊诉说。契阔谈讌,心念旧恩。 明月升起,星星闪烁,一群寻巢乌鹊向南飞去。月明星稀,乌鹊南飞。 绕树飞了三周却没敛绕树三匝,何枝

翅,哪里才有它们栖身之 所? 可依? 高山不辞土石才见巍 峨,大海不弃涓流才见壮阔。(比喻用人要“唯才是举”,多多益善。)山不厌高,水不厌深。 只有像周公那样礼待贤 才(周公见到贤才,吐出口 中正在咀嚼的食物,马上接 待。《史记》载周公自谓: “一沐三握发,一饭三吐哺, 犹恐失天下之贤。”),才 能使天下人心都归向我。 周公吐哺,天 赏析 曹操是汉末杰出的政治家、军事家和文学家,他雅好诗章,好作乐府歌辞,今存诗22首,全是乐府诗。曹操的乐府诗多描写他本人的政治主张和统一天下的雄心壮志。如他的《短歌行》,充分表达了诗人求贤若渴以及统一天下的壮志。 《短歌行》是政治性很强的诗作,主要是为曹操当时所实行的政治路线和政策策略服务的,但是作者将政治内容和意义完全熔铸在浓郁的抒情意境之中,全诗充分发挥了诗歌创作的特长,准确而巧妙地运用了比兴手法,寓理于情,以情感人。诗歌无论在思想内容还是在艺术上都取得了极高的成就,语言质朴,立意深远,气势充沛。这首带有建安时代"志深比长""梗概多气"的时代特色的《短歌行》,读后不觉思接千载,荡气回肠,受到强烈的感染。 对酒当歌,人生几何? 譬如朝露,去日苦多。 慨当以慷,幽思难忘。 何以解忧,唯有杜康。 青青子衿,悠悠我心。 但为君故,沈吟至今。 呦呦鹿鸣,食野之苹。 我有嘉宾,鼓瑟吹笙。 明明如月,何时可掇? 忧从中来,不可断绝。 越陌度阡,枉用相存。 契阔谈,心念旧恩。 月明星稀,乌鹊南飞, 绕树三匝,何枝可依? 山不厌高,海不厌深, 周公吐哺,天下归心。 《短歌行》是汉乐府的旧题,属于《相和歌?平调曲》。这就是说它本来是一个乐曲的名称,这种乐曲怎么唱法,现在当然是不知道了。但乐府《相和歌?平调曲》中除了《短歌行》还有《长歌行》,唐代吴兢《乐府古题要解》引证古诗“长歌正激烈”,魏文帝曹丕《燕歌行》“短歌微吟不能长”和晋代傅玄《艳歌行》“咄来长歌续短歌”等句,认为“长歌”、“短

外国文学名著鉴赏期末论文院—系:数学学院 科目:外国文学名著鉴赏(期末论文)班级: 08级数学与应用数学A班 姓名:沈铁 学号: 200805050149 上课时段:周五晚十、十一节课

奋斗了,才有出路 ——读《鲁宾逊漂游记》有感小说《鲁宾逊漂游记》一直深受人们的喜爱。读完这篇小说,使我对人生应该有自己的一个奋斗历程而受益匪浅。当一个人已经处于绝境的时候,还能够满怀信心的去面对和挑战生活,实在是一种可贵的精神。他使我认识到,人无论何时何地,不管遇到多大的困难,都不能被困难所吓倒,我们要勇敢的面对困难,克服困难,始终保持一种积极向上、乐观的心态去面对。在当今社会只有努力去奋斗,才会有自己的出路! 其实现在的很多人都是那些遇到困难就退缩,不敢勇敢的去面对它。不仅如此,现在很多人都是独生子女,很多家长视子女为掌上明珠,不要说是冒险了,就连小小的家务活也不让孩子做,天天总是说:“我的小宝贝啊,你读好书就行了,其它的爸爸妈妈做就可以了。”读书固然重要,但生活中的小事也不能忽略。想一想,在荒无人烟的孤岛上,如果你连家务活都不会做,你能在那里生存吗?读完这部著作后,我不禁反问自己:“如果我像书中的鲁宾逊那样在大海遭到风暴,我能向他那样与风暴搏斗,最后逃离荒岛得救吗?恐怕我早已经被大海所淹没;如果我漂流到孤岛,能活几天?我又能干些什么?我会劈柴吗?会打猎做饭吗?我连洗洗自己的衣服还笨手笨脚的。”我们应该学习鲁宾逊这种不怕困难的精神,无论何时何地都有坚持地活下去,哪怕只有一线希望也要坚持到底,决不能放弃!我们要像鲁宾

逊那样有志气、有毅力、爱劳动,凭自己的双手创造财富,创造奇迹,取得最后的胜利。这样的例子在我们的生活中屡见不鲜。 《史记》的作者司马迁含冤入狱,可它依然在狱中完成《史记》一书,他之所以能完成此书,靠的也是他心中那顽强的毅力,永不放弃的不断努力的精神。著名作家爱迪生从小就生活在一个贫困的家庭中,可是他从小就表现出了科学方面的天赋。长大后爱迪生着力于电灯的发明与研究,他经过了九百多次的失败,可它依然没有放弃,不断努力,最后终于在第一千次实验中取得了成功。 鲁宾逊在岛上生活了二十八年,他面对了各种各样的困难和挫折,克服了许多常人无法想象的困难,自己动手,丰衣足食,以惊人的毅力,顽强的活了下来。他自从大船失事后,找了一些木材,在岛上盖了一间房屋,为防止野兽,还在房子周围打了木桩,来到荒岛,面对着的首要的就是吃的问题,船上的东西吃完以后,鲁宾逊开始打猎,有时可能会饿肚子,一是他决定播种,几年后他终于可以吃到自己的劳动成果,其实学习也是这样,也有这样一个循序渐进的过程,现在的社会,竞争无处不在,我们要懂得只有付出才会有收获,要勇于付出,在战胜困难的同时不断取得好成绩。要知道只有付出,才会有收获。鲁宾逊在失败后总结教训,终于成果;磨粮食没有石磨,他就用木头代替;没有筛子,就用围巾。鲁宾逊在荒岛上解决了自己的生存难题,面对人生挫折,鲁宾逊的所作所为充分显示了他坚毅的性格和顽强的精神。同样我们在学习上也可以做一些创新,养成一种创新精神,把鲁宾逊在荒岛,不畏艰险,不怕失败挫折,艰苦奋斗的精

The way的用法及其含义(二) 二、the way在句中的语法作用 the way在句中可以作主语、宾语或表语: 1.作主语 The way you are doing it is completely crazy.你这个干法简直发疯。 The way she puts on that accent really irritates me. 她故意操那种口音的样子实在令我恼火。The way she behaved towards him was utterly ruthless. 她对待他真是无情至极。 Words are important, but the way a person stands, folds his or her arms or moves his or her hands can also give us information about his or her feelings. 言语固然重要,但人的站姿,抱臂的方式和手势也回告诉我们他(她)的情感。 2.作宾语 I hate the way she stared at me.我讨厌她盯我看的样子。 We like the way that her hair hangs down.我们喜欢她的头发笔直地垂下来。 You could tell she was foreign by the way she was dressed. 从她的穿著就可以看出她是外国人。 She could not hide her amusement at the way he was dancing. 她见他跳舞的姿势,忍俊不禁。 3.作表语 This is the way the accident happened.这就是事故如何发生的。 Believe it or not, that's the way it is. 信不信由你, 反正事情就是这样。 That's the way I look at it, too. 我也是这么想。 That was the way minority nationalities were treated in old China. 那就是少数民族在旧中

曹操《短歌行》其二翻译及赏析 引导语:曹操(155—220),字孟德,小名阿瞒,《短歌行 二首》 是曹操以乐府古题创作的两首诗, 第一首诗表达了作者求贤若渴的心 态,第二首诗主要是曹操向内外臣僚及天下表明心迹。 短歌行 其二 曹操 周西伯昌,怀此圣德。 三分天下,而有其二。 修奉贡献,臣节不隆。 崇侯谗之,是以拘系。 后见赦原,赐之斧钺,得使征伐。 为仲尼所称,达及德行, 犹奉事殷,论叙其美。 齐桓之功,为霸之首。 九合诸侯,一匡天下。 一匡天下,不以兵车。 正而不谲,其德传称。 孔子所叹,并称夷吾,民受其恩。 赐与庙胙,命无下拜。 小白不敢尔,天威在颜咫尺。 晋文亦霸,躬奉天王。 受赐圭瓒,钜鬯彤弓, 卢弓矢千,虎贲三百人。 威服诸侯,师之所尊。 八方闻之,名亚齐桓。 翻译 姬昌受封为西伯,具有神智和美德。殷朝土地为三份,他有其中两分。 整治贡品来进奉,不失臣子的职责。只因为崇侯进谗言,而受冤拘禁。 后因为送礼而赦免, 受赐斧钺征伐的权利。 他被孔丘称赞, 品德高尚地位显。 始终臣服殷朝帝王,美名后世流传遍。齐桓公拥周建立功业,存亡继绝为霸 首。

聚合诸侯捍卫中原,匡正天下功业千秋。号令诸侯以匡周室,主要靠的不是 武力。 行为磊落不欺诈,美德流传于身后。孔子赞美齐桓公,也称赞管仲。 百姓深受恩惠,天子赐肉与桓公,命其无拜来接受。桓公称小白不敢,天子 威严就在咫尺前。 晋文公继承来称霸,亲身尊奉周天王。周天子赏赐丰厚,仪式隆重。 接受玉器和美酒,弓矢武士三百名。晋文公声望镇诸侯,从其风者受尊重。 威名八方全传遍,名声仅次于齐桓公。佯称周王巡狩,招其天子到河阳,因 此大众议论纷纷。 赏析 《短歌行》 (“周西伯昌”)主要是曹操向内外臣僚及天下表明心 迹,当他翦灭群凶之际,功高震主之时,正所谓“君子终日乾乾,夕惕若 厉”者,但东吴孙权却瞅准时机竟上表大说天命而称臣,意在促曹操代汉 而使其失去“挟天子以令诸侯”之号召, 故曹操机敏地认识到“ 是儿欲据吾著炉上郁!”故曹操运筹谋略而赋此《短歌行 ·周西伯 昌》。 西伯姬昌在纣朝三分天下有其二的大好形势下, 犹能奉事殷纣, 故孔子盛称 “周之德, 其可谓至德也已矣。 ”但纣王亲信崇侯虎仍不免在纣王前 还要谗毁文王,并拘系于羑里。曹操举此史实,意在表明自己正在克心效法先圣 西伯姬昌,并肯定他的所作所为,谨慎惕惧,向来无愧于献帝之所赏。 并大谈西伯姬昌、齐桓公、晋文公皆曾受命“专使征伐”。而当 今天下时势与当年的西伯、齐桓、晋文之际颇相类似,天子如命他“专使 征伐”以讨不臣,乃英明之举。但他亦效西伯之德,重齐桓之功,戒晋文 之诈。然故作谦恭之辞耳,又谁知岂无更讨封赏之意乎 ?不然建安十八年(公元 213 年)五月献帝下诏曰《册魏公九锡文》,其文曰“朕闻先王并建明德, 胙之以土,分之以民,崇其宠章,备其礼物,所以藩卫王室、左右厥世也。其在 周成,管、蔡不静,惩难念功,乃使邵康公赐齐太公履,东至于海,西至于河, 南至于穆陵,北至于无棣,五侯九伯,实得征之。 世祚太师,以表东海。爰及襄王,亦有楚人不供王职,又命晋文登为侯伯, 锡以二辂、虎贲、斧钺、禾巨 鬯、弓矢,大启南阳,世作盟主。故周室之不坏, 系二国是赖。”又“今以冀州之河东、河内、魏郡、赵国、中山、常 山,巨鹿、安平、甘陵、平原凡十郡,封君为魏公。锡君玄土,苴以白茅,爰契 尔龟。”又“加君九锡,其敬听朕命。” 观汉献帝下诏《册魏公九锡文》全篇,尽叙其功,以为其功高于伊、周,而 其奖却低于齐、晋,故赐爵赐土,又加九锡,奖励空前。但曹操被奖愈高,心内 愈忧。故曹操在曾早在五十六岁写的《让县自明本志令》中谓“或者人见 孤强盛, 又性不信天命之事, 恐私心相评, 言有不逊之志, 妄相忖度, 每用耿耿。

(一)文学常识 一、古希腊罗马 1.(1)宙斯(罗马神话称为朱庇特),希腊神话中最高的天神,掌管雷电云雨,是人和神的主宰。 (2)阿波罗,希腊神话中宙斯的儿子,主管光明、青春、音乐、诗歌等,常以手持弓箭的少年形象出现。 (3)雅典那,希腊神话中的智慧女神,雅典城邦的保护神。 (4)潘多拉,希腊神话中的第一个女人,貌美性诈。私自打开了宙斯送她的一只盒子,里面装的疾病、疯狂、罪恶、嫉妒等祸患,一齐飞出,只有希望留在盒底,人间因此充满灾难。“潘多拉的盒子”成为“祸灾的来源”的同义语。 (5)普罗米修斯,希腊神话中造福人间的神。盗取天火带到人间,并传授给人类多种手艺,触怒宙斯,被锁在高加索山崖,受神鹰啄食,是一个反抗强暴、不惜为人类牺牲一切的英雄。 (6)斯芬克司,希腊神话中的狮身女怪。常叫过路行人猜谜,猜不出即将行人杀害;后因谜底被俄底浦斯道破,即自杀。后常喻“谜”一样的人物。与埃及狮身人面像同名。 2.荷马,古希腊盲诗人。主要作品有《伊利亚特》和《奥德赛》,被称为荷马史诗。《伊利亚特》叙述十年特洛伊战争。《奥德赛》写特洛伊战争结束后,希腊英雄奥德赛历险回乡的故事。马克思称赞它“显示出永久的魅力”。 3.埃斯库罗斯,古希腊悲剧之父,代表作《被缚的普罗米修斯》。6.阿里斯托芬,古希腊“喜剧之父”代表作《阿卡奈人》。 4.索福克勒斯,古希腊重要悲剧作家,代表作《俄狄浦斯王》。5.欧里庇得斯,古希腊重要悲剧作家,代表作《美狄亚》。 二、中世纪文学 但丁,意大利人,伟大诗人,文艺复兴的先驱。恩格斯称他是“中世纪的最后一位诗人,同时又是新时代的最初一位诗人”。主要作品有叙事长诗《神曲》,由地狱、炼狱、天堂三部分组成。《神曲》以幻想形式,写但丁迷路,被人导引神游三界。在地狱中见到贪官污吏等受着惩罚,在净界中见到贪色贪财等较轻罪人,在天堂里见到殉道者等高贵的灵魂。 三、文艺复兴时期 1.薄迦丘意大利人短篇小说家,著有《十日谈》拉伯雷,法国人,著《巨人传》塞万提斯,西班牙人,著《堂?吉诃德》。 2.莎士比亚,16-17世纪文艺复兴时期英国伟大的剧作家和诗人,主要作品有四大悲剧——《哈姆雷特》、《奥赛罗》《麦克白》、《李尔王》,另有悲剧《罗密欧与朱丽叶》等,喜剧有《威尼斯商人》《第十二夜》《皆大欢喜》等,历史剧有《理查二世》、《亨利四世》等。马克思称之为“人类最伟大的戏剧天才”。 四、17世纪古典主义 9.笛福,17-18世纪英国著名小说家,被誉为“英国和欧洲小说之父”,主要作品《鲁滨逊漂流记》,是英国第一部现实主义长篇小说。10.弥尔顿,17世纪英国诗人,代表作:长诗《失乐园》,《失乐园》,表现了资产阶级清教徒的革命理想和英雄气概。 25.拉伯雷,16世纪法国作家,代表作:长篇小说《巨人传》。 26.莫里哀,法国17世纪古典主义文学最重要的作家,法国古典主义喜剧的创建者,主要作品为《伪君子》《悭吝人》(主人公叫阿巴公)等喜剧。 五、18世纪启蒙运动 1)歌德,德国文学最高成就的代表者。主要作品有书信体小说《少年维特之烦恼》,诗剧《浮士德》。 11.斯威夫特,18世纪英国作家,代表作:《格列佛游记》,以荒诞的情节讽刺了英国现实。 12.亨利·菲尔丁,18世纪英国作家,代表作:《汤姆·琼斯》。 六、19世纪浪漫主义 (1拜伦, 19世纪初期英国伟大的浪漫主义诗人,代表作为诗体小说《唐璜》通过青年贵族唐璜的种种经历,抨击欧洲反动的封建势力。《恰尔德。哈洛尔游记》 (2雨果,伟大作家,欧洲19世纪浪漫主义文学最卓越的代表。主要作品有长篇小说《巴黎圣母院》、《悲惨世界》、《笑面人》、《九三年》等。《悲惨世界》写的是失业短工冉阿让因偷吃一片面包被抓进监狱,后改名换姓,当上企业主和市长,但终不能摆脱迫害的故事。《巴黎圣母院》 弃儿伽西莫多,在一个偶然的场合被副主教克洛德.孚罗洛收养为义子,长大后有让他当上了巴黎圣母院的敲钟人。他虽然十分丑陋而且有多种残疾,心灵却异常高尚纯洁。 长年流浪街头的波希米亚姑娘拉.爱斯梅拉达,能歌善舞,天真貌美而心地淳厚。青年贫诗人尔比埃尔.甘果瓦偶然同她相遇,并在一个更偶然的场合成了她名义上的丈夫。很有名望的副教主本来一向专心于"圣职",忽然有一天欣赏到波希米亚姑娘的歌舞,忧千方百计要把她据为己有,对她进行了种种威胁甚至陷害,同时还为此不惜玩弄卑鄙手段,去欺骗利用他的义子伽西莫多和学生甘果瓦。眼看无论如何也实现不了占有爱斯梅拉达的罪恶企图,最后竟亲手把那可爱的少女送上了绞刑架。 另一方面,伽西莫多私下也爱慕着波希米亚姑娘。她遭到陷害,被伽西莫多巧计救出,在圣母院一间密室里避难,敲钟人用十分纯朴和真诚的感情去安慰她,保护她。当她再次处于危急中时,敲钟人为了援助她,表现出非凡的英勇和机智。而当他无意中发现自己的"义父"和"恩人"远望着高挂在绞刑架上的波希米亚姑娘而发出恶魔般的狞笑时,伽西莫多立即对那个伪善者下了最后的判决,亲手把克洛德.孚罗洛从高耸入云的钟塔上推下,使他摔的粉身碎骨。 (3司汤达,批判现实主义作家。代表作《红与黑》,写的是不满封建制度的平民青年于连,千方百计向上爬,最终被送上断头台的故事。“红”是将军服色,指“入军界”的道路;“黑”是主教服色,指当神父、主教的道路。 14.雪莱,19世纪积极浪漫主义诗人,欧洲文学史上最早歌颂空想社会主义的诗人之一,主要作品为诗剧《解放了的普罗米修斯》,抒情诗《西风颂》等。 15.托马斯·哈代,19世纪英国作家,代表作:长篇小说《德伯家的苔丝》。 16.萨克雷,19世纪英国作家,代表作:《名利场》 17.盖斯凯尔夫人,19世纪英国作家,代表作:《玛丽·巴顿》。 18.夏洛蒂?勃朗特,19世纪英国女作家,代表作:长篇小说《简?爱》19艾米丽?勃朗特,19世纪英国女作家,夏洛蒂?勃朗特之妹,代表作:长篇小说《呼啸山庄》。 20.狄更斯,19世纪英国批判现实主义文学的重要代表,主要作品为长篇小说《大卫?科波菲尔》、《艰难时世》《双城记》《雾都孤儿》。21.柯南道尔,19世纪英国著名侦探小说家,代表作品侦探小说集《福尔摩斯探案》是世界上最著名的侦探小说。 七、19世纪现实主义 1、巴尔扎克,19世纪上半叶法国和欧洲批判现实主义文学的杰出代表。主要作品有《人间喜剧》,包括《高老头》、《欧也妮·葛朗台》、《贝姨》、《邦斯舅舅》等。《人间喜剧》是世界文学中规模最宏伟的创作之一,也是人类思维劳动最辉煌的成果之一。马克思称其“提供了一部法国社会特别是巴黎上流社会的卓越的现实主义历史”。

定冠词the的用法: 定冠词the与指示代词this ,that同源,有“那(这)个”的意思,但较弱,可以和一个名词连用,来表示某个或某些特定的人或东西. (1)特指双方都明白的人或物 Take the medicine.把药吃了. (2)上文提到过的人或事 He bought a house.他买了幢房子. I've been to the house.我去过那幢房子. (3)指世界上独一无二的事物 the sun ,the sky ,the moon, the earth (4)单数名词连用表示一类事物 the dollar 美元 the fox 狐狸 或与形容词或分词连用,表示一类人 the rich 富人 the living 生者 (5)用在序数词和形容词最高级,及形容词等前面 Where do you live?你住在哪? I live on the second floor.我住在二楼. That's the very thing I've been looking for.那正是我要找的东西. (6)与复数名词连用,指整个群体 They are the teachers of this school.(指全体教师) They are teachers of this school.(指部分教师) (7)表示所有,相当于物主代词,用在表示身体部位的名词前 She caught me by the arm.她抓住了我的手臂. (8)用在某些有普通名词构成的国家名称,机关团体,阶级等专有名词前 the People's Republic of China 中华人民共和国 the United States 美国 (9)用在表示乐器的名词前 She plays the piano.她会弹钢琴. (10)用在姓氏的复数名词之前,表示一家人 the Greens 格林一家人(或格林夫妇) (11)用在惯用语中 in the day, in the morning... the day before yesterday, the next morning... in the sky... in the dark... in the end... on the whole, by the way...

The use of force 大意: Mathilda had been ill for three days. Her mother had given her some medicine, but it didn’t do any good. So they had to ask the doctor to come. There had been a number of cases of diphtheria in Mathilda School and two of them had been dead. When the doctor arrived at Olson’s home, he wanted to examine Mathilda throat first. But no matter how he coaxed, She wouldn’t open her mouth. So the doctor had to get the tongue depressor into her mouth. But Mathilda reduced it to splinters. In orde r to protect Mathilda herself and other children, the doctor had to make sure whether she had diphtheria or not, so that he could treat her in time. Letting Mathilda‘s father hold her wrists he tried his best to open her mouth and found she really had diphtheria. This story made us can think such a question that something in life can’t only depend on self-willingness. Under some circumstances, certain force seems necessary. 对医生的评价:After the doctor arrived at the girl’s home, he wanted to see her throat. As there had been a number of cases of diphtheria in the school to which the girl went during that month, the doctor also thought that of the girl. So he smiled to the girl and asked her to open her mouth and let him have a look at her throat. No matter how the doctor coaxed, the girl shut her mouth firmly. Thinking that the girl might have diphtheria and possibly die of it, the doctor decided to use force to open her mouth. He had seen at least two children lying dead in bed of neglect in such cases. He felt that he must get a diagnosis now. So he grasped the girl’s head with his left hand and tried to get the wooden tongue depressor between her teeth. But when the doctor got the wooden spatula behind her last teeth. She gripped the blade between her molars and reduced it to splinters. In the final unreasoning assault the doctor outer powered the girl. He forced the heavy silver spoon back of her teeth and down her throat till she gagged. Her both tonsils were covered with membrane. From that the doctor had done, I thought he was a responsible person. In order to save the lives of the patients, especially those children who did not know how to co-operate with the doctor, he had to take some measure. Otherwise a good or suitable time of treatment would be missed. The doctor appears to be compassionate and keen to human behavior, characteristic of a good doctor, though he is also undeniably blunt and slightly prejudiced. 思想: Though there are reasons often justifiable, what compels the use of force against others isn't simply altruism alone. The overall theme of the story revolves around power and submission and the doctor's unnerved feeling following the forceful encounter. 作者如何写的: The story is narrated in first person by a doctor, who is answering a house visit to see a sick girl. Williams uses interior monologue as a "stream-of-consciousness" tool reflects the narrator's experience of dialogue and gives insight into the character and his appraisal of the situations he encounters. The story is written without the use of quotation marks, and the dialogue is not distinguished from the narrator's comments. The story is rendered from the subjective point of view of the doctor, and explores his subdued enjoyment of forcefully subduing the stubborn child in an attempt to acquire the throat sample.

题目:浅析从简爱到女性的尊严和爱 学院工商学院 专业新闻学3 学号 姓名闫万里 学科外国文学名着赏析 [摘要] 十九世纪中期,英国伟大的女性存在主义先驱,着名作家夏洛蒂勃朗特创作出了她的代表作--《简爱》,当时轰动了整个文坛,它是一部具有浓厚浪漫主义色彩的现实主义小说,被认为是作者"诗意的生平"的写照。它在问世后的一百多年里,它始终保持着历史不败的艺术感染力。直到现在它的影响还继续存在。在作品的序幕、发展、高潮和结尾中,女主人公的叛逆、自由、平等、自尊、纯洁的个性都是各个重点章节的主旨,而这些主旨则在女主人公的爱情观中被展露的淋漓尽致,它们如同乌云上方的星汉,灼灼闪耀着光芒,照亮着后来的女性者们追求爱情的道路。? [关键词] 自尊个性独特新女性主义自由独立平等 《简爱》是一部带有自转色彩的长篇小说,它阐释了这样一个主题:人的价值=尊严+爱。从小就成长在一个充满暴力的环境中的简爱,经历了同龄人没有的遭遇。她要面对的是舅妈的毫无人性的虐待,表兄的凶暴专横和表姐的傲慢冷漠,尽管她尽力想“竭力赢得别人的好感”,但是事实告诉她这都是白费力气的,因此她发出了“不公平啊!--不公平!”的近乎绝望的呼喊。不公平的生长环境,使得简爱从小就向往平等、自由和爱,这些愿望在她后来的成长过程中表现无疑,

譬如在她的爱情观中的种种体现。? 1.桑菲尔德府? 谭波儿小姐因为出嫁,离开了洛伍德学校,同时也离开了简爱,这使简爱感觉到了“一种稳定的感觉,一切使我觉得洛伍德学校有点像我家的联想,全都随着她消失了”,她意识到:真正的世界是广阔的,一个充满希望和忧虑、激动和兴奋的变化纷呈的天地,正等待着敢于闯入、甘冒风险寻求人生真谛的人们。意识形态的转变促使着简爱走向更广阔的社会,接受社会的挑战,尽管她才只有十八岁。于是,简爱来到了桑菲尔德府,当了一名在当时地位不高的家庭教师。?桑菲尔德府使简爱感受到“这儿有想象中的完美无缺的家庭安乐气氛”,事实证明了她的预感的正确性,。从和简爱相见、相识到相爱的过程当中,简爱的那种叛逆精神、自强自尊的品质深深地征服了罗切斯特,而罗切斯特的优雅风度和渊博知识同样也征服了简爱。最初开始,简爱一直以为罗切斯特会娶高贵漂亮的英格拉姆为妻,她在和罗切斯特谈到婚姻时,曾经义正言辞的对罗切斯特说:“你以为因为我穷,低微,不美,矮小,就没有灵魂了吗?你想错了!我跟你一样有灵魂—也同样有一颗心!我现在不是凭着肉体凡胎跟你说话,而是我的心灵在和你的心灵说话,就好像我们都已经离开人世,两人平等地站在上帝面前—因为我们本来就是平等的。”这充分表现出简爱的叛逆,她这种维护妇女独立人格、主张婚姻独立自主以及男女平等的主张可以看成是他对整个人类社会自由平等的向往追求,罗切斯特正是爱上了她这样的独特个性,同时他也同样重复道:我们本来就是平等的。罗切斯特自始自终爱的是简爱的心灵—有着意志的力量,美德和纯洁的心灵,正是基于如此,简爱才真正的爱着罗切斯特。因为爱情是来不得半点虚假的,一方为另一方付出了真情的爱,假如得到对方的是虚情假意,那么这份爱

“theway+从句”结构的意义及用法 首先让我们来看下面这个句子: Read the followingpassageand talkabout it wi th your classmates.Try totell whatyou think of Tom and ofthe way the childrentreated him. 在这个句子中,the way是先行词,后面是省略了关系副词that或in which的定语从句。 下面我们将叙述“the way+从句”结构的用法。 1.the way之后,引导定语从句的关系词是that而不是how,因此,<<现代英语惯用法词典>>中所给出的下面两个句子是错误的:This is thewayhowithappened. This is the way how he always treats me. 2.在正式语体中,that可被in which所代替;在非正式语体中,that则往往省略。由此我们得到theway后接定语从句时的三种模式:1) the way+that-从句2)the way +in which-从句3) the way +从句 例如:The way(in which ,that) thesecomrade slookatproblems is wrong.这些同志看问题的方法

不对。 Theway(that ,in which)you’re doingit is comple tely crazy.你这么个干法,简直发疯。 Weadmired him for theway inwhich he facesdifficulties. Wallace and Darwingreed on the way inwhi ch different forms of life had begun.华莱士和达尔文对不同类型的生物是如何起源的持相同的观点。 This is the way(that) hedid it. I likedthe way(that) sheorganized the meeting. 3.theway(that)有时可以与how(作“如何”解)通用。例如: That’s the way(that) shespoke. = That’s how shespoke.

短歌行赏析介绍 说道曹操, 大家一定就联想到三国那些烽火狼烟岁月吧。 但是曹操其实也是 一位文学 大家,今天就来分享《短歌行 》赏析。 《短歌行》短歌行》是汉乐府旧题,属于《相和歌辞·平调曲》。这就是说 它本来是一个乐曲名称。最初古辞已经失传。乐府里收集同名诗有 24 首,最早 是曹操这首。 这种乐曲怎么唱法, 现在当然是不知道。 但乐府 《相和歌·平调曲》 中除《短歌行》还有《长歌行》,唐代吴兢《乐府古题要解》引证古诗 “长歌正激烈”, 魏文帝曹丕 《燕歌行》 “短歌微吟不能长”和晋代傅玄 《艳 歌行》 “咄来长歌续短歌”等句, 认为“长歌”、 “短歌”是指“歌声有长短”。 我们现在也就只能根据这一点点材料来理解《短歌行》音乐特点。《短歌行》这 个乐曲,原来当然也有相应歌辞,就是“乐府古辞”,但这古辞已经失传。现在 所能见到最早《短歌行》就是曹操所作拟乐府《短歌行》。所谓“拟乐府”就是 运用乐府旧曲来补作新词,曹操传世《短歌行》共有两首,这里要介绍是其中第 一首。 这首《短歌行》主题非常明确,就是作者希望有大量人才来为自己所用。曹 操在其政治活动中,为扩大他在庶族地主中统治基础,打击反动世袭豪强势力, 曾大力强调“唯才是举”,为此而先后发布“求贤令”、“举士令”、“求逸才 令”等;而《短歌行》实际上就是一曲“求贤歌”、又正因为运用诗歌 形式,含有丰富抒情成分,所以就能起到独特感染作用,有力地宣传他所坚 持主张,配合他所颁发政令。 《短歌行》原来有“六解”(即六个乐段),按照诗意分为四节来读。 “对酒当歌,人生几何?譬如朝露,去日苦多。慨当以慷,忧思难忘。何以 解忧,唯有杜康。” 在这八句中,作者强调他非常发愁,愁得不得。那么愁是什么呢?原来他是 苦于得不到众多“贤才”来同他合作, 一道抓紧时间建功立业。 试想连曹操这样 位高权重人居然在那里为“求贤”而发愁, 那该有多大宣传作用。 假如庶族地主 中真有“贤才”话, 看这些话就不能不大受感动和鼓舞。 他们正苦于找不到出路