MOSFET的驱动技术详解

simtriex/simplis仿真电路用软件

MOSFET作为功率开关管,已经是是开关电源领域的绝对主力器件。虽然MOSFET作为电压型驱动器件,其驱动表面上看来是非常简单,但是详细分析起来并不简单。下面我会花一点时间,一点点来解析MOSFET的驱动技术,以及在不同的应用,应该采用什么样的驱动电路。

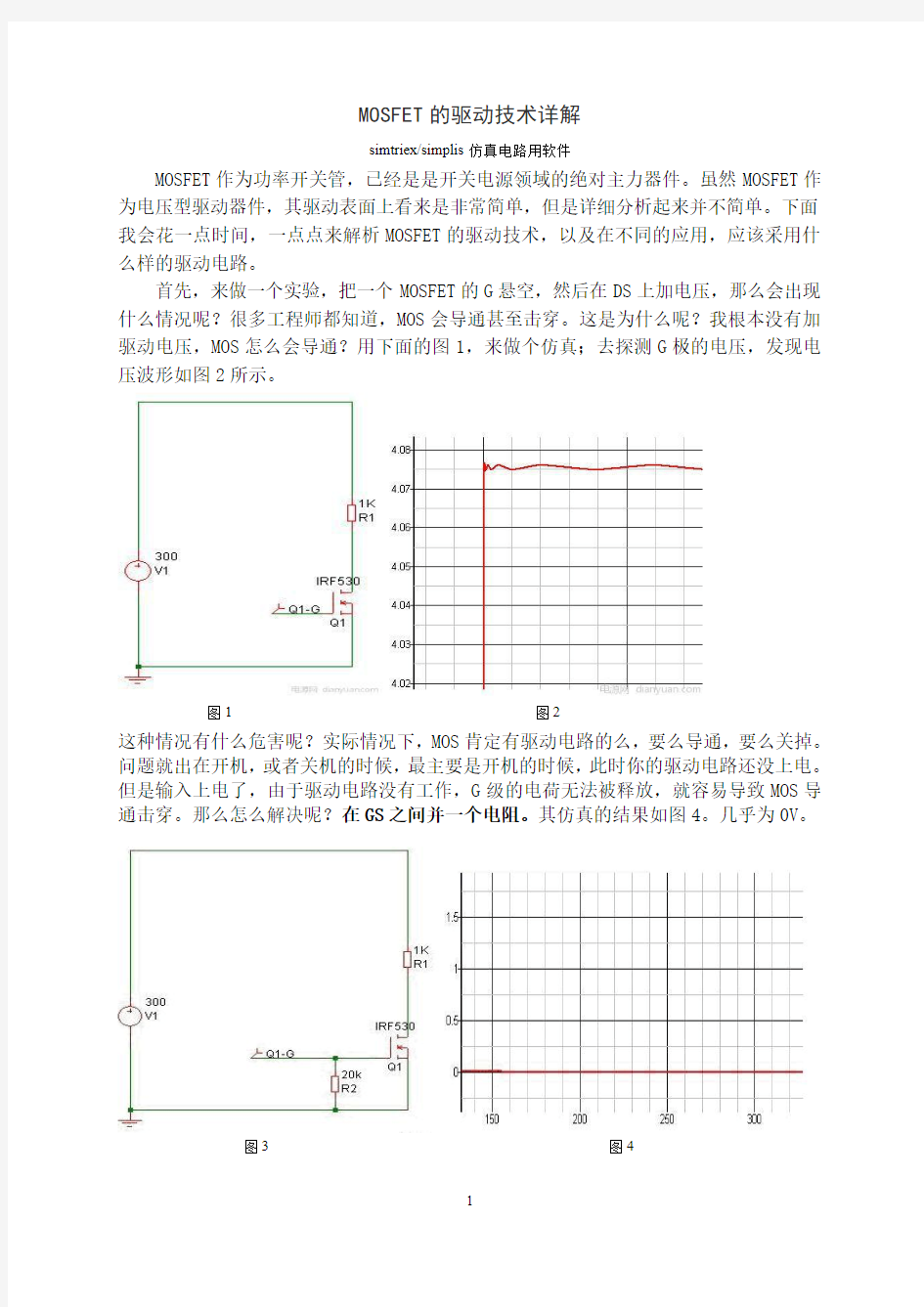

首先,来做一个实验,把一个MOSFET的G悬空,然后在DS上加电压,那么会出现什么情况呢?很多工程师都知道,MOS会导通甚至击穿。这是为什么呢?我根本没有加驱动电压,MOS怎么会导通?用下面的图1,来做个仿真;去探测G极的电压,发现电压波形如图2所示。

图1图2

这种情况有什么危害呢?实际情况下,MOS肯定有驱动电路的么,要么导通,要么关掉。问题就出在开机,或者关机的时候,最主要是开机的时候,此时你的驱动电路还没上电。但是输入上电了,由于驱动电路没有工作,G级的电荷无法被释放,就容易导致MOS导通击穿。那么怎么解决呢?在GS之间并一个电阻。其仿真的结果如图4。几乎为0V。

图3图4

什么叫驱动能力,很多PWM 芯片,或者专门的驱动芯片都会说驱动能力,比如384X 的驱动能力为1A,其含义是什么呢?

假如驱动是个理想脉冲源,那么其驱动能力就是无穷大,想提供多大电流就给多大。但实际中,驱动是有内阻的,假设其内阻为10欧姆,在10V 电压下,最多能提供的峰值电流就是1A,通常也认为其驱动能力为1A。

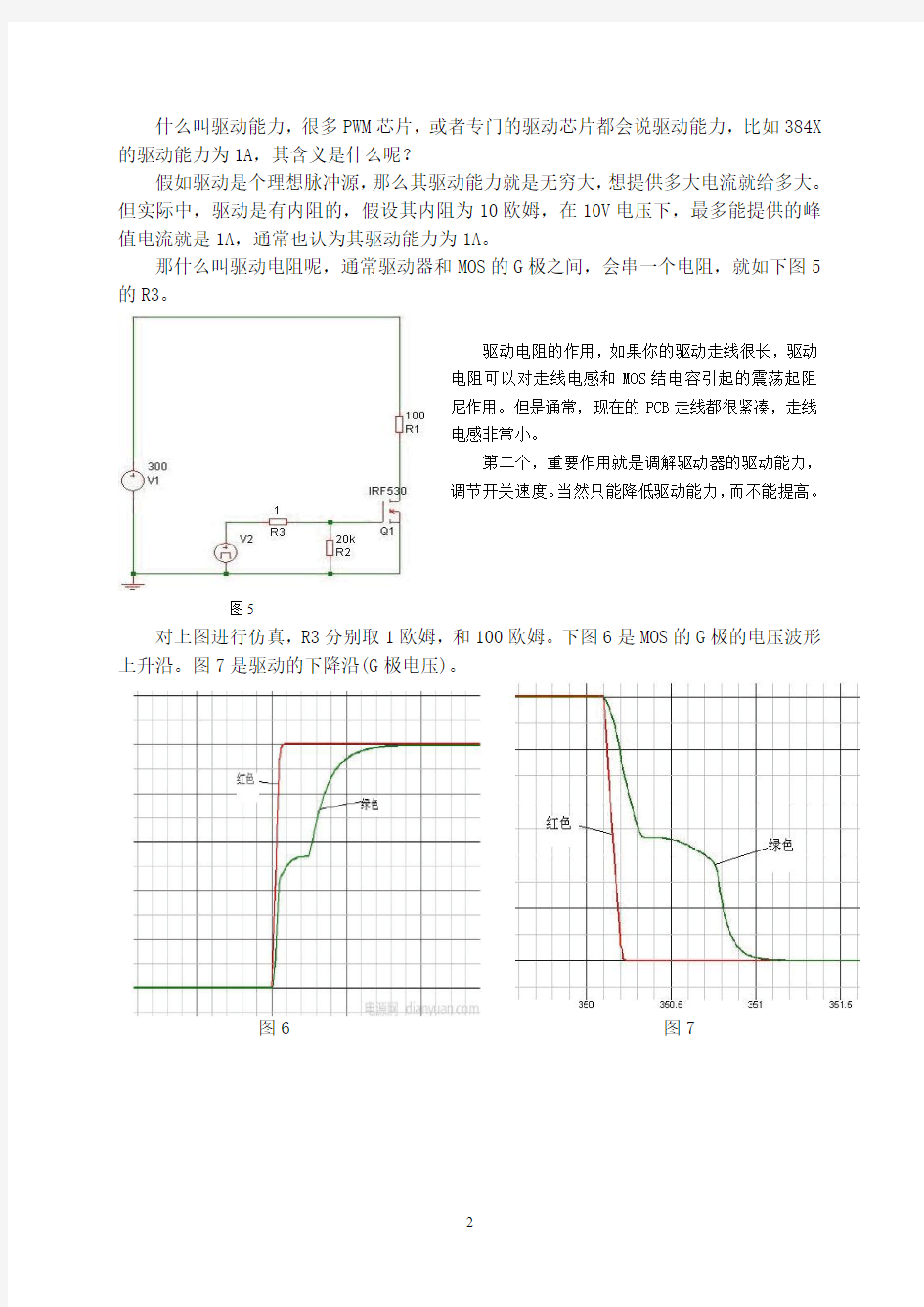

那什么叫驱动电阻呢,通常驱动器和MOS 的G 极之间,会串一个电阻,就如下图5的

R3。

图5

对上图进行仿真,R3分别取1欧姆,和100欧姆。下图6是MOS 的G 极的电压波形上升沿。图7是驱动的下降沿(G 极电压)。

图6图7

驱动电阻的作用,如果你的驱动走线很长,

驱动

电阻可以对走线电感和MOS 结电容引起的震荡起阻

尼作用。但是通常,现在的PCB 走线都很紧凑,走线

电感非常小。

第二个,重要作用就是调解驱动器的驱动能力,

调节开关速度。当然只能降低驱动能力,而不能提高。

那么驱动的快慢对MOS 的开关有什么影响呢?下图8是MOS 导通时候DS 的电压:图9是MOS 导通时候DS 电流波形:

图8

图9可以看到,驱动电阻增加可以降低MOS 开关的时候得电压电流的变化率。比较慢的开关速度,对EMI 有好处。下图10是对两个不同驱动情况下,MOS 的DS 电压波形做付利叶分析得到:

图10

红色的是R3=1欧姆,绿色的是R3=100欧姆。

可见R3越大,MOS 的导通速度越慢。红色的是R3=1欧姆,绿色的是R3=100欧姆。可见R3越大,MOS 的导通速度越慢。红色的是R3=1欧姆,

绿色的是R3=100欧

姆。可见,驱动电阻大

的时候,高频谐波明显

变小。

但是驱动速度慢,又有什么坏处呢?那就是开关损耗大了,下图11是不同驱动电阻下,导通损耗的功率曲线。

图11

结论:驱动电阻到底选多大?还真难讲,小了,EMI 不好,大了,效率不好。所以只能一个折中的选择了。

那如果,开通和关断的速度要分别调节,怎么办?就用以下电路图12、图13。

图12图13

MOSFET 的自举驱动:

对于NMOS 来说,必须是G 极的电压高于S 极一定电压才能导通。那么对于对S 极和控制IC 的地等电位的MOS 来说,驱动根本没有问题,如上图。

但是对于一些拓扑,比如BUCK(开关管放在上端),双管正激,双管反激,半桥,全桥这些拓扑的上管,就没办法直接用芯片去驱动,那么可以采用自举驱动电路。

看下图的BUCK

电路:

红色的是R3=1欧姆,绿色

的是R3=100欧姆。可见,

驱动电阻大的时候,损耗明

显大了。

图14

加入输入12V,MOS的导通阀值为3V,那么对于Q1来说,当Q1导通之后,如果要维持导通状态,Q1的G级必须保证15V以上的电压,因为S级已经有12V了。那么输入才12V,怎么得到15V的电压呢?其实上管Q1驱动的供电在于Cboot。

看下图15,芯片的内部结构:

图15

Cboot是挂在boot和LX之间的,而LX却是下管的D级,当下管导通的时候,LX 接地,芯片的内部基准通过Dboot(自举二极管)对Cboot充电。当下管关,上管通的时候,LX点的电压上升,Cboot上的电压自然就被举了起来。这样驱动电压才能高过输入电压。当然芯片内部的逻辑信号在提供给驱动的时候,还需要Level shift电路,把信号的电平电压也提上去。

Buck电路,现在有太多的控制芯片集成了自举驱动,让整个设计变得很简单。但是对于,双管的,桥式的拓扑,多数芯片没有集成驱动。那样就可以外加自举驱动芯片,48V系统输入的,可以采用Intersil公司的ISL21XX,HIP21XX系列。如果是AC/DC中,电压比较高的,可以采用IR的IR21XX系列。

下图16是ISL21XX的内部框图,其核心的东西,就是红圈里的boot二极管,和Level shift电路:

图16

ISL21XX驱动桥式电路示意图:

驱动双管电路图17:

图17

驱动有源钳位如图18:

图18

当然以上都是示意图,没有完整的外围电路,但是外围其实很简单,参考datasheet 即可。

zgthsx:

LZ是那个电压对电容充电啊会冲到多少负啊有是怎么冲的能不能解释一下啊?

echizen20:

同过CBOOT的的升压??是不是自举升压的道理呢?

tq5920:

楼主您好,说道自举电路,我想请教一般自举电容和二极管应该如何选择?有什么特别要求吗?谢谢!sometimes:

自举电容主要在于其大小,该电容在充电之后,就要对MOS的结电容充电,如果驱动电路上有其他功耗器件,也是该电容供电的。所以要求该电容足够大,在提供电荷之后,电容上的电压下跌最好不要超过原先值的10%,

这样才能保证驱动电压。但是也不用太大,太大的电容会导致二极管在充电的时候,冲击电流过大。对于二极管,由于平均电流不会太大,只要保证是快速二极管。当然,当自举电压比较低的时候,这个二极管的正向压降,尽量选小的。

tq5920:

请问您有没有用过IR2110或IR2111芯片,在高频时,自举电容和二极管应该如何选择?谢谢!sometimes:

电容没什么,磁片电容,几百n就可以了。但是二极管,要超快的,而且耐压要够。电流不用太大,1A足够。leetao365366:

楼主,请教您个问题。一般用MOS管驱动电机要注意哪些细节问题啊。其实MOS只是作为开关管,需要注意的是电机是感性器件,还有电机启动时候的冲击电流。还有堵转时候的的启动电流。

(变压器)隔离驱动

lingqidian:

详细的讲讲隔离驱动吧,在正激拓扑中,我常见到驱动信号连接到一个推挽对管,然后连接一个2R左右的电阻及一个电容然后连接到变压器的初级端,在变压器的次级端输出驱动信号给MOS,这种驱动方式的优点?变压器初级串联的电阻及电容如何设计?

sometimes:

隔离驱动。当控制和MOS处于电气隔离状态下,自举驱动就无法胜任了,那么就需要隔离驱动了。下面来讨论隔离驱动中最常用的,变压器隔离驱动。

Ez八度:

很好很实用的东西,对我们这样的只知道要加下拉电阻不知道其作用的人来说很好懂,期待旅长更多看似很基础实际很受用的课程

edifierwjq:

请问在大功率的系统中如果有几个开关管并联,还能用上文介绍的那些高端驱动芯片来驱动吗?sometimes:

可以的,但是你要选择驱动能力强的IC。

看个最简单的隔离驱动电路,被驱动的对象是Q1。

图19

驱动源参数为12V ,100KHz,D=0.5。

驱动变压器电感量为200uH,匝比为1:1。

图20

下图21为C1

上的电压。

图21

其平均电压为6V,但是峰峰值,却有2V,显然C1不够大,导致驱动信号最终不够平。那么把C1变为470n。Q1-G 的电压波形就变成如下图22:

图22

图

23红色波形为驱动

源V1的输出,绿

色为Q1的G级波

形。可以看到,

Q1-G 的波形为

具有正负电压的

方波,幅值6V

了。

为什么驱动电压

会下降呢,是因

为V1的电压直

流分量,完全被

C1阻挡了。所以

C1也称为隔直

电容。

驱动电压变得平缓了些。如果把驱动变压器的电感量增加到500uH。驱动信号就如上图23。驱动信号显得更为平缓。

lingqidian:

"其平均电压为6V,但是峰峰值,却有2V,显然C1不够大,导致驱动信号最终不够平。"请问这句话怎么理解,C1如果增大的话,由于对C1的存放电,驱动信号到G极后应该会更平滑,上升及下降都会变慢吧?但看你的仿真图好像更好了?串接R、C的取值如何计算?或者选择?

sometimes:

C1大的话,C1上的电压就会比较平稳,波动比较小,那么对驱动的影响就会变小。

smallmore:

楼主,我做了一个全桥的驱动,上面的不是平的,而是有一圆弧型的包包,再斜斜的下来,最后有一小段是平的,加大电容怎么调都是这样,是怎么回事呀?请赐教!!谢谢!

sometimes:

这个可能和你的驱动变压器的漏感有关系。

从这里可以看到,这种驱动,有个明显的特点,就是驱动电平,最终到达MOS的时候,电压幅度减小了,具体减小多少呢,应该是D*V,D为占空比,那么如果D很大的话,驱动电压就会变得很小,如下图24,D=0.9

图24图25

图24中,发现驱动到达MOS的时候,正压不到2V了。显然这种驱动不适合占空比大的情况。从上面可以看到,在驱动工作的时候,其实C1上面始终有一个电压存在,电压平均值为V*D,也就是说这个电容存储着一定的能量。那么这个能量的存在,会带来什么问题呢?下面模拟驱动突然掉电的情况,如图25:可见,在驱动突然关掉之后,C1上的能量,会引起驱动变的电感,C1以及mos 的结电容之间的谐振。如果这个谐振电压足够高的话,就会触发MOS管,对可靠性带来危害。

那么如何来降低这个震荡呢,在GS上并个电阻,下图26是并了1K电阻之后波形:但是这个电阻会给驱动带来额外的损耗。

图26

如何传递大占空比的驱动?看一个简单的驱动电路。图27:

xzszrs :

这个电路的神奇之处就是采用了D1的电平平移电路,使负电平平移到接近0V!相对而言提高了正向电平(绝对值电平是不变的)。进一步发挥的话D1可以改为两个背靠背的稳压二极管,比如上管为15V,下管为5V,这样可以提供+15V,-5V 的驱动电平驱动IGBT.当然次级加上一个由P 三极管组成的放电回路就更好了。hsym_101584:

“这个电路的神奇之处就是采用了D1的电平平移电路,使负电平平移到接近0V!“

这句话该怎么理解呢?

hsym_101584:

比如占空比D=0.9,输入电压Vin=10V,那么此时原边的隔直电容上的直流压降为D*Vin=9V,原边绕组上的压降为1V。当输入电平为低的时候,原边隔直电容9V 加在原边绕组上,感应到副边为下正上负,通过二极管D1给电容C2充电,C2充满后为左负右正,9V。当输入电平变高时,原边绕组电压为1V,上正下负,感应到副边,使副边绕组压降跳变到上正下负,1V。由于电容C2两端电压不能突变,要保持9V 的压差,所以C2右端的电压变为1+9=10V。

图27

当D=0.9的时候,如图28

图28

同样,这个电路在驱动掉电的时候,比如关机,也会出现震荡,如图29。而且似乎这个问题比上面的电路还严重。下面尝试降低这个震荡,首先把R5改为1K,如图

30。

红色波形为驱动源输出,绿

色为到达MOS 的波形。基

本保持了驱动源的波形。

图29图30

确实有改善,但问题还是严重,继续在C2上并一个1K的电阻。如图31:绿色的波形,确实更改善了一些,但是问题还是存在。这是个可靠性的隐患。对于这个问题如何解决呢?可以采用soft stop的方式来关机。soft stop其实就是soft start的反过程,就是在关机的时候,让驱动占空比从大往小变化,直到关机。很多IC 已经集成了该功能。可看到,驱动信号在关机的时候,没有了上面的那些震荡。

图31图32

半桥全桥驱动

对于半桥,全桥的驱动,由于具

有两相驱动,而且相位差为180度,

那么如何用隔离变压器来驱动呢?

如图33:采用一拖二的方式,

可以来驱动两个管子。下

图33

图34是两个驱动源的波形;通过变压器传递之后,到达MOS会变成如图35的波形:

图34图35

在有源钳位,不对称半桥,以及同步整流等场合,需要一对互补的驱动,那么怎么用一路驱动来产生互补驱动,并且形成死区。可用下图36;其波形如图37:

图36图37

MOSFET的并联驱动,由于MOS经常采用并联的方式工作,那么驱动又该如何设计呢?是按图38呢?还是按图39设计呢?

图38图39

图38可用。一般情况下不建议MOS并联使用,因为MOS并联,对驱动的一致性要求就很高了,如果导通,关断时间不一致,会导致其中一个MOS开关损耗剧增。所以在软开关电路上,用MOS并联问题比较少,但是硬开关电路,就要小心了。下面用仿真来看现象,假设两个MOS并联,而且MOS的参数完全一样。但是驱动走线的寄生参数有很大不同。图40中R2,R4,L1,L2都为驱动走线的寄生参数。那么下图41为导通时候,两个mos 的电流,从图中看出两管基本上还算一致。

图40图41

接下去,把两个驱动电阻并联起来一起去驱动两个MOS管,如图42;其导通时候的电流波形如图43:两管子的电流波形,均出现剧烈震荡。

图42图43

showtime2303:

您好,我看到蜘蛛大哥的帖子中提到了可以将一个大FET和一个小FET并联,让大FET先关后开,将大FET的开关过程搞软,降低其开通损耗,不是很明白,想请sometimes大哥分析仿真一下这种情况。sometimes:

两个fet并联,先开的那个mos要承受开通损耗,因为一个开通之后,mos的ds电压降到0,之后另外一个管子开通,就是0电压开通了,后关的那个要承受关断损耗。所以这样做可以让开关损耗全部由小FET来承受,但只这种只不过分散了损耗而已。

showtime2303:这样做对效率的提高没有实质性的帮助吗?

sometimes:这个应该说会对驱动有好处,在驱动大管子的时候,由于没有米勒效应,可以降低驱动损耗,并且对驱动能力要求不高。但是对于主电路的损耗,我觉得没有太大用。

lijieamd:我想问问sometimes大侠关于双NMOS的半桥结构的驱动问题。

问题是这样的:电路如图44,半桥的上下管都是NMOS,上管栅极驱动采用18V电源,下管栅极驱动采用12V电源,当上管驱动是关闭的情况下(也就是上桥臂驱动的PNP管打开,NPN管关闭),下管进行PWM驱动,这个时候上管的栅极也会出现一个比较小幅度的PWM,但是尖峰比较大,大概有4V,这导致很小的一段时间上下管导通,耗散非常大。我猜想可能是通过下管的栅漏电容CGD给耦合到上管的栅源电容上去了,想问问如何解决这个问题,谢谢了!

图44

sometimes:

在GS并个电阻,改善你的驱动走线,可能你的驱动线太长了,降低你的开关速度,也能减低尖峰。

Pmos的驱动:

下图45为Pmos管:Pmos要求GS的电压是负的,也就是G的电压要比S的低,才能导通。那么,如果SD承受高压,G只要比S的电压低一点就能导通,但是一旦SD导通,G必须维持负压才能导通。而GS的耐压是很低的,这就很麻烦了。一般在电源中最常见的Pmos应用,就有有源钳位。

有源钳位的Pmos,是S级接地的,那么要保持导通,G级必须要有负压才行。那么如何产生负压呢,可以采用下图46的驱动方式;其波形如图47所示:

图45图46

图47

sdgcy:

请教一个我很长时间都没有搞明白的问题,就是用自举电路驱动MOS的时候,我发现有好多厂家在处理自举电路PCB的时候,都有这么一个现象,就是自举电容的负极(也就是和上桥MOS的源极相连的极)到上桥MOS的源极之间的连线用蛇形线,不知道这样做的左右是什么?

讨论部分

edifierwjq:

有问题想请教下楼主,最近在调试全桥电路,发现当输入电压加到100V的时候驱动波形就不对了,Vgs会出现一个跌落,如示波器截图所示,输入电压再升高一些就会出现桥臂直通的情况,同一桥臂的两个管子就烧掉了。我是利用光耦A3120来驱动桥臂的四个开关管的。希望得到您的帮助,谢谢了!

sometimes:

你的波形呢?有可能是驱动能力不够

edifierwjq:

不好意思,第一次来咱们论坛,还没搞清楚如何上传图片,等下就上传上去。究竟怎样定义电源的驱动能力呢?A3120的电流驱动能力是2A,电压源用的是实验室那种很笨重的直流源,其电流输出能力为3A,应该够驱动MOSFET了吧?最近我也在学习有关MOSFET的特性及驱动技术,看得有些头大,希望能够得到您的帮助。

这个是我的实验截图,3通道的是Vgs的波形,为什么会出现这么大的跌落呢?请帮忙给分析一下。

sometimes:

你这个跌落有点厉害,能把驱动电路贴出来么?还有你测试的时候,把探头的地线回路弄小点。edifierwjq:

就是这样直接拿高速光耦3120进行驱动的,感觉好像简陋了些,呵呵。直接把光耦副边的地接到高端MOSFET 的S端。当全桥输入比较低的时候驱动是正常的,当输入电压升高,功率加大后就会出现上面所述的问题。sometimes:

你首先要检测一下C5的电压,看有没有跌落,其次,可以适当减少R7的阻值,察看R7输入电压的上升斜率是否足够快。还有你的mos是什么型号的?

edifierwjq:

MOSFET用的是英飞凌的47N60C3coolmos。15V供电我是拿实验室的那种很笨重的辅助电源提供的,它面板上有电压提示,我发现随着主电路功率的提高,辅助电源面板上显示的读数就降下来了,而且在不停地波动,难道是辅助电源功率不够?这电源能够提供3A的输出电流,貌似应该足够了呀。HCPL3120能够提供2A的驱动电流。我增大门极驱动电阻会不会好些呢?增大这个电阻会抑制Vgs的震荡,但同时会增加导通时间,增大开通损耗。

sometimes:

从功率的角度来说,3A绝对够了。0.3A都够了。但是要看你这个电源的动态好不好,所以你还是要用示波器去测试电容上的电压波形。2A的驱动电流稍显不够,但理论上,不会出现这么大的跌落;当然还要看你的电源线长不长。

edifierwjq:

恩,经您这么一说我发现电源线确实拉得挺长,这样的话就引入了不少的电感,这是不是就是所谓的震铃现象啊?加大门极驱动电阻是不是会好些呢?

sometimes:

如果你的供电出了问题,加大电阻是没有用的。

showtime2303:

sometimes大哥,您能把Vds与Ids与Vgs的仿真曲线放在一张图中吗?我想知道vds和ids是不是同时变化的,为什么书上讲的大部分情况下,ids升到最高时,vds才开始变化。这样对效率会不会影响很大?怎么改善?sometimes:

假如电路是理想的,的确会如书上所讲。只有在整流管电流下降到0,开关管上的电压才开始下降。但是实际上,由于漏感,线路寄身电感等参数的影响。有所不同。