一.冯·诺依曼计算机的特点

1945年,数学家冯诺依曼研究EDVAC 机时提出了“存储程序”的概念1.计算机由运算器、存储器、控制器、输入设备和输出设备五大部件组成2.指令和数据以同等地位存放于存储器内,并可按地址寻访。3.指令和数据均用二进制数表示。

4.指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置。

5.指令在存储器内按顺序存放。通常,指令是顺序执行的,在特定条件下,可根据运算结果或根据设定的条件改变执行顺序。

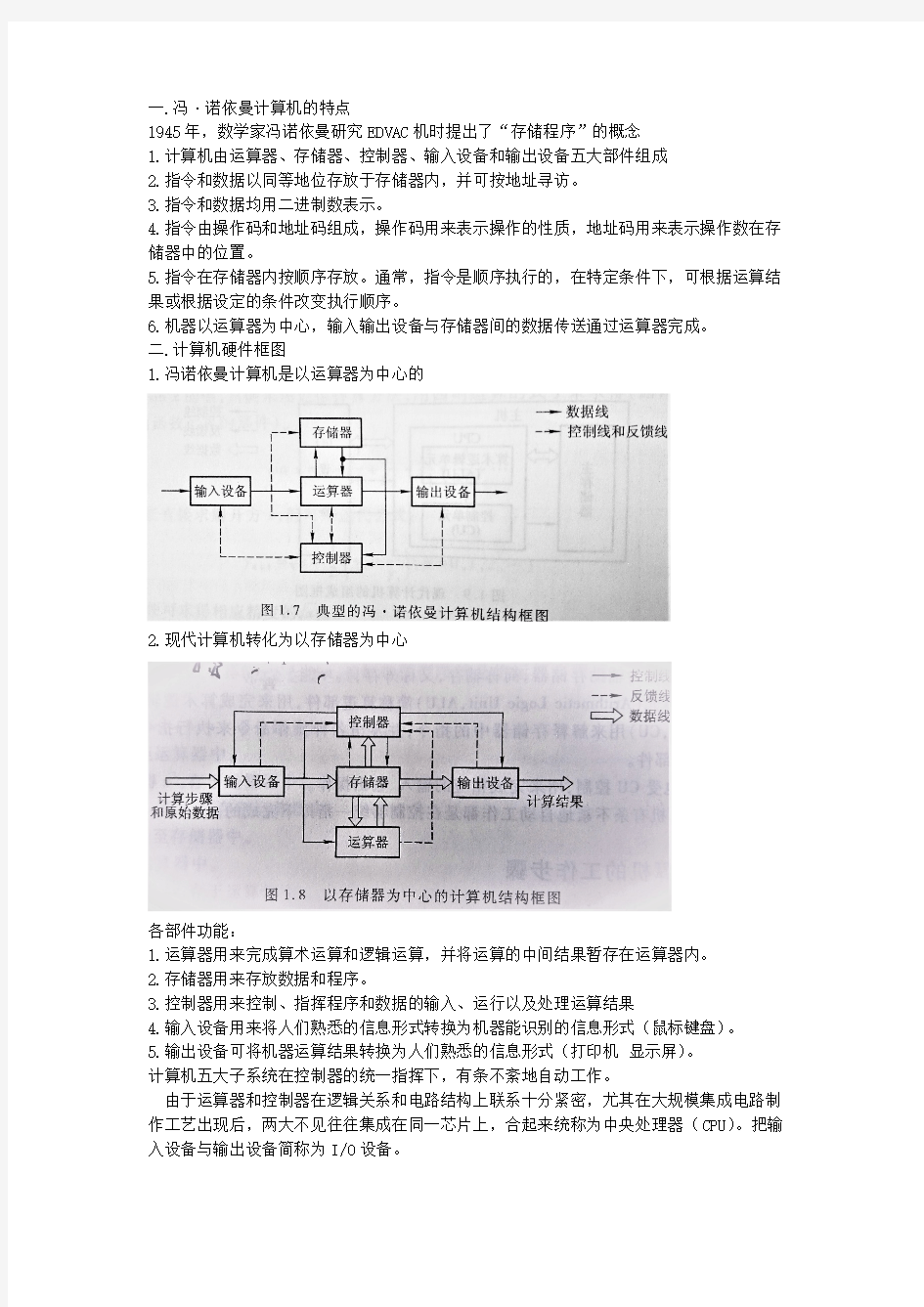

6.机器以运算器为中心,输入输出设备与存储器间的数据传送通过运算器完成。二.计算机硬件框图

1.

冯诺依曼计算机是以运算器为中心的

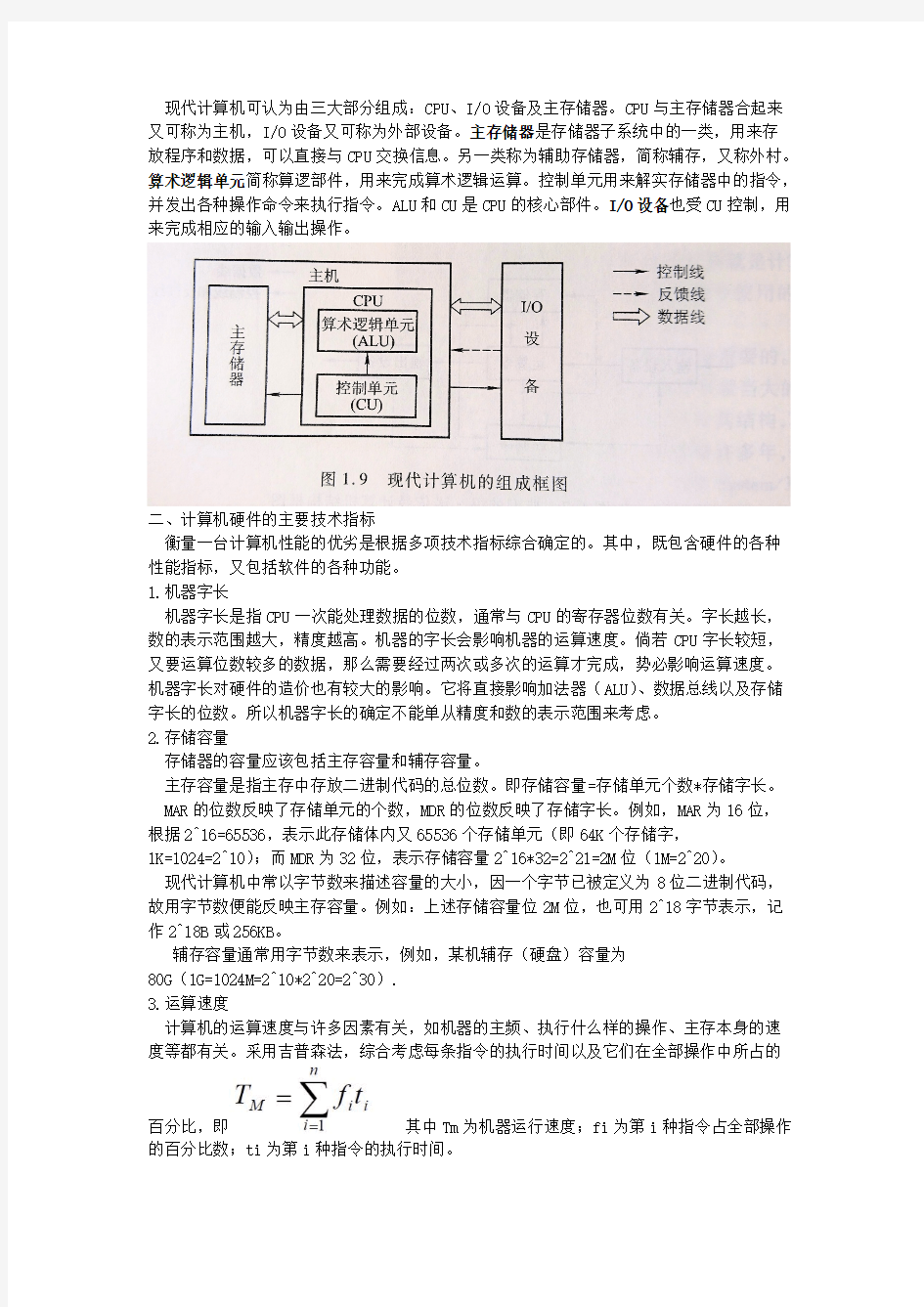

2.

现代计算机转化为以存储器为中心

各部件功能:

1.运算器用来完成算术运算和逻辑运算,并将运算的中间结果暂存在运算器内。

2.存储器用来存放数据和程序。

3.控制器用来控制、指挥程序和数据的输入、运行以及处理运算结果

4.输入设备用来将人们熟悉的信息形式转换为机器能识别的信息形式(鼠标键盘)。

5.输出设备可将机器运算结果转换为人们熟悉的信息形式(打印机 显示屏)。计算机五大子系统在控制器的统一指挥下,有条不紊地自动工作。

由于运算器和控制器在逻辑关系和电路结构上联系十分紧密,尤其在大规模集成电路制作工艺出现后,两大不见往往集成在同一芯片上,合起来统称为中央处理器(CPU )。把输入设备与输出设备简称为I/O 设备。

现代计算机可认为由三大部分组成:CPU 、I/O 设备及主存储器。CPU 与主存储器合起来又可称为主机,I/O 设备又可称为外部设备。主存储器是存储器子系统中的一类,用来存放程序和数据,可以直接与CPU 交换信息。另一类称为辅助存储器,简称辅存,又称外村。算术逻辑单元简称算逻部件,用来完成算术逻辑运算。控制单元用来解实存储器中的指令,并发出各种操作命令来执行指令。ALU 和CU 是CPU 的核心部件。I/O 设备也受CU 控制,用

来完成相应的输入输出操作。

二、计算机硬件的主要技术指标

衡量一台计算机性能的优劣是根据多项技术指标综合确定的。其中,既包含硬件的各种性能指标,又包括软件的各种功能。1.机器字长

机器字长是指CPU 一次能处理数据的位数,通常与CPU 的寄存器位数有关。字长越长,数的表示范围越大,精度越高。机器的字长会影响机器的运算速度。倘若CPU 字长较短,又要运算位数较多的数据,那么需要经过两次或多次的运算才完成,势必影响运算速度。机器字长对硬件的造价也有较大的影响。它将直接影响加法器(ALU )、数据总线以及存储字长的位数。所以机器字长的确定不能单从精度和数的表示范围来考虑。2.存储容量

存储器的容量应该包括主存容量和辅存容量。

主存容量是指主存中存放二进制代码的总位数。即存储容量=存储单元个数*存储字长。MAR 的位数反映了存储单元的个数,MDR 的位数反映了存储字长。例如,MAR 为16位,根据2^16=65536,表示此存储体内又65536个存储单元(即64K 个存储字,1K=1024=2^10);而MDR 为32位,表示存储容量2^16*32=2^21=2M 位(1M=2^20)。

现代计算机中常以字节数来描述容量的大小,因一个字节已被定义为8位二进制代码,故用字节数便能反映主存容量。例如:上述存储容量位2M 位,也可用2^18字节表示,记作2^18B 或256KB 。

辅存容量通常用字节数来表示,例如,某机辅存(硬盘)容量为80G (1G=1024M=2^10*2^20=2^30).3.运算速度

计算机的运算速度与许多因素有关,如机器的主频、执行什么样的操作、主存本身的速度等都有关。采用吉普森法,综合考虑每条指令的执行时间以及它们在全部操作中所占的

百分比,即 其中Tm 为机器运行速度;fi 为第i 种指令占全部操作的百分比数;ti 为第i 种指令的执行时间。

现在机器的运算速度普遍采用单位时间内执行指令的平均条数来衡量,并用MIPS (百万条指令每秒)作为计量单位。也可以用CPI 即执行一条指令所需的时钟周期(机器主频的倒数)。或用FLOPS (浮点运算次数每秒)来衡量运算速度。

三、第一章习题

四、总线的基本概念

1.计算机系统的五大部件之间的互连方式有两种,一种是各部件之间使用单独的连线,称为分散连接;另一种是将各部件连到一组公共信息传输线上,称为总线连接。

2.2.总线定义

总线是连接多个部件的信息传输线,是各部件共享的传输介质。当多个部件与总线相连时,如果出现两个或两个以上部件同时向总线发送信息,势必导致信号冲突,传输无效。因此在某一时刻,只允许有一个部件向总线发送信息,而多个部件可以同时从总线上接收相同的信息。

总线实际上是由许多传输线或通路组成,每条线可一位一位地传输二进制代码,一串二进制代码可在一段时间内逐一传输完成。若干条传输线可以同时传输若干位二进制代码,例如,16条传输线组成的总线可同时传输16位二进制代码。

3.采用总线连接的计算机,以CPU 为中心的双总线结构。其中一组总线连接CPU 和主存,称为存储总线(M 总线);另一组用来建立CPU 和各I/O 设备之间交换信息的通道,称为输入/输出总线(I/O 总线)。各种I/O 设备通过I/O 接口挂到I/O 总线上,便于增删设备。I/O 设备与主存交换信息时占用CPU ,影响CPU 工作效率。

4.CPU 、主存和I/O 设备(通过I/O 接口)都挂到一组总线上,便形成单总线结构的计算机。与主存交换信息时,CPU 仍可继续处理不访问主存或I/O 设备的操作,使工作效率提高。但因为只有一组总线,各部件都要占用总线时,会发生冲突。必须设置总线判优逻辑,按优先级占用总线,影响工作速度。

5.以存储器为中心的双总线结构。在单总线基础上又开辟一条CPU 与主存之间的总线,称为存储主线。这组总线速度高,只供主存与CPU 之间传输信息。提高传输效率,减轻系统总线的负担,保留了I/O 设备与存储器交换信息不经过CPU 的特点。

五、总线的分类

按数据传送方式可分为并行传输总线和串行传输总线,在并行传输总线中,又可按传输数据宽度分为8位、16位、32位、64位等传输总线。若按总线的使用范围划分,则又有计算机总线、测控总线、网络通信总线等。

下面按连接部件不同,介绍三类总线。

1.片内总线指芯片内部的总线,如在CPU芯片内部,寄存器与寄存器之间、寄存器与算逻单元ALU之间都由片内总线连接。

2.系统总线指CPU、主存、I/O设备各大部件之间的信息传输线。由于这些部件通常安放在主板或各个插件板上,故又称板级总线或板间总线。按系统总线传输信息不同,又分为数据总线(传输各部件数据信息)、地址总线(源数据或目的数据在主存的地址)和控制总线(发出控制信号)。

3.通信总线用于计算机系统之间或计算机系统与其他系统之间的通信。由于这类联系涉及多方面,如外部链接、距离远近、速度快慢、工作方式等,按传输方式分为串行通信和并行通信。

五、总线控制(重点)

P57页开始及P61 例3.1 ,P62 63 例3.2 例3.3

六、存储器分类P69

1.按存储介质分类:半导体存储器、磁表面存储器、磁芯存储器、光盘存储器

2.按存取方式分类:随机存储器、只读存储器、串行访问存储器(分为顺序存取存储器、直接存取存储器)

3.按计算机中作用分类:主存储器、辅助存储器、缓冲存储器(特点P70)

七、存储器相关内容都要浏览P68-72

八、主存储器 P72 4.2.1

九、动态RAM的刷新P86

刷新的过程实质上时先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程。分为三种刷新方式:集中刷新、分散刷新和异步刷新。

十、动态RAM与静态RAM的比较 P87

动态RAM的应用比静态RAM要广泛的多。

动态RAM的优点:

1.同样大小的芯片中,动态RAM的集成度远高于静态RAM,如动态RAM的基本单元电路为一个MOS管,静态RAM的基本单元电路可为4~6个MOS管。

2.动态RAM行、列地址按先后顺序输送,减少了芯片引脚,封装尺寸也减少。

3.动态RAM的功耗比静态RAM小

4.动态RAM的价格比静态RAM的价格便宜。动态RAM容量是静态RAM容量的4~8倍,静态RAM的存取周期比动态RAM的快8~16倍,但价格也贵8~16倍。

动态RAM的企缺点:

1.由于使用动态元件(电容),因此它的速度比静态RAM低。

2.动态RAM需要再生,故需配置再生电路,也需要耗一部分功率。容量不大的高速缓冲存储器大多用静态RAM实现。

十一、存储器与CPU的连接 P91 (大题)

所有内容需要理解

另:P94 例4.1 例4.2

十二、高速缓冲存储器 P109 4.3全部

十三、输入输出系统 P156 5.1概述

十四、I/0接口 P187 全部

P190 5.4程序查询方式(重点)

十五、程序中断方式(重点) P194 本章要多看例题本章出大题

十六、计算机运算方法 P219

大题:原码-倍乘/分除/浮点数加减法(P258 P261 P269)P274之后不用看

★补码

本章布置过的作业:P289 6.1 6.4 6.5 6.9

十七、指令系统

7.1-7.4 P300-P319

其中 P318 例7.1 7.2 7.3 ★

十八、中断系统(P358 8.4)

P369 例8.2

十九、控制单元的功能与设计(P375 ----)

执行阶段操作

取指阶段操作