半导体芯片封装之贴片键合概述

作者:聂仁勇海太半导体(无锡)有限公司

引言

半导体芯片封装是指利用精密焊接技术,将芯片粘贴并固定在框架或PBC板等基座上,并通过金丝、铜丝、铝丝或其他介质将芯片的键合区与基座连接起来,再用绝缘材料将它们保护起来,构成独立的电子元器件的工艺。

半导体芯片封装的目的,在于保护芯片不受或少受外界环境的影响,并为它提供一个发挥半导体芯片功能的良好工作环境,以使之稳定、可靠、正常地完成相应的功能。但是芯片的封装只会限制而不会提高芯片的功能。在这样的情况下,全世界都在努力研究并并不断推出新的封装形式,以最大限度地发挥半导体芯片尤其是半导体集成电路本应有的功能,减小因封装对芯片功能产生的影响。半导体芯片封装流程可以分为“前道”流程和“后道”流程两部分。其中,“前道”流程包括贴片(Die Bonding)和键合(Wire Bonding)两道工序,是整个半导体芯片封装流程中至关重要的两道工序,它们决定了整个封装流程的成败;“后道”流程则包括塑封、后固化、高温贮存、去飞边、浸锡(电镀)、切筋(打弯)、测试分类、mark、包装等工序,“后道”流程中测试分类也是比较重要的一道工序,它决定了产品的“去留”。本文将着重介绍贴片和键合这两道工序。

贴片(Die Bonding)

贴片(Die Bonding),是将半导体芯片固定于基板或引线框架的Pad上的工艺工程。装片需要选择与芯片相匹配的基座或Pad的引线框架,因为若基座或Pad太大,则会使内引线宽度太大,在“后道”塑封过程中会由于塑封体流动产生的应力而造成内引线断裂、塌丝等现象,从而导致TEST 不良品增多。

另外,为了形成良好的装片成品率,还需要完善的工艺要素与之相配合,主要包括:温度、时间、气氛、压力等几种因素。

因此装片工序有两大质量要求:产品质量要求和工艺质量要求。

装片的产品质量要求:芯片与引线框架的连接机械强度高,导热性能好(△VBE小)和导电性能好(V CEsat 小),装配平整,焊料厚度适中,定位准确,能满足键合的需要,能承受键合或塑封时可能有的高温,保证器件在各种条件下使用都具有良好的可靠性。

装片的工艺质量要求:芯片位置正确;芯片无沾污、无碎裂、无划伤、无倒装、无误装、无扭转;引线框架无污染、无气泡、无氧化、无变形;焊料熔融良好,无氧化、无漏装、无结球、无翘片、无空洞。

良好的成品率不但要有合适的工艺条件,而且要有理想的合金材料,理想的材料应有以下特点:

1、在半导体晶片中的溶解度高,这样制成的欧姆接触电阻就小;

2、具有较低的蒸气压,即在合金温度下不应大量蒸发;

3、熔点应低于芯片表面的铝与半导体的合金温度,否则会影响器件的电参数;

4、机械性能良好,要有延展性而且热膨胀性能与半导体材料、衬底材料的热膨胀性能相接近或相匹配;

但装片的方式又多种多样,目前比较主流的方式主要有以下4种,分别是:树脂粘接(分导电或非导电树脂)、共晶焊接、银浆或银泥烧结和铅锡合金焊接。

1)树脂粘接(分导电或非导电树脂)

常用的树脂由环氧、聚酰亚胺、酚醛、聚胺树脂及有机硅树脂组成作为粘接剂,加入银粉的称导电树脂(或导电胶);有的加入氧化铝粉填充料,导热性好,绝缘性也好,称非导电树脂(或非导电胶),适用于集成电路与小功率的晶体管。

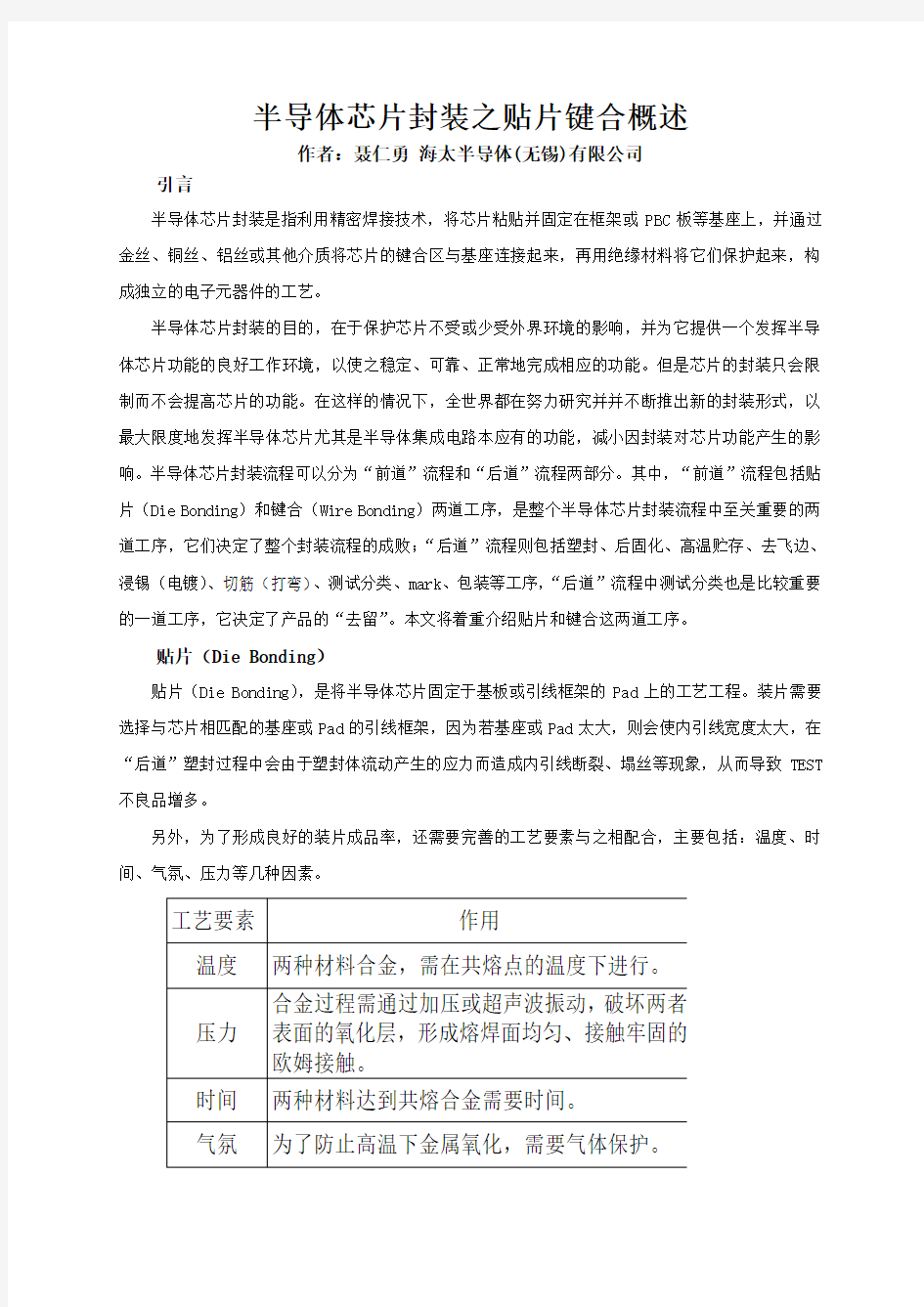

树脂粘接会产生一系列的问题:生产过程中因芯片放置不当(如翘片等)形成空洞率(如图1所示)过高(后面章节即将介绍到的合金焊料装片更容出现这样的情况);空洞率过高直接导致热阻偏大、高应力;树脂滴在引脚上造成搭桥现象,引起内连接问题,在内引线键合时造成框架翘曲,使得一边内引线应力大,一边内引线应力小。

图1-a 装片空洞率不合格样品图1-b 装片空洞率较小合格样品

(空洞大、集中)(空洞小、分散且少)树脂粘接装片后需要进行固化处理,环氧树脂粘贴剂的固化条件一般是150℃,固化时间为半

小时(此数据为KEC-W TO-220IS-4的参数);聚酰亚胺粘贴剂的固化温度要高一些,时间也更长;不同粘贴剂的固化工艺条件都不尽相同,需要相关的实验来确定。

2)共晶焊接

共晶焊接是利用芯片背面的金硅合金和基座或引线框架上镀的金属(银层)在高温氮保护和400~440℃高温下形成合金的办法固定芯片,这种方法需要有相应的背面蒸金的芯片才能进行焊接,导电导热性能都很好,适用于较小尺寸的芯片。特别适用于功率三极管芯片,这样的装片方式比合金焊料装片方式更有助于工作中芯片的散热。

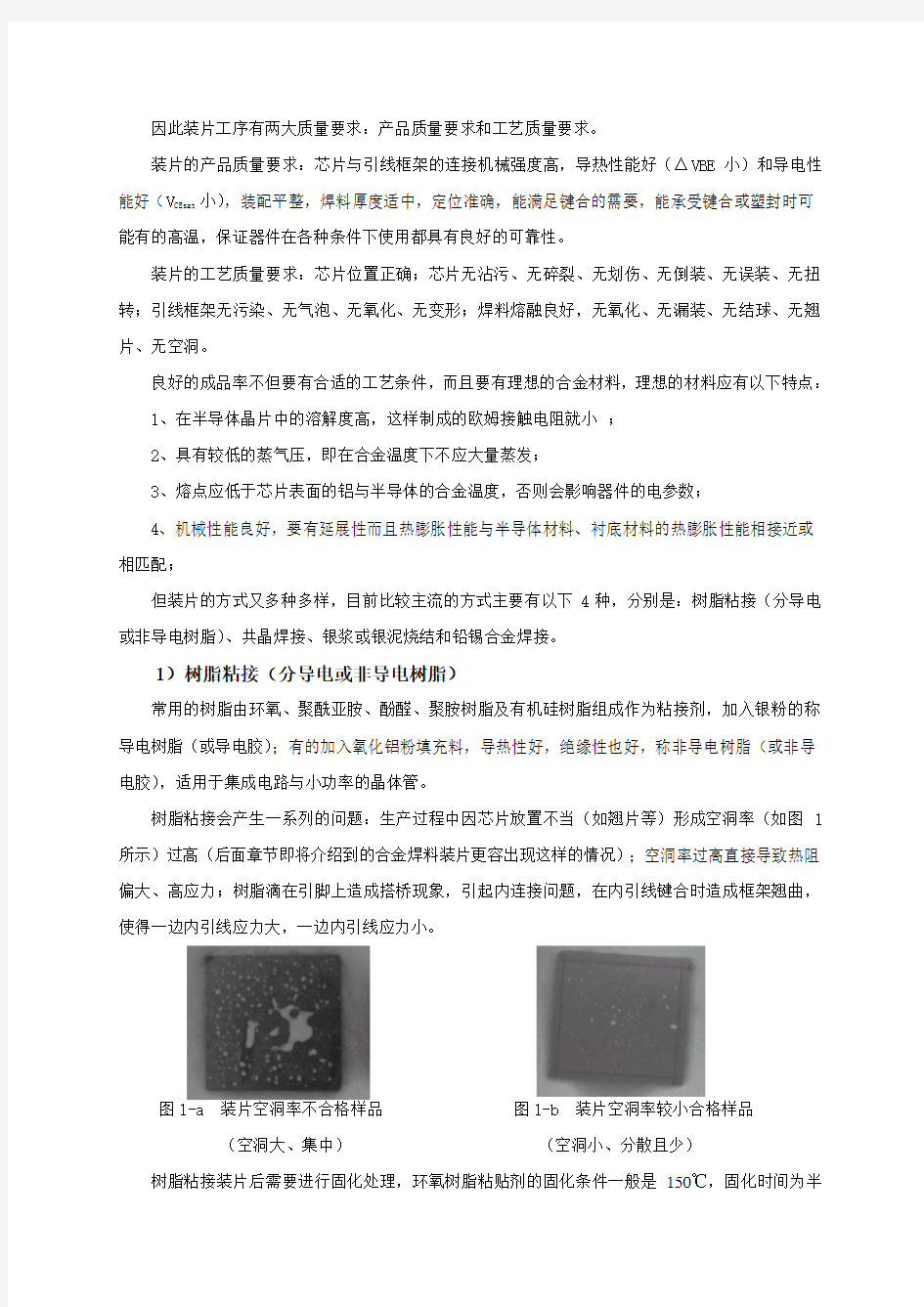

芯片背面不同的合金材料在装片过程中芯片周围将出现不同的溢料现象,五层背金、六层背金芯片的周围没有合金溢出痕迹,而AuGe背金芯片的周围则有明显的合金溢出痕迹。(图2)

图a 五层背金、六层背金图b AuGe背金

图2 不同合金背金现象

共晶焊接装片工艺也存在一定的缺陷,因为共晶装片是要靠机械手向下的压力才能有好的共晶出现的,如果装片的机械手上吸嘴的截面与芯片不平行,则会导致芯片的受力不均,从而出现芯片一边已与银形成合金粘牢,另一边未粘牢的现象。

3)银浆或银泥烧结

银浆或银泥烧结是利用银浆或银泥中的氧化银,高温下分解还原成银来固定芯片,导电和导热性能均较好。适用于小功率晶体管和结深较浅的超高频或微波小功率晶体管。

银浆或银泥烧结方式装片也需采用氮气保护,烧结温度为380~400℃,这种方法最大的特点是成本低、效率高,但高低温热性能、电耐久性、工艺重复性差。

4)铅锡合金焊接

铅锡合金焊接是利用铅锡合金作焊料,把背面已蒸金(银)或镀镍的芯片,焊接在镀银或镀镍的基座或引线框架上,这种装片方式的导电导热性比共晶都要稍差些,但成本更低,适用于中大功率晶体三极管及集成电路。

现在,随着欧盟等一些地区或国家相继加大了对环保的投入,大力发展无铅绿色环保产品。为

了顺应历史发展趋势,科学家们研制出了新型的合金焊料,即在原有的铅锡合金的基础上,用一定比例的“锑+银”或“锑+镍+磷”来替代铅。而且后两者比前者有着巨大的优势:首先,是达到了绿色环保的目的。

其次,后两者形成的合金熔点比前者要低100℃左右,节约了大量的电力能源,符合目前国家正在大力倡导的节能减排要求。

第三,后两者可以直接与裸铜在氢氮混合保护气体下焊接,这样就无需再在铜材上镀银或镍,简化了基座或引线框的生产工序,节约了大量资源,减少了成本,也减轻了对环境的污染。

第四,后两者在高温、保护气氛下的流动性、浸润性比前者要好,有助于装片空洞率的降低,提高产品的成品率。(图3显示了装片后两种焊料的不同状态)

图a 理想的装配图b 非理想的装配

图3 两种焊料的不同状态

键合(Wire Bonding)

键合就是用金丝、铜丝或铝丝将半导体器件芯片表面的电极引线与底座或引线框架外引线相连接起来。键合的目的是把半导体器件芯片表面的电极与引线框架的外引线连接起来(如图4)。

图4 键合的实例照片

与装片相对应的是,键合也有其相应的工艺要素,分别是超声功率、压力、时间、温度(相对于金、铜丝键合而言)。它们各自的作用见表2.

表2 键合工艺要素及其作用

因此键合工序也有两大质量要求:产品质量要求和工艺质量要求。

键合的产品质量要求:内引线与芯片和外引线要形成低电阻欧姆接触,压点的位置准确,结合力要强;内引线要有足够的电流容量,抗拉强度要强,有理想的压点和弧度。

键合的工艺质量要求:配线正确(线径、根数、极性)、无漏键、无错键;压点位置正确、形状理想,无键偏、无根切、无虚焊;弧度合理,无塌丝、无拉丝、无尾丝;测克强度符合要求。

良好的成品率不但要有合适的工艺条件,而且要有理想的引线材料,理想的材料应有下特点:

1、能与半导体材料形成低电阻的欧姆接触;

2、化学性能稳定,不会形成有害的化合物;

3、与半导体材料之间的结合力强;

4、电阻率低,具有良好的导电性能;

5、可塑性好,容易焊接;

6、在键合过程中能保持一定的几何形状。

通过以上分析,理想的引线材料有:

1、纯铝丝

2、硅铝丝

3、金丝

目前,主要的键合技术有:热压键合(Thermocompression Bonding T/C Bonding)(T:330~350 ℃)、热超声波键合(Thermosonic Bonding, T/S Bonding)(T:250℃左右)和超声波键合(Ultrasonic Bonding, U/S Bonding)(T:常温)三种。

1) 热压键合

热压焊接的原理:首先,由于金属丝和芯片上的铝层同时受热受压,接触面便产生塑性形变并破坏了界面的氧化膜,使两者接触面几乎接近原子引力范围,金属丝表面原子与铝层表面原子之间产生吸引力而达到键合的目的。其次,是由于金属丝和铝层表面的不平整,加压后高低不平处相互填充而产生弹性嵌合作用,使两者紧密结合在一起。因此加压后接触面积越大,结合牢固度也越好。

热压焊和电阻焊、锡焊、铜焊的区别:

1、半导体材料有哪些特征? 答:半导体在其电的传导性方面,其电导率低于导体,而高于绝缘体。 (1)在室温下,它的电导率在103~10-9S/cm之间,S为西门子,电导单位,S=1/ρ(Ω. cm) ;一般金属为107~104S/cm,而绝缘体则<10-10,最低可达10-17。同时,同一种半导体材料,因其掺入的杂质量不同,可使其电导率在几个到十几个数量级的范围内变化,也可因光照和射线辐照明显地改变其电导率;而金属的导电性受杂质的影响,一般只在百分之几十的范围内变化,不受光照的影响。 (2)当其纯度较高时,其电导率的温度系数为正值,即随着温度升高,它的电导率增大;而金属导体则相反,其电导率的温度系数为负值。 (3)有两种载流子参加导电。一种是为大家所熟悉的电子,另一种则是带正电的载流子,称为空穴。而且同一种半导体材料,既可以形成以电子为主的导电,也可以形成以空穴为主的导电。在金属中是仅靠电子导电,而在电解质中,则靠正离子和负离子同时导电。 2、简述半导体材料的分类。 答:对半导体材料可从不同的角度进行分类例如: 根据其性能可分为高温半导体、磁性半导体、热电半导体; 根据其晶体结构可分为金刚石型、闪锌矿型、纤锌矿型、黄铜矿型半导体; 根据其结晶程度可分为晶体半导体、非晶半导体、微晶半导体, 但比较通用且覆盖面较全的则是按其化学组成的分类,依此可分为:元素半导体、化合物半导体和固溶半导体三大类。 3、化合物半导体和固溶体半导体有哪些区别。 答:由两个或两个以上的元素构成的具有足够的含量的固体溶液,如果具有半导体性质,就称为固溶半导体,简称固溶体或混晶。固溶半导体又区别于化合物半导体,因后者是靠其价键按一定化学配比所构成的。固溶体则在其固溶度范围内,其组成元素的含量可连续变化,其半导体及有关性质也随之变化。 4、简述半导体材料的电导率与载流子浓度和迁移率的关系。 答:s = nem 其中: n为载流子浓度,单位为个/cm3; e 为电子的电荷,单位为C(库仑),e对所有材料都是一样,e=1.6×10-19C 。 m为载流子的迁移率,它是在单位电场强度下载流子的运动速度,单位为cm2/V.s; 电导率s的单位为S/cm(S为西门子)。 5、简述霍尔效应。 答:将一块矩形样品在一个方向通过电流,在与电流的垂直方向加上磁场(H),那么在样品的第三个方向就可以出现电动势,称霍尔电动势,此效应称霍尔效应。 6、用能带理论阐述导体、半导体和绝缘体的机理。 答:按固体能带理论,物质的核外电子有不同的能量。根据核外电子能级的不同,把它们的能级划分为三种能带:导带、禁带和价带(满带)。 在禁带里,是不允许有电子存在的。禁带把导带和价带分开,对于导体,它的大量电子处于导带,能自由移动。在电场作用下,成为载流子。因此,导体载流子的浓度很大。 对绝缘体和半导体,它的电子大多数都处于价带,不能自由移动。但在热、光等外界因素的作用下,可以使少量价带中的电子越过禁带,跃迁到导带上去成为载流子。 绝缘体和半导体的区别主要是禁的宽度不同。半导体的禁带很窄,(一般低于3eV),绝缘体的禁带宽一些,电子的跃迁困难得多。因此,绝缘体的载流子的浓度很小。导电性能很弱。实际绝缘体里,导带里的电子不是没有,并且总有一些电子会从价带跃迁到导带,但数量极少。所以,在一般情况下,可以忽略在外场作用下它们移动所形成的电流。但是,如果外场很强,束缚电荷挣脱束缚而成为自由电荷,则绝缘体就会被“击穿”而成为导体。 7、什么是本征半导体和杂质半导体? 答:当半导体主要是靠热激发产生载流子时,导电称为本征导电,这种半导体称为本征半导体,其特点是自由电子数等于空穴数。另一种导电机制是靠电活性杂质形成的载流子导电,这种导电称为杂质导电,这种半导体称为杂质

集成电路芯片封装技术(书) 第1章 1、封装定义:(狭义)利用膜技术及细微加工技术,将芯片及其他要素在框架或基板上布置、 粘帖固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构 成整体立体结构的工艺 (广义)将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程 2、集成电路的工艺流程:芯片设计(上)芯片制造(中)封装测试(占50%)(下)(填空) 3、芯片封装实现的功能:传递电能传递电路信号提供散热途径结构保护与支持 4、封装工程的技术层次(论述题):P4图 晶圆Wafer -> 第零层次Die/Chip -> 第一层次Module -> 第二层次Card ->第三层次Board -> 第四层次Gate 第一层次该层次又称芯片层次的封装,是指把集成电路芯片与封装基板或引脚架之间的粘贴固定、电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层组装进行链接的模块 第二层次将数个第一层次完成的封装与其他电子元器件组成一个电路卡的工艺 第三层次将数个第二层次完成的封装组装成的电路卡组合成在一个主电路板上使之成为一个部件或子系统的工艺 第四层次将数个子系统组装成为一个完整电子产品的工艺过程 5、封装的分类与特点: 按照封装中组合集成电路芯片的数目——单芯片封装(SCP)多芯片封装(MCP) 按照密封材料——高分子材料封装陶瓷材料封装 按照器件与电路板互连方式——引脚插入型(PTH)表面贴装型(SMT) 6、DCA(名词解释):芯片直接粘贴,即舍弃有引脚架的第一层次封装,直接将IC芯片粘贴到基板上再进行电路互连 7、TSV硅通孔互连封装 HIC混合集成电路封装 DIP双列直插式引线封装

A、常用芯片封装介绍 来源:互联网作者: 关键字:芯片封装 1、BGA 封装(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。引脚可超过200,是多引脚 LSI 用的一种封装。封装本体也可做得比 QFP(四侧引脚扁平封装)小。例如,引脚中心距为 1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚 QFP 为 40mm 见方。而且 BGA 不用担心 QFP 那样的引脚变形问题。该封装是美国 Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。现在也有一些 LSI 厂家正在开发500 引脚的 BGA。 BGA 的问题是回流焊后的外观检查。 现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国 Motorola 公司把用模压树脂密封的封装称为 OMPAC,而把灌封方法密封的封装称为 GPAC(见 OMPAC 和 GPAC)。 2、BQFP 封装(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和 ASIC 等电路中采用此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见 QFP)。

半导体材料复习题 1、半导体材料有哪些特征? 答:半导体在其电的传导性方面,其电导率低于导体,而高于绝缘体。 (1)在室温下,它的电导率在103~10-9S/cm之间,S为西门子,电导单位,S=1/ρ(Ω. cm) ;一般金属为107~104S/cm,而绝缘体则<10-10,最低可达10-17。同时,同一种半导体材料,因其掺入的杂质量不同,可使其电导率在几个到十几个数量级的范围内变化,也可因光照和射线辐照明显地改变其电导率;而金属的导电性受杂质的影响,一般只在百分之几十的范围内变化,不受光照的影响。 (2)当其纯度较高时,其电导率的温度系数为正值,即随着温度升高,它的电导率增大;而金属导体则相反,其电导率的温度系数为负值。 (3)有两种载流子参加导电。一种是为大家所熟悉的电子,另一种则是带正电的载流子,称为空穴。而且同一种半导体材料,既可以形成以电子为主的导电,也可以形成以空穴为主的导电。在金属中是仅靠电子导电,而在电解质中,则靠正离子和负离子同时导电。 2、简述半导体材料的分类。 答:对半导体材料可从不同的角度进行分类例如: 根据其性能可分为高温半导体、磁性半导体、热电半导体; 根据其晶体结构可分为金刚石型、闪锌矿型、纤锌矿型、黄铜矿型半导体; 根据其结晶程度可分为晶体半导体、非晶半导体、微晶半导体, 但比较通用且覆盖面较全的则是按其化学组成的分类,依此可分为:元素半导体、化合物半导体和固溶半导体三大类。 3、化合物半导体和固溶体半导体有哪些区别。 答:由两个或两个以上的元素构成的具有足够的含量的固体溶液,如果具有半导体性质,就称为固溶半导体,简称固溶体或混晶。固溶半导体又区别于化合物半导体,因后者是靠其价键按一定化学配比所构成的。固溶体则在其固溶度范围内,其组成元素的含量可连续变化,其半导体及有关性质也随之变化。 4、简述半导体材料的电导率与载流子浓度和迁移率的关系。 答:s = nem 其中: n为载流子浓度,单位为个/cm3; e 为电子的电荷,单位为C(库仑),e对所有材料都是一样,e=1.6×10-19C 。 m为载流子的迁移率,它是在单位电场强度下载流子的运动速度,单位为cm2/V.s; 电导率s的单位为S/cm(S为西门子)。 5、简述霍尔效应。 答:将一块矩形样品在一个方向通过电流,在与电流的垂直方向加上磁场(H),那么在样品的第三个方向就可以出现电动势,称霍尔电动势,此效应称霍尔效应。 6、用能带理论阐述导体、半导体和绝缘体的机理。 答:按固体能带理论,物质的核外电子有不同的能量。根据核外电子能级的不同,把它们的能级划分为三种能带:导带、禁带和价带(满带)。 在禁带里,是不允许有电子存在的。禁带把导带和价带分开,对于导体,它的大量电子处于导带,能自由移动。在电场作用下,成为载流子。因此,导体载流子的浓度很大。 对绝缘体和半导体,它的电子大多数都处于价带,不能自由移动。但在热、光等外界因素的作用下,可以使少量价带中的电子越过禁带,跃迁到导带上去成为载流子。 绝缘体和半导体的区别主要是禁的宽度不同。半导体的禁带很窄,(一般低于3eV),绝缘体的禁带宽一些,电子的跃迁困难得多。因此,绝缘体的载流子的浓度很小。导电性能很弱。实际绝缘体里,导带里的电子

半导体材料课程教学大纲 一、课程说明 (一)课程名称:半导体材料 所属专业:微电子科学与工程 课程性质:专业限选 学分: 3 (二)课程简介:本课程重点介绍第一代和第二代半导体材料硅、锗、砷化镓等的制备基本原理、制备工艺和材料特性,介绍第三代半导体材料氮化镓、碳化硅及其他半导体材料的性质及制备方法。 目标与任务:使学生掌握主要半导体材料的性质以及制备方法,了解半导体材料最新发展情况、为将来从事半导体材料科学、半导体器件制备等打下基础。 (三)先修课程要求:《固体物理学》、《半导体物理学》、《热力学统计物理》; 本课程中介绍半导体材料性质方面需要《固体物理学》、《半导体物理学》中晶体结构、能带理论等章节作为基础。同时介绍材料生长方面知识时需要《热力学统计物理》中关于自由能等方面的知识。 (四)教材:杨树人《半导体材料》 主要参考书:褚君浩、张玉龙《半导体材料技术》 陆大成《金属有机化合物气相外延基础及应用》 二、课程内容与安排 第一章半导体材料概述 第一节半导体材料发展历程 第二节半导体材料分类 第三节半导体材料制备方法综述 第二章硅和锗的制备 第一节硅和锗的物理化学性质 第二节高纯硅的制备 第三节锗的富集与提纯

第三章区熔提纯 第一节分凝现象与分凝系数 第二节区熔原理 第三节锗的区熔提纯 第四章晶体生长 第一节晶体生长理论基础 第二节熔体的晶体生长 第三节硅、锗单晶生长 第五章硅、锗晶体中的杂质和缺陷 第一节硅、锗晶体中杂质的性质 第二节硅、锗晶体的掺杂 第三节硅、锗单晶的位错 第四节硅单晶中的微缺陷 第六章硅外延生长 第一节硅的气相外延生长 第二节硅外延生长的缺陷及电阻率控制 第三节硅的异质外延 第七章化合物半导体的外延生长 第一节气相外延生长(VPE) 第二节金属有机物化学气相外延生长(MOCVD) 第三节分子束外延生长(MBE) 第四节其他外延生长技术 第八章化合物半导体材料(一):第二代半导体材料 第一节 GaAs、InP等III-V族化合物半导体材料的特性第二节 GaAs单晶的制备及应用 第三节 GaAs单晶中杂质控制及掺杂 第四节 InP、GaP等的制备及应用 第九章化合物半导体材料(二):第三代半导体材料 第一节氮化物半导体材料特性及应用 第二节氮化物半导体材料的外延生长 第三节碳化硅材料的特性及应用 第十章其他半导体材料

半导体芯片封装之贴片键合概述 作者:聂仁勇海太半导体(无锡)有限公司 引言 半导体芯片封装是指利用精密焊接技术,将芯片粘贴并固定在框架或PBC板等基座上,并通过金丝、铜丝、铝丝或其他介质将芯片的键合区与基座连接起来,再用绝缘材料将它们保护起来,构成独立的电子元器件的工艺。 半导体芯片封装的目的,在于保护芯片不受或少受外界环境的影响,并为它提供一个发挥半导体芯片功能的良好工作环境,以使之稳定、可靠、正常地完成相应的功能。但是芯片的封装只会限制而不会提高芯片的功能。在这样的情况下,全世界都在努力研究并并不断推出新的封装形式,以最大限度地发挥半导体芯片尤其是半导体集成电路本应有的功能,减小因封装对芯片功能产生的影响。半导体芯片封装流程可以分为“前道”流程和“后道”流程两部分。其中,“前道”流程包括贴片(Die Bonding)和键合(Wire Bonding)两道工序,是整个半导体芯片封装流程中至关重要的两道工序,它们决定了整个封装流程的成败;“后道”流程则包括塑封、后固化、高温贮存、去飞边、浸锡(电镀)、切筋(打弯)、测试分类、mark、包装等工序,“后道”流程中测试分类也是比较重要的一道工序,它决定了产品的“去留”。本文将着重介绍贴片和键合这两道工序。 贴片(Die Bonding) 贴片(Die Bonding),是将半导体芯片固定于基板或引线框架的Pad上的工艺工程。装片需要选择与芯片相匹配的基座或Pad的引线框架,因为若基座或Pad太大,则会使内引线宽度太大,在“后道”塑封过程中会由于塑封体流动产生的应力而造成内引线断裂、塌丝等现象,从而导致TEST 不良品增多。 另外,为了形成良好的装片成品率,还需要完善的工艺要素与之相配合,主要包括:温度、时间、气氛、压力等几种因素。

《半导体器件导论》 第4章载流子输运和过剩载流子现象 例4.1 计算给定电场强度下半导体的漂移电流密度。T=300K时,硅的掺杂浓度为N d=106cm,N a=0。电子和空穴的迁移率参见表4.1。若外加电场强度ε=35V cm ?,求漂移电流密度。 【解】 因为N d>N a,所以在室温下,半导体是n型的。若假设掺入杂质完全电离,则 n≈N d=1016cm?3 少数载流子空穴的浓度为 P=n i 2 n =(1.5×1010) 2 1016 =2.25×104cm?3 既然n?p,漂移电流密度 J drf=e(μn n+μp p)ε≈eμn nε 因此 J drf=(1.6×10?19)(1350)(1016)(35)=75.6A cm2 ? 【说明】 在半导体上施加较小的电场就能获得显著的漂移电流密度。这个结果意味着非常小的半导体器件就能产生mA量级的电流。 例4.2 确定硅在不同温度下的电子和空穴迁移率。利用图4.2分别求出以下两种情况载流随机热速度增加子的迁移率。 (a) 确定(i)N d=1017cm?3,Τ=150℃及(ii)N d=1016cm?3,Τ=0℃时的电子迁移率。 (b) 确定(i)N a=1016cm?3,Τ=50℃及(ii)N a=1016cm?3,Τ=150℃时的空穴迁移率。【解】 由图4.2可知: (a)(i)当N d=1017cm?3,Τ=150℃时,电子迁移率μn≈500cm2V?s ?; (ii)当N d=1016cm?3,Τ=0℃时,电子迁移率μn≈1500cm2V?s ?。 (b)(i)当N a=1016cm?3,Τ=50℃时,空穴迁移率μp≈380cm2V?s ?; (i)当N a=1017cm?3,Τ=150℃时,空穴迁移率μp≈200cm2V?s ?。 【说明】 由本例可见,迁移率随温度升高而降低。 例4.3 为了制备具有特定电流—电压特性的半导体电阻器,试确定硅在300K时的掺杂浓度。考虑一均匀受主掺杂的条形硅半导体,其几何结构如图4.5所示。若外加偏压为5V时,电流为2mA,且电流密度不大于J drf=100A cm2 ?。试确定满足条件的截面积、长度及掺杂浓度。 图4.6 硅中电子浓度和电导率与温度倒数的关系曲线(引自S ze[14]) 【解】 所需截面积为

集成电路封装的发展现 状及趋势 公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

序号:39 集成电路封装的发展现状及趋势 姓名:张荣辰 学号: 班级:电科本1303 科目:微电子学概论 二〇一五年 12 月13 日

集成电路封装的发展现状及趋势 摘要: 随着全球集成电路行业的不断发展,集成度越来越高,芯片的尺寸不断缩小,集成电路封装技术也在不断地向前发展,封装产业也在不断更新换代。 我国集成电路行业起步较晚,国家大力促进科学技术和人才培养,重点扶持科学技术改革和创新,集成电路行业发展迅猛。而集成电路芯片的封装作为集成电路制造的重要环节,集成电路芯片封装业同样发展迅猛。得益于我国的地缘和成本优势,依靠广大市场潜力和人才发展,集成电路封装在我国拥有得天独厚的发展条件,已成为我国集成电路行业重要的组成部分,我国优先发展的就是集成电路封装。近年来国外半导体公司也向中国转移封装测试产能,我国的集成电路封装发展具有巨大的潜力。下面就集成电路封装的发展现状及未来的发展趋势进行论述。 关键词:集成电路封装、封装产业发展现状、集成电路封装发展趋势。 一、引言 晶体管的问世和集成电路芯片的出现,改写了电子工程的历史。这些半导体元器件的性能高,并且多功能、多规格。但是这些元器件也有细小易碎的缺点。为了充分发挥半导体元器件的功能,需要对其进行密封、扩大,以实现与外电路可靠的电气连接并得到有效的机械、绝缘等

方面的保护,防止外力或环境因素导致的破坏。“封装”的概念正事在此基础上出现的。 二、集成电路封装的概述 集成电路芯片封装(Packaging,PKG)是指利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连线,引出接线端并通过可塑性绝缘介质灌封固定,构成整体立体结构的工艺。此概念称为狭义的封装。 集成电路封装的目的,在于保护芯片不受或少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。封装为芯片提供了一种保护,人们平时所看到的电子设备如计算机、家用电器、通信设备等中的集成电路芯片都是封装好的,没有封装的集成电路芯片一般是不能直接使用的。 集成电路封装的种类按照外形、尺寸、结构分类可分为引脚插入型、贴片型和高级封装。 引脚插入型有DIP、SIP、S-DIP、SK-DIP、PGA DIP:双列直插式封装;引脚在芯片两侧排列,引脚节距,有利于散热,电气性好。 SIP:单列直插式封装;引脚在芯片单侧排列,引脚节距等特征与DIP基本相同。

《微电子封装技术》试卷 一、填空题(每空2分,共40分) 1.狭义的集成电路芯片封装是指利用精细加工技术及,将芯片及其它要素在框架或基板上,经过布置、粘贴及固定等形成整体立体结构的工艺。 2.通常情况下,厚膜浆料的制备开始于粉末状的物质,为了确保厚膜浆料达到规定的要求,可用颗粒、固体粉末百分比含量、三个参数来表征厚膜浆料。 3.利用厚膜技术可以制作厚膜电阻,其工艺为将玻璃颗粒与颗粒相混合,然后在足够的温度/时间下进行烧结以使两者烧结在一起。 4.芯片封装常用的材料包括金属、陶瓷、玻璃、高分子等,其中封装能提供最好的封装气密性。 5.塑料封装的成型技术包括喷射成型技术、、预成型技术。 6.常见的电路板包括硬式印制电路板、、金属夹层电路板、射出成型电路板四种类型。 7. 在元器件与电路板完成焊接后,电路板表面会存在一些污染,包括非极性/非离子污染、、离子污染、不溶解/粒状污染4大类。 8. 陶瓷封装最常用的材料是氧化铝,用于陶瓷封装的无机浆料一般在其中添加玻璃粉,其目的是调整氧化铝的介电系数、,降低烧结温度。 9. 转移铸膜为塑料封装最常使用的密封工艺技术,在实施此工艺过程中最常发生的封装缺陷是现象。 10. 芯片完成封装后要进行检测,一般情况下要进行质量和两方面的检测。 11. BGA封装的最大优点是可最大限度地节约基板上的空间,BGA可分为四种类型:塑料球栅阵列、、陶瓷圆柱栅格阵列、载带球栅阵列。 12. 为了获得最佳的共晶贴装,通常在IC芯片背面镀上一层金的薄膜或在基板的芯片承载架上先植入。 13. 常见的芯片互连技术包括载带自动键合、、倒装芯片键合三种。 14. 用于制造薄膜的技术包括蒸发、溅射、电镀、。 15. 厚膜制造工艺包括丝网印刷、干燥、烧结,厚膜浆料的组分包括可挥发性组分和不挥发性组分,其中实施厚膜浆料干燥工艺的目的是去除浆料中的绝大部分。 16. 根据封装元器件的引脚分布形态,可将封装元器件分为单边引脚、双边引脚、与底部引脚四种。 17. 载带自动键合与倒装芯片键合共同的关键技术是芯片的制作工艺,这些工艺包括蒸发/溅射、电镀、置球、化学镀、激光法、移植法、叠层制作法等。 18. 厚膜浆料必须具备的两个特性,一是用于丝网印刷的浆料为具有非牛顿流变能力的粘性流体;二是由两种不同的多组分相组成,即和载体相。 19. 烧结为陶瓷基板成型的关键步骤,在烧结过程中,最常发生的现象为生胚片的现

芯片封装的主要步骤 板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。 裸芯片技术主要有两种形式:一种是COB技术,另一种是倒装片技术(Flip Chip)。板上芯片封装(COB),半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。虽然COB是最简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。 COB主要的焊接方法: (1)热压焊 利用加热和加压力使金属丝与焊区压焊在一起。其原理是通过加热和加压力,使焊区(如AI)发生塑性形变同时破坏压焊界面上的氧化层,从而使原子间产生吸引力达到“键合”的目的,此外,两金属界面不平整加热加压时可使上下的金属相互镶嵌。此技术一般用为玻璃板上芯片COG。 (2)超声焊 超声焊是利用超声波发生器产生的能量,通过换能器在超高频的磁场感应下,迅速伸缩产生弹性振动,使劈刀相应振动,同时在劈刀上施加一定的压力,于是劈刀在这两种力的共同作用下,带动AI丝在被焊区的金属化层如(AI膜)表面迅速摩擦,使AI丝和AI膜表面产生塑性变形,这种形变也破坏了AI层界面的氧化层,使两个纯净的金属表面紧密接触达到原子间的结合,从而形成焊接。主要焊接材料为铝线焊头,一般为楔形。 (3)金丝焊 球焊在引线键合中是最具代表性的焊接技术,因为现在的半导体封装二、三极管封装都采用AU线球焊。而且它操作方便、灵活、焊点牢固(直径为25UM的AU丝的焊接强度一般为0.07~0.09N/点),又无方向性,焊接速度可高达15点/秒以上。金丝焊也叫热(压)(超)声焊主要键合材料为金(AU)线焊头为球形故为球焊。 COB封装流程 第一步:扩晶。采用扩张机将厂商提供的整张LED晶片薄膜均匀扩张,使附着在薄膜表面紧密排列的LED晶粒拉开,便于刺晶。 第二步:背胶。将扩好晶的扩晶环放在已刮好银浆层的背胶机面上,背上银浆。点银浆。

半导体集成电路封装技术试题汇总 第一章集成电路芯片封装技术 1. (P1)封装概念:狭义:集成电路芯片封装是利用(膜技术)及(微细加工技术),将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体结构的工艺。 广义:将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程。 2.集成电路封装的目的:在于保护芯片不受或者少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。 3.芯片封装所实现的功能:①传递电能,②传递电路信号,③提供散热途径,④结构保护与支持。 4.在选择具体的封装形式时主要考虑四种主要设计参数:性能,尺寸,重量,可靠性和成本目标。 5.封装工程的技术的技术层次? 第一层次,又称为芯片层次的封装,是指把集成电路芯片与封装基板或引脚架之间的粘贴固定电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层次的组装进行连接的模块元件。第二层次,将数个第一层次完成的封装与其他电子元器件组成一个电子卡的工艺。第三层次,将数个第二层次完成的封装组成的电路卡组合成在一个主电路版上使之成为一个部件或子系统的工艺。第四层次,将数个子系统组装成为一个完整电子厂品的工艺过程。 6.封装的分类?

按照封装中组合集成电路芯片的数目,芯片封装可分为:单芯片封装与多芯片封装两大类,按照密封的材料区分,可分为高分子材料和陶瓷为主的种类,按照器件与电路板互连方式,封装可区分为引脚插入型和表面贴装型两大类。依据引脚分布形态区分,封装元器件有单边引脚,双边引脚,四边引脚,底部引脚四种。常见的单边引脚有单列式封装与交叉引脚式封装,双边引脚元器件有双列式封装小型化封装,四边引脚有四边扁平封装,底部引脚有金属罐式与点阵列式封装。 7.芯片封装所使用的材料有金属陶瓷玻璃高分子 8.集成电路的发展主要表现在以下几个方面? 1芯片尺寸变得越来越大2工作频率越来越高3发热量日趋增大4引脚越来越多 对封装的要求:1小型化2适应高发热3集成度提高,同时适应大芯片要求4高密度化5适应多引脚6适应高温环境7适应高可靠性 9.有关名词: SIP :单列式封装 SQP:小型化封装 MCP:金属鑵式封装 DIP:双列式封装 CSP:芯片尺寸封装 QFP:四边扁平封装 PGA:点阵式封装 BGA:球栅阵列式封装 LCCC:无引线陶瓷芯片载体 第二章封装工艺流程 1.封装工艺流程一般可以分为两个部分,用塑料封装之前的工艺步骤成为前段操作,在成型之后的工艺步骤成为后段操作

集成电路封装知识 典子封装是一个富于挑战、引人入胜的领域。它是集成电路芯片生产完成后不可缺少的一道工序,是器件到系统的桥梁。封装这一生产环节对微电子产品的质量和竞争力都有极大的影响。按目前国际上流行的看法认为,在微电子器件的总体成本中,设计占了三分之一,芯片生产占了三分之一,而封装和测试也占了三分之一,真可谓三分天下有其一。封装研究在全球范围的发展是如此迅猛,而它所面临的挑战和机遇也是自电子产品问世以来所从未遇到过的;封装所涉及的问题之多之广,也是其它许多领域中少见的,它需要从材料到工艺、从无机到聚合物、从大型生产设备到计算力学等等许许多多似乎毫不关连的专家的协同努力,是一门综合性非常强的新型高科技学科。 集成电路封装知识 典子封装是一个富于挑战、引人入胜的领域。它是集成电路芯片生产完成后不可缺少的一道工序,是器件到系统的桥梁。封装这一生产环节对微电子产品的质量和竞争力都有极大的影响。按目前国际上流行的看法认为,在微电子器件的总体成本中,设计占了三分之一,芯片生产占了三分之一,而封装和测试也占了三分之一,真可谓三分天下有其一。封装研究在全球范围的发展是如此迅猛,而它所面临的挑战和机遇也是自电子产品问世以来所从未遇到过的;封装所涉及的问题之多之广,也是其它许多领域中少见的,它需要从材料到工艺、从无机到聚合物、从大型生产设备到计算力学等等许许多多似乎毫不关连的专家的协同努力,是一门综合性非常强的新型高科技学科。 什么是电子封装(electronic packaging)? 封装最初的定义是:保护电路芯片免受周围环境的影响(包括物理、化学的影响)。所以,在最初的微电子封装中,是用金属罐(metal can) 作为外壳,用与外界完全隔离的、气密的方法,来保护脆弱的电子元件。但是,随着集成电路技术的发展,尤其是芯片钝化层技术的不断改进,封装的功能也在慢慢异化。通常认为,封装主要有四大功能,即功率分配、信号分配、散热及包装保护,它的作用是从集成电路器件到系统之间的连接,包括电学连接和物理连接。目前,集成电路芯片的I/O线越来越多,它们的电源供应和信号传送都是要通过封装来实现与系统的连接;芯片的速度越来越快,功率也越来越大,使得芯片的散热问题日趋严重;由于芯片钝化层质量的提高,封装用以保护电路功能的作用其重要性正在下降。电子封装的类型也很复杂。从使用的包装材料来分,我们可以 将封装划分为金属封装、陶瓷封装和塑料封装;从成型工艺来分,我们又可以将封装划分为预成型封装(p re-mold)和后成型封装(post-mold);至于从封装外型来讲,则有SIP(single in-line pack age)、DIP(dual in-line package)、PLCC(plastic-leaded chip carrier)、PQFP(p lastic quad flat pack)、SOP(small-outline package)、TSOP(thin small-outline package)、PPGA(plastic pin grid array)、PBGA(plastic ball grid array)、CS

半导体导论翻译(精)

半导体导论 P124-125 CHAPTER 3 The Semiconductor in Equilibrium (d) T = 400 K, N d = 0, N a = 1014 cm-3 (e) T = 500 K, N d = 1014 cm-3, Na = 0 3.37 Repeat problem 3.36 for GaAs. 3.38 Assume that silicon, germanium, and gallium arsenide each have dopant concentrations of Nd = 1X1013 cm-3 and Na = 2.5 x 1014 cm-3 at T=300K.For each of the three materials(a) Is this material n type or p type?(b) Calculate n0 and p0. 3.39 A sample of silicon at T =450K is doped with boron at a concentration 0f 1.5x1015cm-3and with arsenic at a concentration of 8 X 1014cm-3 .(a) Is the material n type or p type? (b) Determine the electron and hole concentrations .(c) Calculate the total ionized impurity concentration. 3.40 The thermal equilibrium hole concentration in silicon at T = 300 K is p0=2x1015 cm-3 .Determine the thermal-equilibrium electron concentration .Is the material n type or p type? 3.41 In a sample of GaAs at T = 200 K, we have experimentally determined that n0 = 5 p0 and that Na = 0. Calculate n0, p0, and N d. 3.42 Consider a sample of silicon doped at N d = 1014 cm-3 and Na = 0 Calcu1ate the majority-carrier concentration at (a) T = 300 K, (b) T = 350 K,(C ) T = 400 K (d) T = 450 K, and (e) T = 500 K. 3.43 Consider a sample of silicon doped at N d = 0 and Na = 1014 cm-3 .Plot the majority-carrier concentration versus temperature over the range 200≤T≤500K. 3.44 The temperature of a sample of silicon is T = 300 K and the acceptor doping concentration is Na = 0. Plot the minority-carrier concentration (on a log-log plot) versus Nd over the range 1015≤N d≤1018 cm-3. 3.45 Repeat problem 3.44 for GaAs. 3.46 A particular semiconductor material is doped at N d = 2 x 1013 cm-3, Na = 0, and the intrinsic carrier concentration is ni = 2 x 1013cm-3. Assume complete ionization. Determine the thermal-equilibrium majority-and minority-carrier concentrations. 3.47 (a) Silicon at T = 300 K is uniformly doped with arsenic atoms at a concentration of 2 x 1016cm-3and boron atoms at a concentration of 1 x1013 cm-3. Determine the thermal-equilibrium concentrations of majority and

光電子學期末報告 Introduction to InGaAsP Semiconductor Materials 指導教師:郭艷光(Yen-Kuang Kuo) 教授 學生:蔡政訓 學號:8522022 系別:物理系 班級:四年級乙班

內容大綱: (一)前言 (二)波長範圍與能隙(Eg)寬(三)起振條件與輸出功率:(四)各種不同結構的雷射(五)先進的半導體結構及其性能(六)結語 (七)參考書目

(一)、前言 現在是資訊時代,為了高速處理資訊社會所擁有的龐大資料,利用光和電子技術之光電業於焉誕生。應用同調(coherence)光的工業在1984年度(以光學式影像機為中心)的生產規模為6600億日元,到西元2000年,預料將以光通訊為中心,生產規模也將成長為12兆日元。其製品包括同調光通訊系統、光IC(光電子積體電路,OEIC)光電算機等。 光IC 係將光與電子的功能特性集積在一片基板上,而以砷化鋁鎵及磷砷化銦鎵系半導體技術最為先進,其與化合物半導體IC 同樣,有實現的可能。光電半導體材料之研究十分積極,已開發出砷化鎵、磷化銦、砷化鋁鎵、磷砷化銦鎵等。 至於光通訊系統方面,與傳統的有線通訊系統比較起來,光纖通訊具有較大的通訊頻寬,較小的訊號衰減,不受電磁波干擾,沒有串音、保密性高、線徑小、重量輕、可靠度高、、等優點,因此可已知道隨著資訊的暴漲,據高速大容量高品質的光纖通訊系統毫無疑問的將是未來資訊傳遞的主流。而光纖系統中最重要的關鍵性元件就是它的光源,也就是雷射二極體,本文就是要介紹在光纖系統中最常被使用的雷射:磷砷化銦鎵 ( InGaAsP) 的特性以及其結構。 (二)、波長範圍與能隙(Eg )寬 光纖通訊中最常使用的波長為1.3以及1.55微米,主要是由於光在石英光纖中的傳輸損失在這兩個波長最低,在1.3微米處約0.6dB/km ,而在1.55微米處約0.2 dB/km 。在光纖中,由於材料色散的緣故,不同波長的光在光纖中有不同的色散,因而傳輸速率的不同,會造成訊號的波形變形,而限制了傳輸的距離。波長於1.3微米附近的色散是零,因此雖然其損失比1.55微米時大,但仍然最常用來當作短距離光纖通訊的光源。 在光纖通訊所使用的長波長範圍內,最常用InP 為基板材料。為了能與InP 的晶格常數(a=5.87埃)相匹配,必須使用四元化合物InGaAsP 。當晶格與InP 相匹配時(y=2.2x ),其能隙Eg (單位是eV )的變化為 212.072.035.1y y Eg +-= 則我們由公式 : Eg 24.1=λ可知由0.92到1.65微米的整個波長範圍均被此種材料系統所涵蓋。

¥ 一、填空题 1、将芯片及其他要素在框架或基板上布置,粘贴固定以及连接,引出接线端子并且通过可塑性绝缘介质灌封固定的过程为狭义封装 ;在次基础之上,将封装体与装配成完整的系统或者设备,这个过程称之为广义封装。 2、芯片封装所实现的功能有传递电能;传递电路信号;提供散热途径;结构保护与支持。 3、芯片封装工艺的流程为硅片减薄与切割、芯片贴装、芯片互连、成型技术、去飞边毛刺、切筋成形、上焊锡、打码。 4、芯片贴装的主要方法有共晶粘贴法、焊接粘贴法、导电胶粘贴发、玻璃胶粘贴法。 5、金属凸点制作工艺中,多金属分层为黏着层、扩散阻挡层、表层金保护层。 6、成型技术有多种,包括了转移成型技术、喷射成型技术、预成型技术、其中最主要的是转移成型技术。 ' 7、在焊接材料中,形成焊点完成电路电气连接的物质叫做焊料;用于去除焊盘表面氧化物,提高可焊性的物质叫做助焊剂;在SMT中常用的可印刷焊接材料叫做锡膏。 8、气密性封装主要包括了金属气密性封装、陶瓷气密性封装、玻璃气密性封装。 9、薄膜工艺主要有溅射工艺、蒸发工艺、电镀工艺、

光刻工艺。 10、集成电路封装的层次分为四级分别为模块元件(Module)、电路卡工艺(Card)、主电路板(Board)、完整电子产品。 11、在芯片的减薄过程中,主要方法有磨削、研磨、干式抛光、化学机械平坦工艺、电化学腐蚀、湿法腐蚀、等离子增强化学腐蚀等。 12、芯片的互连技术可以分为打线键合技术、载带自动键合技术、倒装芯片键合技术。 ^ 13、DBG切割方法进行芯片处理时,首先进行在硅片正面切割一定深度切口再进行背面磨削。 14、膜技术包括了薄膜技术和厚膜技术,制作较厚薄膜时常采用丝网印刷和浆料干燥烧结的方法。 15、芯片的表面组装过程中,焊料的涂覆方法有点涂、 丝网印刷、钢模板印刷三种。 16、涂封技术一般包括了顺形涂封和封胶涂封。 二、名词解释 1、芯片的引线键合技术(3种) ] 是将细金属线或金属带按顺序打在芯片与引脚架或封装基板的焊垫上而形成电路互连,包括超声波键合、热压键合、热超声波键合。 2、陶瓷封装

半导体材料 摘要:目前半导体产品广泛应用于生活生产中,半导体材料及其应用已经成为衡量一个国家经济发展和科技进步的重要标志。本文对半导体材料的定义、特性性能、材料分类及应用和发展方向作出简要解析。 关键词:半导体材料半导体材料分类半导体特性制备方法半导体材料应用引言:20世纪中叶,单晶硅和半导体晶体管的发明及其硅集成电路的研制成功,导致了电子工业革命;70年代光纤通讯技术迅速发展并逐步形成高新技术产业,使人类进入信息时代;超晶格概念的提出及其半导体超晶格,量子阱材料的诞生,改变了光电器件的发展,纳米技术的发展与运用使得半导体进入纳米时代。然而半导体材料的价值仍在于它的光学、电学及其他各种特性,自硅出现在很长时间内,硅仍将是大规模集成电路的主要材料,如在军事领域中应用的抗辐射硅单体、高效太阳能电池用硅单体、红外CCD器件用硅单体等。 随着半导体技术的发展和半导体材料的研究,微电子技术朝着高密度,高可靠性方向发展,各种各样新的半导体材料出现,而 GaAs和InP基材料等还是化合物半导体及器件的主要支柱材料。与此同时以硅材料为核心的当代微电子技术趋向于纳米级,到达这一尺寸后,一些列来自期间工作原理和工艺技术本身的物理限制以及制造成本大幅度提高等将成为难以克服的问题,为满足人类社会不断增长的对更大信息量的需求,近年来新的半导体材料制备方法出现,新的制备方法的研究与发展极有可能触发当前国际前沿研究热点,从而引起新的技术革命。 中国半导体材料经过40多年的研究与发展,已具备了相当的基础,特别是在改革开放后,中国的半导体材料和半导体技术获得明显发展,除满足国内需求外,一些材料已经进入国际市场,然而综观中国半导体产业链的全局,上端的设计,制造业较弱,尤其凸显的瓶颈部位式设计与材料设备业,但是可以相信整个发展大路上市顺利的,中国半导体材料应该掌握自主知识产权,系统技术的开发人才,规模化产业化生产,尽快在材料设备业发展。 1.半导体材料的定义及性质 当今,以半导体材料为芯片的各种产品已广泛进入人们的生活生产中,电视机,电子计算机,电子表等等,半导体材料为什么会拥有如此巨大的应用,我们

一、填空题 1、将芯片及其他要素在框架或基板上布置,粘贴固定以及连接,引出接线端子并且通过可塑性绝缘介质灌封固定的过程为狭义封装 ;在次基础之上,将封装体与装配成完整的系统或者设备,这个过程称之为广义封装。 2、芯片封装所实现的功能有传递电能;传递电路信号;提供散热途径;结构保护与支持。 3、芯片封装工艺的流程为硅片减薄与切割、芯片贴装、芯片互连、成型技术、去飞边毛刺、切筋成形、上焊锡、打码。 4、芯片贴装的主要方法有共晶粘贴法、焊接粘贴法、导电胶粘贴发、玻璃胶粘贴法。 5、金属凸点制作工艺中,多金属分层为黏着层、扩散阻挡层、表层金保护层。 6、成型技术有多种,包括了转移成型技术、喷射成型技术、预成型技术、其中最主要的是转移成型技术。 7、在焊接材料中,形成焊点完成电路电气连接的物质叫做焊料;用于去除焊盘表面氧化物,提高可焊性的物质叫做助焊剂;在SMT中常用的可印刷焊接材料叫做锡膏。 8、气密性封装主要包括了金属气密性封装、陶瓷气密性封装、玻璃气密性封装。 9、薄膜工艺主要有溅射工艺、蒸发工艺、电镀工艺、 光刻工艺。

10、集成电路封装的层次分为四级分别为模块元件(Module)、电路卡工艺(Card)、主电路板(Board)、完整电子产品。 11、在芯片的减薄过程中,主要方法有磨削、研磨、干式抛光、化学机械平坦工艺、电化学腐蚀、湿法腐蚀、等离子增强化学腐蚀等。 12、芯片的互连技术可以分为打线键合技术、载带自动键合技术、倒装芯片键合技术。 13、DBG切割方法进行芯片处理时,首先进行在硅片正面切割一定深度切口再进行背面磨削。 14、膜技术包括了薄膜技术和厚膜技术,制作较厚薄膜时常采用丝网印刷和浆料干燥烧结的方法。 15、芯片的表面组装过程中,焊料的涂覆方法有点涂、 丝网印刷、钢模板印刷三种。 16、涂封技术一般包括了顺形涂封和封胶涂封。 二、名词解释 1、芯片的引线键合技术(3种) 是将细金属线或金属带按顺序打在芯片与引脚架或封装基板的焊垫上而形成电路互连,包括超声波键合、热压键合、热超声波键合。 2、陶瓷封装 陶瓷封装能提供高可靠度与密封性是利用玻璃与陶瓷及Kovar 或Alloy42合金引脚架材料间能形成紧密接合的特性。