(19)中华人民共和国国家知识产权局

(12)发明专利申请

(10)申请公布号 (43)申请公布日 (21)申请号 201910140900.9

(22)申请日 2019.02.26

(71)申请人 中国电子科技集团公司第二十四研

究所

地址 400060 重庆市南岸区南坪花园路14

号

(72)发明人 徐代果 蒋和全 徐学良 王健安

陈光炳 付东兵 王育新 于晓权

徐世六 刘涛

(74)专利代理机构 重庆辉腾律师事务所 50215

代理人 卢胜斌

(51)Int.Cl.

H03M 1/38(2006.01)

H03M 1/12(2006.01)

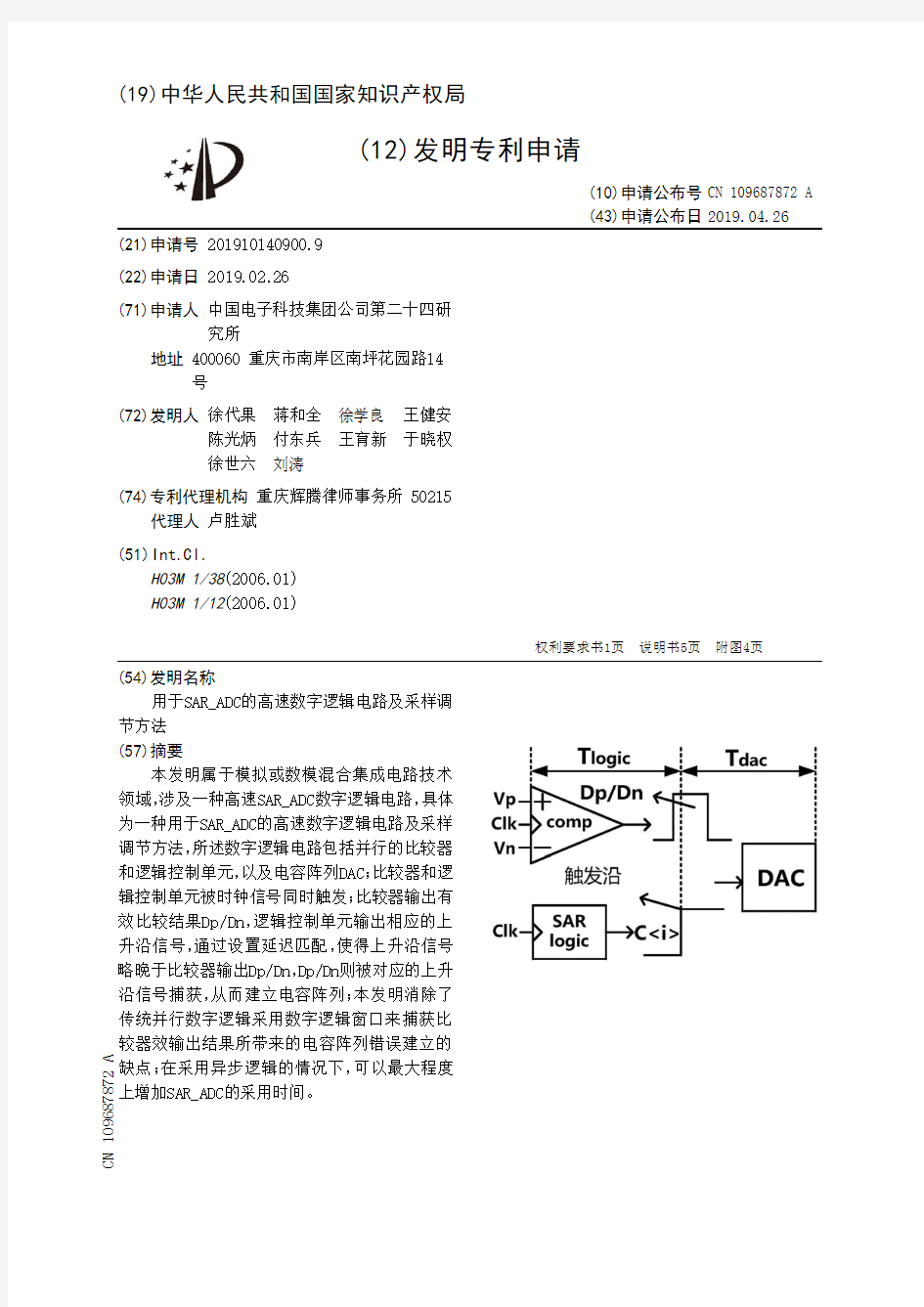

(54)发明名称用于SAR_ADC的高速数字逻辑电路及采样调节方法(57)摘要本发明属于模拟或数模混合集成电路技术领域,涉及一种高速SAR_ADC数字逻辑电路,具体为一种用于SAR_ADC的高速数字逻辑电路及采样调节方法,所述数字逻辑电路包括并行的比较器和逻辑控制单元,以及电容阵列DAC;比较器和逻辑控制单元被时钟信号同时触发;比较器输出有效比较结果Dp/Dn,逻辑控制单元输出相应的上升沿信号,通过设置延迟匹配,使得上升沿信号略晚于比较器输出Dp/Dn,Dp/Dn则被对应的上升沿信号捕获,从而建立电容阵列;本发明消除了传统并行数字逻辑采用数字逻辑窗口来捕获比较器效输出结果所带来的电容阵列错误建立的缺点;在采用异步逻辑的情况下,可以最大程度

上增加SAR_ADC的采用时间。权利要求书1页 说明书5页 附图4页CN 109687872 A 2019.04.26

C N 109687872

A

权 利 要 求 书1/1页CN 109687872 A

1.一种用于SAR_ADC的高速数字逻辑电路,所述电路包括并行的比较器和逻辑控制单元,以及电容阵列DAC;其特征在于,比较器和逻辑控制单元被时钟信号Clk同时触发;比较器输出有效比较结果Dp/Dn,逻辑控制单元输出相应的上升沿信号C,通过设置延迟匹配,使得逻辑控制单元输出的上升沿信号C略晚于比较器输出有效比较结果Dp/Dn,从而使得Dp/Dn被对应的上升沿信号C捕获,从而建立电容阵列;i=0,1,…,N-1,N表示SAR_ ADC的位数。

2.根据权利要求1所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,所述逻辑控制单元包括或门和串联的N+1个D触发器,所述D触发器包括与门、上拉PMOS管、传输门和多个反相器;数据信号D从数据输入端进入传输门并发送至第一反相器,复位信号R从复位信号输入端对第一反相器输出的信号进行反向处理,经过第二反相器的数据输出端输出数据信号Q;将复位信号R与时钟输入端CP端的时钟信号Clk中CP经过与门从第三反相器的输出。

3.根据权利要求2所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,当复位信号输入端输入的复位信号R和时钟信号CP都为0时,D触发器的数据输出端Q被复位为0;当复位信号输入端的复位信号R为1,且时钟信号输入端的时钟信号CP为1时,D触发器的数据输出端的输出数据信号Q被刷新为其数据输入端的输入信号D;D 触发器的复位信号R为1,时钟信号CP为0时,D触发器的数据输出端Q保持上一个状态的值;D触发器的复位信号R为0时,比较器的时钟信号CP不能为1。

4.根据权利要求2或3所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,所述复位信号输入端是通过内部采样控制信号Clks_in的反相信号Clks_inn进行控制;所述内部采样控制信号Clks_in包括通过将第N+1个D触发器的输出信号和外部采样控制信号输入或门,或门的输出信号即为内部采样控制信号Clks_in。

5.一种用于权利要求1~4任一所述的SAR_ADC的高速数字逻辑电路的采样调节方法,其特征在于,所述方法包括当N次逐次逼近过程完成后,外部采样控制信号Clks仍然为0,第N+1个D触发器产生的输出信号变为1,使得或门的输出信号变为1,从而SAR_ADC立即进入采样状态,同时,前N个D触发器被复位;当外部采样控制信号Clks由0变为1之后,第N+1个D触发器的被复位,其输出信号变为0,或门的输出信号仍然保持为1,使得SAR_ADC仍然处于采样状态,直到外部采样控制信号变为0,采样状态结束,SAR_ADC进入逐次逼近状态。

2