DDS 电路设计

摘要

本文介绍了DDS的原理,给出了用Altera Cyclone 1 EP1CQ240C8 FPGA芯片实现直接数字频率合成器的工作原理、设计思路、电路结

构和仿真结果以及频谱纯度分析。

关键词:直接数字频率合成(DDS);现场可编程门阵列(FPGA);相位累加器

一、DDS原理概述

1、DDS在基本原理

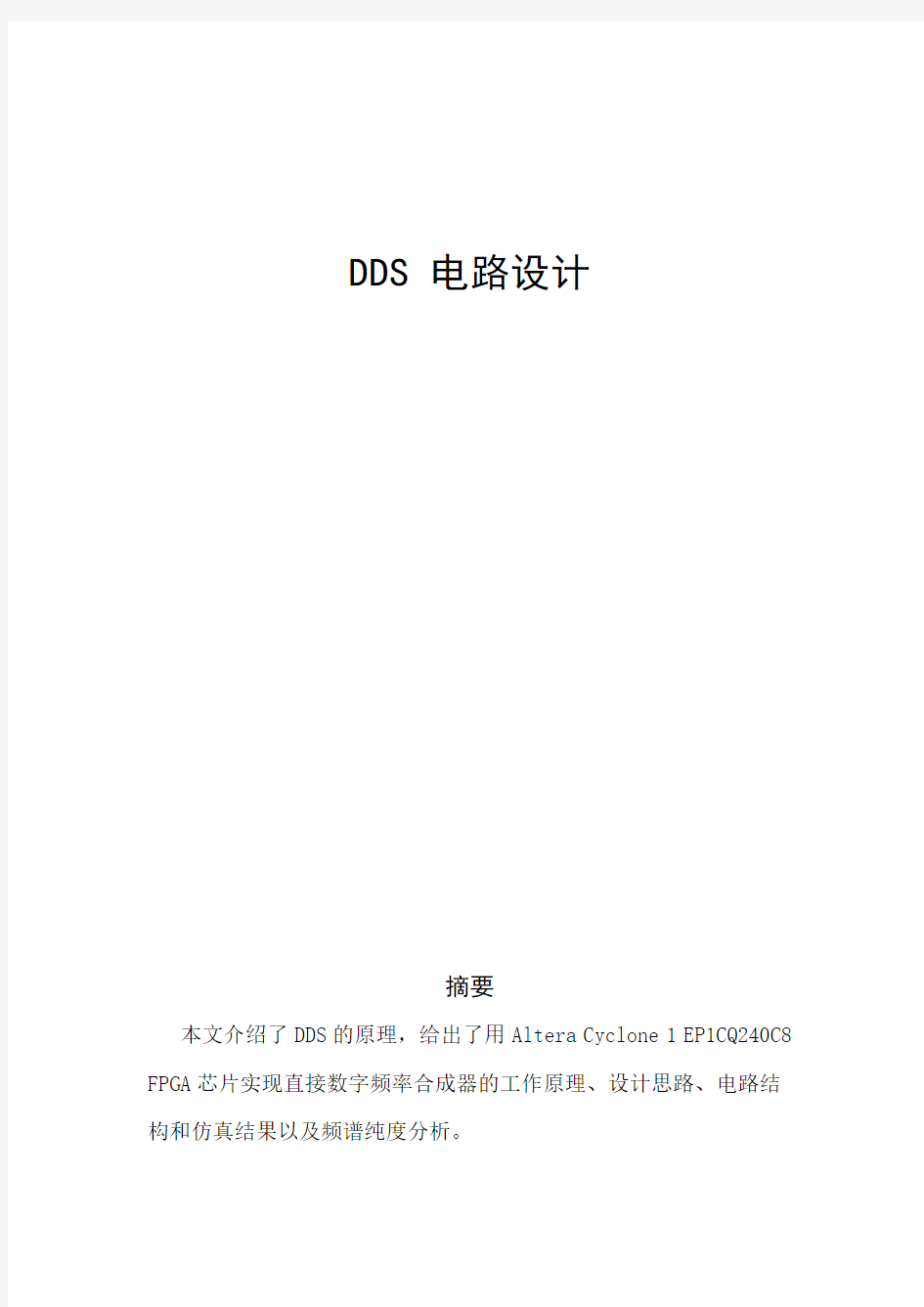

框图如图所示。它主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。DDS的实质是对相位进行可控等间隔的采样。

为实现全数字化的频率可调的频率合成器,本系统基于FPGA采用Verilog HDL设计而成直接数字频率合成器(DDS)。

系统由加法器、累加寄存器、波形存储器、D/A转换器、低通滤波器构成。在FPGA 里面做到的是D/A转换器之前的部分。

图一DDS原理图

DDS系统的核心是相位累加器,它由一个N位累加器与N位相位寄存器构成。时钟脉冲每触发一次,累加器便将频率控制数据与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位寄存器的数据输入端。相位寄存器将累加器在上一个时钟作用后所产生的新相位数据反馈到累加器的输入端,以使加法器在下一个时钟的作用下继续与频率控制数据相加。这样,相位累加器在参考时钟的作用下将进行线性相位累加,当相位累加器累加满时,就会产生一次溢出,以完成一个周期性的动作,这个周期就是DDS合成信号的一个频率周期,相位累加器的溢出频率就是DDS输出的信号频率。

2、DDS参数计算

相位寄存器每经过2N/M 个f c 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波频率:

2

N

C out

f

f M ?

=

本设计中,N=10,M 为位宽为32的频率控制字,fc=20Mhz

二、DDS 电路结构设计

1、电路描述

接口信号

名称 位宽 方向 描述 备注 freq 32 输入 输入频率字

reset 1 输入 复位 高电平异步复位 clock 1 输入 时钟 上升沿有效 sinout 8

输出

输出波形

2补码格式

2、电路结构

DDS 模块RTL Viewer

累加器ACC模块RTL Viewer

ROM模块RTL Viewer

三、DDS电路仿真结果

1、Quartus时序仿真

设定时序分析工具为Class timing analyzer tool,观察电路最大运行频率fMAX

用二补码格式观察

2、Modelsim时序仿真

参考时钟fc=20Mhz

(1)当freq =

32'b0000_0001_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 78Khz

(2)当freq =

32'b0000_0010_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 156Khz

(3)当freq =

32'b0000_0100_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo =

(4)当freq =

32'b0000_1000_0000_0000_0000_0000_0000_0000; Modelsim仿真波形如图fo = 625Khz