实验33 模拟集成电路版图的反向提取

模拟集成电路具有设计难度大、应用范围宽等优点,早已成为了集成电路设计领域的重要研究热点,引起了研究者的广泛关注。模拟集成电路版图的反向提取关乎电路设计的成败,是设计过程中的重要关键环节之一。

本实验要求学生能够独立对标准CMOS模拟集成电路版图单元,完成电路的反向提取、绘制整理和功能分析等工作。通过对CMOS模拟集成电路版图单元的反向提取实践,锻炼和提高学生对集成半导体器件和模拟集成电路版图的认知能力和对电路整理与结构优化技能,培养学生对模拟集成电路反向设计思想的理解,加强学生灵活运用所学《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等理论知识的能力。

一、实验原理

1. 模拟集成电路中的集成器件

在标准CMOS工艺下,模拟集成半导体器件主要有:MOS晶体管、扩散电阻、多晶硅电阻、多晶硅电容和MOS电容等。在P型衬底N阱CMOS工艺条件下,NMOS器件直接制作在衬底材料上,PMOS器件制作在N阱中。在模拟集成电路中,MOS晶体管常常工作在线性区或饱和区,需要承受较大的功耗,这些晶体管具有较大的宽长比。模拟集成电路版图常常不规则,这就要求在电路提取时要充分注意电路连接关系。

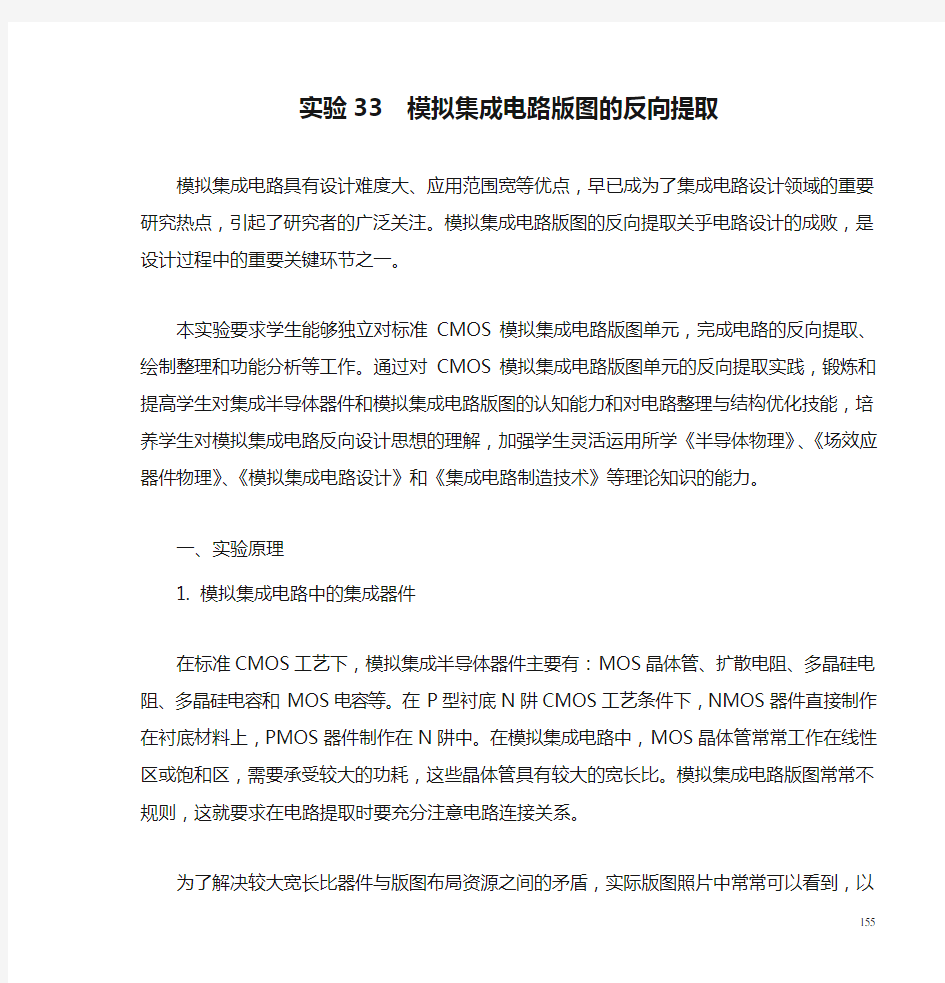

为了解决较大宽长比器件与版图布局资源之间的矛盾,实际版图照片中常常可以看到,以多只较小宽长比晶体管并联形式等效一只较大宽长比晶体管的情形。这种版图尺寸的转换技术可以实现对芯片总体布局资源的充分合理利用,同时又有利于系统的整体性能提升,有着非常重要的应用。图33.1给出了大宽长比器件转换示意图,(a)图为多只具有较小宽长比的晶体管,(b)图为这些晶体管通过共用源、漏和栅极,采用并联连接方式实现向大宽长比的转换。

(a) (b)

图33.1 大宽长比器件转换示意图

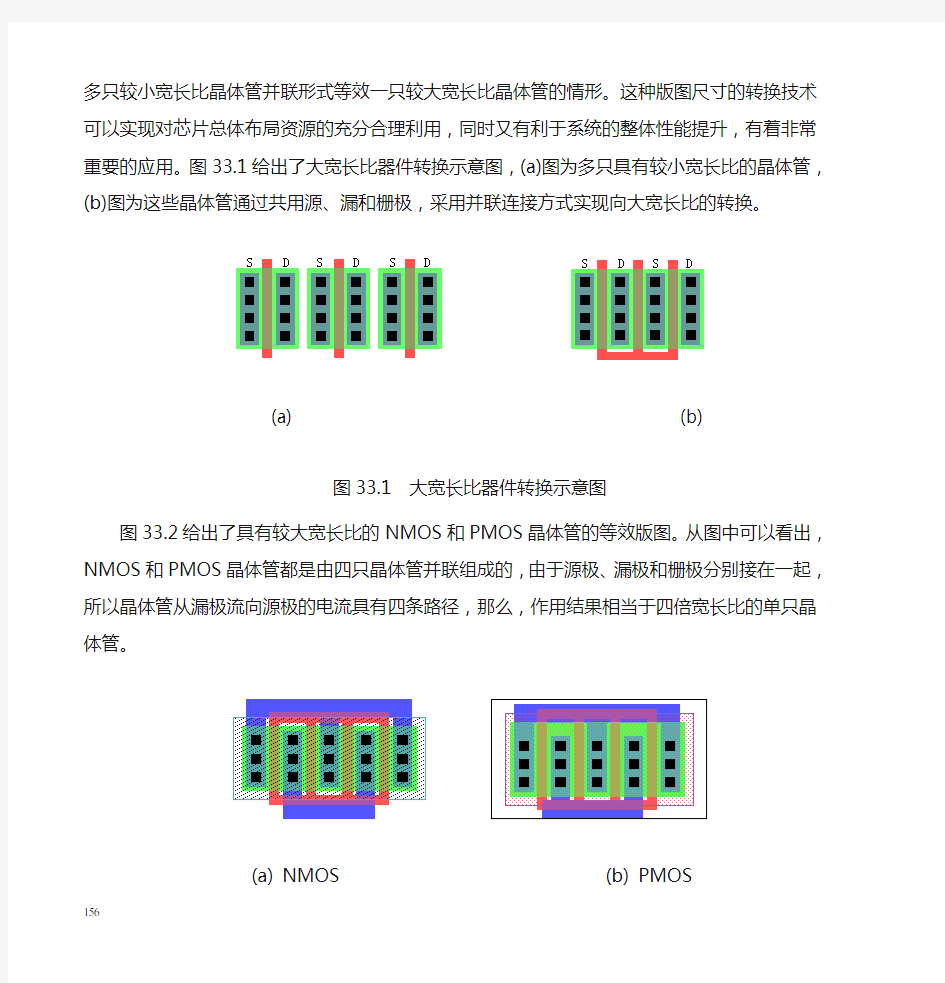

图33.2给出了具有较大宽长比的NMOS和PMOS晶体管的等效版图。从图

155

中可以看出,NMOS和PMOS晶体管都是由四只晶体管并联组成的,由于源极、漏极和栅极分别接在一起,所以晶体管从漏极流向源极的电流具有四条路径,那么,作用结果相当于四倍宽长比的单只晶体管。

(a) NMOS (b) PMOS

图33.2 具有大宽长比的NMOS和PMOS晶体管版图

在P型衬底N阱CMOS工艺条件下,有源区扩散条是小值电阻的重要选择,这是由于N型或P型有源区均为重掺杂区,具有较小的方块电阻。图33.3给出了N型和P型有源区扩散电阻,电阻的方块数包括直线部分、拐角部分和接触孔部分。拐角处可以简单地看作两个方块的电阻并联,记为0.5方块,更加细致的计算为0.56方块;接触孔处的电阻按照0.5方块进行估算;直线部分的方块数等于除去拐角部分的有源区线长度除以线宽度。这样可以计算出总方块数,然后乘以方块电阻,即为所设计电阻的阻值。

(a) N型扩散电阻(b) P型扩散电阻

图33.3 N型和P型扩散电阻版图

同样的,多晶硅中也存在重掺杂情形,N阱掺杂较轻,这样,多晶硅和N阱扩散条均可以作为电阻的选项。多晶硅适合制作阻值较小的电阻,它具有与有源区电阻相近的方块电阻。N阱扩散适合制作阻值较大的电阻。图33.4分别给出了多晶硅电阻和N阱扩散电阻版图。

(a) 多晶硅电阻(b) N阱扩散电阻

图33.4 多晶硅电阻条和N阱扩散电阻条版图

156

在CMOS工艺条件下,电容通常采用平行板电容器原理制作。电容的上极板常常采用多晶硅材料,二氧化硅薄膜作绝缘介质材料,下极板为衬底材料。图33.5给出了下极板为N型或P型有源区的NMOS电容和PMOS电容,由于这种电容具有类似MOS晶体管的结构,故而得名。

(a) NMOS电容(b) PMOS电容

图33.5 NMOS和PMOS电容版图

2. 电路提取和参数确定

在模拟集成电路版图中,普通信号连线往往比电源连线要细些,由此可以确定与NMOS源极连接连线为地线或较低电位,与PMOS源极连接连线为正电源或较高电位,这样可以确认正负电源位置。接合上述知识,可以确认版图中的各类器件。可以完成各个器件之间的连接关系确认,画出相应电路的结构图。晶体管宽长比不计算多晶硅超出有源区部分;测量电阻条长、条宽,计算方块数;测量电容宽度和长度,计算电容。

二、实验内容

1. 完成给定的P型衬底N阱CMOS工艺条件下,各模拟集成电路版图单元的电路反向提取、整理和结构优化;

2. 完成各模拟集成电路版图单元中的晶体管宽长比的测量,并将结果标注在整理完成的电路上;

3. 完成各数字集成电路单元中电阻方块数的计算和标注;

4. 完成各模拟集成电路单元中电容面积的测量和标注;

5. 进行功能分析,简要叙述电路的功能。

三、实验思考题

1. 在P型衬底N阱CMOS工艺条件下,电阻和电容的选择有那些?请举例。

2. 比较模拟集成电路和数字集成电路版图,说明两者间的主要差别。

四、参考资料

[1]. 李乃平编,《微电子器件工艺》,华中理工大学出版社,1995;

[2]. Allen, R. E.等著,《CMOS模拟集成电路设计(第二版)》,电子工业出版社,2005。

157

集成电路版图设计师职业标准(试行) 一.、职业概况 1.1 职业名称集成电路版图设计师 1.2 职业定义 通过EDA 设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII 数据。 1.3 职业等级本职业共设四个等级,分别是版图设计员(职业资格四级)、助理版图设计师(职业资格三级)、版图设计师(职业资格二级)、高级版图设计师(职业资格一级)。 1.4 职业环境条件室内、常温 1.5 职业能力特征具有良好的电脑使用基础与较强的外语阅读能力;具备一定的半导体微电子基础理论。具有很强的学习能力。 1.6 基本文化程度理工科高等专科学历。 1.7 培训要求 1.7.1 培训期限全日制职业学校教育:根据其培养目标和教学计划确定。晋级培训 期限:版图设计员不少于240 标准学时;助理版图设计师不少于 240 标准学时;版图设计师不少于200 标准学时;高级版图设计师不少于180标准学时。 1.8 鉴定要求 1.8.1 适用对象从事或准备从事集成电路版图设计的人员。 1.8.2 申报条件以上各等级申报条件均参照“关于职业技能鉴定申报条件的暂行规 定” 1.8.3 鉴定方式分为理论知识考试和技能操作考核。技能操作考核采用上机实际操作 方式, 由3- 5 名考评员组成考评小组,根据考生现场操作表现及实际操作输出结果,按统一标准评定得分。两项鉴定均采用100分制,皆达60 分及以上者为合格。 1.8.4 考评人员与考生 理论知识考试:平均15 名考生配一名考评员。技能操作考核:平均5-8 名考生配 1 名考评员。 1.8.5 鉴定时间 理论知识考试:设计员、助理设计师90 分钟,设计师、高级设计师120分钟。 技能操作考核:设计员、助理设计师90 分钟,设计师、高级设计师120分钟。 1.8.6 鉴定场地设备用于理论知识考试的标准教室;用于操作技能考试的场所:具有EDA 设计平台和网络教学系统等设备和软件,不少于20 个考位。

集成电路设计实习Integrated Circuits Design Labs I t t d Ci it D i L b 单元实验三(第二次课) 模拟电路单元实验-差分放大器版图设计 2007-2008 Institute of Microelectronics Peking University

实验内容、实验目的、时间安排 z实验内容: z完成差分放大器的版图 z完成验证:DRC、LVS、后仿真 z目的: z掌握模拟集成电路单元模块的版图设计方法 z时间安排: z一次课完成差分放大器的版图与验证 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page1

实验步骤 1.完成上节课设计放大器对应的版图 对版图进行、检查 2.DRC LVS 3.创建后仿真电路 44.后仿真(进度慢的同学可只选做部分分析) z DC分析:直流功耗等 z AC分析:增益、GBW、PM z Tran分析:建立时间、瞬态功耗等 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page2

Display Option z Layout->Options ->Display z请按左图操作 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page3

由Schematic创建Layout z Schematic->Tools->Design Synthesis->Layout XL->弹出窗口 ->Create New->OK >选择Create New>OK z Virtuoso XL->Design->Gen From Source->弹出窗口 z选择所有Pin z设置Pin的Layer z Update Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page4

实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院

一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系:

转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

电子科技大学 实验报告 学生姓名:连亚涛/王俊颖学号:2011031010032/0007指导教师:王向展实验地点:微固楼606实验时间:2014.6. 一、实验室名称:微电子技术实验室 二、实验项目名称:模拟集成电路版图设计和绘制 三、实验学时:4 四、实验原理 参照实验指导书。 五、实验目的 本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计, 掌握基本的IC版图布局布线技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计。 六、实验内容 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。 2、根据设计指标要求,自主完成版图设计,并掌握布局布线的基本技巧。 七、实验仪器设备 (1)工作站或微机终端一台

八、实验步骤 1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握CadenceEDA 仿真环境的调用。 2、根据设计指标要求,设计出如下图所示的运算放大器电路版图,过程中应注意设计规则。 九、实验数据及结果分析: 1、通过本次实验掌握了UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。达到了实验目的。 2、根据设计指标要求,设计出运算放大器模拟集成电路版图。 (备注:小组共同完成) 十、实验结论: 通过这次实验,学习并掌握国际流行的EDA仿真软件Cadence的使用方法,完成了运算放大器集成电路版图的设计,其难点是版图的布局布线和设计规则的理解。 十一、总结及心得体会: 2学会了cadence在linux下的使用,在回去安装Ubuntu的过程中发生了很多错误,有了一定的提高,让我了解到使用免费破解的专业软件的不易。其次,cadence使用过程中,有很多技巧值得认真学习,如左手键盘右手鼠标操作,以及先画基本的接触孔,再画mos管,再用已有的Mos管拼接出其他宽长比的方法。同时,学会了如何提高画图效率的“偷懒”的办法。 当然,还有很多的不足,比如有些地方容易忽略版图的规则没有全局考量,造成重复赶工。在一些技巧上,如画不规则多边形保护环的方法还是太笨,没有用聪明的方法(多次shift+c)。

北京工业大学集成电路板图设计报告 姓名:张靖维 学号:12023224 2015年 6 月 1日

目录 目录 (1) 1 绪论 (2) 1.1 介绍 (2) 1.1.1 集成电路的发展现状 (2) 1.1.2 集成电路设计流程及数字集成电路设计流程 (2) 1.1.3 CAD发展现状 (3) 2 电路设计 (4) 2.1 运算放大器电路 (4) 2.1.1 工作原理 (4) 2.1.2 电路设计 (4) 2.2 D触发器电路 (12) 2.2.1 反相器 (12) 2.2.2 传输门 (12) 2.2.3 与非门 (13) 2.2.4 D触发器 (14) 3 版图设计 (15) 3.1 运算放大器 (15) 3.1.1 运算放大器版图设计 (15) 3.2 D触发器 (16) 3.2.1 反相器 (16) 3.2.2 传输门 (17) 3.2.3 与非门 (17) 3.2.4 D触发器 (18) 4 总结与体会 (19)

1 绪论 随着晶体管的出现,集成电路随之产生,并极大地降低了电路的尺寸和成本。而由于追求集成度的提高,渐渐设计者不得不利用CAD工具设计集成电路的版图,这样大大提高了工作效率。在此单元中,我将介绍集成电路及CAD发展现状,本次课设所用EDA工具的简介以及集成电路设计流程等相关内容。 1.1介绍 1.1.1集成电路的发展现状 2014年,在国家一系列政策密集出台的环境下,在国内市场强劲需求的推动下,我国集成电路产业整体保持平稳较快增长,开始迎来发展的加速期。随着产业投入加大、技术突破与规模积累,在可以预见的未来,集成电路产业将成为支撑自主可控信息产业的核心力量,成为推动两化深度融合的重要基础。、 1.1.2集成电路设计流程及数字集成电路设计流程 集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。芯片硬件设计包括:功能设计阶段,设计描述和行为级验证,逻辑综合,门级验证(Gate-Level Netlist Verification),布局和布线。模拟集成电路设计的一般过程:电路设计,依据电路功能完成电路的设计;.前仿真,电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真;版图设计(Layout),依据所设计的电路画版图;后仿真,对所画的版图进行仿真,并与前仿真比较,若达不到要求需修改或重新设

集成电路版图设计 班级12级微电子姓名陈仁浩学号2012221105240013 摘要:介绍了集成电路版图设计的各个环节及设计过程中需注意的问题,然后将IC版图设计与PCB版图设计进行对比,分析两者的差异。最后介绍了集成电路版图设计师这一职业,加深对该行业的认识。 关键词: 集成电路版图设计 引言: 集成电路版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。近年来迅速发展的计算机、通信、嵌入式或便携式设备中集成电路的高性能低功耗运行都离不开集成电路掩模版图的精心设计。一个优秀的掩模版图设计者对于开发超性能的集成电路是极其关键的。 一、集成电路版图设计的过程 集成电路设计的流程:系统设计、逻辑设计、电路设计(包括:布局布线验证)、版图设计版图后仿真(加上寄生负载后检查设计是否能够正常工作)。集成电路版图设计是集成电路从电路拓扑到电路芯片的一个重要的设计过程,它需要设计者具有电路及电子元件的工作原理与工艺制造方面的基础知识,还需要设计者熟练运用绘图软件对电路进行合理的布局规划,设计出最大程度体现高性能、低功耗、低成本、能实际可靠工作的芯片版图。集成电路版图设计包括数字电路、模拟电路、标准单元、高频电路、双极型和射频集成电路等的版图设计。具体的过程为: 1、画版图之前,应与IC 工程师建立良好沟通在画版图之前,应该向电路设计者了解PAD 摆放的顺序及位置,了解版图的最终面积是多少。在电路当中,哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组,每组之间各自是如何分布在版图上的? IC 工程师要求的工作进度与自己预估的进度有哪些出入? 2、全局设计:这个布局图应该和功能框图或电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的任务是焊盘的布局。焊盘的安排要便于内部信号的连接,要尽量节省芯片面积以减少制作成本。焊盘的布局还应该便于测试,特别是晶上测试。 3、分层设计:按照电路功能划分整个电路,对每个功能块进行再划分,每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计,设计者需要建立多个单元。这一步就是自上向下的设计。 4、版图的检查: (1)Design Rules Checker 运行DRC,DRC 有识别能力,能够进行复杂的识别工作,在生成最终送交的图形之前进行检查。程序就按照规则检查文件运行,发现错误时,会在错误的地方做出标记,并且做出解释。

集成电路版图设计笔试面试大全 1. calibre语句 2. 对电路是否了解。似乎这个非常关心。 3. 使用的工具。 , 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula 拽可乐(DIVA),等软件进行IC版图 绘制和DRC,LVS,ERC等后端验证 4. 做过哪些模块 其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接 5. 是否用过双阱工艺。 工艺流程见版图资料 在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成,但是工艺较复杂。 制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可以用SiO2层进行注入。 双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。 N阱、P阱之间无space。

6. 你认为如何能做好一个版图,或者做一个好版图需要注意些什么需要很仔细的回答~答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。总体原则是 模拟电路应该以模拟信号对噪声的敏感度来分类。例如,低电平信号节点或高阻抗节点,它们与输入信号典型相关,因此认为它们对噪声的敏感度很高。这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。高摆幅的模拟电路,例如比较器和输出缓冲放大器应放置在敏感模拟电路和数字电路之间。数字电路应以速度和功能来分类。显而易见,因为数字输出缓冲器通常在高速时驱动电容负载,所以应使它离敏感模拟信号最远。其次,速度较低的逻辑电路位于敏感模拟电路和缓冲输出之间。注意到敏感模拟电路是尽可能远离数字缓冲输出,并且最不敏感的模拟电路与噪声最小的数字电路邻近。 芯片布局时具体需考虑的问题,如在进行系统整体版图布局时,要充分考虑模块之间的走线,避免时钟信号线对单元以及内部信号的干扰。模块间摆放时要配合压焊点的分布,另外对时钟布线要充分考虑时延,不同的时钟信号布线应尽量一致,以保证时钟之间的同步性问题。而信号的走线要完全对称以克服外界干扰。 二(电源线和地线的布局问题

模拟cmos集成电路设计实验 实验要求: 设计一个单级放大器和一个两级运算放大器。单级放大器设计在课堂检查,两级运算放大器设计需要于学期结束前,提交一份实验报告。实验报告包括以下几部分内容: 1、电路结构分析及公式推导 (例如如何根据指标确定端口电压及宽长比) 2、电路设计步骤 3、仿真测试图 (需包含瞬态、直流和交流仿真图) 4、给出每个MOS管的宽长比 (做成表格形式,并在旁边附上电路图,与电路图一一对应) 5、实验心得和小结 单级放大器设计指标 两级放大器设计指标

实验操作步骤: a.安装Xmanager b.打开Xmanager中的Xstart

c.在Xstart中输入服务器地址、账号和密码 Host:202.38.81.119 Protocol: SSH Username/password: 学号(大写)/ 学号@567& (大写)Command : Linux type 2 然后点击run运行。会弹出xterm窗口。 修改密码

输入passwd,先输入当前密码,然后再输入两遍新密码。 注意密码不会显示出来。 d.设置服务器节点 用浏览器登陆http://202.38.81.119/ganglia/,查看机器负载情况,尽量选择负载轻的机器登陆,(注:mgt和rack01不要选取) 选择节点,在xterm中输入 ssh –X c01n?? (X为大写,??为节点名) 如选择13号节点,则输入ssh –X c01n13 e.文件夹管理 通常在主目录中,不同工艺库建立相应的文件夹,便于管理。本实验采用SMIC40nm工艺,所以在主目录新建SMIC40文件夹。 在xterm中,输入mkdir SMIC40 然后进入新建的SMIC40文件夹, 在xterm中,输入cd SMIC40.

北京邮电大学 实验报告 实验题目:cmos模拟集成电路实验 姓名:何明枢 班级:2013211207 班内序号:19 学号:2013211007 指导老师:韩可 日期:2016 年 1 月16 日星期六

目录 实验一:共源级放大器性能分析 (1) 一、实验目的 (1) 二、实验内容 (1) 三、实验结果 (1) 四、实验结果分析 (3) 实验二:差分放大器设计 (4) 一、实验目的 (4) 二、实验要求 (4) 三、实验原理 (4) 四、实验结果 (5) 五、思考题 (6) 实验三:电流源负载差分放大器设计 (7) 一、实验目的 (7) 二、实验内容 (7) 三、差分放大器的设计方法 (7) 四、实验原理 (7) 五、实验结果 (9) 六、实验分析 (10) 实验五:共源共栅电流镜设计 (11) 一、实验目的 (11) 二、实验题目及要求 (11) 三、实验内容 (11) 四、实验原理 (11) 五、实验结果 (14) 六、电路工作状态分析 (15) 实验六:两级运算放大器设计 (17) 一、实验目的 (17) 二、实验要求 (17) 三、实验内容 (17) 四、实验原理 (21) 五、实验结果 (23) 六、思考题 (24) 七、实验结果分析 (24) 实验总结与体会 (26) 一、实验中遇到的的问题 (26) 二、实验体会 (26) 三、对课程的一些建议 (27)

实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验内容 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、实验电路图

实验38 模拟集成电路的版图设计 模拟集成电路设计是现代集成电路设计的重要组成部分。模拟集成电路的版图设计是模拟集成电路设计环节中的重要关键环节。模拟集成电路版图设计的优劣直接影响着整个集成电路的性能和设计的成败。 本实验要求学生在系统地学习了《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等专业知识的基础上,使用Tanner公司设计开发的集成电路版图设计工具Ledit软件,独立完成CMOS模拟集成电路单元的版图设计和布局工作,提高模拟集成电路版图设计和布局能力,强化对模拟集成电路制造技术的理解和知识运用能力,培养学生初步的模拟集成电路版图设计能力。 一、实验原理 1. 模拟集成电路版图中的器件与设计规则 在模拟集成电路中,主要器件有NMOS、PMOS、NPN和PNP晶体管,二极管、电阻和电容等。这些器件在Ledit软件中,实现的方法存在较大差异,但都是遵循器件的定义实现的。器件的定义存储在以.ext为后缀的器件萃取文件中。 在Ledit软件环境下,P型衬底N阱CMOS 2P2M工艺下(两层多晶两层金属>,模拟集成电路版图中器件的设计规则,除去与数字集成电路版图设计中通用的规则外,主要还有:NPN、PNP晶体管设计规则、电容设计规则和电阻设计规则等,表38.1中摘录了这些规则中的部分内容。使用这些设计规则可以实现NPN、PNP、MOS电容和电阻等器件版图。 表38.1 P型衬底N阱CMOS工艺下,=1.0μm部分设计规则

在绘制模拟集成电路版图时,所绘制的各种基本图形尺寸不能小于这些设计规则要求的尺寸,否则将导致设计规则错误。在Ledit软件环境下,完成设计规则检查的功能称为设计规则检查 1、 CMOS analog circuit design by P.E.ALLEN 评定:理论性90 实用性70 编写 100 精彩内容:运放的设计流程、比较器、 开关电容 这本书在国内非常流行,中文版也 翻译的很好,是很多人的入门教材。 建议大家读影印版,因为ic 领域 的绝大部分文献是以英文写成的。 如果你只能读中文版,你的学习资料 将非常有限。笔者对这本书的评价 并不高,认为该书理论有余,实用性 不足,在内容的安排上也有不妥的地 方,比如没有安排专门的章节讲述反 馈,在小信号的计算方面也没有巧方法。本书最精彩的部分应该就是运放的设计流程了。这是领域里非常重要的问题,像Allen 教授这样将设计流程一步一步表述出来在其他书里是没有的。这正体现了Allen 教授的治学风格:苛求理论的完整性系统性。但是,作为一项工程技术,最关键的是要解决问题,是能够拿出一套实用的经济的保险的方案。所以,读者会发现,看完最后一章关于ADC/DAC 的内容,似乎是面面俱到,几种结构的ADC 都提到了,但是当读者想要根据需求选择并设计一种ADC/DAC 时,却无从下手。书中关于比较器的内容也很精彩,也体现了Allen 教授求全的风格。不过,正好其它教科书里对比较器的系统讲述较少,该书正好弥补了这一缺陷。Allen 教授是开关电容电路和滤波器电路的专家。书中的相关章节很适合作为开关电容电路的入门教材。该书的排版、图表等书籍编写方面的工作也做的很好。像Allen 这样的理论派教授不管在那所大学里,大概都会很快的获得晋升吧。另外,Allen 教授的学生Rincon Moca 教授写的关于LDO 的书非常详尽,值得一读。 2、 CMOS Circuit Design Layout and Simulation CMOS Mixed-Signal Circuit Design by R.J.Baker 评定:理论性80 实用性100 编写80 精彩内容:数据转换器的建模和测量、hspice 网表这本书的风格和Allen 的书刚好相反: 理论的系统性不强,但是极为实用,甚至给出 大量的电路仿真网表和hspice 仿真图线。 这本书的中文版翻译的也很好。最近出了第二 版,翻译人员换了,不知道翻译的水平如何。 不过,第二版好贵啊~~ Baker 教授在工业界 的实战经验丰富,曾经参加过多年的军方项目 的研发,接收器,锁相环,数据转换器,DRAM 等曾设计过。所以,书中的内容几乎了包含 了数字、模拟的所有重要电路,Baker 教授 《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_ 较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来 表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输 出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制 沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS CMOS放大器设计实验报告 一、实验目的 1.培养学生分析、解决问题的综合能力; 2.熟悉计算机进行集成电路辅助设计的流程; 3.学会适应cadence设计工具; 4.掌握模拟电路仿真方法 6.掌握电子电路、电子芯片底层版图设计原则和方法; 7.掌握使用计算机对电路、电子器件进行参数提取及功能模拟的过程; 8.熟悉设计验证流程和方法。 二、实验原理 单级差分放大器结构如下图所示: 在电路结构中,M2和M3组成了NMOS差分输入对,差分输入与 单端输入相比可以有效抑制共模信号干扰;M0和M1电流镜为有源负载,可将差分输入转化为单端输出;M5管提供恒定的偏置电流。三、实验要求 设计电路使得其达到以下指标: 1.供电电压: 2.输入信号:正弦差分信号 3.共模电压范围为 4.差分模值范围 5.输出信号:正弦信号 6.摆率大于 7.带宽大于 8.幅值增益: 9.相位裕度: 10.功耗: 11.工作温度: 四、差分放大器分析 1、直流分析 为了使电路正常工作,电路中的MOS管都应处于饱和状态。 1.1 M2管的饱和条件: 1.2 M4管的饱和条件: 2.小信号分析 小信号模型如下: 由图可得: 2.1 增益分析 其中 2.2 频率响应分析由小信号模型易知: 其中 3.电路参数计算3.1确定电流 根据摆率指标: 根据功耗指标易知: 根据带宽指标: 综上,取: 3.2宽长比的确定 M4与M5:电流源提供的电流为,参数设为,根据电流镜原理,可以算出 M2与M3: 带入数据可得 取值为20,则取 M0与M1:这两个PMOS管对交流性能影响不大,只要使其下方的 关于IC集成电路版图设计的调查报告 IC版图设计是指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程,简单来说,是将所设计的电路转化为图形描述格式,即设计工艺中所需要的各种掩模板,而掩模板上的几何图形包括如下几层:n阱、有源区、多晶硅、n+和p+注入、接触孔以及金属层。 一. 版图设计流程 集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形。概括说来,对于复杂的版图设计,一般分成若干个子步骤进行: 1.模块划分。为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。 2.布局布线。布局图应该和功能框图或者电路图大体一致,然后根据各个模块的面积大小进行调整,接着完成模块间的互连,并进一步优化布线结果。 3.版图压缩。压缩是布线完成后的优化处理过程,试图进一步减小芯片的占用面积。 4.版图检查。版图检查主要包括三个部分:1. Design Rules Checker(DR C)。DRC有识别能力,能够进行复杂的识别工作,在生成最终送交的图形之前进行检查,程序就会按照规则检查文件运行,发现错误时,会在错误的地方做出标记与解释。2. Electrical Rules Checker(ERC),它是用来检查线路短路,线路开路以及floating结点。ERC检查短路错误后,会将错误提示局限在最短的连接通路上。3. Layout Versus Schematic(LVS),LVS比较IC版图和原理图,报告版图连接和原理图的不一致,并进行修改直到版图与电路图完全一致为止。 5.版图修改。此时的工作主要包括检查Label是否正确,label所选的lay er是否正确;Power & Ground连接是否有问题,得到的files是否确实可靠,检查netlist中器件类型的命名是否规范等。 模拟集成电路设计软件实验教程 月4年2006 1 目录 实验一自上而下(Top-Down)的电路设计 (3) Lab 1.1 启动软件 (3) Lab 1.2 自上而下的系统级仿真 (3) Lab 1.3 电路图输入 (7) Lab 1.4 模块的创建 (10) Lab 1.5 电源的创建 (12) Lab 1.6 建立运放测试电路 (14) 实验二使用Spectre Direct进行模拟仿真 (17) Lab 2.1 运行仿真 (17) Lab 2.2 使用激励模板 (28) Lab 2.3 波形窗的使用 (32) Lab 2.4 保存仿真状态 (36) Lab 2.5 将仿真结果注释在电路图窗口 (37) 2 实验一自上而下(Top-Down)的电路设计Lab 1.1 启动软件 实验目的: 掌握如何启动模拟电路设计环境. 实验步骤: 1.进入Linux界面后,点击鼠标右键,选中New Terminal,则会弹出一个交互终端. 2.进入教程所在目录后,输入命令cd Artist446 (注意:cd后必须有空格;命令行大小写敏感) 3.在同一个交互终端内,输入命令icms &,在屏幕底部会出现一个命令交互窗(Command Interpreter Window,CIW).如果出现What's New窗口,可使用File-Close命令关闭. Lab 1.2 自上而下的系统级仿真 实验目的: 掌握如何对含AHDL模块的模块级设计进行仿真. 实验步骤: 1.在CIW中选择Tool-Library Manager,会弹出库管理器(Library Manager). 2.在库管理器中,用鼠标左键选中training,则cell中会显示出training库中所有的cell;在training 的所有cell中用左键选中peakTestv;用鼠标中键(或右键)打开(open)view中的schematic.将会出现如下图所示的测试电路: 3 点击左当该模块四周出现一高亮黄色虚线框时,将鼠标置于图中peakDetectv模块上,3. . ,则模块四周线框变为白色实线框键选中该模块EditDesign-Hierarchy-Descend 设置Name将View ,,弹出Descend对话框4.选择: peakDetectv模块的电路图OK.为schematic,然后点击则出现 集成电路基础工艺和版图设计测试试卷 (考试时间:60分钟,总分100分) 第一部分、填空题(共30分。每空2分) 1、NMOS是利用电子来传输电信号的金属半导体;PMOS是利用空穴来传输电信号的金属半导体。 2、集成电路即“IC”,俗称芯片,按功能不同可分为数字集成电路和模拟集成电路,按导电类型不同可分为 双极型集成电路和单极型集成电路,前者频率特性好,但功耗较大,而且制作工艺复杂,不利于大规模集成;后者工作速度低,但是输入阻抗高、功耗小、制作工艺简单、易于大规模集成。 3、金属(metal)—氧化物(oxid)—半导体(semiconductor)场效应晶体管即MOS管,是一个四端有源器件,其四端分别是栅 极、源极、漏极、背栅。 4、集成电路设计分为全定制设计方法和半定制设计方法,其中全定制设计方法又分为基于门阵列和标准单元 的设计方法,芯片利用率最低的是基于门阵列的设计方法。 第二部分、不定项选择题(共45分。每题3分,多选,错选不得分,少选得1分) 1、在CMOS集成电路中,以下属于常用电容类型的有(ABCD) A、MOS电容 B、双层多晶硅电容 C、金属多晶硅电容 D、金属—金属电容 2、在CMOS集成电路中,以下属于常用电阻类型的有(ABCD) A、源漏扩散电阻 B、阱扩散电阻 C、沟道电阻 D、多晶硅电阻 3、以下属于无源器件的是(CD ) A、MOS晶体管 B、BJT晶体管 C、POL Y电阻 D、MIM电容 4、与芯片成本相关的是(ABC) A、晶圆上功能完好的芯片数 B、晶圆成本 C、芯片的成品率 D、以上都不是 5、通孔的作用是(AB ) A、连接相邻的不同金属层 B、使跳线成为可能 C、连接第一层金属和有源区 D、连接第一层金属和衬底 6、IC版图的可靠性设计主要体现在(ABC)等方面,避免器件出现毁灭性失效而影响良率。 A、天线效应 B、闩锁(Latch up) C、ESD(静电泄放)保护 D、工艺角(process corner)分析 7、减小晶体管尺寸可以有效提高数字集成电路的性能,其原因是(AB) A、寄生电容减小,增加开关速度 B、门延时和功耗乘积减小 C、高阶物理效应减少 D、门翻转电流减小 8、一般在版图设计中可能要对电源线等非常宽的金属线进行宽金属开槽,主要是抑制热效应对芯片的损害。下面哪些做法符合宽金属开槽的基本规则?(ABCD) A、开槽的拐角处呈45度角,减轻大电流密度导致的压力 B、把很宽的金属线分成几个宽度小于规则最小宽度的金属线 C、开槽的放置应该总是与电流的方向一致 D、在拐角、T型结构和电源PAD区域开槽之前要分析电流流向 9、以下版图的图层中与工艺制造中出现的外延层可能直接相接触的是(AB)。 A、AA(active area) B、NW(N-Well) C、POLY D、METAL1 模拟集成电路课程设计 设计目的: 复习、巩固模拟集成电路课程所学知识,运用EDA 软件,在一定的工艺模型基础上,完成一个基本功能单元的电路结构设计、参数手工估算和电路仿真验证,并根据仿真结果与指标间的折衷关系,对重点指标进行优化,掌握电路分析、电路设计的基本方法,加深对运放、带隙基准、稳定性、功耗等相关知识点的理解,培养分析问题、解决问题的能力。 实验安排: 同学们自由组合,2 人一个设计小组选择五道题目中的一道完成,为了避免所选题目过度集中的现象,规定每个题目的最高限额为 4 组。小组成员协调好每个人的任务,分工合作,发挥团队精神,同时注意复习课堂所学内容,必要时查阅相关文献,完成设计后对 验收与考核: 该门设计实验课程的考核将采取现场验收和设计报告相结合的方式。当小组成员完成了所选题目的设计过程,并且仿真结果达到了所要求的性能指标,可以申请现场验收,向老师演示设计步骤和仿真结果,通过验收后每小组提交一份设计报告(打印版和电子版)。其中,设计指标,电路设计要求和设计报告要求的具体内容在下面的各个题目中给出了参考。成绩的评定将根据各个小组成员在完成项目中的贡献度以及验收情况和设计报告的完成度来确定。 时间安排: 机房开放时间:2013 年10 月28 日~11 月8 日,8:30~12:00,14:00~18:00 课程设计报告提交截止日期:2012 年11 月15 日 该专题实验的总学时为48 学时(1.5 学分),请同学们安排好知识复习,理论计算与上机设计的时间,该实验以上机设计为主,在机房开放时间内保证5 天以上的上机时间,我们将实行每天上下午不定时签到制度。 工艺与模型: 采用某工艺厂提供的两层多晶、两层金属(2p2m)的0.5um CMOS 工艺,model 文件为/data/wanghy/anglog/model/s05mixdtssa01v11.scs 。绘制电路图时,器件从/data/wanghy/ anglog/st02 库中调用,采用以下器件完成设计: 1)PMOS 模型名mp,NMOS 模型名mn;2) BJT 三种模型可选:qvp5,qvp10,qvp20;3) 电阻模型rhr1k; 4)电容模型cpip。 1. calibre语句 2. 对电路是否了解。似乎这个非常关心。 3. 使用的工具。 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula拽可乐(DIVA),等软件进行IC版图绘制和DRC,LVS,ERC等后端验证 4. 做过哪些模块 其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接 5. 是否用过双阱工艺。 工艺流程见版图资料 在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种 沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成, 但是工艺较复杂。 制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可 以用SiO2层进行注入。 双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。 N阱、P阱之间无space。 6. 你认为如何能做好一个版图?或者做一个好版图需要注意些什么需要很仔细的回答! 答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。总体原则是 模拟电路应该以模拟信号对噪声的敏感度来分类。例如,低电平信号节点或高阻抗节点,它们与输入信号典型相 关,因此认为它们对噪声的敏感度很高。这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。高 摆幅的模拟电路,例如比较器和输出缓冲放大器应放置在敏感模拟电路和数字电路之间。数字电路应以速度和功能来 分类。显而易见,因为数字输出缓冲器通常在高速时驱动电容负载,所以应使它离敏感模拟信号最远。其次,速度较 低的逻辑电路位于敏感模拟电路和缓冲输出之间。注意到敏感模拟电路是尽可能远离数字缓冲输出,并且最不敏感的 模拟电路与噪声最小的数字电路邻近。 芯片布局时具体需考虑的问题,如在进行系统整体版图布局时,要充分考虑模块之间的走线,避免时钟信号线对模拟集成电路设计经典教材

模拟集成电路设计期末试卷..

模拟集成电路实验报告

集成电路版图设计调查报告

模拟集成电路设计软件使用教程

集成电路基础工艺和版图设计测试试卷

模拟集成电路课程设计

集成电路版图设计笔试面试大全整理