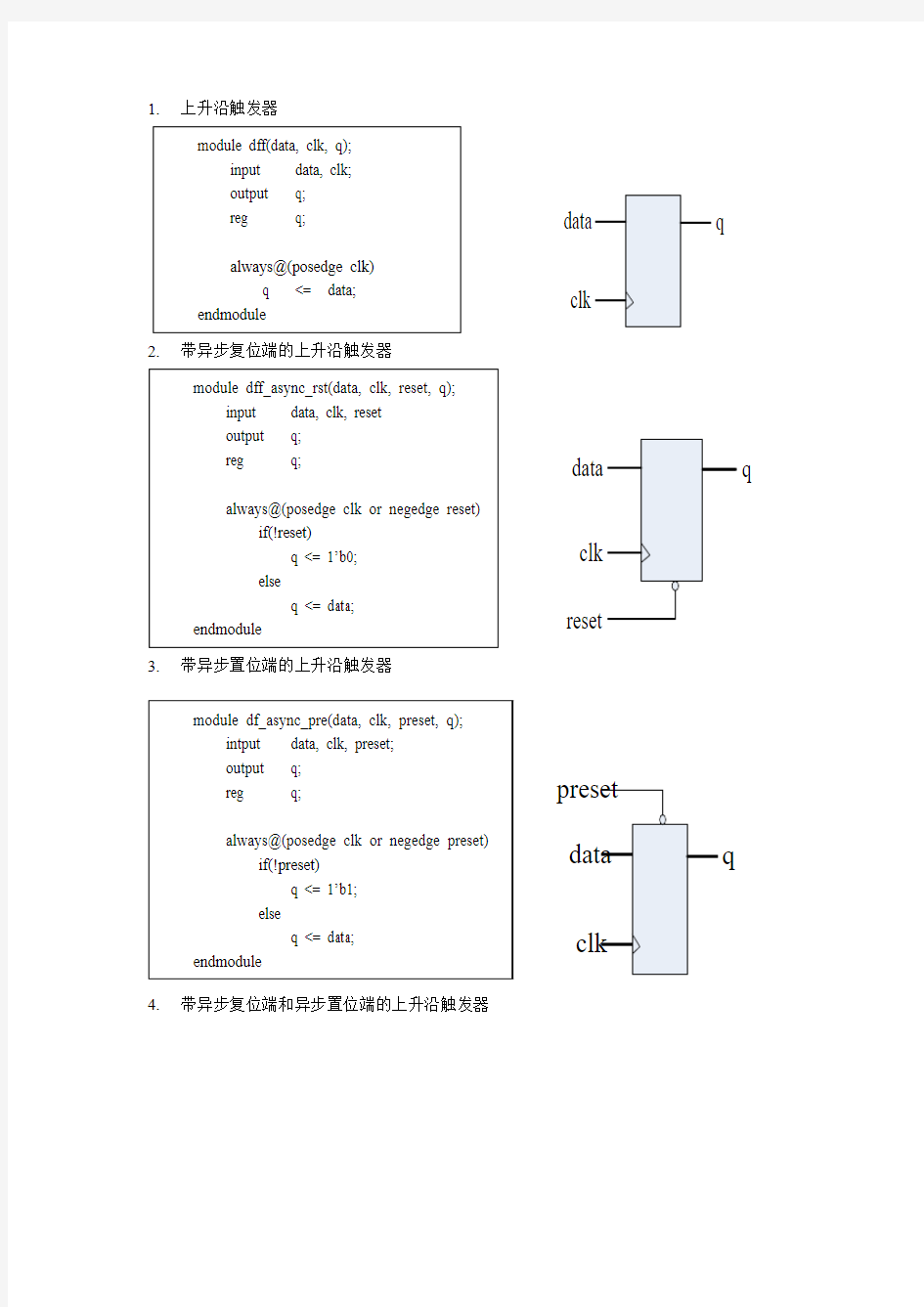

1. 上升沿触发器

q

data clk

2. 带异步复位端的上升沿触发器

q

data clk reset

3. 带异步置位端的上升沿触发器

q

data clk

4. 带异步复位端和异步置位端的上升沿触发器

q

clk

5. 带异步复位端和输出使能端上升沿触发器

q

data

clk

1. 带使能端的锁存器

q

data

enable

2. 可异步选通数据的锁存器

q

3. 可选通使能端的锁存器

q

4. 带异步复位端的锁存器

q

verilog 数字系统设计教程习题答案第二章 HDL 既是一种行为描述语言,也是一种结构描述语言。如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。这意味着利用Verilog 语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。 2.模块的基本结构由关键词module和endmodule构成。 3.一个复杂电路系统的完整Verilog HDL 模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。 HDL和VHDL乍为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。 5.不是

6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 7.综合工具可以把HDL变成门级网表。这方面Synopsys工具占有较大的优势,它的Design Compile 是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler ,可以提供更高级的综合。 另外最近美国又出了一个软件叫Ambit ,据说比Synopsys 的软件更有效,可以综合50万门的电路,速度更快。今年初Ambit 被Cadence 公司收购,为此Cade nee放弃了它原来的综合软件Syn ergy。随着FPGA 设计的规模越来越大,各EDA公司又开发了用于FPGA设计的综合软件,比较有名的有:Sy nopsys 的FPGAExpress,Cade nee 的Syn plity ,Mentor的Leonardo,这三家的FPGA综合软件占了市场的绝大部分。 8.整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件 进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。用于适配,适配将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如JEDEC Jam格式的 文件 9.在FPGA设计中,仿真一般分为功能仿真(前仿真)和时序仿真(后仿真)。功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证;而时序仿真是在布局布线后进行,它与

给两个例子, 一个是VHDL做顶层调用verilog 一个是verilog 做顶层调用VHDL VHDL调用verilog: module sync_block #( parameter INITIALISE = 2'b00 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); //VHD entity dcm_reset is port( ref_reset : in std_logic; -- Synchronous reset in ref_clk domain ref_clk : in std_logic; -- Reliable reference clock of known frequency (125MHz) dcm_locked : in std_logic; -- The DCM locked signal dcm_reset : out std_logic -- The reset signal which should be connected to the DCM ); end dcm_reset; component sync_block port ( clk : in std_logic; -- clock to be sync'ed to data_in : in std_logic; -- Data to be 'synced' data_out : out std_logic -- synced data ); end component; dcm_locked_sync_tx : sync_block port map( clk => ref_clk, data_in => dcm_locked, data_out => dcm_locked_sync ); verilog调用VHDL:(目标还是上述VHDL模块) module gmii_if ( …… ); dcm_reset rx_dcm_reset ( .ref_reset (tx_reset), .ref_clk (tx_clk),

SystemVerilog Tutorials 下面的手册会帮助你了解一些SystemVerilog中最重要的新特点。手册还提供了一些代码样本和例子使你可以对语言有更好"感觉"。这些辅导假设你们已经了解了一些Verilog语言。如果没有,你可以先去看看Verilog设计者指南(V erilog Designer’s Guide)。 * Data types * RTL design * Interfaces * Clocking * Assertion-based verification * Classes * Testbench automation and constraints * The Direct Programming Interface (DPI) SystemVerilog 的数据类型 这个手册将描述Systemverilog新引进的数据类型。他们大多数都是可以综合的,并且可以使RTL级描述更易于理解和书写。 整型和实型 SystemVerilog引进了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVerilog有相同的数据类型可以使C语言算法模型更容易的转化为SystemVerilog模型。 Verilog的变量类型有四态:既是0,1,X,Z。SystemVerilog引进了新的两态数据类型,每一位只可以是0或是1。当你不需要使用的X和Z值时,譬如在写Testbench和做为for语句的循环变量。使用两态变量的RTL级模型,可以使模拟器更有效率。并且使用得当的话将不会对综合结果产生影响。 二态整型 类型描述例子 Bit user-defined size bit [3:0] a_nibble; Byte 8 bits, unsigned byte a, b; Shortint 16 bits, signed shortint c, d; Int 32 bits, signed int i,j; Longint 64 bits, signed longint lword;

本文档含有很多Verilog HDL例子://与门 module zxhand2(c,a,b); input a,b; output c; assign c= a & b; endmodule //或门 module zxhor2(c,a,b); input a,b; output c; assign c= a | b; endmodule //非门 module zxhnot2(c,b); input b; output c; assign c=~ b; endmodule ////异或门 module zxhxro2(c,a,b); input b; output c; assign c=a ^ b; endmodule 两选一电路 module data_scan(d0,d1,sel,q); output q; input d0,d1,sel; wire t1,t2,t3; n1 zxhand2(t1,d0,sel); n2 zxhnot2 (t4,sel); n3 zxhand2(t2,d1,t4); n4 zxhor2(t3,t1,t2);

assign q=t1; endmodule verilog HDL实例(一) 练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意 equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源代码: //--------------- compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时, //equal输出为0。 endmodule 测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。 测试模块源代码: `timescale 1ns/1ns //定义时间单位。 module comparetest; reg a,b; wire equal; initial //initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 $stop; //系统任务,暂停仿真以便观察仿真波形。 end compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。 Endmodule

Quartus Ⅱ入门教程 (一个Verilog 程序的编译和功能仿真) Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的EDA 工具进行初步的学习。使大家以后的数字系统设计更加容易上手。 ● 快捷工具栏:提供设置(setting ),编译(compile )等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。 ● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。 ● 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

1 工程名称: 2添加已有文件(没有已有文件的直接跳过next)

3 选择芯片型号(我们选择cylone II 系列下的EP2C70F896C6芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置) 4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )

5 工程建立完成(点finish )

第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。 第四步:编写程序 以实现一个与门和或门为例,Verilog描述源文件如下: module test(a,b,out1,out2); input a,b; output out1,out2; assign out1=a&b; assign out2=a | b; endmodule 然后保存源文件; 第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis))

一、组合逻辑实验 (2) 实验13X8译码器程序 (2) 实验2二-十进制译码器 (2) 实验3BCD码—七段数码管显示译码器 (3) 实验48-3编码器 (4) 实验58-3优先编码器 (4) 实验6十—二进制编码器 (5) 实验7三选一数据选择器 (5) 实验8半加器 (6) 实验9全加器 (7) 实验10半减器 (8) 实验11全减器 (8) 实验12多位数值比较器 (9) 实验13奇偶校验 (9) 实验14补码生成 (10) 实验158位硬件加法器的设计 (10) 实验164位并行乘法器 (10) 实验17七人表决器 (10) 实验18格雷码变换 (11) 二、时序逻辑实验 (11) 实验1D触发器 (11) 实验2JK触发器 (12) 实验3四位移位寄存器 (12) 实验4异步计数器 (13) 实验5同步计数器 (14) 实验6可逆计数器 (15) 实验7步长可变的加减计数器 (16) 实验8含异步清0和同步时钟使能的4位加法计数器 (17) 实验9顺序脉冲发生器 (18) 实验10序列信号发生器 (18) 实验11用状态机实现串行数据检测器 (19) 实验12分频器 (20) 实验13Moore状态机 (21) 实验14Mealy状态机 (23) 实验15三层电梯 (24) 实验16性线反馈移位寄存器(LFSR)设计 (32) 实验17正负脉宽数控调制信号发生器 (32) 三、存储器设计 (34) 实验1只读存储器(ROM) (34) 实验2SRAM (34) 实验3FIFO (35) 四、扩展接口实验 (39) 实验1流水灯 (39) 实验2VGA彩色信号显示控制器设计 (40)

【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

Verilog HDL Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象 设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 =============================== 中文版Verilog HDL简明教程:第1章简介 Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 历史 Verilog HDL语言最初是于1983年由Gateway Design Automation公司为其模

1.0 41 HDL Verilog HDL () 2004.8.3 yyyy/mm/dd

Verilog HDL 2004.8.3 1.00 2004-08-16241

28 5 ..............................................................274.8 case ..........................................................254.7 ..........................................................254.6.6 ....................................................254.6.5 ....................................................244.6.4 ................................................234.6.3 ....................................................224.6.2 ....................................................214.6.1 . (21) 4.6 .....................................................204.5.2 ...................................................204.5.1 (20) 4.5 ..........................................................184.4.2 .........................................................184.4.1 . (18) 4.4 ........................................................184.3 .............................................................174.2 .............................................................174.1.3 ..................................................174.1.2 .......................................................174.1.1 (17) 4.1 (17) 4 Verilog HDL (16) 3.3.4 ..................................................153.3.3 ..................................................143.3.2 ................................................123.3.1 (12) 3.3 ......................................................113.2 .............................................................113.1.3 ......................................................103.1.2 ....................................................93.1.1 . (9) 3.1 (9) 3 Verilog HDL (7) 2.4.2 ..........................................................72.4.1 . (7) 2.4 Verilog HDL .....................................................62.3 .........................................................62.2 .......................................................52.1 . (5) 2 HDL ......................................................51 ................................................................... Verilog HDL 2004-08-16 341

jtag的经典例子 module jtag(TCK,TMS, TDI, PROGRAM_COUNT, SFR_DATA, SOURCE_DI, XRAMDI, PROGDI, TRESET, SCLK, //Output TDO, //SOURCE_AJ, DESTIN_AJ, XRAMAJ, PROGAJ, DESTIN_DOJ, XRAMDOJ, PROGRAM_COUNTJ, PROGDOJ, NXRAMRJ, nXRAMWJ, NPSENJ ,PROGWE, SFR_WRITEJ, Write_SFR, Read_SFR , Read_RAM, NDESTIN_WEJ, nDESTIN_WEJ, Write_PC, ICReset,ICDisable,ICClock_Disable,ICClock_Enable ); //Input input TCK; input TMS; input TDI; input TRESET; input SCLK; //IC stop feedback signal at step_into state

input [15:0] PROGRAM_COUNT; //present PC value input [7:0] SFR_DATA; input [7:0] SOURCE_DI; input [7:0] XRAMDI; input [7:0] PROGDI; //Output output ICReset; output ICDisable; output ICClock_Disable; output TDO; //output [7:0] SOURCE_AJ; //output [15:0] XRAMAJ; //output [15:0] PROGAJ; //output [7:0] DESTIN_DOJ; //output [7:0] XRAMDOJ; //output [7:0] PROGDOJ; //output [15:0] PROGRAM_COUNTJ; output Write_PC; output NXRAMRJ; output nXRAMWJ;//NXRAMWJ, output NPSENJ;

modul e and1(a, b, c); input a; input b; output c; assign c = a & b; endmodul e `timescale 1ns/1ns modul e t; reg a; reg b; wire c; and1 t(a,b,c); initial begin a=0; b=0; #100 a = 1; b = 0; #100 a = 0; b = 1; #100 a = 0; b = 0; #100 a = 1; b = 1; #100 $stop;

end initial $monitor("a = %d, ", a, " b = %d, ", b, "c = %d\n", c); endmodul e modul e add(a, b, in, c, out); input a; input b; input in; output c; output out; assign {out, c} = a + b + in; endmodul e `timescal e 1ns/1ns modul e count_t; reg clk; reg a; reg b; reg in; wire c; wire out; ad d process(a, b, in, c, out);

initial clk = 0; always forever #5 clk = ~clk; initial begin a = 0; b = 0; in = 0; #10 a = 0; b = 0; in = 1; #10 a = 0; b = 1; in = 0; #10 a = 0; b = 1; in = 1; #10 a = 1; b = 0; in = 0; #10 a = 1; b = 0; in = 1; #10 a = 1; b = 1; in = 0; #10 a = 1; b = 1; in = 1; end initial begin #200 $finish; end initial $monitor(" out = %d, c = %d\n", out, c); endmodul e modul e compare (equal, a, b); input a,b; output equal; assign equal= (a==b)?1:0; endmodul e `timescal e 1ns/1ns modul e t; reg a, b; wire equal; initial begin a=0; b=0; #100 a = 1; b = 0;

?Verilog-A 30分钟快速入门教程 进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“Verilog-AMS Language Reference Manual”和ADS的帮助文档。 现在的状态算是入门了,写了个简单的PLL。总结这几天的学习,觉得效率太低,我以前有一定Verilog基础,研一时学过一点VHDL-AMS,学到现在这个状态应该半天就够了;入门的话,30分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A。(前提是有一定的Verilog基础和电路基础) 1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的简化版),作为模拟电路描述语言Verilog-A,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow)和位(Potential),在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。 在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(out)/R,这样就产生了一个电阻,最后Verilog-A仿真器会用某种算法(迭代是最常见的)将I(out)和V(out)求解出来,然后根据这个解去算下一个时刻的I、V等,当然这仅仅是指时域仿真。 2、下面讲Verilog-A的语法: begin end //相当于C语言的一对大括号,与Verilog同 if ( expression ) true_statement ; [ else false_statement ; ] //与Verilog同 case ( expression ) case_item { case_item } endcase for ( procedural_assignment ; expression; procedural_assignment ) statement //case与for语句都跟Verilog、C语言类似 cross( expr [, dir [, time_tol [, expr_tol ]]] ); //cross用来产生一个event,如: @(cross(V(sample) -2.0, +1.0)) //指sample的电压超过2.0时触发该事件,将会执行后面的语句,+1.0表示正向越过,-1.0则相反 ddt( expr ) //求导,如: I(n1,n2) <+ C * ddt(V(n1, n2)); //表示了一个电容 idt( expr ,[ ic [, assert [, abstol ]]] ) //积分,如: V(out) <+ gain * idt(V(in) ,0) + gain * V(in); //比例积分,式中的0表示积分的初值 transition( expr [, time_delay [, rise_time [, fall_time [, time_tol ]]]] ) //将expr的值delay一下并指定上升下降沿时间,相当于一个传输门

module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

?进入正题,学了几天的Verilog-A,平台是Agilent ADS,主要参考“Verilog-AMS L anguage Reference Manual”和ADS的帮助文档。 现在的状态算是入门了,写了个简单的PLL。总结这几天的学习,觉得效率太低,我以前有一定Verilog基础,研一时学过一点VHDL-AMS,学到现在这个状态应该半天就够了;入门的话,30分钟足矣;跟着这个教程走,你会很快了解和熟悉Verilog-A。(前提是有一定的Verilog 基础和电路基础) 1、基尔霍夫定律撑起了整个电路学的大厦(当然也可以认为基尔霍夫定律只是麦克斯韦方程的 简化版),作为模拟电路描述语言Verilog-A,同样将基尔霍夫定律作为其基本,最重要的两个概念便是流量(Flow)和位(Potential),在电学里是电流和电压,在力学里可以是力和距离,在热学里可以是功率和温差,等等。 在Verilog-A中,你可以将电阻电容电感等器件用一个方程式来表述,比如I(out) <+ V(o ut)/R,这样就产生了一个电阻,最后Verilog-A仿真器会用某种算法(迭代是最常见的)将I(o ut)和V(out)求解出来,然后根据这个解去算下一个时刻的I、V等,当然这仅仅是指时域仿真。 2、下面讲Verilog-A的语法: begin end //相当于C语言的一对大括号,与Verilog同 if ( expression ) true_statement ; [ else false_statement ; ] //与Verilog同 case ( expression ) case_item { case_item } endcase for ( procedural_assignment ; expression; procedural_assignment ) statement //case与for语句都跟Verilog、C语言类似 cross( expr [, dir [, time_tol [, expr_tol ]]] ); //cross用来产生一个event,如:

v e r i l o g实例代码2

//与门 module zxhand2(c,a,b); input a,b; output c; assign c= a & b; endmodule //或门 module zxhor2(c,a,b); input a,b; output c; assign c= a | b; endmodule //非门 module zxhnot2(c,b); input b; output c; assign c=~ b; endmodule ////异或门 module zxhxro2(c,a,b); input b; output c; assign c=a ^ b; endmodule 两选一电路 module data_scan(d0,d1,sel,q); output q; input d0,d1,sel; wire t1,t2,t3; n1 zxhand2(t1,d0,sel); n2 zxhnot2 (t4,sel); n3 zxhand2(t2,d1,t4); n4 zxhor2(t3,t1,t2); assign q=t1;

endmodule verilog HDL实例(一) 练习一.简单的组合逻辑设计 目的: 掌握基本组合逻辑电路的实现方法。 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。 模块源代码: //--------------- compare.v ----------------- module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时, //equal输出为0。 endmodule 测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。 测试模块源代码: `timescale 1ns/1ns //定义时间单位。 module comparetest; reg a,b; wire equal; initial //initial常用于仿真时信号的给出。 begin a=0; b=0; #100 a=0; b=1; #100 a=1; b=1; #100 a=1; b=0; #100 $stop; //系统任务,暂停仿真以便观察仿真波形。 end compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。 Endmodule

中文版)) 简明教程((中文版 Verilog HDL简明教程 Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。 Verilog HDL语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。 Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操作符和结构。Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。 历史