1、讨论集成运放稳定性与闭环增益的关系,并简述相位补偿的方法。

由于运放电路是一个多极点高增益放大器,且一般都工作在闭环状态,所以在实际应用中有时会出现自激振荡,而使运放电路不能正常工作。

产生自激振荡的条件:A(j ω)F(j ω)=-1 其中幅值条件: A(j ω)F(j ω)=1 相位条件:()()0F 2n φωφωππ

+=±±

只有同时满足幅值条件和相位条件,运放才会产生自激振荡,只满足其中条件之一,运放不会产生自激振荡。要使集成运放在闭环下能稳定地工作,就必须破坏产生自激振荡的两个条件或两个条件之一。所以运放电路闭环稳定工作的条件应为

()()A .F 1ωω≥时,相移φπ<±

相移φπ=±时,()()A .F 1

ωω<

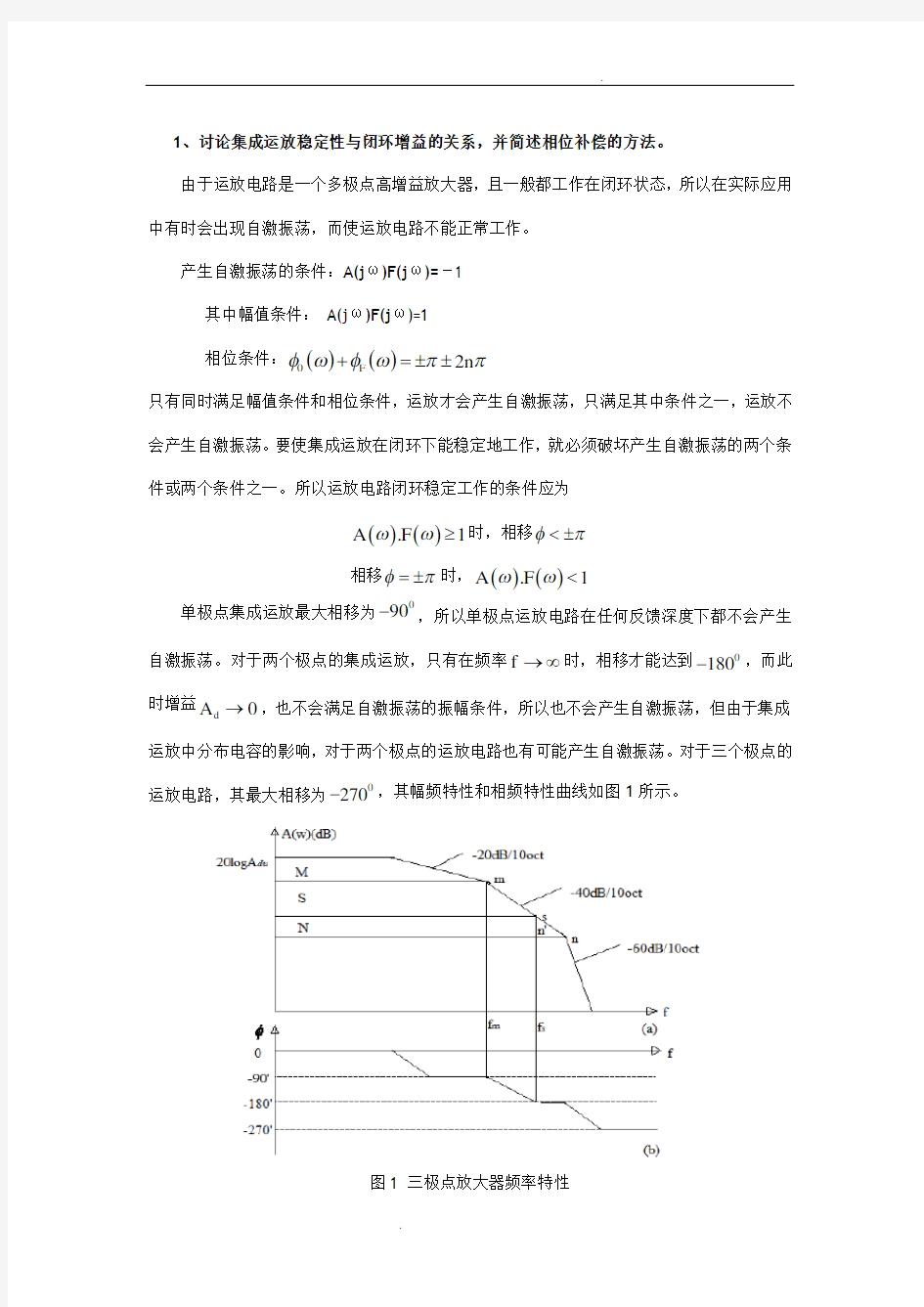

单极点集成运放最大相移为0

90-,所以单极点运放电路在任何反馈深度下都不会产生自激振荡。对于两个极点的集成运放,只有在频率f →∞时,相移才能达到0180-,而此时增益d A 0→,也不会满足自激振荡的振幅条件,所以也不会产生自激振荡,但由于集成运放中分布电容的影响,对于两个极点的运放电路也有可能产生自激振荡。对于三个极点的

运放电路,其最大相移为0

270-,其幅频特性和相频特性曲线如图1所示。

图1 三极点放大器频率特性

假设环路增益是与频率无关的常数,则环路增一为d A F ,取对数后为

d 120lg A 20lg F ??

- ?

??

其中,d 20lg A 是开环增益频率特性曲线,120lg F ??

???

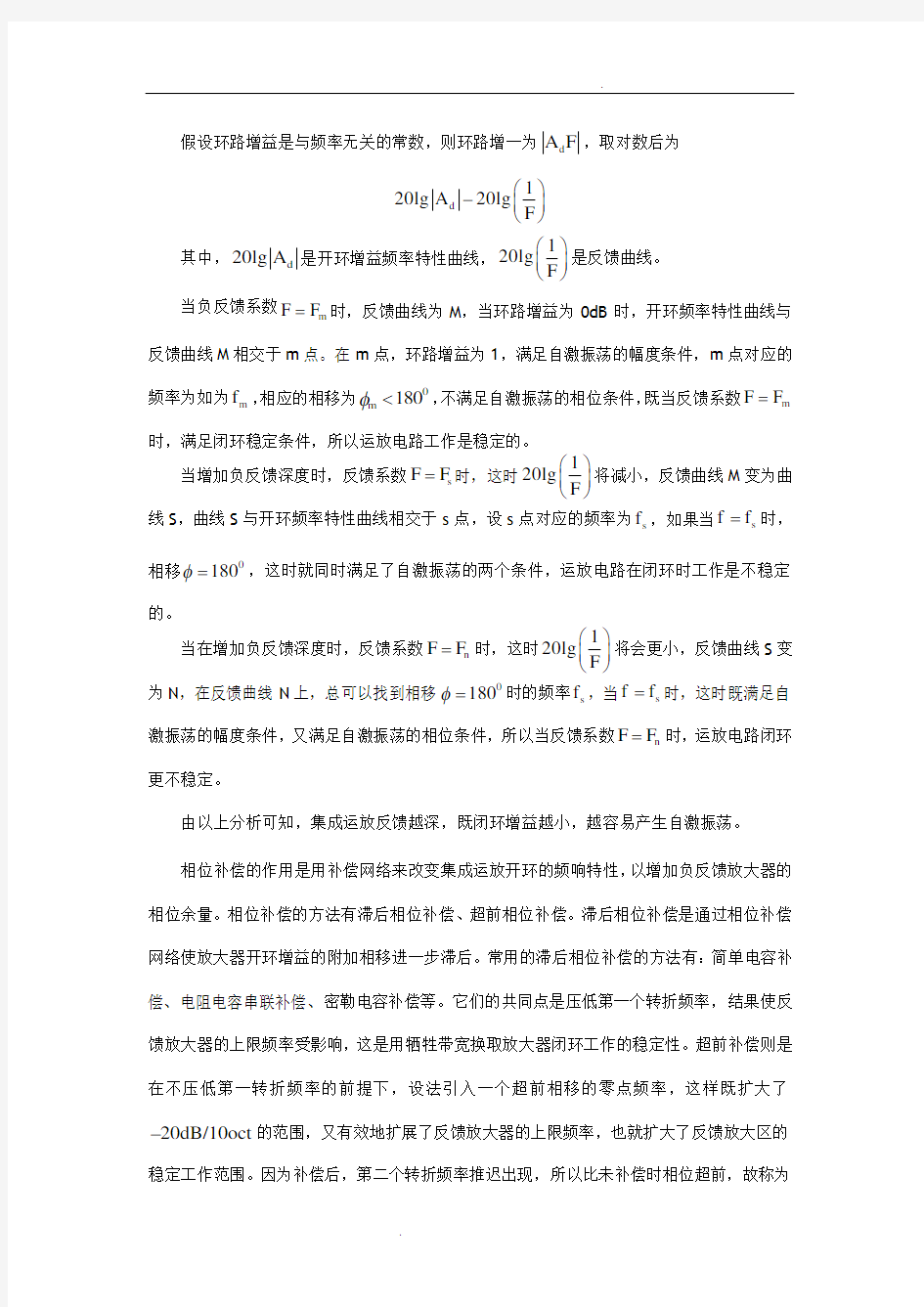

是反馈曲线。 当负反馈系数m F F =时,反馈曲线为M ,当环路增益为0dB 时,开环频率特性曲线与反馈曲线M 相交于m 点。在m 点,环路增益为1,满足自激振荡的幅度条件,m 点对应的频率为如为m f ,相应的相移为0

m 180φ<,不满足自激振荡的相位条件,既当反馈系数m F F =时,满足闭环稳定条件,所以运放电路工作是稳定的。

当增加负反馈深度时,反馈系数s F F =时,这时120lg F ??

???

将减小,反馈曲线M 变为曲线S ,曲线S 与开环频率特性曲线相交于s 点,设s 点对应的频率为s f ,如果当s f f =时,

相移0

180φ=,这时就同时满足了自激振荡的两个条件,运放电路在闭环时工作是不稳定的。

当在增加负反馈深度时,反馈系数n F F =时,这时120lg F ??

???

将会更小,反馈曲线S 变为N ,在反馈曲线N 上,总可以找到相移0

180φ=时的频率s f ,当s f f =时,这时既满足自

激振荡的幅度条件,又满足自激振荡的相位条件,所以当反馈系数n F F =时,运放电路闭环更不稳定。

由以上分析可知,集成运放反馈越深,既闭环增益越小,越容易产生自激振荡。 相位补偿的作用是用补偿网络来改变集成运放开环的频响特性,以增加负反馈放大器的相位余量。相位补偿的方法有滞后相位补偿、超前相位补偿。滞后相位补偿是通过相位补偿网络使放大器开环增益的附加相移进一步滞后。常用的滞后相位补偿的方法有:简单电容补偿、电阻电容串联补偿、密勒电容补偿等。它们的共同点是压低第一个转折频率,结果使反馈放大器的上限频率受影响,这是用牺牲带宽换取放大器闭环工作的稳定性。超前补偿则是在不压低第一转折频率的前提下,设法引入一个超前相移的零点频率,这样既扩大了

20dB/10oct -的范围,又有效地扩展了反馈放大器的上限频率,也就扩大了反馈放大区的

稳定工作范围。因为补偿后,第二个转折频率推迟出现,所以比未补偿时相位超前,故称为

超前补偿。其缺点是不一定能实现单位增益补偿。

2、举例说明(至少三个)集成运放线性应用时如何选择它的技术参数?

A、反相放大器

反相输入放大电路如图2所示,信号电压通过电阻

1

R加至运放的反相输入端,输出电

压

V通过反馈电阻

2

R反馈到运放的反相输入端,构成电压并联负反馈放大电路。

3

R为平衡

电阻应满足

312

//

R R R

=。

图2 基本反相放大器

利用理想集成运放条件:虚短和虚断,即u u

+-

=,

A A

i i

+-

=,可得出此电路的闭环

增益为222

111

o

F

i

U R I R

A

U R I R

-

===-即2

1

F

R

A

R

=-

此电路输入电压与输出电压之间的关系为

2

1

o i

R

u u

R

=-或2

1

o i

R

U U

R

=-

2

1

R

R

-即为反相放大器的放大倍数。

此电路的等效输入电阻为11

1

1

i

ie

i

U R I

R R

I I

===

此电路的等效输出电阻为

1

o

oe

dF

R

R

A

≈

+

在理想条件下,1

dF

A

+很大,

o

R很小,所以0

oe

R≈。

一般

1

R,

2

R取值范围为1K?~1M?,阻值太小,字则输入电阻太低,但大到超出1M?又难以保证阻值的稳定性和精度,所以对于基本反相放大器必须设法提高其输入电阻。

B、积分电路

积分电路是应用非常广泛的一种集成运放电路。它在控制系统中常作为积分环节,在D

/

A变换中用来产生线性度很高的斜坡电压,在F/

U变换器和压控振荡器中用来产生三角波、锯齿波波形,在测量电路中用于实现积分变换,如实现加速度到速度、速度到位移振动信号的变换等。

图3所示为基本反相积分器。当运放为理想集成运放时,分析积分器的以下特性。

图3 基本反相积分器

(1)传输函数

()

()

()()

()()

()

()ST

SRC

R

SC

S

Z

S

Z

S

Z

S

I

S

Z

S

I

S

U

S

U

G

i

o

S

1

1

1

1

2

1

1

2

2-

=

-

=

-

=

-

=

-

=

=

式中,RC

T=,T为积分时间常数。

(2)频率特性

()

RC

j

U

U

j

A

i

o

ω

ω

1

-

=

=

?

?

其中,幅频特性为

()()

ω

ω

ω

ω

ωT

RC

j

G

G=

=

=

1

式中,

RC

T

1

=

ω,

T

ω为幅频特性的交接频率。

相频特性为

()2

π

ω?=

(3)输出电压与输入电压的关系

()()dt t u RC t u i o ?

-

=1

C 、微分电路

微分电路与积分电路互为模拟量间的逆运算、逆变换。微分电路和积分电路一样应用非常广泛,除了在线性系统中做微分运算外,在控制系统中用于实现微分校正,在脉冲数字电路中常用来做波形变换,如将矩形波变为尖顶脉冲波。

图4为基本微分器,在理想运放条件下,微分器的理想积分常数为

()()()

ST SRC S U S U S G i o -=-==

式中,RC T =为微分时间常数。

图4 基本微分器

此微分器的频率特性为

()RC j U U j A i

o

ωω-==

其中,幅频特性为

()()T

RC j G G ωωωωω=

== 式中,RC

T 1

=

ω,T ω为幅频特性的交接频率。 相频特性为

()2

π

ω?-

=

输出电压与输入电压的关系为

()()dt

t du RC

t u i o -= 基本微分器在实际使用中存在稳定性差、高频输入阻抗低、高频干扰大等缺点。 3、阐述抽样数据电路的特点和分析方法。

数据抽样电路是处理抽样信号(时间离散、幅度连续信号)的电路。由于抽样信号是幅度连续信号,常将抽样数据电路归入模拟电路大类。只要满足抽样定理所规定的条件,抽样数据信号可以无失真地复原抽样前的模拟信号,所以用抽样数据电路处理模拟信号时,只要电路特性理想,就不会产生失真。而数据信号是用有限个离散值逼近连续值,因而它不可能无失真地复原数字化前的模拟信号,增加字长只能减小误差,但不可能消除,所以用数字电路处理模拟信号,肯定会产生失真。因为抽样数据电路要处理时间离散的抽样信号,所以电路中必含有存储信号的元件和控制电路工作的时钟,对存储信号的精度和时钟信号参量将影响电路性能。因为抽样数据电路的输入和输出都是抽样信号,它们的频谱按抽样时钟频率的整倍数重复,所以抽样数据电路的频率特性也按抽样时钟频率的整倍数重复。

抽样数据电路目前有三种型式:由电荷耦合器器件(CCD )构成的电路、开关电容电路(SC )和开关电流电路(SI )。在信号处理中得到广泛应用的是开关电容电路和开关电流电路。开关电容电路和开关电流电路的输入输出信号均是离散时间信号,它们的输出输入关系都是用差分方程描述。

在开关电容电路时域分析中,需要使用电荷守恒原理。电荷守恒原理是指在开关电容电路中,用“闭合面”包围各电容器一个极板的集合,只要闭合面内没有存储电荷的元件,并且没有导电路径穿过这个“闭合面”,那么闭合面内所有电容器极板上所存储的总电荷就不会发生变化,并且与整个电路中开关的闭合和断开以及电容器上的电压因任何原因而发生的变化无关。

以简单开关电容电路为例,其图为图5,假定电路中的开关和电容器具有理想特性,时钟信号使用两相不重叠时钟,并假定各电容器上的初始电压均为零。

从(n-1)TC 到(n-1/2)TC 时区间,电容器C1两端电压随输入电压变化,电容器C2两端

电压为零。

在(n-1/2)TC 时刻,开关S1断开、S2闭合,利用电荷守恒原理和KVL 计算电容器上电压,选择闭合面为SC ,可得:

时间上标“+”表示开关闭合后电容器上的电压值,时间上标“-”表示开关闭合前电容器上的电压值。

图5 简单开关电容电路

根据KVL ,可得()()121/21/2+

+

-=-????????C C C C V n T V n T 可得该时刻电容器C2上的电压为

()()()11

21222

1/21/21/211+

---=

-+-????????????++C C C C C C C C V n T V n T V n T C C C C

假定()21/20-

-=????C C V n T ,所以有()()1

212

1/21/21+

--=-?

???????+C C C C C V n T V n T C C

从()1/2-C n T 到C nT 区间,电容器C1和C2上的电压均保持()1/2+

-????C n T 时刻的值。至此,电路完成了一个时钟周期工作,此后在每个时钟周期内,都将重复上述工作过程,

只是电容器上电压的数值将不断变化。因为

()[]

221+-

-=????C C C C V n T V nT

()()2211-

+

-=-????????

C C C C V n T V n T

可得一个时钟周期内输出与输入电压的关系

[]()()21

22122

11/211-

-=-????????++C C C C C C C C V nT V n T V n T C C C C

图6为基本开关电流电路,其中(a )为电路图,(b )为工作波形。

(a )

(b)

图6 基本开关电流电路

在()1C n T -时刻,S1闭合,S2断开,则

()()011D C i C i n T I i n T -=+-????????

在()1/2C n T -时刻,S2闭合,S1断开,则

()()001/21/2C D C i n T I i n T -=--????????

因栅源电容的保持作用()()1/21D C D C i n T i n T -=-???????? 可得()()01/21C i C i n T i n T -=--????????

该式表明,在()1/2C n T -时刻输出电流值比()1C n T -时刻输入电流值延时了1/2时钟周期,并反相。此后,在每个时钟周期将重复上述过程。

4、运用运算仿真法设计二阶以上的有源滤波器并进行仿真分析。

用运算仿真法设计一个低通滤波器,其3dB 带宽为1KHz ,信源阻抗和负载阻抗均为600Ω,在5KHz 处衰减大于60dB 。

log50.7=

0.71007060dB dB dB ?=>

采用巴特沃斯逼近的五阶无源LC 低通滤波器满足给定频率特性的要求,图7所示为其电路图,其频率特性如图8所示,其参数值为

600S L R R ==Ω,15163.9C C nF ==, 24154.5L L mH ==,3530.5C mH

=

图7 LC 低通滤波器

图8 五阶巴特沃斯低通滤波器频率特性

利用KVL 和KCL 可以列出图3所示的电路的状态方程组,表示为

5

S S S

V V I R -=

4

55S i i V SC -= 53

44V V I SL -= 42

33

i i V SC -=

31

22V V I SL -= 211

L

i i V SC -= 1

2

L V I R =

可以看出方程组中每个方程均为一阶积分方程,但它们输入输出变量量纲不同。为减少电路中积分器的类型,需要将它们变换成输出变量和输入变量相同的积分方程,引入参考变量

C R ,变换为输入输出参考变量均为电压的积分方程,通常取C L R R =,定义

'S S L V I R = '44L V I R = '22L

V I R = 'L L L

V I R =

带入上式中,整理可得

()'55451

S L

V V V V SC R =

--

()'4534

L

R V V V SL =

-

()''34231

L

V V V SC R =-

()

'2312

L R

V V V SL =-

()'12111L

V V V SC R =- 满足此方程组数学关系的信号流图如图9所示。

图9 信号流程图

用有源电路实现图9的信号流图,电路如图10所示,在不考虑滤波器动态范围的情况下,所有电阻均取600?,则

15163.9C C nF

==

222429.2L L

C nF

R ==

3530.5C nF

=

442429.2L

L

C nF

R ==

图10 运放实现的有源滤波器

为调整动态范围,需要计算各积分器输出处的峰值,图11为不同频率下各积分器的输出幅度。图中各积分器的最大输出幅度为

1

500.8

M

V mV

=,

2

536.2

M

V mV

=,

3

640.6

M

V mV

=,

4

826.7

M

V mV

=,

5

973.2

M

V mV

=

图11 调整增益前各积分器的输出幅度

为了使整个滤波器动态范围最大,需要调整各支路增益,使各支路增益输出幅度的峰值相等。具体方法是,若原连接第j 个积分器的输出和第i个积分器的输入之间的支路增益为K ij,需要调整为()

/

j i ij

P P K,P j为第j 个积分器输出节点处的峰值,P i为第i个积分器输出节点处的峰值。信号输入支路增益的处理规则是用输出节点的峰值与对输入信号进行积分的积分器的峰值比调整。所以

1

5

308.8

M

S L

M

V

R R

V

==Ω

5

54

4

706.3

M

L

M

V

R R

V

==Ω

4

45

5

509.7

M

L

M

V

R R

V

==Ω

3

34

4

464.9

M

L

M

V

R R

V

==Ω

4

43

3

774.3

M

L

M

V

R R

V

==Ω

3

32

2

716.8

M

L

M

V

R R

V

==Ω

2

23

3

502.2

M

L

M

V

R R

V

==Ω

1

12

2

560.4

M

L

M

V

R R

V

==Ω

2

21

1

642.4

M

L

M

V

R R

V

==Ω

调整各支路增益后,使动态范围扩大。调整后的电路图如图12所示。各积分器输出随频率变化如图13所示。可以看出,调整后各积分器输出的最大幅度均相同。

图12 调整各支路增益后电路图

图13 调整增益后各积分器输出幅度

对调整好的五阶有源巴特沃斯低通滤波器进行小信号分析,如图14所示。分析可以看出在截止频率1KHz处,刚好是-3dB点。

图14 交流小信号分析

图15 5KHz处的衰减

由图15可以看出在5KHz处衰减为70dB,大于60dB,满足设计要求。

集成电路原理及应用(第2版)谭博学苗汇静主编 课后习题答案 第二章 模拟集成电路的线性应用 对 A 2 :由"虚断”和"虚短”得 i 3=i 4, v 2_=v 2 - =u i2, 代入 U o1 得U 。哙呱…), 2.11 求图3所示电路的增益A f ,并说明该电路完成什么功能 则 u i1 = U 01 R 1 R 2 R 2 R 1 ,即 u o-(1 K )u i1 , 则 U 。1 -U i2 R 3 U i2 -U o R 4 R 3 因两个输入信号均从同相端输入, 所以输入阻抗比较高。该电路为高输入阻抗的差动放 2.9 试分析图1所示电路是什么电路,有何特点?图中设 解:第一级运放为同相放大器。对 A 1 :由"虚断”和"虚短”得 i 1 =i 2, v^=v 1. =u , 1)U i2 - U o1

解:该电路由两个集成运放构成, A1为主放大器接成反相运算放大器, A2为辅助放大器, A2也接成反相放大器,利用 A2对A1构成正反馈,是整个电路向信号源索取的电流极少。 主放大器A 1 :由“虚断”和“虚短”得 R i U i I i u i 01 u 。 R 2 R i R 2 u i u i 辅助放大器A2的电压放大倍数: o2 u o2 2R 1 该电路为自举电路, U i U i U i R i I i I i - I R 2 R 2 U i U i u i2 u 。 R 2 目的是提高电路的输入电阻。 2R 得 U^2U i RR

当 R = R 1 时,R t 2.12 求图4所示电路输出电压与输入电压的表达式,并说明该电路完成什么 功能 i1 -u o1 ,即u o1 =-u i1 。A 1为倒相器 解:对A 1 :由

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚图

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院

一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系:

转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

电子科技大学 实验报告 二、实验项目名称:CMOS模拟集成电路设计与仿真 三、实验地点:211大楼606房间 四、实验学时:4 五、实验目的: (1)综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。 (2)学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证 六、实验原理: IC设计一般规则: ①根据用途要求,确定系统总体方案 ②根据电路的指标和工作条件,确定电路结构与类型,然后通过模拟计算, 决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。 ③根据电路特点选择适当的工艺,再按电路中各器件的参数要求,确定满足 这些参数的工艺参数、工艺流程和工艺条件。 ④按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一 定的规则布置在硅片上,绘制出相互套合的版图,以供制作各次光刻掩模版用。 ⑤生成PG带制作掩模版 ⑥工艺流片 ⑦测试,划片封装

实验模拟基于Cadence 平台的电路设计与仿真 七、实验内容: 1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。 2、设计一个运算放大器电路,要求其增益大于60dB, 相位裕度大于45o, 功耗小于10mW。 3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans 分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。 5、电路性能的优化与器件参数调试,要求达到预定的技术指标。 6、整理仿真数据与曲线图表,撰写并提交实验报告。 八、实验仪器与器材 (1)工作站或微机终端一台 (2)EDA仿真软件 1套 九、实验结果: 1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。 2、根据设计指标要求,设计出如下图所示的电路结构。并进行计算分析,确定其中各器件的参数。 4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分 ①增益与频率之间的关系、相位裕度与频率之间关系图如下所示: ②输入、输出关系曲线 十、实验结果计算与分析: 从幅频特性曲线图像中可以读出,电路的增益A V=59dB略小于设计所要求的60dB;找出增益接近于0时候的截止频率为102.4MHz,对应到下方相频特性曲线图像中为-130o,则相位裕度为180o-130o=50o,

家电检修技术<资料版>2007第7期总页(?? 初 学者天地 压从0V 逐渐升高,刚开始可看到两个万用表的数 值都上升,当电压增高到某一值时,可以看到表1的电压值在增大,而表2的电流值却在减小,当电压继续增大到另一个值时,这时又可以看到两个表的电压、电流值都开始增大。如果测试过程与上述的一样,说明该管是好的。如果不一样或变化很不明显,表明该管是坏的。 (完 TD 表1 5V 表2 10mA 20k 图11(b 判断隧道二极管测试电路 功率放大集成电路原理及应用 !丁朋 要点提示: ▲功率放大集成电路的功能是对音频信号进行功率放大,其最大特点是具有较大的输出功率,能够推动扬声器等负载。

▲功率放大集成电路的主要参数有:电源电压、静态电流、输出功率、电压增益、频响范围和谐波失真等。▲O TL 电路的优点是可以使用单电源,缺点是由于输出电容的存在,低频响应较差。 一、功能与参数 1.功能与特点 功率放大集成电路的功能是对音频信号进行功率放大。其最大特点是:具有较大的输出功率,能够推动扬声器等负载。 功率放大集成电路品种规格众多。按声道数可分为单声道音频功放和双声道音频功放;按电路形式可分为O TL 功率放大器、O CL 功率放大器和BTL 功率放大器等。其输出功率从数十毫瓦到数百瓦,具有很多规格,并具有多种封装形式。许多功率放大集成电路自带散热板,但由于自带的散热板一般较小,因此功率较大的功率放大集成电路在应用时仍应按要求安装散热器。功率放大集成电路自带的散热板有的与内部电路绝缘,有的与内部电路的接地点连通,有的与内部输出功放管集电极连通,安装散热器时应区别对待。对于自带散热板与内部电路不绝缘的功率放大集成电路,应在集成电路与散热器之间放置耐热绝缘垫片,如图1所示。 2.参数 功率放大集成电路的主要参数有:电源电压V CC 、静态电流I O 、输出功率P O 、电压增益、频响范围和谐波失真THD 等。 (1电源电压V CC ,包括最高电源电压和额定电源 电压,对于O TL 功率放大器一般为单电源(+V CC ,对于 O CL 功率放大器一般为双电源(±V CC 。最高电源电压是极限参数,使用中不得超过,推荐使用额定电源电压。

集成电路原理及应用(第3版) 谭博学 苗汇静 主编 课后习题答案 第二章 模拟集成电路的线性应用 2.9 试分析图1所示电路是什么电路,有何特点?图中设 3 4 21R R R R =。 (图1) 解:第一级运放为同相放大器。对A 1:由“虚断”和“虚短”得 i 1=i 2,v -1=v +1=u 1i , 则u 1i = 1211R R R u o +,即11 21)1(i o u R R u +=, 对A 2:由“虚断”和“虚短”得 i 3=i 4,v -2=v +2=u 2i , 则 4 2321R u u R u u o i i o -=-,即1342 34)1(o i o u R R u R R u -+= 代入u 1o 得))(1( 123 4 i i o u u R R u -+=, 因两个输入信号均从同相端输入,所以输入阻抗比较高。该电路为高输入阻抗的差动放大器。 2.11 求图3所示电路的增益A f ,并说明该电路完成什么功能。

解:该电路由两个集成运放构成,A1为主放大器接成反相运算放大器,A2为辅助放大器,A2也接成反相放大器,利用A2对A1构成正反馈,是整个电路向信号源索取的电流极少。 主放大器A 1:由“虚断”和“虚短”得 2 1R u R u o i -= ,则A f =121o o i i u u R u u R ===- 辅助放大器A2的电压放大倍数:221222 2o o VF i o u u R A u u R = ==- 该电路为自举电路,目的是提高电路的输入电阻。 由1i i i i U U R I I I = = - 由 12i o U U R R =-和321 2o U U R R =-得32i U U = 所以 1i i i U U I R R = - 因此1 1 i i i U RR R I R R = = - 当1R R =时,i R →∞,1I I = 2.12 求图4所示电路输出电压与输入电压的表达式,并说明该电路完成什么功能。

实验报告

一、实验名称:集成电路版图识别与提取 二、实验学时:4 三、实验原理 本实验重点放在版图识别、电路拓扑提取、电路功能分析三大模块, 1、仔细观察芯片图形总体的布局布线,找出电源线、地线、输入端、 输出端及其对应的压焊点。 2、判定此IC采用P阱还是N阱工艺;进行版图中元器件的辨认, 要求分出MOS管、多晶硅电阻和MOS电容。 3、根据以上的判别依据,提取芯片上图形所表示的电路连接拓扑结

构;复查,加以修正;完成电路的提取,并分析电路功能,应用Visio 或Cadence等软件对电路进行复原。 六、实验仪器设备 (1)工作站或微机终端 1台 (2)芯片显微图片 1张 图1 1、观察芯片布局明确V DD、GND、V in1、V in 2、V out、Test的压焊点。 2、根据V DD连接的有源区可以判断为PMOS管,根据比较环数推测出 此IC采用了P阱工艺。

3、确定P阱工艺后,从输入端开始逐一对元器件及其连线进行辨认。从输入端出来,直接看到在输入压焊点到输入管之间有一段多晶硅,但又无连线的“交叉”出现,排除了“过桥”的可能,初步判断为电阻,再根据其后的二极管可以判定为是与二极管组成保护电路最终与输入管相接,可断定是输入端起限流作用的电阻。其中绿色圈标识有大片的多晶硅覆盖扩散区的区域判断为MOS电容。

图2 2、可见,实验图片为一个采用CMOS P阱工艺制造的放大器电路,该电路为典型的差分放大输入级。由电路图可以看出,器件连接方式正确,逻辑上能完成确定的功能,说明提取结果是正确的。 3、整个实验过程是对IC逆向设计的尝试,IC逆向设计是IC设计的一条关键技术之一,一方面可借鉴并消化吸收先进、富有创意的版图 步提取; 由将二者提取的电路结合所学知识修改、完善,并最终确定电路; 由用Cadence 软件搭建出所提取的电路,并完善布局; 最后,由二者共同完成该实验报告。

1、课程代码 0700559 2、课程名称 集成电路原理及应用 Integrated Circuit Principle and Application 3、授课对象 电子科学与技术专业 4、学分 3 5、修读期 第七学期 6、课程组负责人 主讲教师:刘威、讲师、硕士 7、课程简介 《集成电路设计与应用》是电子科技的一门应用课程,也是进入物理学其它学科学习的先导课程。本课程内容包括集成电路发展历史、集成电路器件原理与模型、反相器的原理、反相器的功耗与延迟分析和模拟、集成电路的基本逻辑门原理、逻辑门的功耗和延迟分析及优化、集成电路的寄生效应、时序集成电路的分析和设计、加法器模块设计、移位器模块设计、存储器模块的设计和优化、模拟电路模块的设计和优化。除了课程讲授之外,还安排了上机时间进行集成电路的模拟实验。学习利用软件模拟合设计集成电路,以及对其进行分析。 通过对本课程的学习,使学生不仅掌握集成电路的设计原理,还能运用自己动手设计集成电路,并能对其性能进行分析和优化。为进行相关工作较好的基础。 8、实践环节学时与内容或辅助学习活动 上机时间课6 学时,利用软件Hspice 和Tannar pro 设计集成电路,并对其功耗、延迟进行分析。 9、课程考核 平时成绩、上机成绩、期末成绩、 10、指定教材 《半导体集成电路》朱正涌编著,张开华主审,清华大学出版杜2001年,高等学校工科电子类规划教材11、参考书目 11、参考书目 《数字集成电路》, 2ndEdition.Rabaey et. al. 2002 Berkeley 《数字集成电路分析与设计》,3rdEdition.David et.al.2005 Berkeley 《模拟CMOS集成电路设计》,Razavi. 2001 Stanford 12、网上资源

1.什么是差动放大电路?什么是差模信号?什么是共模信号?差动放大器对差模信号和共模信 号分别起什么作用? 差动放大电路是把两个输入信号分别输入到运算放大器的同相和反相输入端,然后在输出端取出两个信号的差模成分,而尽量抑制两个信号的共模成分的电路。 共模信号:双端输入时,两个大小相同,极性相同的信号。 差模信号:双端输入时,两个大小相等,极性相反的信号。 对差模输入信号的放大作用、对共模输入信号的抑制作用 2.集成运放有哪几部分组成?各部分的典型电路分别是什么? 输入级、中间级、输出级、偏置电路四大部分组成 输入级的典型电路是差动放大电路, 利用它的电路对称性可提高整个电路的性能,减小温漂; 中间级的典型电路是电平位移电路, 将电平移动到地电平,满足零输入时零输出的要求; 输出级的典型电路是互补推挽输出放大电路,使输出级输出以零电平为中心,并能与中间电压放大级和负载进行匹配; 偏置电路典型电路是电流源电路,给各级电路提供合适的静态工作点、所需的电压 3.共模抑制比的定义? 集成运放工作于线性区时,其差模电压增益Aud与共模电压增益Auc之比 4.集成运放的主要直流参数: 输入失调电压Uos、输入失调电压的温度系数△Uos/△T、输入偏置电流、输入失调电流、差模开环直流电压增益、共模抑制比、电源电压抑制比、输出峰--峰电压、最大共模输入电压、最大差模输入电压 5.集成运放主要交流参数: 开环带宽、单位增益带宽、转换速率、全功率带宽、建立时间、等效输入噪声电压、差模输入阻抗、共模输入阻抗、输出阻抗。 6.理想集成运放的基本条件。 1.差模电压增益为无穷大 2.输入电阻为无穷大 3.输出电阻为0 4.共模抑制比CMRR为无穷大 5.转换速率为无穷大即Sr=00 6.具有无限宽的频带 7.失调电压·失调电流极其温漂均为0 8. 干扰和噪声均为0 7.理想集成运放的两个基本特性:虚短和虚断。代表的实际物理意义。 其实,虚短和虚断的原因只有一个,那就是:输入端输入电阻无穷大。 虚短:集成运放两输入端的电位相等。 集成运放的两个输入端好像短路,但不是真正的短路,所以成为虚短,只有集成运放工作于线性状态时,才存在虚短 虚断:集成运放两输入端的输入电流为零。 由于集成运放输入电阻为无穷大,不可能吸收任何电流,就像输入端被剪断了,跟断路了一样。但是绝对不是真的断路,这大概就是虚断的由来。 1. 集成运放的线性电路包含哪些?非线性电路又包含哪些? 线性电路包括:模拟集成电路的基本放大电路(反相放大器,同相放大器,差动放大器)积分电路,微分电路。 非线性电路包括:对数器和指数器,乘法器,二极管检波器和绝对值变换器,限幅器,二极管函数变换器,电压比较器

模拟CMOS集成电路实验报告 专业: 班级: 姓名: 学号:

实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验要求 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、原理图

2、幅频特性曲线 3、相频特性曲线

四、实验结果分析 器件参数: NMOS管的宽长比为10,栅源之间所接电容1pF,Rd=10K。 实验结果: 输入交流电源电压为1V,所得增益为12dB。 由仿真结果有:gm=496u,R=10k,所以增益Av=496*10/1000=4.96=13.91 dB 可见,实际增益大于理论增益。 补充:电阻改为1k后 实验二:差分放大器设计 一、实验目的 1.掌握差分放大器的设计方法; 2.掌握差分放大器的调试与性能指标的测试方法。

二、实验要求 1. 确定放大电路;2.确定静态工作点Q ; 3.确定电路其他参数。 4.电压放大倍数大于20dB ,尽量增大GBW ,设计差分放大器; 5.对所设计电路调试; 6.对电路性能指标进行测试仿真,并对测量结果进行验算和误差分析。 三、实验原理 平衡态下的小信号差动电压增益A V 为: β1= β2= β=μn C OX (W/L) 四、实验结果 W/L R 5 10 20 30 20K 14.3dB 15.6dB 16.8dB 17.3dB 30K 16.8dB 19dB 20.2dB 20.8dB 40K 20.1dB 20.9dB 21.7dB 22.4dB R 的增加,增益也增加。但从仿真特性曲线我们可以知道,这会限制带宽的特性,W/L 增大时,带宽会下降。为保证带宽, 选取W/L=5,R=40K 的情况下的数值,带宽约为1.18G ,可以符合系统的功能特性,实验结果见下图。 SS V SS D D I A =βI R =2β()R 2

1 《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容Cin为__ CF(1-A) __。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 11、1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,VGS=VTH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当VGS 集成电路芯片的原理及其应用 摘要: 基于分组网络的电路仿真服务在分组网络上提供了一种传输传统电路交换业务的方法,对于现代网络融合具有重要意义。为了实现分组网络中的E1信号传送,提出一种分组电路仿真处理芯片的实现方案,并完成了芯片设计及应用试验。芯片实施协议符合IETF(internet engineeringtask force)PWE3(pseudo wire emulation edge-to-edge)工作组的相关建议草案,芯片内部集成全数字自适应时钟提取算法和服务恢复策略。目前基于该芯片方案的验证系统已经通过了10~100Mb以太网和802.11a无线网络的环境测试。结果表明:该实现方案能够有效抑制分组网络传输抖动和传输误码导致的服务失效,可以应用于多种网络环境。 当前数据业务已经逐渐超过了传统的时分复用(time division multiplexing,TDM)业务,在网络中占据了主导地位;数据分组传送技术也已经取代电路交换技术成为建设下一代网络的主要技术方案。分组电路仿真提供了一种可行的网络融合和过渡方案,它可以在分组交换网上透明传输具有恒定速率的TDM数据流,利用分组交换网来提供传统的时分复用业务。 CESoP技术的标准化工作已经在多个标准化组织中进行。其中,IETF制定的边缘到边缘的伪线仿真技术得到了较为广泛的应用。目前,RAD公司已经开发出IPmux系列电路仿真设备;Zarlink公司已经开发出了分组电路仿真业务处理器芯片。 本文提出一种CESoP芯片实现方案,其处理协议符合IETF PWE3工作组关于CESoPSN(circuitemulation setvice overpacket:switched networks)的建议草案,相比其他芯片具有以下优点:内部集成自适应定时恢复算法,无须外部处理器干预;采用全数字的恢复算法,可以方便地实现系统集成;片内实现基于差错掩蔽的服务恢复策略,可以有效地抑制由于数据分组丢失造成的TDM设备故障;采用片外SDRAM(synchrono-us dynamic randomaccess memory)存储器可以实现最多256 ms的抖动抑制时间。 1. 芯片方案结构 芯片主要由以太网媒体访问控制单元、协议处理单元、队列管理单元、队列仲裁单元、时隙分配单元、时隙提取单元、共享存储管理单元、SDRAM控制单元、E1处理单元、E1接口单元以及微处理器接口单元等构成,1)上行TDM数据流。 由E1接口至MII(media independentinterface)接口,来自E1接口的TDM数据进行线路解码,通过E1处理单元完成数据定帧和时钟提取,再通过时隙提取单元取出需要传送的有效时隙和信令,并通过共享存储管理单元保存到外部存储器中,队列仲裁单元根据E1队列优先级通过共享存储管理单元从外部存储器中读出相应的E1数据并将其发送到协议处理单元,其根据设定的协议格式将TDM数据封装到以太网数据帧中,数据帧通过以太网媒体访问控制(media access control,MAC)处理单元最终被发送到以太网MII接口。 下行TDM数据流,由MII接口至E1接口,到达目的地的以太网数据帧经过MAC处理单元和协议处理单元处理,提取出有效的E1数据分组并将其通过共享存储管理单元保存到外部存储器中,队列管理单元对接收到的El数据分组进行缓存管理、重排序、抖动平滑、差错掩蔽等处理,时隙分配单元根据输出E1接口的情况,通过共享存储管理单元从外部存储器中读出相应的E1数据,重新生成E1数据帧,然后发送到E1处理单元进行时钟恢复和编码处理,最后形成标准格式的E1数据帧发送到E1接口。 上行MCU数据流,由MCU接口至MII接口,外部微处理器通过MCU接口将控制数据分组 电科《集成电路原理》期末考试试卷 一、填空题 1.(1分) 年,第一次观测到了具有放大作用的晶体管。 2 . ( 2 分 ) 摩 尔 定 律 是 指 。 3. 集 成 电 路 按 工 作 原 理 来 分 可 分 为 、 、 。 4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。 5. ( 4 分 ) MOSFET 可 以 分 为 、 、 、 四种基本类型。 6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。 7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。 8.(2分)CMOS 逻辑电路的功耗可以分为 和 。 9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。 DD 1 3 2 10.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。 A B Y 1 A B 2 3 二、画图题:(共12分) =+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD MOS管最少。 2.(6分)用动态电路级联实现逻辑功能Y ABC =,画出其相应的电路图。 三、简答题:(每小题5分,共20分) 1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么? 2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么? 555定时电路内部结构分析及应用 1 绪言 555定时器是电子工程领域中广泛使用的一种中规模集成电路,它将模拟与逻辑功能巧妙地组合在一起,具有结构简单、使用电压范围宽、工作速度快、定时精度高、驱动能力强等优点。555定时器配以外部元件,可以构成多种实际应用电路。广泛应用于产生多种波形的脉冲振荡器、检测电路、自动控制电路、家用电器以及通信产品等电子设备中。 2555定时器功能及结构分析 2.1 555定时器的分类及管脚作用 555定时器又称时基电路。555定时器按照内部元件分有双极型(又称TTL型)和单极型两种。双极型内部采用的是晶体管;单极型内部采用的则是场效应管,常见的555时基集成电路为塑料双列直插式封装(见图2-1),正面印有555字样,左下角为脚①,管脚号按逆时针方向排列。 2-1 555时基集成电路各管脚排布 555时基集成电路各管脚的作用:脚①是公共地端为负极;脚②为低触发端TR,低于1/3电源电压以下时即导通;脚③是输出端V,电流可达2000mA;脚④是强制复位端MR,不用可与电源正极相连或悬空;脚⑤是用来调节比较器的基准电压,简称控制端VC,不用时可悬空,或通过0.01μF电容器接地;脚⑥为高触发端TH,也称阈值端,高于2/3电源电压发上时即截止;脚⑦是放电端DIS;脚⑧是电源正极VC。 2.2 555定时器的电路组成 图2-2为555芯片的内部等效电路 2-2 555定时器电路组成 5G555定时器内部电路如图所示,一般由分压器、比较器、触发器和开关。及输出等四部分组成,这里我们主要介绍RS触发器和电压比较器。 2.2.1基本RS触发器原理 如图2-3是由两个“与非”门构成的基本R-S触发器, RD、SD是两个输入端,Q及是两个输出端。 2-3 RS触发器 正常工作时,触发器的Q和应保持相反,因而触发器具有两个稳定状态: 1)Q=1,=0。通常将Q端作为触发器的状态。若Q端处于高电平,就说触发器是1状态;2)Q=0,=1。Q端处于低电平,就说触发器是0状态;Q端称为触发器的原端或1端,端称为触发器的非端或0端。 由图可看出,如果Q端的初始状态设为1,RD、SD端都作用于高电平(逻辑1),则一定为0。如果RD、SD状态不变,则Q及的状态也不会改变。这是一个稳定状态;同理,若触发器的初始状态Q为0而为1,在RD、SD为1的情况下这种状态也不会改变。这又是一个稳定状态。可见,它具有两个稳定状态。 输入与输出之间的逻辑关系可以用真值表来描述。 首先对该RS触发器Q端状态仿真。如图2-4 2-4 RS触发器Q端仿真电路图 Q端状态变化规律如图2-5 2-5 Q端状态变化规律仿真 此图中A即SD,B即RD.,再对该R—S触发器Q非端状态仿真,如图2-6 2-6 RS触发器Q非端仿真图 Q非端状态变化规律如图2-7 2-7 Q非端状态变化规律 此图中A即SD,B即RD. R-S触发器的逻辑功能,可以用输入、输出之间的逻辑关系构成一个真值表(或叫功能表)来描述,由仿真可得以下结论。当RD =0,SD=1时,不论触发器的初始状态如何,一定为1,由于“与非”门的输入全是1,Q端应为0。称触发器为0状态,RD为置0端。 电子科技大学学院 (微电子技术系) 实验报告书 课程名称:芯片解剖实验 学号: 姓名: 教师: 年6月28日 实验一去塑胶芯片的封装 实验时间:同组人员: 一、实验目的 1.了解集成电路封装知识,集成电路封装类型。 2.了解集成电路工艺流程。 3.掌握化学去封装的方法。 二、实验仪器设备 1:烧杯,镊子,电炉。 2:发烟硝酸,弄硫酸,芯片。 3:超纯水等其他设备。 三、实验原理和容 实验原理: 1..传统封装:塑料封装、瓷封装 (1)塑料封装(环氧树脂聚合物) 双列直插DIP、单列直插SIP、双列表面安装式封装SOP、四边形扁平封装QFP 具有J型管脚的塑料电极芯片载体PLCC、小外形J引线塑料封装SOJ (2)瓷封装 具有气密性好,高可靠性或者大功率 A.耐熔瓷(三氧化二铝和适当玻璃浆料):针栅阵列PGA、瓷扁平封装FPG B.薄层瓷:无引线瓷封装LCCC 2..集成电路工艺 (1)标准双极性工艺 (2)CMOS工艺 (3)BiCMOS工艺 3.去封装 1.瓷封装 一般用刀片划开。 2. 塑料封装 化学方法腐蚀,沸煮。 (1)发烟硝酸煮(小火)20~30分钟 (2)浓硫酸沸煮30~50分钟 实验容: 去塑胶芯片的封装 四、实验步骤 1.打开抽风柜电源,打开抽风柜。 2.将要去封装的芯片(去掉引脚)放入有柄石英烧杯中。 3.带上塑胶手套,在药品台上去浓硝酸。向石英烧杯中注入适量浓硝酸。(操作时一定注意安全) 4.将石英烧杯放到电炉上加热,记录加热时间。(注意:火不要太大) 5.观察烧杯中的变化,并做好记录。 6.取出去封装的芯片并清洗芯片,在显微镜下观察腐蚀效果。 7.等完成腐蚀后,对废液进行处理。 西安邮电学院电子工程学院 本科集成电路设计与集成系统专业培养方案 学科:工学---电气信息专业:集成电路设计与集成系统(Engineering---Electric Information)(Integrated Circuit Design & Integrated System)专业代码:080615w 授予学位:工学学士 一、专业培养指导思想 遵循党和国家的教育方针,体现“两化融合”的时代精神,把握高等教育教学改革发展的规律与趋势,树立现代教育思想与观念,结合社会需求和学校实际,按照“打好基础、加强实践,拓宽专业、优化课程、提高能力”的原则,适应社会主义现代化建设和信息领域发展需要,德、智、体、美全面发展,具有良好的道德修养、科学文化素质、创新精神、敬业精神、社会责任感以及坚实的数理基础、外语能力和电子技术应用能力,系统地掌握专业领域的基本理论和基本知识,受到严格的科学实验训练和科学研究训练,能够在集成电路设计与集成系统领域,特别是通信专用集成电路与系统领域从事科学研究、产品开发、教学和管理等方面工作的高素质应用型人才。 二、专业培养目标 本专业学生的知识、能力、素质主要有:①较宽厚的自然科学理论基础知识、电路与系统的学科专业知识、必要的人文社会学科知识和良好的外语基础;②较强的集成电路设计和技术创新能力,具有通信、计算机、信号处理等相关学科领域的系统知识及其综合运用知识解决问题的能力;③较强的科学研究和工程实践能力,总结实践经验发现新知识的能力,掌握电子设计自动化(EDA)工具的应用;④掌握资料查询的基本方法和撰写科学论文的能力,了解本专业领域的理论前沿和发展动态;⑤良好的与人沟通和交流的能力,协同工作与组织能力;⑥良好的思想道德修养、职业素养、身心素质。毕业学生能够从事通信集成电路设计与集成系统的设计、开发、应用、教学和管理工作,成为具有奉献精神、创新意识和实践能力的高级应用型人才。 三、学制与学分 学制四年,毕业生应修最低学分198学分,其中必修课110学分,限选课36学分,任选课10学分,集中实践环节34学分,课外科技与实践活动8学分。 集成电路原理与设计重点容总结 第一章 绪论 摩尔定律:(P4) 集成度大约是每18个月翻一番或者集成度每三年4倍的增长规律就是世界上公认的摩尔定律。 集成度提高原因: 倍;二是芯片面积不断增大,大约每三年增大1.5倍;三是器件和电路结构的不断改进。 等比例缩小定律:(种类 优缺点)(P7-8) 1.恒定电场等比例缩小规律(简称CE 定律) a.器件的所有尺寸都等比例缩小K 倍,电源电压也要缩小K 倍,衬底掺杂浓度增大K 倍,保证器件部的电场不变。 b.集成度提高K 2倍,速度提高K 倍,功耗降低K 2倍。 c.改变电源电压标准,使用不方便。阈值电压降低,增加了泄漏功耗。 2.恒定电压等比例缩小规律(简称CV 定律) a.保持电源电压和阈值电压不变,器件的所有几何尺寸都缩小K 倍,衬底掺杂浓度增加K 2倍。 b.集成度提高K 2倍,速度提高K 2倍。 c.功耗增大K 倍。部电场强度增大,载流子漂移速度饱和,限制器件驱动电流的增加。 3.准恒定电场等比例缩小规则(QCE) 器件尺寸将缩小K 倍,衬底掺杂浓度增加lK (1 【集成电路技术在医疗健康领域的应用】集成电路原理及应 用 随着社会的发展和科学技术的不断进步,人们对医疗健康、生活质量、疾病护理等方面提出了越来越高的要求。同时,依托于高新领域电子技术的各种治疗和监护手段越来越先进,也使得医疗产品突破了以往观念的约束和限制,在信息化、微型化、实用化等方面得到了长足发展。本文从医疗健康领域的需求分析入手,从集成电路技术的角度对医疗健康领域的应用的关键技术(现状和前景)做了大致的分析探讨。 1医疗健康领域的需求现状 在医疗健康领域,关注的热点正在渐渐从最基本的疾病产业向保健产业转变。这二者都是以健康服务为最终目的,但是前者主要是有针对性的“对症下药”,而后者则更倾向于为一般消费者提供更全面的保健解决方案。 美国著名经济学家保罗?皮尔泽(Paul Zane Pilzer)曾是花旗银行最年轻的副总裁并出任布什、克林顿两任总统的经济顾问,在他的《财富第五波》一书中指出:二十一世纪人类面临严重饮食失衡,却人人希望更健康、抗老化,预防胜于治疗,从而开启保健产业的兆亿商机。这是继第四波网络革命后的明星产业,相比疾病产业的被动性,保健 事业是主动积极的产业。 世界卫生组织(WHO)在xx年10月公开的一份档案中提到:人口 老龄化助长癌症和心脏病病例上升;心血管疾病是全世界主要的死亡 原因,听力丧失、视力问题和精神障碍是最常见的残疾原因。 庞大的老龄化群体和慢性疾病患者等群体的现状(换言之,是社 会需求和市场需求的现状)使得疾病产业、保健产业中亟需发展应用 新的技术和产品。 2.1 世界人口老龄化,对医疗护理产品提出了更高的要求。 随着医疗水平的提高,世界平均人口寿命增加,世界和中国都面 临着人口结构老龄化的问题。如根据 __经济社会部的研究数据(如图1),到2050年世界60岁以上的老年人将达20亿,约占世界总人口的 电子科技大学集成电路原理实验集成电路图识别与提取王向展 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】 实验报告 课程名称:集成电路原理 实验名称:集成电路版图识别与提取 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年5月22日 2017年5月22日 微电子与固体电子学院 一、实验名称:集成电路版图识别与提取 二、实验学时:4 三、实验原理 本实验重点放在版图识别、电路拓扑提取、电路功能分析三大模块,实验流程如下: 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC 设计性实验。其目的在于: 了解对塑封、陶瓷封装等不同封装形式的芯片解剖的方法及注意事项。 学习并掌握集成电路版图的图形识别、电路拓扑结构提取。 能对提取得到的电路进行功能分析、确定,并可运用PSPICE 等ICCAD 工具展开模拟仿真。 五、实验内容 1、仔细观察芯片图形总体的布局布线,找出电源线、地线、输入端、输出端及其对应的压焊点。 2、判定此IC采用P阱还是N阱工艺;进行版图中元器件的辨认,要求分出MOS 管、多晶硅电阻和MOS电容。 3、根据以上的判别依据,提取芯片上图形所表示的电路连接拓扑结构;复查,加以修正;完成电路的提取,并分析电路功能,应用Visio或Cadence等软件对电路进行复原。 六、实验仪器设备 (1)工作站或微机终端 1台 (2)芯片显微图片 1张 (3)版图编辑软件 1套 七、实验步骤 实验所要提取的电路显微图片如图1所示。集成电路芯片的原理及其应用

《集成电路设计原理》试卷及答案

芯片内部原理及经典应用

实验报告芯片解剖实验

集成电路培养方案

《集成电路原理与设计》重点内容总结

【集成电路技术在医疗健康领域的应用】集成电路原理及应用

电子科技大学集成电路原理实验集成电路图识别与提取王向展完整版