实验七 波形产生及单稳态触发器

班级: 姓名: 学号: 实验台: 实验日期: ---------------------------------------------------------------------------------------------------------------------

1-1 一、实验目的

1.熟悉多谐振荡器的电路特点及振荡频率估算方法。

2.掌握单稳态触发器的使用。

二、实验仪器及器件

1.仪器:数字电路学习机,双踪示波器

2.器件:74LS00 二输入四与非门 1片

CD4069 六反相器 1片

三、实验内容

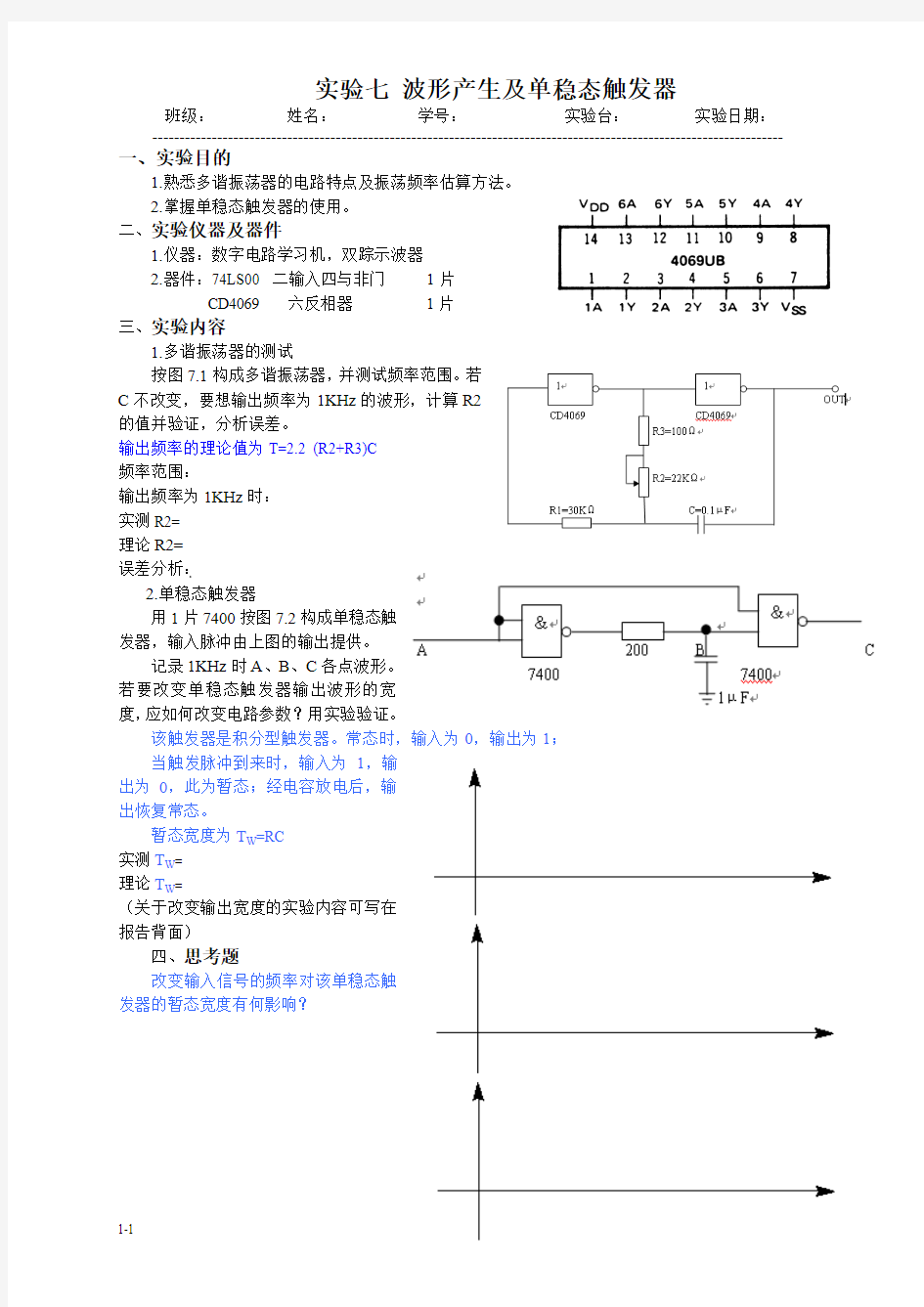

1.多谐振荡器的测试

按图7.1构成多谐振荡器,并测试频率范围。若

C 不改变,要想输出频率为1KHz 的波形,计算R2

的值并验证,分析误差。

输出频率的理论值为T=2.2 (R2+R3)C

频率范围:

输出频率为1KHz 时:

实测R2=

理论R2=

误差分析:

2.单稳态触发器

用1片7400按图7.2构成单稳态触

发器,输入脉冲由上图的输出提供。

记录1KHz 时A 、B 、C 各点波形。

若要改变单稳态触发器输出波形的宽

度,应如何改变电路参数?用实验验证。

该触发器是积分型触发器。常态时,输入为0,输出为1;

当触发脉冲到来时,输入为1,输

出为0,此为暂态;经电容放电后,输

出恢复常态。

暂态宽度为T W =RC

实测T W =

理论T W =

(关于改变输出宽度的实验内容可写在

报告背面)

四、思考题

改变输入信号的频率对该单稳态触

发器的暂态宽度有何影响?

实验七、触发器 一、实验目的 (1)理解触发器的用途、类型和工作原理。 (2)掌握利用T-SQL语句创建和维护触发器的方法。(3)掌握利用SQL Server Management Studio创建、维护触发器的方法。 二、实验内容、 1、创建AFTER触发器 (1)创建一个在插入时触发的触发器sc_insert,当向SC表插入数据时,须确保插入的学号已在Student表中存在,并且还须确保插入课程号在Course表中存在;若不存在,则给出相应的提示信息,并取消插入操作,提示信息要求指明插入信息是学号不满足条件还是课程号不满足条件。(注:Student表与SC表的外键约束要先取消。)

(2)为Course表创建一个触发器Course_del,当删除了Course表中的一条课程信息时,同时将表SC中相应的学生选课记录也删除。 (3)在Course表中添加一个平均成绩avg_modify,当SC表中某学

生的成绩发生变化时,则Course表中的平均成绩也能及时相应发生改变。 (4)测试上述三个触发器。

2、创建INSERTED OF 触发器 (1)创建一视图student_view,包含学号、姓名、课程号、课程名、成绩等属性,在student_view上创建一个触发器grade_modify,当对student_view中的学生的成绩进行修改时,实际修改的是SC中的相应记录。

(2)在Student表中插入一个getcredit字段(记录学生所获学分的情况),创建一个触发器ins_credit,当更改(注:含插入时)SC表中的学生成绩时,如果新成绩大于等于60分,则该生可获得这门课的学分,如果新成绩小于60分,则该生未能获得这门课的学分。 (3)测试上述两个触发器。

单稳态触发器特点: 电路有一个稳态、一个暂稳态。 在外来触发信号作用下,电路由稳态翻转到暂稳态。 暂稳态不能长久保持,由于电路中RC延时环节的作用,经过一段时间后,电路会自动返回到稳态。暂稳态的持续时间取决于RC电路的参数值。 单稳态触发器的这些特点被广泛地应用于脉冲波形的变换与延时中。 一、门电路组成的微分型单稳态触发器 1. 电路组成及工作原理 微分型单稳态触发器可由与非门或或非门电路构成,如下图。与基本RS触发器不同, (a)由与非门构成的微分型单稳态触发器 (b)由或非门构成的微分型单稳态触发 图6.7微分型单稳态触发器 构成单稳态触发器的两个逻辑门是由RC耦合的,由于RC电路为微分电路的形式,故称为微分型单稳态触发器。下面以CMOS或非门构成的单稳态触发器为例,来说明它的工作原理。 ⑴ 没有触发信号时,电路处于一种稳态 没有触发信号时,为低电平。由于门输入端经电阻R接至,因此 为低电平; 的两个输入均为0,故输出为高电平,电容两端的电压接近0V,这是电路的“稳态”。在触发信号到来之前,电路一直处于这个状态:

, 。 ⑵ 外加触发信号,电路由稳态翻转到暂稳态 当时,的输出由1 0,经电容C耦合,使,于是的输出v02 =1, 的高电平接至门的输入端,从而再次瞬间导致如下反馈过程: 这样导通截至在瞬间完成。此时,即使触发信号撤除(), 由于的作用,仍维持低电平。然而,电路的这种状态是不能长久保持的,故称之为暂稳态。暂稳态时, ,。 ⑶ 电容充电,电路由暂稳态自动返回至稳态 在暂稳态期间,电源经电阻R和门的导通工作管对电容C充电,随着充电时 间的增加增加,升高,使时,电路发生下述正反馈过程(设此时触发器脉冲已消失): 迅速截止,很快导通,电路从暂稳态返回稳态。, 。 暂稳态结束后,电容将通过电阻R放电,使C上的电压恢复到稳定状态时的初始值。在整个过程中,电路各点工作波形如图6.8所示。

桂林航天工业学院学生实验报告 实验七 实验名称触发器实验日期2019.11.12 实验目的 1.了解触发器的基本原理,掌握创建触发器的方法。 2.掌握修改和删除触发器的方法,能够设计简单的触发器。 实验内容触发器 实验方法及步骤 1、创建一个触发器InsStud,当向student表插入一条记录时,同时把该记录插入到关系student2。 CREATE TRIGGER InsStud on student FOR INSERT AS insert into student2 select*from inserted 2、向student表中插入一条记录('201215130','张三','男',20,'CS'),查看student和student2表中记录的变化是什么? student和student2表中都能插入('201215130','张三','男',20,'CS')这条记录 insert student values('201215130','张三','男',20,'CS'); select*from student select*from student2 3、创建一个触发器DelStud,当向student表删除一条记录时,同时把该记录从student2表删除掉。

CREATE TRIGGER DelStud on student FOR delete AS delete student2 select*from deleted 4、删除student表中的sno为201215130的元组,同时查看student2表中元组的变化是什么? student和student2表中都能删除('201215130','张三','男',20,'CS')这条记录。 delete student where sno='201215130' select*from student select*from student2 5、为course表创建一个名为del_rollback_tr的DELETE触发器,该触发器的作用是禁止删除course表中的记录。 CREATE TRIGGER del_rollback_tr on course FOR delete AS if (exists(select*from deleted)) rollback insert course values('8','张','5',2); delete course where cno='8'

实验七触发器 文件编码(008-TTIG-UTITD-GKBTT-PUUTI-WYTUI-8256)

实验七触发器 一、实验目的 (1)理解触发器的用途、类型和工作原理 (2)掌握利用T-SQL语句创建和维护触发器的方法 (3)掌握利用企业管理器创建、维护触发器的方法 二、实验内容 1.创建after触发器 (1)创建一个在插入时触发的触发器sc_insert,当向sc表插入数据时,须确保插入的学号已在Student表中存在,并且还须确保插入的课程号在Course表中存在;若不存在,则给出相应的提示信息,并取消插入操作,提示信息要求指明插入信息是学号不满足条件还是课程号不满足条件(注:Student表与sc表的外键约束要先取消)。 create trigger sc_insert on sc after insert as

if not exists(select*from student,inserted where= begin print'插入信息的学号不在学生表中!' if not exists(select*from course,inserted where= print'插入信息的课程号不在课程表中!' rollback end else begin if not exists(select*from course,inserted where= begin print'插入信息的课程号不在课程表中!' rollback end

end 执行: ①、insert into SC values(,'001','78') 删除外键约束: alter table SC drop constraint FK__SC__Sno__182C9B23 ②、insert into SC values(,'001','78') ③、insert into SC values('','006','78') (2)为Course表创建一个触发器Course_del,当删除了Course表中的一条课程信息时,同时将表sc表中相应的学生选课记录删除掉。 create trigger course_del on course after delete

双稳态电路的工作原理 双稳态电路是由什么组成的?他的工作原理是什么? 一、工作原理 图一为双稳态电路,它是由两级反相器组成的正反馈电路,有两个稳定状态,或者是BG1导通、BG2截止;或者是BG1截止、BG2导通,由于它具有记忆功能,所以广泛地用于计数电路、分频电路和控制电路中,原理,图2(a)中,设触发器的初始状态为BG1导通,BG2截止,当触发脉冲方波从1端输入,经CpRp 微分后,在A点产生正、负方向的尖脉冲,而只有正尖脉冲能通过二极管D1作用于导通管BG1的基极是。ic1减小使BG1退出饱和并进入放大状态,于是它的集电极电位降低,经电阻分压器送到截止管BG2的基极,使BG2的基极电位下降,如果下降幅度足够时,BG2将由截止进入放大状态,因而产生下列正反馈过程(看下列反馈过程时,应注意:在图一的PNP电路中,晶体管的基极和集电极电位均为负值,所以uc1↓,表示BG1集电极电位降低,而uc1↑则表示BG1集电极电位升高,当BG1基极电位降低时,则ic1↑,反之当BG1基极电位升高时,ic1↓ ic1越来越小,ic2越来越大,最后到达BG1截止、BG2导通;接差触发脉冲方波从2端输入,并在t=t2时,有正尖脉冲作用于导通管BG2的基极,又经过正反馈过程,使BG1导通,BG2截止。以后,在1、2端的触发脉冲的轮流作用下,双稳电路的状态也作用相应的翻转,如图一(b)所示。 图一、双稳态电路 由上述过程可见:(1)双稳态电路的尖顶触发脉冲极性由晶体管的管型决定:PNP管要求正极性脉冲触发,而NPN管却要求负极性脉冲触发。(2)每触发一次,电路翻转一次,因此,从翻转次数的多少,就可以计算输入脉冲的个数,这就是双稳态电路能够计算的原理。 双稳态电路的触发电路形式有:单边触发、基极触发、集电极触发和控制触发等。 图二给出几种实用的双稳态电路。电路(a)中D3、D4为限幅二极管,使输出幅度限制在-6伏左右;电路(b)中的D5、D6是削去负尖脉冲;电路(C)中的ui1、ui2为单触发,ui为输入触发表一是上述电路的技术指标。 图二、几种实用的双稳态电路 表一几种双稳态触发器的技术指标 图二(a)(b)(c)(d) 管型二极管2AP32AP152AK1C2AK17 三极管3AX31B3AG403AK203DK3B 信号电平“0”(无信号)(V)000+6 “1”(有信号)(V)-6-6-90 工作频率(KHz)1060010008000 抗干扰电压(V)≥1≥1.5≥20.8-1 触发灵敏度(V)≤4≤4.8≤72.5 输出端的吸收能力(mA)≤4≤6.7≤210 输出端的发射能力(mA)≤44≤12≤127 输出脉冲的上升时间(μs)2≤0.30≤0.1≤0.1 输出脉冲的下降时间(μs)2≤0.36≤0.15≤0.1 对β值的要求>5050-8060-90>50 元件参数的允许化△β<10,±5%△β<10,±5%△β<10,±5%△β<10,±5%

555构成的单稳态触发器的四种基本电路 图(a所示电路是典型的单稳模式电路。当外加脉冲经C1、R1微分电路加至555的2脚时,负向脉冲(<1/3VDD使555置位,3脚输出暂稳脉冲宽度td=1.1RC。 图(b与图(a类同,但它有两个输出端。C通过R至555内部灌电流放电,恢复时间比图(a要长。 图(c电路的2、6脚接法与图(a、(b不同,外加触发应为正向脉冲,幅值应大于号VDD,暂稳脉冲 为负向,其宽度td=1.1RC,可同时输出两路。 图(d与图(c类同,但由于在充电回路中加进了导向二极管D,加快了充电速率,使工作频率大大 提高。该电路可同时输出两路。 [日期:2010-02-20]来源:作者:[字体:大中小] 555电路 2008/12/17 15:15 555 集成电路开始出现时是作定时器应用的,所以叫做 555 定时器或555 时基电路。但是后来经过开发,它除了作定时延时控制外,还可以用于调光、调温、调压、调速等多种控制以及计量检测等作用;还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,作为交流信号源以及完成电源变换、频率变换、脉冲调制等用途。由于它工作可靠、使用方便、价格低廉,因此目前被广泛用于各种小家电中。 555 集成电路内部有几十个元器件,有分压器、比较器、触发器、输出管和放电管等,电路比较复杂,是模拟电路和数字电路的混合体。它的性能和参数要在非线性模拟集成电路手册中才能查到。 555 集成电路是 8 脚封装,图 1 ( a )是双列直插型封装,按输入输出的排列可画成图 1 ( b )。其中 6 脚称阀值端( TH ),是上比较器的输入。 2 脚称触发端(),是下比较器的输入。 3 脚是输出端( V O ),它有 0 和 1 两种状态,它的状态是由输入端所加的电平决定的。 7 脚的放电端( DIS ),它是内部放电管的输出,它也有悬空和接地两种状态,也是由输入端的状态决定的。 4 脚是复位端(),加上低电砰(< 0.3 伏)时可使输出成低电平。 5 脚称控制电压端( V C ),可以用它改变上下触发电平值。 8 脚是电源, 1 脚为地端。

数字电路与逻辑设计基础实验 任课教师:陈志坚 实验名称:触发器(实验七) 云南大学信息学院 一、实验目的 ⑴学习触发器逻辑功能的测试方法 ⑵进一步熟悉RS触发器、集成D触发器和JK触发器的逻辑功能及其触发方式二、实验器材 ⑴直流稳压电源、数字逻辑实验箱 ⑵74LS00、74LS74、74LS76 三、实验内容和仿真

1.基本RS触发器 基本RS触发器用与非门74LS00构成,按图7-1接好线。在输入端加上不同的信号,通过发光二极管观察电路输出端的状态。把结果填入自制的表中。 图7-1 基本RS触发器图7-2 D触发器的预置和清零功能 用带预置和清除的双D型触发器74LS74来测试上升沿触发集成D型触发器的逻辑功能。先按图7-2接线,在时钟脉冲的不同电平状态,改变预置端PRE 和清除端CLR的信号,通过发光二极管观察触发器的输出状态。把结果填入自制的表中。然后,按图7-3接线,测试D触发器的逻辑功能。 在D触发器的逻辑功能测试中,先将数据输入端D分别置入“0”或“1”,再用清零端CLR和预置端PRE分别将触发器的输出端清除为“0”或置位为“1”,最后再用单脉冲按钮向触发器的时钟输入端CLK发出脉冲的上升边沿和下降边沿,同时观察电路输出端Q的输出状态,把结果填入表7-1中。 注意:清零和置位之后,清除端CLK和预置端PRE必须置成“1”状态。 图7-3 D触发器逻辑功能测试7-4 JK触发器清除和预置功能的测试

D触发器仿真(1) D触发器仿真(2

1 3.JK触发器 用带预置和清除的双JK触发器74LS76来测试下降沿触发集成JK触发器的逻辑功能。先按图7-4接线,改变预置端PRE和清除端CLR的信号,通过发光二极管观察触发器Q输出端的输出状态。把结果填入自制的表中。然后,按图7-5接线,测试JK触发器的逻辑功能。 图7-5 JK触发器逻辑功能测试

单稳态触发器只有一个稳定状态,在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂态,该暂态维持一段时间又回到原来的稳态。 一、用555定时器构成单稳态触发器: 1.电路组成 如图6-7所示,其中R、C为单稳态触发器的定时元件,它们的连接点Vc与定时器的阀值输入端(6脚)及输出端Vo'(7脚)相连。单稳态触发器输出脉冲宽度tpo=1.1RC。 Ri、Ci构成输入回路的微分环节,用以使输入信号Vi的负脉冲宽度tpi限制在允许的范围内,一般tpi>5RiCi,通过微分环节,可使Vi'的尖脉冲宽度小于单稳态触发器的输出脉冲宽度tpo。若输入信号的负脉冲宽度tpi本来就小于tpo,则微分环节可省略。 定时器复位输入端(4脚)接高电平,控制输入端Vm通过0.01uF接地,定时器输出端Vo(3脚)作为单稳态触发器的单稳信号输出端。 2.工作原理 当输入Vi保持高电平时,Ci相当于断开。输入Vi'由于Ri的存在而为高电平Vcc。此时,①若定时器原始状态为0,则集电极输出(7脚)导通接地,使电容C放电、Vc=0,即输入6脚的信号低于2/3Vcc,此时定时器维持0不变。 ②若定时器原始状态为1,则集电极输出(7脚)对地断开,Vcc经R向C充电,使Vc电位升高,待Vc值高于2/3Vcc时,定时器翻转为0态。 结论:单稳态触发器正常工作时,若未加输入负脉冲,即Vi保持高电平,则单稳态触发器的输出Vo一定是低电平。 单稳态触发器的工作过程分为下面三个阶段来分析,图6-8为其工作波形图:

①触发翻转阶段: 输入负脉冲Vi到来时,下降沿经RiCi微分环节在Vi'端产生下跳负向尖脉冲,其值低于负向阀值(1/3Vcc)。由于稳态时Vc低于正向阀值(2/3Vcc),固定时器翻转为1,输出Vo 为高电平,集电极输出对地断开,此时单稳态触发器进入暂稳状态。 ②暂态维持阶段: 由于集电极开路输出端(7脚)对地断开,Vcc通过R向C充电,Vc按指数规律上升并趋向于Vcc。从暂稳态开始到Vc值到达正向阀值(2/3Vcc)之前的这段时间就是暂态维持时间tpo。 ③返回恢复阶段: 当C充电使Vc值高于正向阀值(2/3Vcc)时,由于Vi'端负向尖脉冲已消失,Vi'值高于负向阀值(1/3Vcc),定时器翻转为0,输出低电平,集电极输出端(7脚)对地导通,暂态阶段结束。C通过7脚放电,使Vc值低于正向阀值(2/3Vcc),使单稳态触发器恢复稳态。 二、单稳态触发器应用举例 利用单稳态触发器的特性可以实现脉冲整形,脉冲定时等功能。 1.脉冲整形

实验四双稳态触发器功能及应用 一、实验目的 1.掌握两种基本RS触发器的构成、集成JK和D触发器的逻辑功能测试、触发方式和使用方法。 2.掌握触发器之间的相互转换。 3.掌握时序逻辑电路的分析方法与步骤,并通过实验进行逻辑功能验证。 4.学会应用双稳态触发器设计电路。 二、实验任务(建议学时:2学时) (一)基本实验任务 1. 两种基本RS触发器逻辑功能测试; 2. D触发器(74LS74)的逻辑功能测试; 3. JK触发器(74LS112)的逻辑功能测试; 4. 用JK触发器构成D、T、T'触发器,并验证其逻辑功能; (二)扩展实验任务(电类本科生1、2、3项必选一个,4、5项必选一个,非电类本科生1、2、3项任选一个) 1. 对图4-5所示时序逻辑电路1进行分析,画出电路的状态表,并说明该电路实现的逻辑功能是什么?请根据电路原理图在实验室完成电路连线,并验证你的结论。 2. 对图4-6 异步时序逻辑电路2进行分析,画出电路的状态表,并说明该电路实现的逻辑功能是什么?请根据电路原理图在实验室完成电路连线,并验证你的结论。 3. 对图4-7 异步时序逻辑电路3进行分析,画出电路的状态表,并说明该电路实现的逻辑功能是什么?请根据电路原理图在实验室完成电路连线,并验证你的结论。 4.使用D触发器设计一个四位同步加法计数器(可适当增加必要的基本门电路),并验证其逻辑功能。 5.根据图4-9所示电路及工作原理,使用D触发器将图中的控制电路设计出来,以实现图4-9电路的功能。

三、实验原理 触发器(Flip-flop)简称FF。按电路结构分为:基本RS触发器(又称RS锁存器)、同步触发器、主从触发器(Master-Slave FF)、边沿触发器(Edge-Triggered)、维持阻塞触发器等,不同电路结构的触发器有不同的动作特点。按逻辑功能分为:RS触发器(RS锁存器)、D触发器、JK触发器、T和T′触发器等。 1)基本RS触发器动作特点:基本RS触发器,其输出端和Q′状态由输入信号R和S来决定,当输入信号R和S发生变化时,输出端Q和Q′的状态作相应的变化。 2)同步RS触发器(高电平触发)动作特点:输入信号在CP=0期间保持不变,在CP=1的全部时间内R、S的变化都将引起触发器状态的相应改变,即在CP=1期间输入信号发生多次变化,触发器的状态也可能发生多次翻转,电路的抗干扰能力弱。 3)主从触发器的动作特点:①在CP=1期间,主触发器接收输入端(S、R或J、K)的信号,输出端被置为相应的状态,从触发器保持原状态;②在CP下降沿(或上升沿)到来时从触发器按主触发器的状态翻转,即Q和Q′端的状态改变发生在CP的下降沿(或上升沿)。 使用主从触发器应注意:只有在CP=1期间输入状态不变的条件下,当下降沿(或上升沿)到来时,输出状态(次态)才会由输入的状态决定。否则,必须考虑CP=1期间输入状态的全部变化过程,才能确定当下降沿(或上升沿)到来时,触发器的输出状态(次态)。4)边沿触发器的动作特点:边沿触发器的次态仅取决于CP信号的上升沿(或下降沿)到达时输入端的逻辑状态,而在这以前或以后,输入信号的变化对触发器的状态没有影响。这种特点有效的提高了触发器电路的抗干扰能力,因而也提高了电路的工作可靠性。 目前生产的触发器定型产品中只有JK触发器和D触发器两大类。 (一)基本实验任务 1. 与非门、或非门分别构成的RS基本触发器逻辑功能测试 如图4-1所示的两种基本RS触发器分别由与非门和或非门构成。

实验七设计基本触发器一、实验准备 该实验不需要使用七个模块组中的功能单元,所以拨码开关状态;拨码开关MODEL_SEL5-8全置于“OFF状态,以使用JTAG下载方式,这里用户可根据自己所用的下载线来选择适当的下载方式。矚慫润厲钐瘗睞枥庑赖賃軔朧。 二、实验目的 熟悉利用Quartusll开发数字电路的基本流程和Quartusll软件的相关操作, 介绍Quartusll的软件,掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,下载等基本操作。 了解VHDL或原理图设计方法与定制IP模块的思想。 掌握基本触发器的设计思路及工作原理 三、实验原理 通过开关分别输入单bit的数据,并用开关作为控制信号,实现置位和复位。将 T触发器的结果分别在2个LED上显示。聞創沟燴鐺險爱氇谴净祸測樅。 四、实验内容 1、用VHDL语言设计D触发器和T触发器;注意时钟要用到分频电路。 2、用Quartusll软件进行编译,仿真,下载到实验平台进行验证。 五、设计原理框图 六、引脚分配情况 D A21 CLK P25 CLR F6 P SET B21 QT AA11 Q AC10 MODEL SEL1-3 均置于“OFF D触发器和

Q,QT 为D 触发器和T 触发器的输出信号,分别对应平台上的 LED0和LED7。CLR,PSET 为高电平清零和置位信号, CLK 为时钟信号。残骛楼諍锩瀨濟溆塹籟婭骤東。 七、结果分析 波形仿真 如上所述,Q,QT 作为D 触发器和T 触发器的输出信号,分别对应平台 CLR,PSET 为高电平清零和置位信号, CLK 为时 这里简单列出波形图, 实际可以自己加上其他的 八、VHDL 源程序代码 --D flip flop library IEEE; use IEEE.std_logic_1164.all; ENTITY DFFL OP IS PORT ( D: in STD_LOGIC; CLK,CLR, PSET: in STD_LOGIC;-- 时钟,清零,置位 Q: out STD LOGIC --输出 ); END DFFL OP; ARCHITECTURE FFA OF DFFL OP IS BEGIN P ROCESS(CLK ,P SET,CLR) BEGIN Q<='1'; ELSIF CLR='1' THEN Q<='0'; ELSIF CLK'EVENT AND CLK='1' THEN Name CLK CLR £ FS ET G QT Value a 11.£5 ] B B B B B B ]ps ISO. 0 ILS 11.25 ns -J ______________ -rLZFLZFLFLJnLJn_J^ 4S0 0 ns 从上图可以看出, 上的LED0和LED7,正确对应了结果。 钟信 号,都实现了相应的功能, 限于篇幅, 信号进行仿真。酽锕极額閉镇桧猪訣锥顧荭钯。 --输入 IF P SET='1' THEN --异步置位 --异步7冃零

双稳态电路原理及设计、实际应用 一、工作原理 图一为双稳态电路,它是由两级反相器组成的正反馈电路,有两个稳定状态,或者是BG1导通、BG2截止;或者是BG1截止、BG2导通,由于它具有记忆功能,所以广泛地用于计数电路、分频电路和控制电路中。 原理,图2(a)中,设触发器的初始状态为BG1导通,BG2截止,当触发脉冲方波从1端输入,经CpRp微分后,在A点产生正、负方向的尖脉冲,而只有正尖脉冲能通过二极管D1作用于导通管BG1的基极是。ic1减小使BG1退出饱和并进入放大状态,于是它的集电极电位降低,经电阻分压器送到截止管BG2的基极,使BG2的基极电位下降,如果下降幅度足够时,BG2将由截止进入放大状态,因而产生下列正反馈过程(看下列反馈过程时,应注意:在图一的PNP电路中,晶体管的基极和集电极电位均为负值,所以uc1↓,表示BG1集电极电位降低,而uc1↑则表示BG1集电极电位升高,当BG1基极电位降低时,则ic1↑,反之当BG1基极电位升高时,ic1↓,ic1越来越小,ic2越来越大,最后到达BG1截止、BG2导通;接差触发脉冲方波从2端输入,并在t=t2时,有正尖脉冲作用于导通管BG2的基极,又经过正反馈过程,使BG1导通,BG2截止。以后,在1、2端的触发脉冲的轮流作用下,双稳电路的状态也作用相应的翻转,如图一(b)所示。 图一、双稳态电路 由上述过程可见:(1)双稳态电路的尖顶触发脉冲极性由晶体管的管型决定:PNP管要求正极性脉冲触发,而NPN管却要求负极性脉冲触发。(2)每触发一次,电路翻转一次,因此,从翻转次数的多少,就可以计算输入脉冲的个数,这就是双稳态电路能够计算的原理。双稳态电路的触发电路形式有:单边触发、基极触发、集电极触发和控制触发等。 图二给出几种实用的双稳态电路。电路(a)中D3、D4为限幅二极管,使输出幅度限制在-6伏左右;电路(b)中的D5、D6是削去负尖脉冲;电路(C)中的ui1、ui2为单触发,ui为输入触发表一是上述电路的技术指标。

实验七8421码检测电路的设计 姓名:张跃佳 班级:电自2班 学号: 实验时间:2015.12.24

【实验目的】 1.了解检测电路的工作原理 2.进一步掌握同步时序逻辑电路的设计方法 【实验仪器及器件】 1.实验箱、万用表、示波器 2.74LS73、74LS74、74LS00、74LS20、74LS197 【实验原理】 本实验要求设计一个8421BCD码(串行输入)检测电路。此电路是用来检测串行的8421码传输过程中是否发生错误。假定8421BCD码传送过程中是由低到高串行送数,例如十进制2(代码为0010)是按0、1、0、0次序传送的。如果在传送过程中代码发生错误,出现非法数码(不在0000到1001之间的代码)则检测电路发生一脉冲信号。 实验所用触发器为JK触发器,要求自己设计、自己安装和测试。 设计提示 本实验的设计关键是建立原始状态图和状态表。根据要求8421BCD码是由低位到高位传送,该电路每四个码元检测一次,当电路收到第四个码元时,若判断是非法码,则输出为1,否则输出为0.可见此电路为米里时序电路。 设检测电路初始状态为S ,当电路接收第一个码元后,根据输入是0还是1, 将分别转到两个不同的新状态S 1和S 2 ,从S 1 或S 2 出发,接收到第二个码元后, 又根据是0还是1,又转到两个不同的新状态,类推到接收到的第三、四码元后电路执行统一的动作。在接收到第四个码元后,根据接收的代码判断是否是非法码而确定其输出是否为1,并且电路回到初始状态S ,准备接受新的一组码组。 根据上面的分析很容易做出原始状态和状态表了。这样做出的元素状态表有15个状态,经过化简后只剩下6个状态。化简后的状态如表(一)。由简化状态表,根据状态分配原则,可得许多分配方案,其中一种分配方案如表(二),得到的结果是:

置位和复位优先双稳态触发器指令 RS触发器具有置位和复位的双重功能,RS触发器是复位优先时,当置位(S)和复位(R)同时为真时,输出为假。而SR触发器是置位优先触发器时,当置位(S)和复位(R)同时为真时,输出为真。RS 和SR触发器指令应用如下图所示: 图4-16 RS 和SR 触发器指令应用 边沿触发指令 边沿触发是指用边沿触发信号产生一个机器周期的扫描脉冲,通常用做脉冲整形。边沿触发指令分为上升沿(正跳变触发)和下降沿(负跳变触发)两大类,正跳变触发指令指输入脉冲的上升沿使触点闭合(ON)一个扫描周期。负跳变触发指输入脉冲的下降沿使触点闭合(ON)一个扫描周期。边沿触发指令格式见表4-5

【例4-5】如图4-17所示的程序,若I0.0上电一段时间后再断开,请画出I0.0,Q0.0,Q0.1和Q0.2 图4-17 边沿触发指令应用实例 [解]如图4-17所示,在I0.0的上升沿,触点(EU)产生一个扫描周期的时钟脉冲,驱动输出线圈Q0.1通电一个扫描周期,Q0.0通电,使输出线圈Q0.0置位并保持。 在I0.0的下降沿,触点(ED)产生一个扫描周期的时钟脉冲,驱动输出线圈Q0.2通电一个扫面周期,是输出线圈Q0.0复位并报出。【例4-6】设计用一个单按钮控制一盏灯的亮和灭,即按奇数次按钮灯亮,按偶数次按钮等灭。 [解] 当I0.0第一次合上时,V0.0接通一个扫描周期,使得Q0.0线圈得电一个扫描周期,当下一次扫描周期到达,Q0.0常开触点闭合自

锁,灯亮。 当I0.0第二次合上时,V0.0接通一个扫描周期,使得Q0.0线圈闭合一个扫描周期。切断Q0.0的敞开触点和V0.0的敞开触点,使得灯灭。

第25次课 单稳态触发器 ● 本次重点内容: 1、单稳态触发器的工作原理。 2、周期的计算方法。 ● 教学过程 25.1单稳态触发器 一、单稳态触发器的特点: 1、有一个稳定状态和一个暂稳状态。 2、在触发脉冲作用下,电路将从稳态翻转到暂稳态,在暂稳态停留一段时间后,又自动返回稳定状态。 3、暂稳态时间的长短取决于电路本身参数,与触发脉冲的宽度无关。 二、电路组成: 图25-1(a ) 图25-1(b ) 三、工作原理: 1、稳定状态: 接通电源前,u I 为高电平。接通电源后,U CC 经R 对电容C 充电,当电 容C 上的电压u c ≥32U CC 时,由于u I >3 1U CC ,555定时器输出为低电平。放电

管VT 导通,电容C 经放电管VT 迅速放电,u c ≈0,由于U TH <32U CC , U TR >3 1U CC ,所以555定时器保持0状态不变。稳态时,u c =0,u o =0。 2、暂稳态 在负触发脉冲u I 的作用下,低电平触发端TR 得到低于3 1U CC 的触发电 平,由于此时u c =0,U TH <32U CC , U TR <3 1U CC , 555定时器输出高电平。同时放电管VT 截止,电路进入暂稳态,定时开始。 暂稳态阶段(t1~t2),电容C 充电,充电回路为U CC →R →C →地,充电时间常数为RC ,u c 按指数上升。 3、自动返回稳定状态 当电容C 上的电压u c 上升32U CC 时,由于U TH ≥32U CC , U TR ≥3 1U CC ,555定时器输出由高电平变为低电平,放电管VT 由截止变为饱和,暂稳态结束。电容C 经放电管VT 迅速放电到0V ,由于放电管饱和导通的等效电阻较小,所以放电速度快,在这个阶段555定时器维持低电平状态。 电路返回稳态后,当下一个触发信号到来时,又重复上述过程。 可见,输出脉冲宽度t w 为电容C 上的电压u c 由0充到3 2U CC 所需的时间,其大小可用下式计算: t w =RCln 3≈1.1RC 四、用门电路构成的微分型单稳态触发器 (一)电路组成:

( 二 〇 一 五 年 五 月 《数据库原理及应用》实验报告 学校代码: 10128 学 号: 201220905048 题 目:存储过程和触发器的使用 学生姓名:孙跃 学 院:理学院 系 别:数学系 专 业:信息与计算科学 班 级:信计12-2 任课教师:侯睿

一、实验目的 1.掌握存储过程的使用方法; 2.掌握触发器的使用方法。 二、实验内容 1.存储过程; 2.触发器。 三、实验程序及结果 1、存储过程 (1)创建存储过程,使用Employees表中的员工人数来初始化一个局部变量,并调用这个存储过程。 USE YGGL GO CREATE PROCEDURE TEST @NUMBER1 int OUTPUT AS BEGIN DECLARE @NUMBER2 int SET @NUMBER2=(SELECT COUNT(*)FROM Employees) SET @NUMBER1=@NUMBER2 END GO USE YGGL GO DECLARE @num int EXEC TEST @num OUTPUT SELECT @num (2)创建存储过程,比较两个员工的实际收入,若前者比后者高就输出0,否则输出1。USE YGGL GO CREATE PROCEDURE COMPA @ID1 CHAR(6),@ID2 CHAR(6),@BJ INT OUTPUT AS BEGIN DECLARE @SR1 FLOAT,@SR2 FLOAT SELECT @SR1=InCome-OutCome FROM Salary

EmployeeID=@ID1 SELECT @SR2=InCome-OutCome FROM Salary WHERE EmployeeID=@ID2 IF @ID1>@ID2 SET @BJ=0 ELSE SET @BJ=1 END USE YGGL GO DECLARE @BJ int EXEC COMPA '000001','108991',@BJ OUTPUT SELECT @BJ (3)创建添加职员记录的存储过程EmployeeADD。 USE YGGL GO CREATE PROCEDURE EmployeeAdd ( @employeeid char(6), @name char(10), @education char(4), @birthday datetime, @woekyear tinyint, @sex bit, @address char(40), @phonenumber char(12), @departmentID char(3) ) AS BEGIN INSERT INTO Employees VALUES(@employeeid,@name,@education,@birthday, @woekyear, @sex,@address,@phonenumber,@departmentID) END RETURN GO

课题:单稳态触发器 课时:讲/练二课时 教学要求: (1)理解单稳态触发器的工作原理; (2)掌握输出波形周期的估计。 教学过程: 一、微分型单稳态触发器 1、单稳态触发器的功能特点:只有一个稳定状态的触发器。如果没有外来 触发信号,电路将保持这一稳定状态不变。只有在外来触发信号作用下,电路才会从原来的稳态翻转到另一个状态。但是,这一状态是暂时的,故称为暂稳态,经过一段时间后,电路将自动返回到原来的稳定状态。 2、功能:常用于脉冲的整形和延时。 3、电路组成: vo经过R、C组成的微分电路,耦合 到门G2的输入端,故称微分型单稳态电路。 4、工作原理: 1)电路的稳态:无触发信号输入时,v I为高 电平。由于电阻R很小,B端相当于接地,门 G2的输入信号为低电平0,v o输出高电平1 态。 2)电路的暂稳态:当输入端A加入低电 平触发信号时,门G1的输出为高电平1,通过电容C耦合,门G2 的输入信号为高电平1,v o输出低电平0态。 3)暂稳态期间:v o1高电平对C充电,使B端的电平也逐渐下降。 4)自动恢复为稳态:当B端的电平下降到关门电平时,门G2关闭,输出电压又上跳为高电平。 5、输出脉冲宽度:T W≈0.7RC。 二、集成单稳态触发器-CT74121 (一)外引线排列及引出端符号 Q:暂稳态正脉冲输出端; Q:暂稳态负脉冲输出端; TR+:为正触发(上升沿触发)输入端; TR一A、TR一B:两个负脉冲(下降沿触发)输入端;

Cext:为外接电容端; Rint:为内电阻端; Rext/Cext:为外接电阻和电容的公共端; Vcc、GND、NC。 (二)逻辑功能及简要说明 1、外引线排列图: 2、输出脉冲宽度T W由定时元件R、C决定。T W≈0.7RC。作业:P26713-9、13-10

实验七触发器的仿真 实验目的 1.用逻辑图和VHDL语言设计D锁存器,并进行仿真与分析; 2.参看Maxplus中器件7474(边沿D触发器)的逻辑功能,用VHDL语言设计边沿触发式D触发器,并进行仿真与分析。 3.参看Maxplus中器件7476(边沿JK触发器)的逻辑功能,用VHDL语言设计边沿触发式JK触发器,并进行仿真与分析。 1.D锁存器(D Latch) 实验设计思想 使能端EN输入为1时,输出Q与输入D值相同;使能端EN输入为0时,输出Q保持不变。 实验原理图 实验VHDL源程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY ex71 IS PORT( C,D:IN STD_LOGIC; Q,QN:BUFFER STD_LOGIC); END ex71; architecture bhv OF ex71 IS BEGIN PROCESS(C,D,Q) BEGIN IF (C='1') THEN Q<=D;ELSE Q<=Q;END IF; QN<=NOT Q; END PROCESS; END bhv; 实验波形仿真

Preset , Clear and Complementary Outputs) 实验原理图

实验VHDL源程序 library ieee; use ieee.std_logic_1164.all; entity ex72 is port( D,CLK,PR_L,CLR_L:IN std_logic; Q,QN:out std_logic); end ex72; architecture vhb of ex72 is signal PR,CLR:STD_LOGIC; BEGIN process(CLR_L,CLR,PR_L,PR,CLK) begin PR<=not PR_L;CLR<=not CLR_L; if(CLR AND PR)='1'then Q<='1';QN<='1'; elsif CLR='1' then Q<='0';QN<='1'; elsif PR='1'then Q<='1';QN<='0'; elsif (CLK'event and CLK='1')then Q<=D;QN<=not D; end if; end process; end vhb; 实验波形仿真

单稳态触发器芯片有哪些_单稳态触发器工作原理 单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。 单稳态触发器电路组成如图所示,其中R、C为单稳态触发器的定时元件,它们的连接点Vc与定时器的阈值输入端(6脚)及输出端V o(7脚)相连。单稳态触发器输出脉冲宽度tpo=1.1RC。 Ri、Ci构成输入回路的微分环节,用以使输入信号Vi的负脉冲宽度tpi限制在允许的范围内,一般tpi》5RiCi,通过微分环节,可使Vi’的尖脉冲宽度小于单稳态触发器的输出脉冲宽度tpo。若输入信号的负脉冲宽度tpi本来就小于tpo,则微分环节可省略。 定时器复位输入端(4脚)接高电平,控制输入端Vm通过0.01uF接地,定时器输出端V o(3脚)作为单稳态触发器的单稳信号输出端。 单稳态触发器工作原理当输入Vi保持高电平时,Ci相当于断开。输入Vi‘由于Ri的存在而为高电平Vcc。此时,①若定时器原始状态为0,则集电极输出(7脚)导通接地,使电容C放电、Vc=0,即输入6脚的信号低于2/3Vcc,此时定时器维持0不变。 ②若定时器原始状态为1,则集电极输出(7脚)对地断开,Vcc经R向C充电,使Vc 电位升高,待Vc值高于2/3Vcc时,定时器翻转为0态。 结论:单稳态触发器正常工作时,若未加输入负脉冲,即Vi保持高电平,则单稳态触发器的输出V o一定是低电平。 单稳态触发器的工作过程分为下面三个阶段来分析,图为其工作波形图: ①触发翻转阶段: 输入负脉冲Vi到来时,下降沿经RiCi微分环节在Vi’端产生下跳负向尖脉冲,其值低于负向阀值(1/3Vcc)。由于稳态时Vc低于正向阀值(2/3Vcc),固定时器翻转为1,输出V o为高电平,集电极输出对地断开,此时单稳态触发器进入暂稳状态。 ②暂态维持阶段:

门电路构成的单稳态触发器及典型应用分析 单稳态触发器有一个稳定状态和一个暂稳态。当外加触发信号时,单稳态触发器从稳定状态转换到暂稳态,在暂稳态维持一段时间后,由于电路中所包含的电容元件的充放电作用,电路自动返回到稳定状态,因此这种电路称为“单稳”。暂稳态维持的时间取决于电路本身的参数,而与外触发信号的宽度无关。 根据单稳态触发器的这些特点,数字系统常用它构成整形、脉冲展宽、延时和定时(产生一定宽度的方波)等电路。 【项目任务】 一、门电路构成的单稳态触发器 1.电路结构 由门电路和RC 元件组成的单稳态触发器电路形式较多。一个电阻和一个电容元件可以组成积分电路或者微分电路,因此,由门电路和RC 元件可组成积分型单稳态触发器和微分型单稳态触发器。图9.10所示电路就是微分型单稳态触发器的电路形式之一。电路中电阻R 的值小于门电路的关门电阻值,即R