《工业控制计算机》2019年第32卷第2期

?国家自然科学基金项目(61674100);国家自然科学基金项目(61774101)

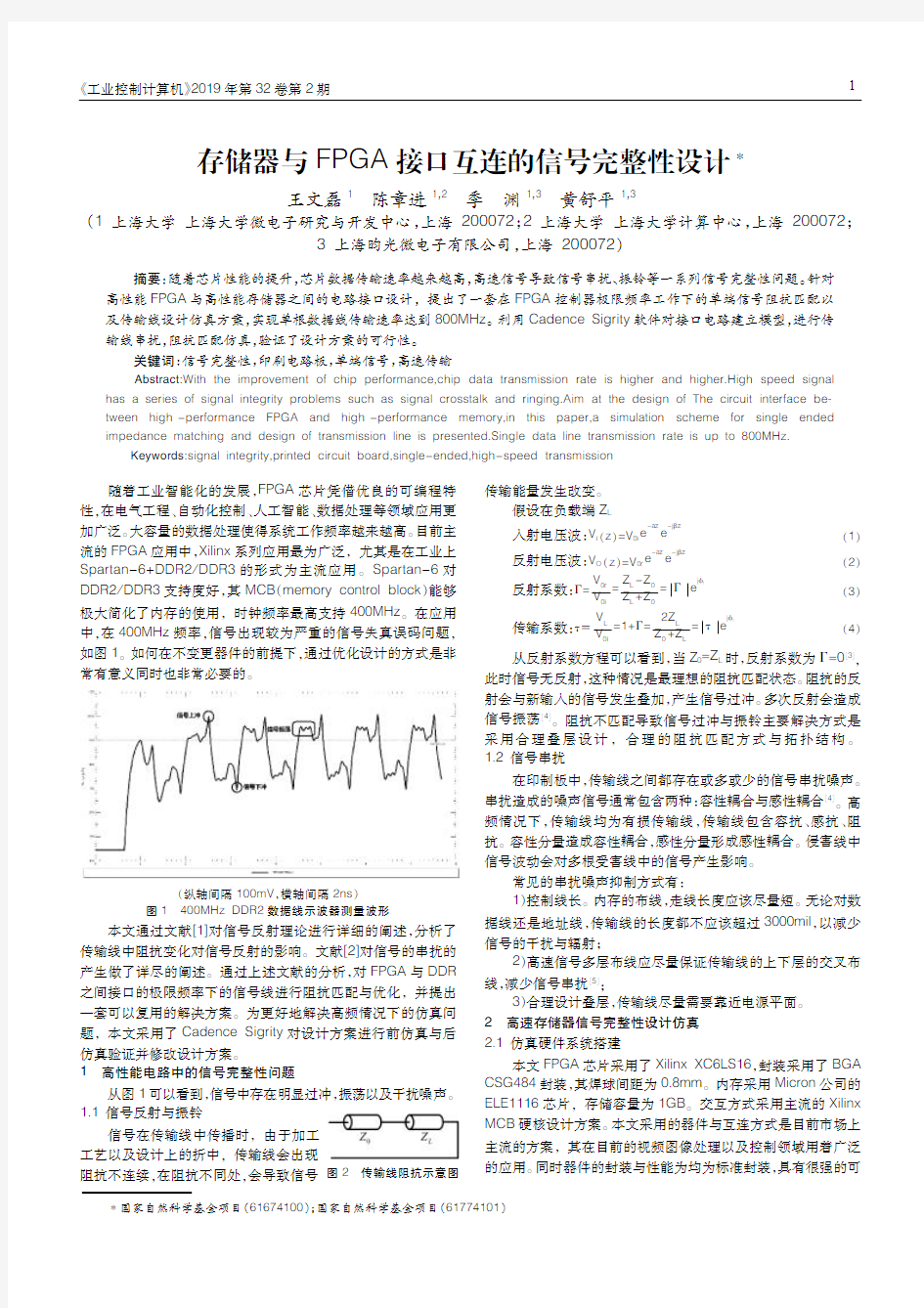

随着工业智能化的发展,FPGA 芯片凭借优良的可编程特性,在电气工程、自动化控制、人工智能、数据处理等领域应用更加广泛。大容量的数据处理使得系统工作频率越来越高。目前主流的FPGA 应用中,Xilinx 系列应用最为广泛,尤其是在工业上Spartan-6+DDR2/DDR3的形式为主流应用。Spartan-6对DDR2/DDR3支持度好,其MCB (memory control block )能够极大简化了内存的使用,时钟频率最高支持400MHz 。在应用中,在400MHz 频率,信号出现较为严重的信号失真误码问题,如图1。如何在不变更器件的前提下,通过优化设计的方式是非常有意义同时也非常必要的。

(纵轴间隔100mV ,横轴间隔2ns )

图1

400MHz DDR2数据线示波器测量波形

本文通过文献眼1演对信号反射理论进行详细的阐述,分析了传输线中阻抗变化对信号反射的影响。文献眼2演对信号的串扰的产生做了详尽的阐述。通过上述文献的分析,对FPGA 与DDR 之间接口的极限频率下的信号线进行阻抗匹配与优化,并提出一套可以复用的解决方案。为更好地解决高频情况下的仿真问题,本文采用了Cadence Sigrity 对设计方案进行前仿真与后仿真验证并修改设计方案。

1高性能电路中的信号完整性问题

从图1可以看到,信号中存在明显过冲,振荡以及干扰噪声。1.1信号反射与振铃

信号在传输线中传播时,由于加工工艺以及设计上的折中,传输线会出现

阻抗不连续,在阻抗不同处,会导致信号传输能量发生改变。

假设在负载端Z L

入射电压波:V i (z )=V 0i e -az

e

-j βz (1)反射电压波:V O (z )=V 0r e -az e -j βz

(2)

反射系数:Γ=V 0r V 0i =Z L -Z 0

Z L +Z 0

=Γe j ?r

(3)传输系数:τ≡

V L V 0i =1+Γ=2Z L

Z 0+Z L

=τe j ?r

(4)

从反射系数方程可以看到,当Z 0=Z L 时,反射系数为Γ=0[3],此时信号无反射,这种情况是最理想的阻抗匹配状态。阻抗的反射会与新输入的信号发生叠加,产生信号过冲。多次反射会造成信号振荡[4]。阻抗不匹配导致信号过冲与振铃主要解决方式是采用合理叠层设计,合理的阻抗匹配方式与拓扑结构。1.2信号串扰

在印制板中,传输线之间都存在或多或少的信号串扰噪声。串扰造成的噪声信号通常包含两种:容性耦合与感性耦合[4]。高频情况下,传输线均为有损传输线,传输线包含容抗、感抗、阻抗。容性分量造成容性耦合,感性分量形成感性耦合。侵害线中信号波动会对多根受害线中的信号产生影响。

常见的串扰噪声抑制方式有:

1)控制线长。内存的布线,走线长度应该尽量短。无论对数据线还是地址线,传输线的长度都不应该超过3000mil ,以减少信号的干扰与辐射;

2)高速信号多层布线应尽量保证传输线的上下层的交叉布线,减少信号串扰[5];

3)合理设计叠层,传输线尽量需要靠近电源平面。2高速存储器信号完整性设计仿真2.1仿真硬件系统搭建

本文FPGA 芯片采用了Xilinx XC6LS16,封装采用了BGA CSG484封装,其焊球间距为0.8mm 。内存采用Micron 公司的ELE1116芯片,存储容量为1GB 。交互方式采用主流的Xilinx MCB 硬核设计方案。本文采用的器件与互连方式是目前市场上主流的方案,其在目前的视频图像处理以及控制领域用着广泛的应用。同时器件的封装与性能为均为标准封装,具有很强的可

存储器与FPGA 接口互连的信号完整性设计?

王文磊1陈章进1,2季渊1,3黄舒平1,3

(1上海大学上海大学微电子研究与开发中心,上海200072;2上海大学上海大学计算中心,上海200072;

3上海昀光微电子有限公司,上海200072)

摘要:随着芯片性能的提升,芯片数据传输速率越来越高,高速信号导致信号串扰、振铃等一系列信号完整性问题。针对高性能FPGA 与高性能存储器之间的电路接口设计,提出了一套在FPGA 控制器极限频率工作下的单端信号阻抗匹配以及传输线设计仿真方案,实现单根数据线传输速率达到800MHz 。利用Cadence Sigrity 软件对接口电路建立模型,进行传输线串扰,阻抗匹配仿真,验证了设计方案的可行性。

关键词:信号完整性,印刷电路板,单端信号,高速传输

Abstract 押With the improvement of chip performance熏chip data transmission rate is higher and higher.High speed signal has a series of signal integrity problems such as signal crosstalk and ringing.Aim at the design of The circuit interface be?tween high -performance FPGA and high -performance memory熏in this paper熏a simulation scheme for single ended impedance matching and design of transmission line is presented.Single data line transmission rate is up to 800MHz.

Keywords 押signal integrity熏printed circuit board熏single-ended熏high-speed

transmission

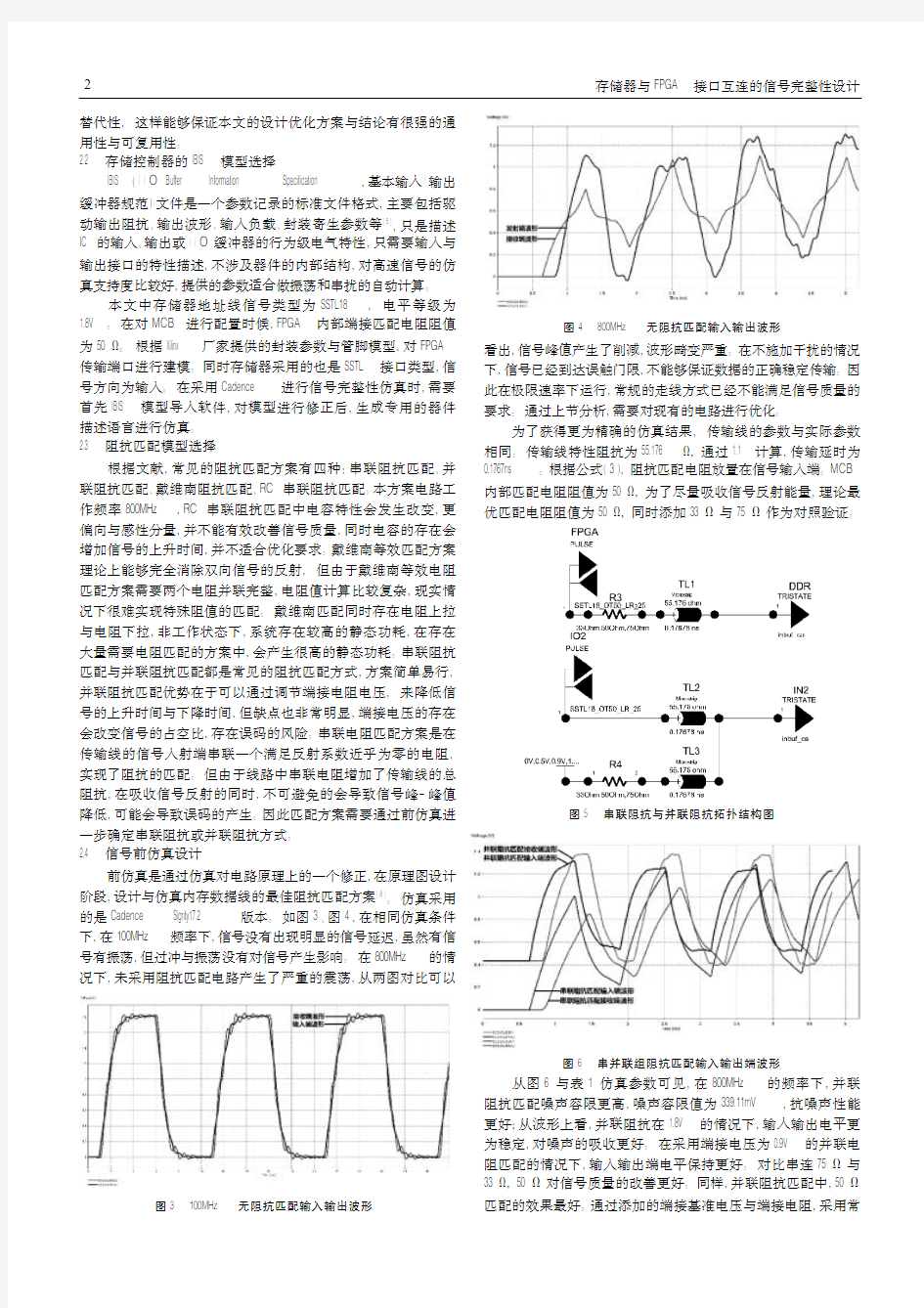

图2传输线阻抗示意图

1