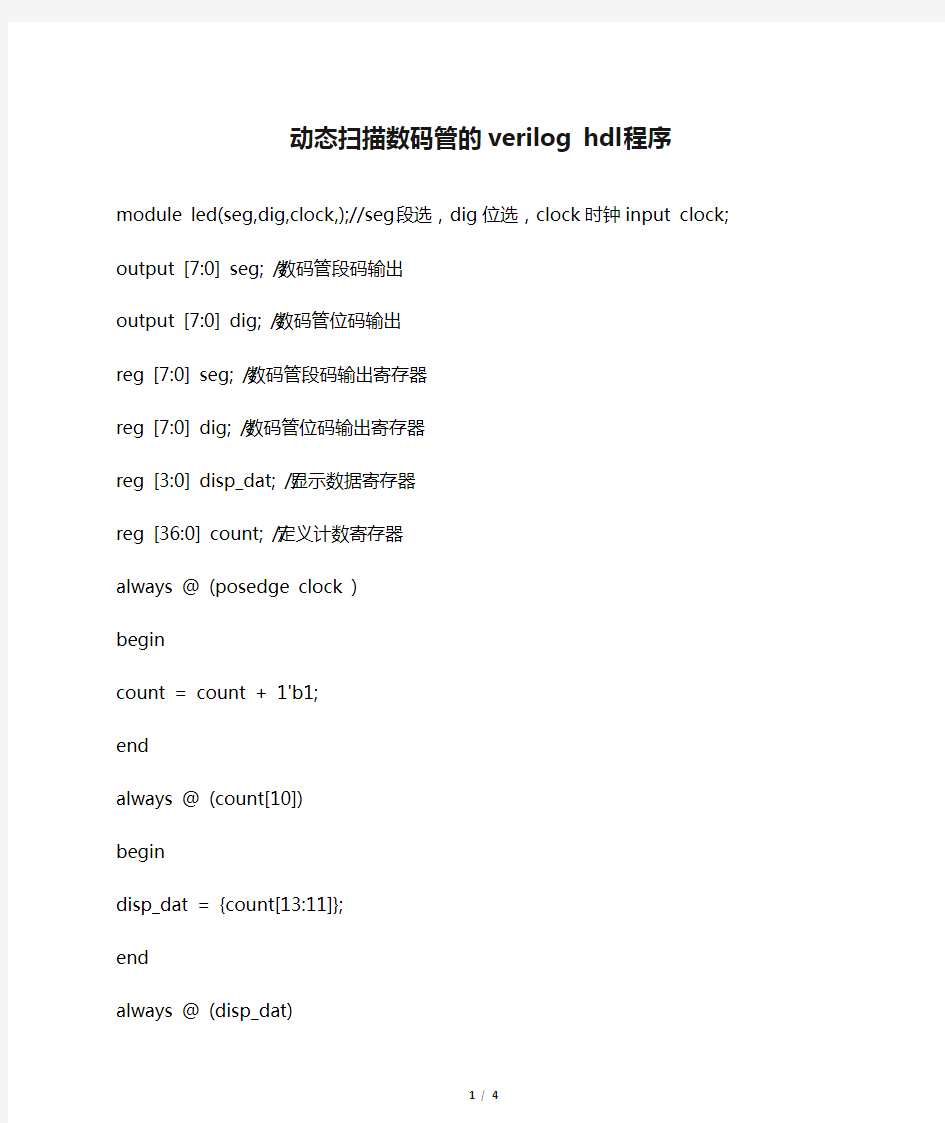

动态扫描数码管的verilog hdl程序

module led(seg,dig,clock,);//seg段选,dig位选,clock时钟input clock; output [7:0] seg; //数码管段码输出

output [7:0] dig; //数码管位码输出

reg [7:0] seg; //数码管段码输出寄存器

reg [7:0] dig; //数码管位码输出寄存器

reg [3:0] disp_dat; //显示数据寄存器

reg [36:0] count; //定义计数寄存器

always @ (posedge clock )

begin

count = count + 1'b1;

end

always @ (count[10])

begin

disp_dat = {count[13:11]};

end

always @ (disp_dat)

begin

case (disp_dat)

3'h0 :

dig = 8'b11110; //显示第一个数码管,低电平有效3'h1 :

dig = 8'b11101; //显示第二个数码管,低电平有效3'h2 : dig = 8'b111011; //显示第三个数码管,低电平有效3'h3 : dig = 8'b110111; //显示第四个数码管,低电平有效3'h4 : dig = 8'b111011; //显示第五个数码管,低电平有效3'h5 : dig = 8'b110111; //显示第六个数码管,低电平有效3'h6 : dig = 8'b10111; //显示第七个数码管,低电平有效3'h7 : dig = 8'b01111; //显示第八个数码管,低电平有效endcase end

always @ (disp_dat)

begin

case (disp_dat)

4'h0 :

seg = 8'hc0; //显示"0"

4'h1 :

seg = 8'hf9; //显示"1"

4'h2 :

seg = 8'ha4; //显示"2"

4'h3 :

seg = 8'hb0; //显示"3"

4'h4 :

seg = 8'h99; //显示"4"

4'h5 :

seg = 8'h92; //显示"5" 4'h6 :

seg = 8'h82; //显示"6" 4'h7 :

seg = 8'hf8; //显示"7" 4'h8 :

seg = 8'h80; //显示"8" 4'h9 :

seg = 8'h90; //显示"9" 4'ha :

seg = 8'h88; //显示"a" 4'hb :

seg = 8'h83; //显示"b" 4'hc :

seg = 8'hc6; //显示"c" 4'hd :

seg = 8'ha1; //显示"d" 4'he :

seg = 8'h86; //显示"e" 4'hf :

seg = 8'h8e; //显示"f" endcase

end

endmodule