实验九可逆计数器的功能测试及应用电路

实验目的:

(1)掌握可逆计数器74LS191、74LS191、74LS192、74LS193的逻辑功能及使用方法。

(2)熟悉可逆计数器实现任意进制的数码倒计时电路的工作原理。

实验仪器与器件:

实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。

74LS191、74LS191、74LS191或74HC48、74LS00和74LS04。

实验内容:

1测试74LS190和74LS191的逻辑功能,并用数码管显示,验证是否与表2-9-4一致,分别画出各单元的电路图,写出各自的状态

实验原理:单时钟74LS191二进制同步加/减计数器的功能表如下:

表2-9-4单时钟74LS191二进制同步加/减计数器的功能表

单时钟74LS191二进制同步加/减计数器是十进制的,其他功能与74LS191一样。它的有效状态为0000~1001.

实验电路:

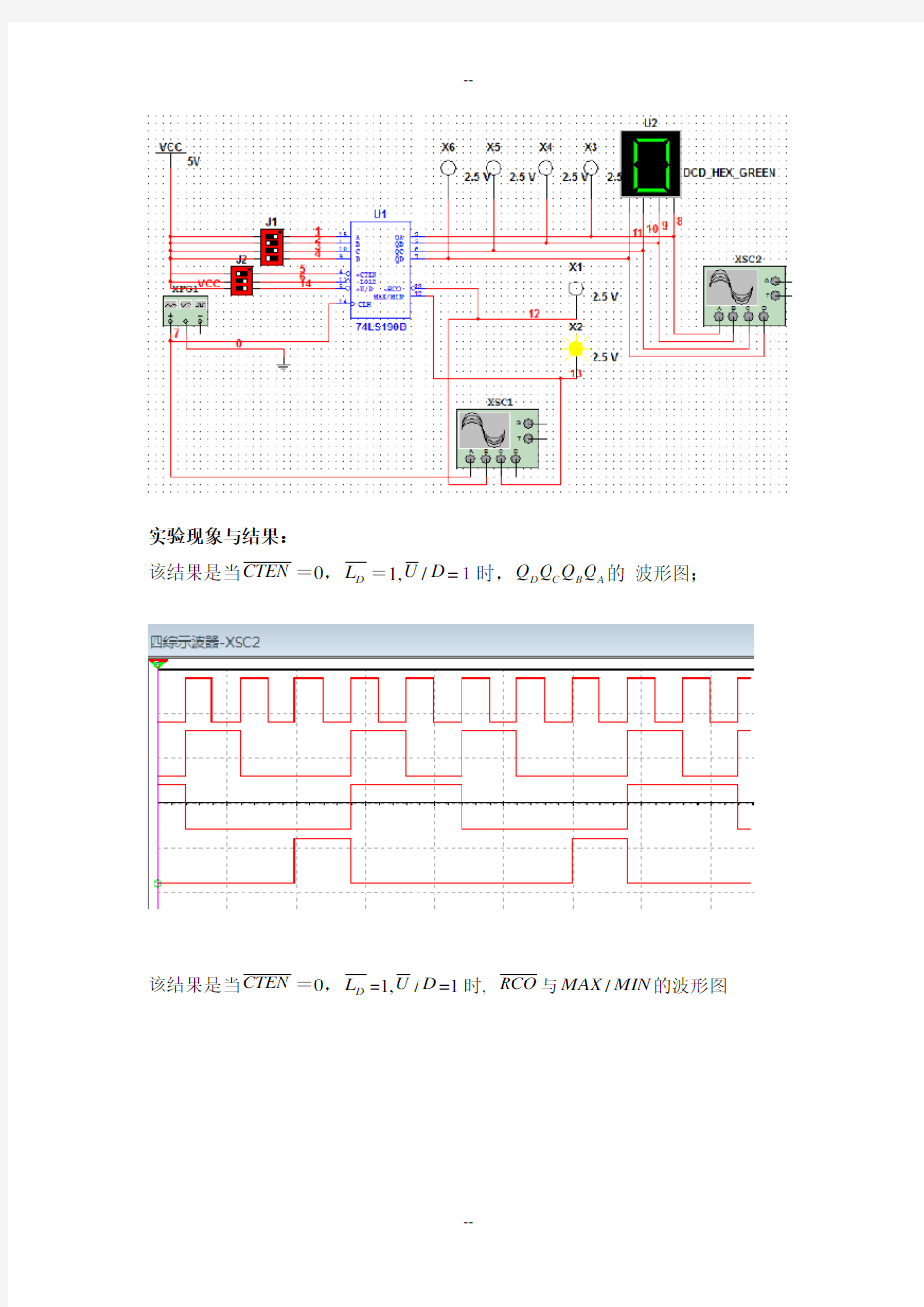

如图所示是减计数时当计数器的状态变为0时的电路状态:RCO=0,MAX/=1;

MIN

实验现象与结果:

该结果是当CTEN =0,D L =1,D U /=1时,A B C D Q Q Q Q 的 波形图;

该结果是当CTEN =0,D L =1,D U /=1时, RCO 与MIN MAX /的波形图

需要说明的是:当CTEN=

D

L=1时,电路保持原来的状态。

2测试74LS192和74LS193的逻辑功能,并用数码管显示,验证是否与表2-9-3及2-9-5一致。画出测试电路图。

实验原理:

双时钟74LS192同步十进制可逆计数器的功能表如下表所示,74LS192是十进制计数器。

表2-9-3双时钟74LS192同步十进制可逆计数器的功能表

输入输出工作

状态

U CP UP

D

CP

DOW

N

CLR

D

L

DCBA

A

B

C

D

Q

Q

Q

Q

U

TC

D

TC

**H H **** 0000H H 异步

清零* *L L 1001 1001H H 异步

置数

H ↑L H **** 1001→

0001→

0000H

H

H

L

减法

计数

↑H L H ****0000→1

000→

1001H

L

H

H

加法

计数

双时钟74LS193二进制同步加/减法计数器的功能表如下表所示,74LS193是一个十六进制的计数器。

U CP UP D CP D OW

N

CLR D L

DC B

A

A B C D Q Q Q Q U TC D TC

工作状态

* * H H **** 0000 H H 异步清零 * * L L 1001 1001

H H 异步置数 H

↑

L

H

****

1111→0001→0000

H

H H L 减法计数 ↑ H L H

**** 0000→0001→1

111

H L

H H

加法计数

74L S193和74LS 193除了一个是十进制,一个是十六进制以外,其他功能一模一样。 实验电路:

实验现象: 当U CP =1, D CP 接CP 脉冲时且 C LR=0、D L =1时,此时为减法计数, A B C D Q Q Q Q 波形图如下:

当U CP =1, D CP 接CP脉冲时且 CL R=0、D L =1时,此时为减法计数,

U TC 与D TC 的波形图如下:

当D CP =1,U CP 接C P脉冲时且 CLR=0、D L =1时,此时为加法计数,

A B C D Q Q Q Q 波形图如下:

当D CP =1, U CP 接CP脉冲时且 CLR=0、D L =1时,此时为加法计数, U TC

与

TC的波形图如下:

D

3用74LS190或74LS191设计一个可预置60S倒计时的电路,参考电路如图2-9-4所示。

U/置为1,实现减法计数。由于74LS190是十进制的计数器,实验原理:将D

所以将两片74LS190级联,即将低位片的RCO接到高位片的CLK端,就可实现低于100的任意加减法计数器。本题的具体实现方法如下:级联后,将高位片的数据端置为0110,低位片的数据端置为0000;将两片74LS190的RCO端通过一个或门后与一个开关再通过一个与门接到

L端,所实现的功能是:当两片74LS

D

190的计数状态都减到0000时,RCO均为0,此时让两片74LS190置数为60,或者当开关闭合时,也让两片74LS190置数为60。

实验电路:

电路说明:为了简化电路,所以使用自带有译码功能的数码管。

实验现象与结果:

当开关闭合时,

L=0,数码管显示60,再将开关断开时,开始减法计数,有效状

D

态为60~0,如此,便实现了一个倒计时电路