DC的使用

一、实验目的

1、掌握DC软件的基本使用流程;

2、熟悉基本的DC命令,并理解其意义;

3、对DC综合后的结果进行分析。

二、实验工具

Synopsys 公司电路综合工具Design Complier,即DC。

三、实验内容概述

1、利用DC图形界面进行电路综合;

2、使用DC脚本文件进行电路综合;

3、查看综合报告,根据报告分析电路性能。

四、实验步骤

(文件说明:为了演示方便,在进行下面的实验时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v 的脚本文件。)

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。当然,它们二者功能是一样的,在图形界面的每步操作都有相应的命令。我们先以较为直观的图形界面来演示各个操作步骤,并给出相应的tcl命令,再用DC 脚本来对电路进行综合。准备好需要综合的文件和相应的脚本文件后,下面就开始我们的实验:

一、DC图形界面的使用。

1.DC图形界面的启动

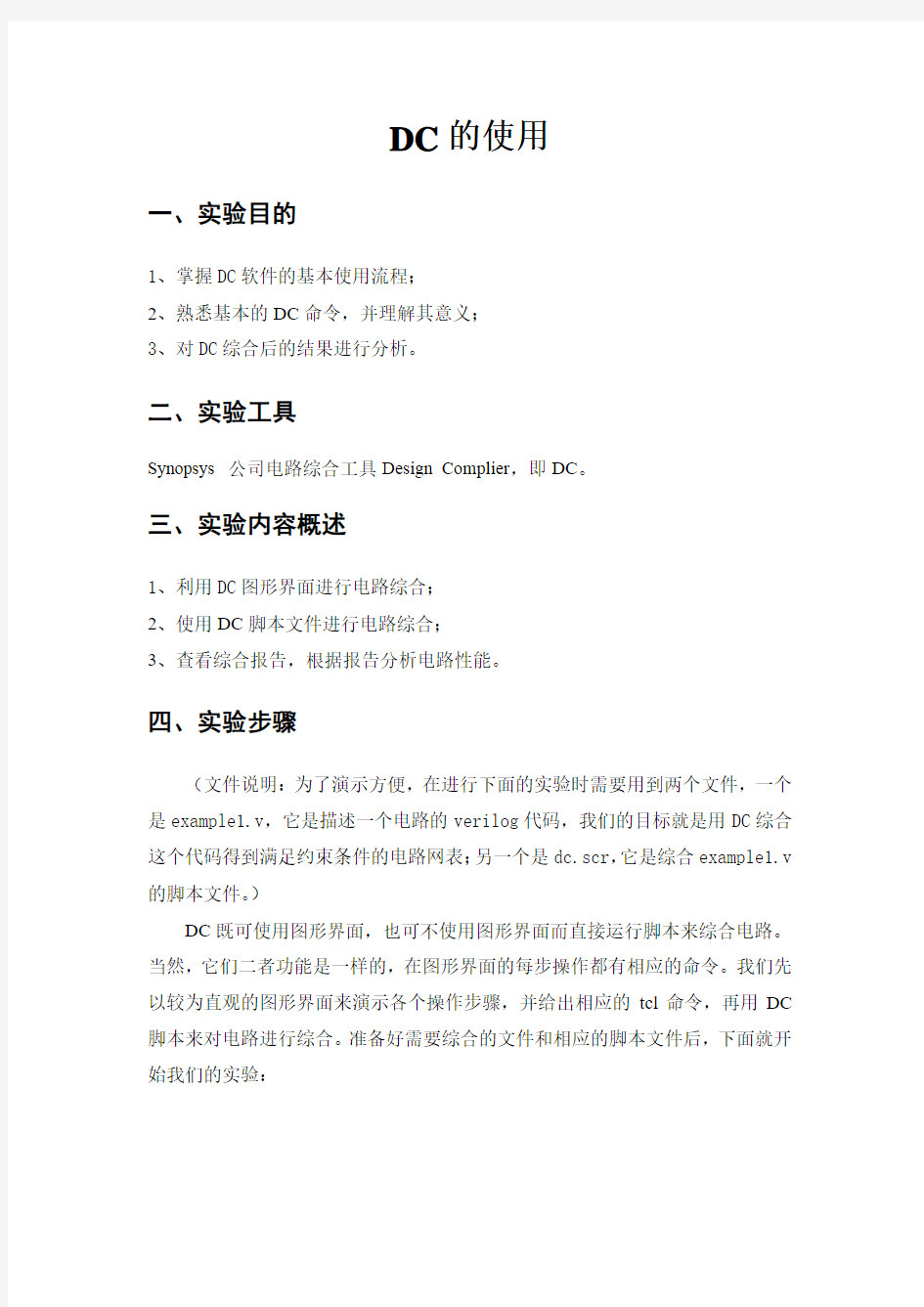

打开一个终端窗口,键入命令dv –db_mode,回车:

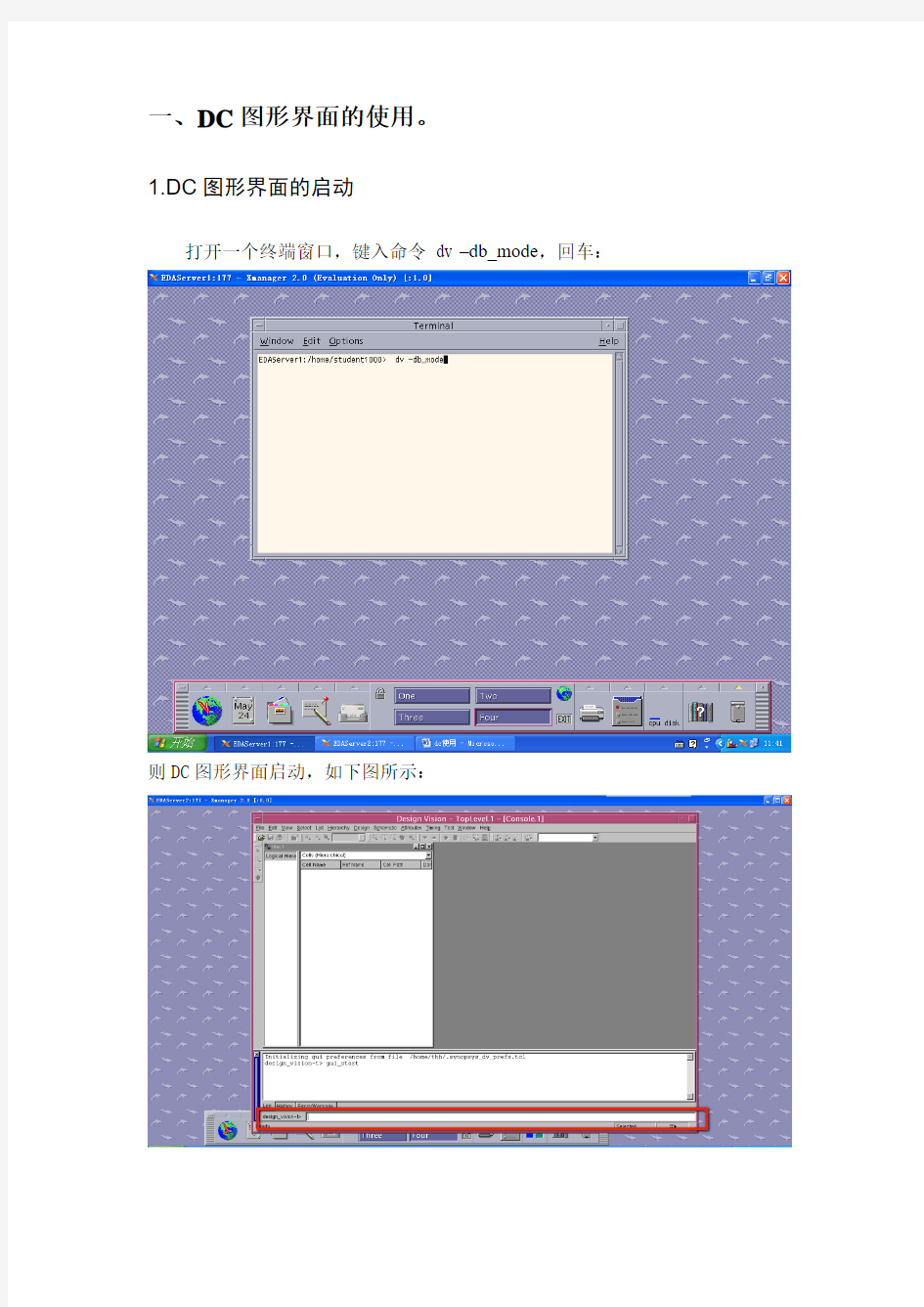

则DC图形界面启动,如下图所示:

红框处是DC的命令输入框,所有以下在图形界面上的操作都可以在这个命令输入框中输入相应的命令来完成。

选择Help-----→Man Pages可以查看DC的联机帮助。相应指令:man。例:man man表示查看man命令的帮助。man create_clock表示查看creat_clock命令的帮助。

2.设置库文件

选择File----→Setup

打开如下界面:

接下来就要在这设置库文件了,在设置之前我们有必要对这些库做个简单说明:

●search_path是要指定综合工具的搜索路径。

●target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

●synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

●link_library是链接库,它是DC在解释综合后网表时用来参考的库。一般

情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

●symbol_library为指定的符号库。

我们的库文件设置如下:

search_path:list /tools/lib/smic25/feview_s/version1/STD/Synopsys \

/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys target_library:smic25_tt.db

link_library :* smic25_tt.db

symbol_library :smic25.sdb

设置完毕,点击OK退出该窗口。

以上设置过程也可以在命令窗口键入命令来设置,相应命令为:

set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \

/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]

set target_library { smic25_tt.db }

set link_library { * smic25_tt.db }

set symbol_library { smic25.sdb }

3.读入verilog文件

选择File--- Read

在打开文件对话框中选中要打开的文件,在这里我们选中sync_FIFO.v文件。

在Log框中出现successfully字样表明读入文件成功。相应命令:read –format verilog /home/eda000/dc/sync_FIFO.v (注:这是待打开文件的路径)。有时可能要读入多个文件,每个文件中都有电路module,则读入后要指定这些module中的最顶层module,例如顶层module名是top,则可以键入命令:current_design top

来指定它。

图。

4.设置约束条件

4.1设置时钟约束

在symbol 图上选中clk_i 端口: 选择Attributes----- Specify Clock :

上升沿0ns,下降沿10ns:

点击OK,时钟约束设置完成。

以上操作的相应命令:create_clock –name clock –period 20 -waveform{0 10}

[get_ports clk_i]。

4.2设置复位信号约束

在symbol图中选中rst_i端口(在本例中它是复位端口),选择

Attributes-----→Optimization Directives-----→Input Port

[get_ports rst_i]。

同时选中输入端口we_i,rd_i,data_i

选择Attributes----→Operating Environment-----→Input Delay

设置Relative to clock为clock(即我们刚才加约束的时钟信号),并设置上升延迟为12ns(根据经验,该值是时钟周期的60%,本例中设置了时钟周期为

20ns,20*0.6=12ns。

相应命令:set_input_delay 12 -clock clock [get_ports [list we_i rd_i data_i]]。

4.4设置输出端口约束

在symbol图上选中输出端口full_o、empty_o、data_o。

选择Attributes-----→Operating Environment-----→Output Delay:

设置输出延迟为12ns。

或可以键入相应指令:set_output_delay 12 –clock clock [all_outputs]。4.5设置面积约束

选择Attributes-----→Optimization Constraints-----→Design Constraints

设置Max area的值为0,表明让DC向电路面积为0的方向来优化电路,使面积最小。当然,面积为0是达不到的。Max fanout为4,Max transition为0.5

(具体含义参见SYNTHESIS.pdf)。

或键入相应命令:set_max_area 0,set_max_fanout 4,set_max_transition 0.5。5.综合优化

选择Design----- Compile Design

点击OK。相应命令:compile –map_effort medium。

在Log框中出现Optimization Complete字样表明优化完成,如下图所示。

6.查看报告

6.1查看面积报告

选择Design----- Report Area。

点击OK 。相应命令:report_area 。

报告总面积为108787.710938,单位是平方微米。

选择Design----- Report Constraints

告综合后所有不满足原先设置的约束条件的条款。

从下图可以看出有max_area(最大面积)和max_fanout两项约束不满足,因为我们设置的最大面积约束是0(见4.5),而实际综合出的电路面积是108787。该项violator是合理的。由于rst_i是复位信号其扇出非常高,同时由于我们之前对rst_i信号设置了don’t_touch,DC在综合的过程中没有对该信号进行优化,所以在DRC的时候会违反我们设定的max_fanout(最大扇出)。如果还存在其它violators,说明前面的约束设置不合理或电路设计不合理,需要对其修改,最终

要求除max_area violator外没有其它violators。相应命令:report_constraint

–all_violators。

6.3时序报告

选择Timing----- Report Timing

点击OK。相应命令是:report_timing

报告的是最大延迟路径,这里我们看到红圈中所标slack值为5.28,是正值,说明电路满足时序要求;如果该值是负的,就表明电路不满足我们前面所设的时

序约束条件,要更改原设计或调整约束。

7.保存文件

现在DC综合的工作已基本结束,我们需要保存综合后产生的几个文件,如

电路网表和延迟文件等,以备后续工作所需。

选择File----- Save As:

彩机工作的7个步骤: 1、充电通过充电电极丝给感光鼓表面充上高压电 2、曝光利用感光鼓表面的光导特性,感光鼓表面曝光,形成一定形状不等位的电荷区 3、显影碳粉颗粒在电场作用下吸附在感光鼓表面被曝光的区域 4、转印当打印纸通过转印辊时,被带上与碳粉相反的电荷,使碳粉颗粒按一定 的形状转印到纸上 5、分离纸从感光鼓和转印辊上分离出来 6、定影已经印上文字的打印纸上的碳粉颗粒,需要熔化才能渗透到纸里 7、清洁感光鼓表面的碳粉并未完全被转印到纸上,通过刮刀清理后,并可完成 下一轮转印成像过程。 打印常见问题(人为原因) 1.文件有明显问题(破图,掉字,白页,文件不完整,乱码,出边),但打印前没有预览检查而造成打废; 2. 文件正反错(拼错,位置错,头对头,头对脚设置问题,打印正反错位而导 致废P,纸尺寸有差别而导致错位较大 3.文件尺寸问题,尺寸太满,打不满或太靠边,图像会被打掉 4.印制单上设置与文件设置不符(克度,尺寸,正反面,页数) 5.操作员打完单子后没有提交,其他操作员又打印一遍,造成多打 6.用错纸,克度,铜版,哑粉用错

7.纸中混其它不同克度的纸,导致打废 8.单双面打错,导致单打双,双打单 9.打印薄纸夹纸,特别是80g,128g纸,打印前要多洗纸 10.份数不对,有时输入份数时会输不上去,输入后腰检查份数是否正确11.打印图像有质量问题,但是操作员发完作业后,并没有检查成品图像质量,而造成废P 12.特别强调的是正反套位的问题,打印样后腰检查正反套位是否正常,不正常一定要调整,一般在服务器上调整。 常用配件及耗材

日常操作规 1.颜色管理:a.早班人员每天上午必须校色,并把校色后打印样登记存放b.更换重要零配件(鼓,载体,一次转印辊,二次转印辊,IBT等)候及大修后,要执行校色流程 c.校色步骤(略) 2.调整双面错位: 进入步骤:钥匙键(11111)---- Tools pathway---- machine defaults 2 --- alignment adjustment -----Paper tray 1 --- alignment profile1 ----- Lead registration(调整左右错位值) side registration(调整上下错位值) 在出纸方向,图像太靠下,要调整左右值,按加;图像靠上,按减 注:调整左右值,没有作用时,说明纸尺寸不符合标准(太短或太长)3.电极丝原则上每打印5000P清洁一次,实际中每天要清洁一次 4.每日检查耗材的使用状况,及时备用或更换 5.机器大批量打印时,操作员应时刻监看设备运转情况,以防出现大批量打印错误和复本质量问题 6.大批量打印时,请经常清理接纸盘,总是等到EMPTY OCT提示才拿纸很容易造成接纸盘被压坏 7.打印到一半急停,按UI上粉红色的键或者纸盒是最好的方法,千万不要拉门,这样容易造成卡纸 8.有些人为不可判断的故障恢复,可以重新启动打印机和服务器 9.换鼓时贴上标签(日期, 当前总P数) 10.换新鼓后要打印200P左右再校色 11.加硅油量不要太多,与油槽颈部平行即可 12.IBT支架上右侧红色辊每打印10万P顺时针转一格 13.要轻推纸盒及大抽屉 14.每周日对DC8000进行大的维护保养,即执行DC8000每周日常维护规15.打印机台面上严禁放置矿泉水,酒精等液体,以防漏水造成电路板烧坏 取卡纸的方法,取卡纸请遵照两个原则:

DNDC模型使用手册 ( 9.3版本 ) 新罕布什尔大学 地球海洋与空间研究所 2010年1月15日

致谢 我们感谢美国国家科学基金会(NSF)、美国航天与空间总署(NASA)、美国农业部(USDA)、环境保护署(EPA)、国家海洋与大气总署(NOAA)及国家大气研究中心(NCAR/UCAR)自1989年以来为发展DNDC模型所提供的持续支持。世界许多国家的科研人员为该模型的发展做出了贡献,他们或为模型验证提供数据,还为模型添加新的功能。这些研究者包括李长生(Changsheng Li美国)、斯苐夫·富罗京(Steve Frolking美国)、罗伯特·哈里斯(Robert Harriss美国)、里查德·泰瑞(Richard Terry美国)、麦克·凯雷(Michael Keller美国)、帕提克·葛瑞尔(Patrick Crill美国)、安姬·卫紫(Antje Weitz德国)、泰德·派克(Ted Peck美国)、卫理·温岚德(Wayne Wendland美国)、大卫·金克森(David Jenkinson英国)、王英平(Yingping Wang澳大利亚)、庄亚辉(Yahui Zhuang 中国)、戴昭华(Zhaohua Dai中国)、罗尔·布兰特(Roel Plant 荷兰)、周叶(Ye Zhou中国)、张宇(Yu Zhang中国)、林清华(Qinghua Lin中国)、王晓科(Xiaoke Wang中国)、富罗里安·史坦格(Florian Stange德国)、克劳斯·布特巴赫-巴尔(Klaus Butterbach-Bahl德国)、汉斯·帕潘(Hans Papen德国)、索菲亚·泽克美斯特-波坦斯顿(Sophie Zechmeister-Boltenstern奥地利)、郑循华(Xunhua Zheng中国)、孙建中(Jianzhong Sun中国)、秦晓光(Xiaoguang Qin中国)、斯蒂夫·佳伟斯(Steve Jarvis英国)、布朗尼·斯依德(Bronwyn Syed英国)、劳娜·布朗(Lorna Brown英国)、雷·德斯佳丁(Ray Desjardins加拿大)、沃特·斯密思(Ward Smith加拿大)、布莱安·格兰特(Brian Grant 加拿大)、 罗·萨斯(Ron Sass美国)、黄燿(Yao Huang中国)、蔡祖聪(Zucong Cai中国)、康国鼎(Guoding Kang中国)、佳瑞亚· 波佳瓦特(Jariya Boonjawat泰国)、鹤田治雄(Haruo Tsuruta 日本)、泽本卓治(Ta kuji Sawamoto 日本)、小林和彦(Kazuhiko Kobayashi日本)、邱建军(Jianjun Qiu中国)、拉福·柯斯(Ralf Kiese德国)、卡尔·特伦蒂(Carl Trettin美国)葛荪(Sun Ge美国)、徐成一(Cheng-I Hsieh台湾)、雷纳德·莱姆克(Reynald. Lemke加拿大)、瑟雷德·萨喀(Surinder Saggar新西兰)、罗波·安德欧(Robbie Androw新西兰)、阿温·缪斯(Arvin Mosier美国)、卡罗斯·爱得阿多(Carlos Eduardo巴西)、程根伟

DC/DC 模块电源 应用手册 广州德励电子科技有限公司 二零零七年三月二十二日

目 录 一、基本术语解释 (1) 输入电压范围(Input Voltage Range) (1) 负载电压调整率(Load Voltage Regulation) (1) 输入(线性)电压调整率(Line Voltage Regulation) (1) 输出电压精度(Ouput Voltage Accuracy) (1) 输入和输出波纹电压(Input and Output Ripple) (1) 输入与输出隔离电压(Input to Output Isolation) (1) 绝缘阻抗(Insulation Resistance) (1) 全负载效率(Efficiency at Full Load) (1) 温度漂移(Temperature Drift) (1) 温升(Temperature above Ambient) (1) 开关频率(Switching Frequency) (1) 空载功耗(No Load Power consumption) (1) 隔离电容(Isolation Capacitance) (1) 平均无故障时间(Mean Time Between Failure)[MTBF] (1) 躁声(Noise) (1) 工作温度范围(Operating temperature range) (2) 二、电源的设计及选用 (3) 确定电源规格 (3) 系统配电设计 (4) 三、电源的测试 (7) 开尔文四端测试法 (7) 模块的性能 (7) 四、电源的应用 (11) 隔离(Isolation) (11) 串联使用(Connecting DC/DC Converters in Series) (11) 并联使用(Connecting DC/DC Converters in Parallel) (11) 模块并联使用的推荐值 (12) 滤波(Filtering) (12) 输出滤波计算 (12) 限制涌浪电流(Limiting Inrush Current) (13) 容性负载 (13) 隔离电容和漏电流 (13) 过载保护 (14) 输入欠压保护 (15) 无负载过压上锁 (15) 输入短路保护 (15) EIA-232接口 (16) 隔离数据采集系统 (16) 远距离传输 (16) 减小噪声 (17) 电磁兼容 (17)

说明:本教程在ubuntu10.04 之后,一直到ubuntu11.10 上验证成功,在之前的版本应该也以。 首先表示歉意。由于之前发的那个教程在破解的地方少截了一张图,部分人无法找到文件,造成无法破解,对那些已经下载了的朋友造成误导,表示歉意。为了能使更多的人正确破解并应用这个强大的软件,所以在此重新安装一次,并编写教程,顺便改正上次其他的几个小错误。 1、准备安装文件(setup 文件夹),内容如下图: 2、在主目录下建立soft 文件夹,并在soft 文件夹下建立dc2012,在dc2012 下新建dc、scl 文件夹,同时把setup 文件夹也拷贝到soft 文件夹下(本教程中,主目录为lbq 文件夹,在上步骤中,已经把setup 文件夹拷贝到soft 文件夹下了)。 3、由于早期的ubuntu 默认没有安装csh,需要先打开终端,运行sudo apt-get install csh,11.04版之后的好像都默认安装了。然后在ubuntu 软件中心中搜索wine,并安装成功(在后面的破解中需要用到wine)。 4、开始安装。如下图,按照图中所示路径,进入到该文件夹中,右键单击setup.sh,“” 点击属性,打开选中允许以程序执行文件(E)”。 权限标签, “ “”

5、右键单击setup.sh,“” 点击打开,如下图6“” 、点击运行,如下图: 7“ 、点击Start”,如下图:

8、选择所要安装软件dc “ 的原程序路径。点击Browse...”,选择路径如下图所示: 9“ 、点击Done”,如下图所示:

10“ 、一路Next”,遇到的几处选择如下几幅图所示,紫色表示选择。

max_transition可以定义为上升或下降电阻和线网负载的乘积,除了工艺库中提供的,用户也可自己定义,而实际采用的是最严格的那个定义值。 相比较max——transition并不直接控制线网的实际电容,而max_capacitance作为直接控制电容的限制而提出的。但是其cost function是基于总的电容而不是瞬态时间。二者可以同时定义。没有违反约束的定义是:驱动pin或者是port的max capacitance大于或者是等于所有被驱动管的电容之和。 Max transition和max fanout 和max capacitance可以用来决定设计中的buffer个数。―――影响时间参数 优化约束―――对时间的约束优先于对面积的约束。在满足对面积的约束之前,会尽量的考虑满足对时间约束条件的满足。 对时间的约束―――-时序电路中通过对时钟的定义来达到,set input delay和set output delay。 ――――组合电路通过对set max delay和set min delay来设定点点之间的时间延迟,max delay通过设定set max delay和creat clock来达到; 而min delay通过设定set min delay和对保持时间的要求来达到。其中的使用set fix hold来固定保持时间。 优化的过程就是减少代价函数的过程――包括设计规则代价函数和优化代价函数。Max delay cost;min delay cost;max power cost;max area cost; 其中max delay cost是代价函数中具有最优权。 Max delay cost的计算:最差的违背和每个路径组的权重之积――worst violation;path group; 当设计不能满足时序单元的建立时间的要求的时候,违背就发生了。一般,把由一个时钟约束的路径组合成一个路径组,这样每个时钟都建立了一个单独的路径组,而剩余的路径组合成默认的路径组,如果在没有时钟的情况下,所有的路径都组合成一个默认的路径组。而综合总是针对路径进行的,所以很容易给每个路径定义其权重。如:max delay cost=1×1+1×2+1×3=6 min delay cost次重。与路径无关,是所有的最差的min delay违背之和,当实际的延迟时间小于设定的期望的延迟时间的时候,违背就发生了。如:min delay=1+2+3=6 max power是用于ECL电路中。 综合时候的时钟设定: 设定时钟树的时候,使用set dont touch network来设定时钟的dont touch参数值,防止 buffers。 Synopsys的STA不报告时序单元中针对时钟管脚的延迟(认为是理想状态-0)。如果时钟经过门单元的话,则不能认为时钟延迟是0,所以也要设定set clock skew-proagated选项来得到非零的时钟延迟,如果ASIC提供商已经定义了相对于时序单元管脚的潜在的时钟skew的上限的话,可以用set clock skew -uncertainty来定义skew。在设定完时钟之后,我们要使用set input delay和set output delay-option来设定输入输出端口的时间设定。用set multicycle path来设定复合时钟。

DC使用说明 文件说明:在进行下面的演示时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v的脚本文件。这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。 一、DC图形界面的使用。 1.DC图形界面的启动 1.1 打开一个终端窗口,写入命令dv –db_mode,敲入回车。 则DC图形界面启动,如下图所示

红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。 选择Help----- Man Pages可以查看DC的联机帮助。相应指令:man。例:man man表示 查看man命令的帮助。man create_clock表示查看creat_clock命令的帮助。

2.设置库文件 选择File---- Setup 需要设置以下库文件,如下图。 相应指令: set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library { smic25_ff.db } set link_library { smic25_ff.db smic25_ss.db } set symbol_library { smic25.sdb }