第二单元 集成电路芯片封装可靠性知识—郭小伟

(60学时)

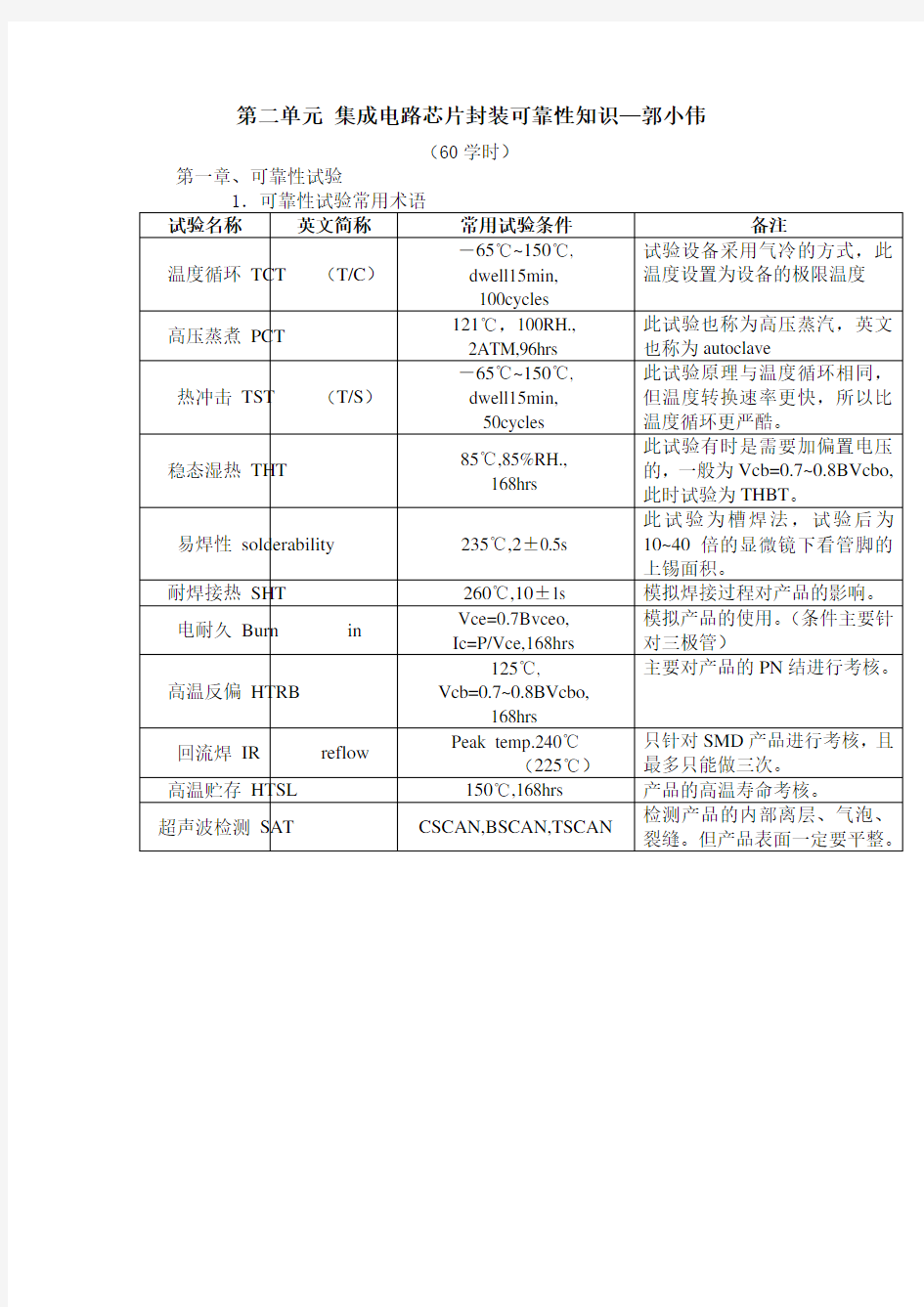

第一章、可靠性试验 1.可靠性试验常用术语

试验名称 英文简称

常用试验条件 备注 温度循环 TCT (T/C )

-65℃~150℃, dwell15min, 100cycles 试验设备采用气冷的方式,此温度设置为设备的极限温度 高压蒸煮 PCT

121℃,100RH., 2ATM,96hrs 此试验也称为高压蒸汽,英文也称为autoclave 热冲击 TST (T/S ) -65℃~150℃, dwell15min,

50cycles

此试验原理与温度循环相同,但温度转换速率更快,所以比温度循环更严酷。 稳态湿热 THT 85℃,85%RH.,

168hrs

此试验有时是需要加偏置电压的,一般为Vcb=0.7~0.8BVcbo,此时试验为THBT 。 易焊性 solderability 235℃,2±0.5s 此试验为槽焊法,试验后为10~40倍的显微镜下看管脚的

上锡面积。

耐焊接热 SHT

260℃,10±1s 模拟焊接过程对产品的影响。

电耐久 Burn in Vce=0.7Bvceo, Ic=P/Vce,168hrs 模拟产品的使用。(条件主要针

对三极管)

高温反偏 HTRB 125℃, Vcb=0.7~0.8BVcbo, 168hrs 主要对产品的PN 结进行考核。回流焊 IR reflow Peak temp.240℃ (225℃) 只针对SMD 产品进行考核,且

最多只能做三次。

高温贮存 HTSL 150℃,168hrs

产品的高温寿命考核。

超声波检测 SAT CSCAN,BSCAN,TSCAN 检测产品的内部离层、气泡、裂缝。但产品表面一定要平整。

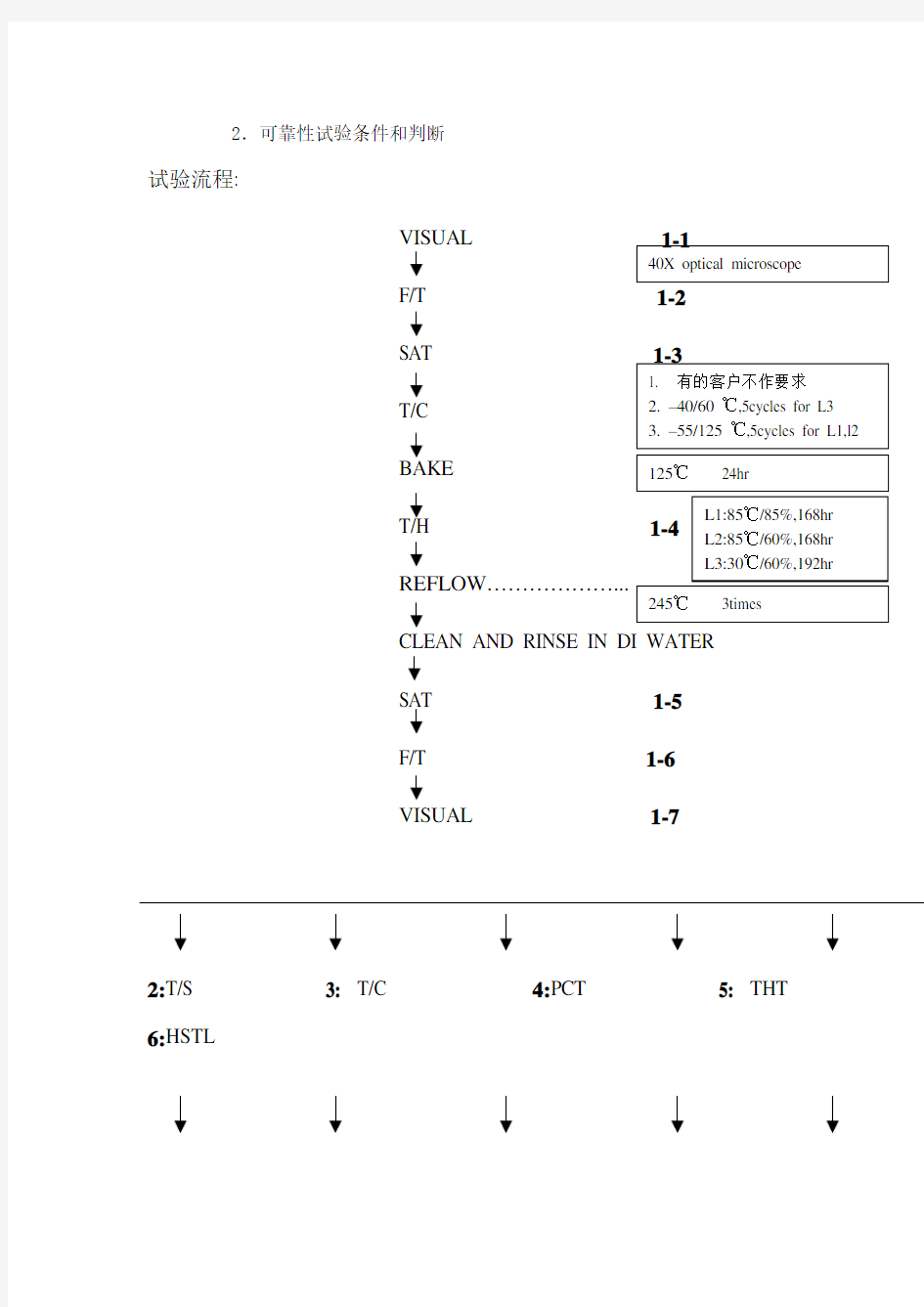

2.可靠性试验条件和判断

试验流程:

F/T SAT 1-4 1-5

F/T 1-6

1-7

2:T/S 3: T/C 4:PCT 5: THT 6:HSTL

以客户为代表为例子:

客户1:

precondition TCT –55/125℃,5cycles for L1,l2,L3 Ac:Re=(0,1)

T/S: –55/125℃,5min,100cycles sample size: 45 Ac:Re=(0,1)

T/C: –55/125℃,10min,200cycles sample size: 45 Ac:Re=(0,1)

PCT: 121℃/100%rh,15Psig,96hr sample size: 45 Ac:Re=(0,1)

THT: 85℃/85%,168/500/1000hrs sample size: 45 Ac:Re=(0,1)

客户2:

precondition T/C –40/60℃,5cycles forL3 Ac:Re=(0,1)

T/S: –55/125℃,5min,100cycles sample size: 45 Ac:Re=(0,1)

T/C: –65/150℃,10min,500cycles sample size: 77

Ac:Re=(0,1)

PCT: 121℃/100%rh,15Psig,168hr sample size: 77 Ac:Re=(0,1)

THT: 85℃/85%,1000hrs sample size: 77 Ac:Re=(0,1)

HTSL: 150℃,1000hrs sample size:77 Ac:Re=(0,1)

HAST: 130℃/85%rh,168hr sample size: 77 Ac:Re=(0,1)

客户3:

precondition T/C –40/60℃,5cycles forL3 Ac:Re=(0,1)

T/S: –55/125℃,5min,50cycles sample size: 24 Ac:Re=(0,1)

T/C: –65/150℃,15min,50cycles sample size: 24 Ac:Re=(0,1)

PCT: 121℃/100%rh,15Psig,168hr sample size: 24 Ac:Re=(0,1)

HTSL: 150℃,168hrs sample size:24 Ac:Re=(0,1)

客户4:

precondition T/C N/A ,L1 Ac:Re=(0,1)

T/C: –65/150℃,15min,100/500cycles sample size: 45 Ac:Re=(0,1)

PCT: 121℃/100%rh,15Psig,168/336hr sample size: 45 Ac:Re=(0,1)

SOLDER DUNK: 245℃10SEC sample size: 45 Ac:Re=(0,1)

客户5:

QFP 做 precondition,DIP不做precondition

precondition T/C N/A,L3 sample size:184 Ac:Re=(5,6)

T/C: –65/150℃,15min,200/500cycles sample size: 45 Ac:Re=(0,1)

PCT: 121℃/100%rh,15Psig,168hr sample size: 45 Ac:Re=(0,1)

HTSL: 150℃,168/500/1000hrs sample size:45 Ac:Re=(0,1)

SOLDER DUNK: 245℃5SEC sample size: 15 Ac:Re=(0,1)

塑料密封等级

塑料密封等级:在装配现场拆包后地面存放期标准试验条件

LEVEL 1 在小于30C/85%相对湿度无期限 85C/85% 168小时

LEVEL 2 在30C/60%条件下1年85C/60% 168小时

LEVEL 3 在小于30C/60%条件下1周 30C/60% 192小时加速=60C/60% 40小时

SAMPLE:50

塑料密封等级试验步骤:

1. DC和功能测试

2.外观检查(在80倍以上显微镜下检查)

3. SAT扫描

4. BAKE 125C/24小时

5.做LEVEL 相应条件的试验

6.在15分钟后和4小时内做3次回流焊—注意温度曲线必须提供和符合JEDEC标准。7.外观检查(在80倍以上显微镜下检查)--不可以有裂缝。

8. DC和功能测试—注意如果无法通过测试要验证是否和塑料密封有关部门

9. ------可以做BAKE 150C/24小时,冷却2小时后做未通过产品的功能测试来验证10. SAT扫描----判断依据:

A 芯片表面不可有离层

B镀银脚精压区域不可有离层

C产品内部不可有进水后离层图像(图形上表现该有图像却隐隐约约或同被划伤的痕迹)

D引脚与引脚之间在胶体内部分,离层相连的面积不可超过胶体正面面积的10%或引脚通过离层相连的脚数不可超过引脚总数的1/5

E芯片四周导电胶造成的离层不可超过胶体正面面积的10%

集成电路封装在设计过程中可靠性的考虑

封装所用主要材料:

? 磨划片所用薄膜:型号、纯度、厚度、粘度

? 引线框架:材质、厚度、防拖性、电性能、传热性、热膨胀系数、镀层材料、镀层厚度、镀层质量

? 芯片粘接剂:型号、电性能、传热性、抗疲劳、热膨胀系数、装片牢度? 焊线:型号、HAZ、电性能、传热性、拉力、弧度

? 塑封料:型号、热硬度、传热性、电性能、玻璃化温度、线膨胀系数、离子纯度、填料比例、吸水率、抗弯强度、粘结力、阻燃性、对应封装别水汽敏感等级

? 电镀成份:SN/Pb的比例

集成电路封装在设计过程中可靠性的考虑

封装工艺控制要关注的方面:

? 磨片进刀速度、转速、磨片厚度、去离子水电导率

? 划片进刀速度、转速、切割深度、防静电措施

? 装片压力、顶针、吸嘴、银浆头的选用

? 球焊第一点参数、焊针的选用、温度、弧度

? 塑封模具的设计如顶杆位置、脱模角度、侧面粗糙度及塑封温度、压强、速度

? 后固化温度、时间

? 冲塑刀片与胶体的距离

? 电镀去飞边工艺、电镀电流、前处理、后处理、镀液成份

? 切筋成形时产品胶体受力情况的监控(显微镜和SAT)、共面性、防静电? 对薄形产品激光打印打印深度的控制

? 对薄形但面积较大胶体产品真空包装

封装工艺控制要关注的方面(球焊后合理的金线拉力下限):

? 集成电路封装中球焊后金线拉力最低要求,应该考虑金线在塑封时的受力情况

和运输及操作时的合理振动。金线在塑封时的受力不仅与金线的长度、直径有关,还与塑封料的粘度、塑封时的注射速度有关,并与塑封产品的几何尺寸、注胶口的形状和尺寸等诸多因素有关。应该按照不同封装形式的产品给出球焊后金线拉力最低要求,并给出最佳的范围。

下面是我们对不同封装别(均指传统模要求)拉力的模拟计算结果(部分内容)

在实际工艺标准控制中对25微米的金线拉力下限我们建议通常可以是5g

集成电路封装在设计过程中可靠性的考虑

封装工艺控制要关注的方面(超声SAT):

超声图片观察和判断:

? 芯片表面不可有离层

? 镀银脚精压区域不可有离层

? 产品内部不可有进水后离层图像(图形上表现该有图像却隐隐约约或同被划伤的痕迹)

? 引脚与引脚之间在胶体内部分,离层相连的面积不可超过胶体

正面面积的20%或引脚通过离层相连的脚数不可超过引脚总数的1/5

? 芯片四周导电胶造成的离层在做可靠性试验通过或做Bscan时未超出芯片高度的2/3不判为不合格

? 判断超声图片时要以波形为准,要注意对颜色黑白异常区域的波形检查。

下面的图片均为不正常:

集成电路封装常用可靠性试验对应的缺点项目

第二章、失效分析

1.集成电路封装失效分析的常规流程

1. 接受分析请求

2. 在数据库中登记

3. 收集相关的信息

4. 对失效的产品确认

5. 对漏电流超差的产品在125度~150度的温度下烘烤2小时,再测试是否通过

对功能失效的产品在125度~150度的温度下烘烤24小时,再测试是否通过

6. 在80倍显微镜下检查外观

7. 开短路测试,检查对应PIN是否开短路或对应内阻异常

8. X-RAY,检查打线情况

9. C-SAM,检查分层情况和内部气泡

10. Decapsulation (开帽)or Cross-section(做对应分层区域横切面)

11. 检查芯片表面、球状质量、裂缝、扫描电子显微镜(SEM)检查焊点形貌、结构、沾污、腐球后检查是否有压区凹陷

12. 更多的检查方法和试验方案

13. 结论和图片记录在数据库中

14. 出具报告

15. 存入档案

2.集成电路封装失效分析的常用方法

1. 立体或金相显微镜下检查形貌、结构

2. 开短路测试,检查对应PIN是否开短路或对应内阻异常

3. X-RAY,检查打线情况、焊点错位、碰线、塌丝、球脱、点脱

4. C-SAM,检查分层情况和内部气泡

5. 扫描电子显微镜(SEM)检查焊点形貌、结构

6. 红外热像仪检查温度分布

集成电路封装失效分析的常用方法还有

? 表面形貌:

? 表面轮廓仪(Surface profiler) 器件、电路板变形等

? 激光轮廓仪(Laser profiler) 焊膏印刷尺寸,引脚平整度等

? 扫描超声显微镜(C-SAM)· 各种行貌观测

? 力学性能:

? 推力/拉力(shear/pull test) 焊线、贴片、焊接力学性能等

? 材料试验机(Mircotester) 材料力学性能等

? 粘度计(Viscosity measurement) 焊膏、贴片胶粘度测量等

? 成份分析:

? 化学分析(CA) 定量分析焊料主成份;助焊剂、稀释剂中卤素含量;封装、组装用金属合金材料的主成份等。

? 电子能谱/波谱·(EDX/WDX) 半定量分析元素成份、杂质含量、微区成份等

? 卢瑟辐背散射(RBS) 分析镀层成份、厚度等

? 等离子发射光谱(ICP) 定量分析焊料杂质成份等

? X-射线荧光分析镀层成份、厚度等

? 热力学

? 扫描差热分析(DSC) 分析贴片胶等的玻璃化转变温度、焊料熔点等? 热天平(TGA) 分析胶等材料固化过程的挥发,助焊剂挥发等

? 热机械分析仪(TMA) 测量热膨胀系数、玻璃化转变温度等

? 动态热机械分析(DMA) 测量杨氏模量、玻璃化转变温度等

? 结构

? 透射电子显微镜(TEM) 焊点微观缺陷、微结构、物相鉴定等? 富立叶变换红外光谱(FTIR) 分析有机物如助焊剂残留等? 拉曼光谱(Raman spectroscopy) 分析有机物如助焊剂残留等

3.集成电路封装常规失效的可能原因

? silicon substrate 硅基体

? deformation 变形

? strain 应力

? wrap 翘曲

? scratch 擦伤

? resistivity 电阻率

? crystal defect 晶体缺点

? dislocation 断层

? stacking fault 层错

? contamination 污染

? surface contamination 表面污染

? heavy metals 重金属污染

? carbonoxygen 碳氧化物

? oxide film formation 氧化膜薄层

? contamination 污染

? interface state 界面态

? alkaline ion 碱金属离子

? defect 缺点

? crack 裂缝

? pinhole 针孔

? process induced defect 过程诱生缺陷? film thickness 薄膜厚度

? non uniformation 厚度不均? excess insufficiency 超过范围

? shape 形状

? steped oxide film 阶梯式氧化膜

? film quality 膜质量

? photolithography 照相平板

? mask 光掩模板

? misalignment 未对准

? scratch 划伤

? dust 沾污

? photo resist 照相阻抗

? adhesive 粘着性? pinhole 针孔? crack 裂缝? residue 残存物? foreign particles 外来小颗粒

? etching 蚀刻

? undercut 过蚀

? insufficiency 不足

? temperature 温度

? chemical residue 化学残余物

? exposure development 暴光程度

? EXCESS/insufficiency 过头/不足

? junction formation 接合处构造

? diffusion 扩散

? thermal stress 热应力

? depth 深度

? bulk destruction 大量失效

? interface state 界面态

? stacking fault 层错

? dislocation 断层

? ion implantation 离子注入

? annealing 退火

? implanted dose 注入的剂量

? metallization 金属化

? thickness 厚度

? adhesive 粘着性

? step coverage 阶梯式覆盖

? defect 缺点

? scratch 擦伤

? void 空洞

? hillock 小丘

? electron migration 电迁徙

? contamination 沾污

? corrosion 腐蚀

? adhesion 粘着力

? defective contact 接触不量

? misalignment 未对准

? soil 粘污

? al penetration 铝渗透

? die bonding 装片

? material mismatch 材料失配

? gas generation 气体产生

? solid overflow 固体粒子超值

? floating foreign particles 漂浮的外来粒子? thermal strain 热应力

? cracked chip 芯片破裂

? inadequate strength 强度不够

? void 空洞

? temperature 温度

? surface contamination 表面沾污

? 表面压伤:

? 吸嘴与芯片接触面积过大

? 吸嘴沾污

? 装片膜过粘,真空过大

? 芯片破裂

? 装片压力过大

? 背面顶针面积过小

? 背面顶针顶出过高

? 导电胶量过多/少/不均

? 背面接触不良

? wire bonding 球焊

? wire scrap 金线残留

? misalignment 球焊飘移

? pressure 球焊压力

? crack 裂缝

? insufficient strength 强度不够

? contamination 沾污

? inadequate strength 强度不够

? temperature

? abnormal alloying 异常合金

? wire condition 金线条件

? abnormal loop 弧度异常

? scratch 擦伤

? inadequate tail processing 线尾处理不当

? sealing 封装

? stress to wire 金线冲力

? thermal stress 热应力

? wire drift 金线冲移位

? wire breakage due to void 气孔界面力造成金线冲断? resin strain 树脂应力

? chip strain 芯片受损

? cracked chip 芯片破裂

? seal 包封

? adhesion to frame 对框架的粘着力(分层)

? void 气孔

? crack 破裂

? foreign particles 外来小颗粒

? surface contamination 表面沾污

? solder 焊料

? internal gas 内部气孔

? impurities 不洁净? humidity 湿气

? Alpha particles α粒子

? other processes 其它过程

? poor solderability 可焊性

? external lead 外引脚

? bend 弯曲

? breakage 缺损

? die separation 产品分离

? contamination 沾污

? crack 裂缝

? adhesion to frame 胶体对体内框架的粘着力(分层)? plating 镀层

? rust 腐蚀

? residue 锡渣

? whisker 锡须

? oxidation 氧化

? operating environment 作业环境

? cosmic ray 射线

? radiation 辐射

? radiography X射线

? mechanical stress 机械受力

? shock 冲击

? vibration 振动

? assembly

? ultrasonic clean 超声

? soldering heat 焊接热

? atmosphere 大气

? atmospheric pressure 大气压力

? humidity 湿气

? gas 气体

? temperature 温度

? voltage/current 电压电流

? surge 浪涌

? noise 噪声信号

? static electricity 静电

4.开帽方法

原理:高分子的树脂体在热的浓硝酸作用下,被腐去变成易溶于丙酮的低分子化合物,在超声作用下,低分子化合物被清洗掉,从而露出芯片表层。

开帽方法:取一块不锈钢板,上铺一层薄薄的黄沙,(对于树脂体薄的产品不

必放沙)放在电炉上加热,砂温要达100-120度,将产品放在砂子上,芯片面向上,用吸管吸取少量的发烟硝酸(浓度>98%)。滴在树脂体表面,这时树脂表面起化学反应,且冒出气泡,待反应稍止再滴,这样连滴5-10滴后,用镊子夹住,放入盛有丙酮的烧杯中,在超声机中清洗2-5分钟后,取出再滴,如此反复,直到露出芯片为止,最后以大量清水超声清洗。

注意:A,所有一切操作均应在通风柜中进行,且要戴好防酸手套。

B,产品开帽越到最后越要少滴酸,多清洗,以避免过腐蚀。

C,清洗过程中注意镊子勿碰到金丝和芯片表面,以免擦伤芯片。

D,根据产品或分析要求有的开帽后要露出芯片下面的导电胶.,有的则不必.

E,,最后以纯水和丙酮反复轮流超声清洗产品,以洗去丙酮和硝酸,最后在滤纸上风干。

5.超声原理

超声扫描显微镜:SAM,Scanning Acoustic Microscope

超声波:频率超过20KHz的声波,

超声波的典型特征:

碰到气体(离层)就100%全反射

在物质的分界面产生反射

横波:传播方向与振动方向垂直,不能在液体或气体中传播

纵波: 传播方向于振动方向相同, 可在液体中传播

超声波的优势所在:

可发现裂缝的最小厚度为0.13微米

可测量失效区域的尺寸、位置、形状

可以实时检测

安全:对人体无害

超声波弱点:

表面粗糙或内部有气泡、球状物(如塑料泡沫)的样品检测较困难 必须以液体为传播媒介

常用检测集成电路的项目:离层、芯片裂缝、胶体裂缝、气泡等

检测原理图:

检测方法:

A-SCAN

B-SCAN:

MOS 器件及其集成电路的可靠性与失效分析(提要) 作者:Xie M. X. (UESTC ,成都市) 影响MOS 器件及其集成电路可靠性的因素很多,有设计方面的,如材料、器件和工艺等的选取;有工艺方面的,如物理、化学等工艺的不稳定性;也有使用方面的,如电、热、机械等的应力和水汽等的侵入等。 从器件和工艺方面来考虑,影响MOS 集成电路可靠性的主要因素有三个:一是栅极氧化层性能退化;二是热电子效应;三是电极布线的退化。 由于器件和电路存在有一定失效的可能性,所以为了保证器件和电路能够正常工作一定的年限(例如,对于集成电路一般要求在10年以上),在出厂前就需要进行所谓可靠性评估,即事先预测出器件或者IC 的寿命或者失效率。 (1)可靠性评估: 对于各种元器件进行可靠性评估,实际上也就是根据检测到的元器件失效的数据来估算出元器件的有效使用寿命——能够正常工作的平均时间(MTTF ,mean time to failure )的一种处理过程。 因为对于元器件通过可靠性试验而获得的失效数据,往往遵从某种规律的分布,因此根据这些数据,由一定的分布规律出发,即可估算出MTTF 和失效率。 比较符合实际情况、使用最广泛的分布规律有两种,即对数正态分布和Weibull 分布。 ①对数正态分布: 若一个随机变量x 的对数服从正态分布,则该随机变量x 就服从对数正态分布;对数正态分布的概率密度函数为 222/)(ln 21)(σμπσ--?=x e x x f 该分布函数的形式如图1所示。 对数正态分布是对数为正态分布的任 意随机变量的概率分布;如果x 是正态分布 的随机变量,则exp(x)为对数分布;同样, 如果y 是对数正态分布,则log(y)为正态分 布。 ②Weibull 分布: 由于Weibull 分布是根据最弱环节模型 或串联模型得到的,能充分反映材料缺陷和 应力集中源对材料疲劳寿命的影响,而且具 有递增的失效率,所以,将它作为材料或零件的寿命分布模型或给定寿命下的疲劳强 度模型是合适的;而且尤其适用于机电类产品的磨损累计失效的分布形式。由于它可以根据失效概率密度来容易地推断出其分布参数,故被广泛地应用于各种寿命试验的数据处理。与对数正态分布相比,Weibull 分布具有更大的适用性。 Weibull 分布的失效概率密度函数为 m t m t m e t m t f )/()(ηη--?= 图1 对数正态分布

第二单元 集成电路芯片封装可靠性知识—郭小伟 (60学时) 第一章、可靠性试验 1.可靠性试验常用术语 试验名称 英文简称 常用试验条件 备注 温度循环 TCT (T/C ) -65℃~150℃, dwell15min, 100cycles 试验设备采用气冷的方式,此温度设置为设备的极限温度 高压蒸煮 PCT 121℃,100RH., 2ATM,96hrs 此试验也称为高压蒸汽,英文也称为autoclave 热冲击 TST (T/S ) -65℃~150℃, dwell15min, 50cycles 此试验原理与温度循环相同,但温度转换速率更快,所以比温度循环更严酷。 稳态湿热 THT 85℃,85%RH., 168hrs 此试验有时是需要加偏置电压的,一般为Vcb=0.7~0.8BVcbo,此时试验为THBT 。 易焊性 solderability 235℃,2±0.5s 此试验为槽焊法,试验后为10~40倍的显微镜下看管脚的 上锡面积。 耐焊接热 SHT 260℃,10±1s 模拟焊接过程对产品的影响。 电耐久 Burn in Vce=0.7Bvceo, Ic=P/Vce,168hrs 模拟产品的使用。(条件主要针 对三极管) 高温反偏 HTRB 125℃, Vcb=0.7~0.8BVcbo, 168hrs 主要对产品的PN 结进行考核。回流焊 IR reflow Peak temp.240℃ (225℃) 只针对SMD 产品进行考核,且 最多只能做三次。 高温贮存 HTSL 150℃,168hrs 产品的高温寿命考核。 超声波检测 SAT CSCAN,BSCAN,TSCAN 检测产品的内部离层、气泡、裂缝。但产品表面一定要平整。

芯片封装方式大全 各种IC封装形式图片 BGA Ball Grid Array EBGA 680L LBGA 160L PBGA 217L Plastic Ball Grid Array SBGA 192L QFP Quad Flat Package TQFP 100L SBGA SC-70 5L SDIP SIP Single Inline Package

TSBGA 680L CLCC CNR Communicatio n and Networking Riser Specification Revision 1.2 CPGA Ceramic Pin Grid Array DIP Dual Inline Package SO Small Outline Package SOJ 32L SOJ SOP EIAJ TYPE II 14L SOT220 SSOP 16L

DIP-tab Dual Inline Package with Metal Heatsink FBGA FDIP FTO220 Flat Pack HSOP28SSOP TO18 TO220 TO247 TO264 TO3

ITO220 ITO3p JLCC LCC LDCC LGA LQFP PCDIP TO5 TO52 TO71 TO72 TO78 TO8 TO92

PGA Plastic Pin Grid Array PLCC 详细规格PQFP PSDIP LQFP 100L 详细规格METAL QUAD 100L 详细规格PQFP 100L 详细规格TO93 TO99 TSOP Thin Small Outline Package TSSOP or TSOP II Thin Shrink Outline Package uBGA Micro Ball Grid Array uBGA Micro Ball Grid

常规封装失效分析流程1q5| `4q { H v 芯片设计版图芯片制造工艺制程封装测试,wafer,chip,ic,process,lay out,pack age,F A,QA G L g l ^ d 封装常规失效分析流程 1,接受上级或客户不良品信息反馈及分析请求,并了解客户相关信息。(指失效模式,参数值,客户抱怨内容,型号,批号,失效率,所占比例等,与正常品相比不同之处)芯片设计版图芯片制造工艺制程封装测试,wafer,chip,ic,process,lay out,pack age,F A,QA a/r m)_6D#X B 2,记录各项信息内容,以在长期记录中形成信息库,为今后的分析工作提供经验值。 3,收信工艺信息,包括与此产品有关的生产过程中的人,机,料,法,环变动的情况(老员工,新员工,班次,人员当时的工作状态,机台状况,工夹具,所采用的原材料,工艺参数的变动,环境温湿度的变动等) 通常有:装片机号,球焊机号,包封机号,后固化烘箱号,去飞边机号,软化线号,是否二次软化,测试机台,测试参数,料饼品种型号,引线条供应者及批号,金丝品种及型号,供应者等。https://www.doczj.com/doc/0f5428052.html,:? _ F8D8F 2F3J 半导体技术天地Semiconductor Technolo gy World] d ;R R;U R 4,失效确认,可用自已的测试机检测功能、开短路,以确认客户反映情况是否属实。 "s o v z4d*X | a;f 5,对于非开短路情况,如对于漏电流大的产品要彻底清洗(用冷热纯水或有机溶剂如丙酮)后再进行下述烘烤试验:125度烘烤24小时或175度烘烤4小时以上,烘箱关电源后门打开45度角缓慢冷却1小时后再测其功能,如功能变好,则极有可能是封装或者测试问题,对封装工艺要严查。https://www.doczj.com/doc/0f5428052.html, o*B\'d ~-M0j 6? n)z v ]3I/\\ y L8m 6,对于开短路情况,观察开短路测试值是开路还是短路,还是芯片不良,如是开路或短路,则要注意是第几脚开路或短路,待开帽后用万用表测量该脚所连的金丝的压区与脚之间的电阻,以判断该脚球焊是否虚焊。 4c\'{ J ` _ i a Y"U 7,对于大芯片薄形封装产品要注意所用材料(如料饼,导电胶)是否确当,产品失效是否与应力和湿气有关(125度烘烤24小时或175度烘烤4小时以上,烘箱关电源后,门打开45度角缓慢冷却1小时后再测其功能,如功能变好,则极有可能是封装或者测试的问题,对封装工艺要严查,如检查去飞边方式,浸酸时间等。)芯片设计版图晶圆制造工艺制程封装测试,wafer,chip,ic,design,fabrication,process,lay out,pac age,test,A,RA,QA m } U Y$P b h9n"j&ZQ 半导体技术天地Semiconductor Technolo gy World]"?$Z u0Z4\\ 8,80倍以上显微镜观察产品外形特征,特别是树脂休是否有破裂,裂缝,鼓泡膨胀。(注胶口,脚与脚之间树脂体和导电物) 半导体技术天地Semiconductor Technolo gy World] n:m b q z4_ 9,对所有失效样品进行X-RAY检查,观察金丝情况,并和布线图相比较,以判断布线是否错误。如发现错误要加抽产品确认失效总数并及时反映相关信息给责任人。芯片设计版图晶圆制造工艺制程封装测试,wafer,chip,ic,design,fabrication,process,lay out,pack age,test,FA,RA,QA Q/p c k L 芯片设计版图晶圆制造工艺制程封装测试,wafer,chip,ic,design,fabrication,process,lay out,pac age,test,A,RA,QA0Y,\\-n+O H |2R v 10,C-SAM即SA T,观察产品芯片分层情况。判断规范另见。样品数量为10只以内/批。 g0@ N/~ P\'] ? M4P m 11,开帽:对于漏电流大的产品采用机械方式即干开帽形式,其它情况用强酸即湿开帽形式。切开剖面观察金丝情况,及金球情况,表面铝线是否受伤,芯片是否有裂缝,光刻是否不良,是否中测,芯片名是否与布线图芯片名相符。样品数量为5只/批。对于开短路和用不导电胶装片的产品要用万用表检测芯片地线和基岛之间电阻检查装片是否有问题。对于密间距产品要测量铝线宽度,确认所用材料(料饼,导电胶,金丝)是否确当开帽后应该再测试,根据结果进一步分析。芯片设计版图芯片制造工艺制程封装测试,wafer,chip,ic,process,lay out,pack age,A,QA G1R M9A } d G y#i%L U

封装有两大类;一类是通孔插入式封装(through-hole package);另—类为表面安装式封装(surface moun te d Package)。每一类中又有多种形式。表l和表2是它们的图例,英文缩写、英文全称和中文译名。图6示出了封装技术在小尺寸和多引脚数这两个方向发展的情况。 DIP是20世纪70年代出现的封装形式。它能适应当时多数集成电路工作频率的要求,制造成本较低,较易实现封装自动化印测试自动化,因而在相当一段时间内在集成电路封装中占有主导地位。 但DIP的引脚节距较大(为2.54mm),并占用PCB板较多的空间,为此出现了SHDIP和SKDIP等改进形式,它们在减小引脚节距和缩小体积方面作了不少改进,但DIP最大引脚数难以提高(最大引脚数为64条)且采用通孔插入方式,因而使它的应用受到很大限制。 为突破引脚数的限制,20世纪80年代开发了PGA封装,虽然它的引脚节距仍维持在2.54mm或1.77mm,但由于采用底面引出方式,因而引脚数可高达500条~600条。 随着表面安装技术(surface mounted technology, SMT)的出现,DIP封装的数量逐渐下降,表面安装技术可节省空间,提高性能,且可放置在印刷电路板的上下两面上。SOP应运而生,它的引脚从两边引出,且为扁平封装,引脚可直接焊接在PCB板上,也不再需要插座。它的引脚节距也从DIP的2.54 mm减小到1.77mm。后来有SSOP和TSOP改进型的出现,但引脚数仍受到限制。 QFP也是扁平封装,但它们的引脚是从四边引出,且为水平直线,其电感较小,可工作在较高频率。引脚节距进一步降低到1.00mm,以至0.65 mm和0.5 mm,引脚数可达500条,因而这种封装形式受到广泛欢迎。但在管脚数要求不高的情况下,SOP以及它的变形SOJ(J型引脚)仍是优先选用的封装形式,也是目前生产最多的一种封装形式。 方形扁平封装-QFP (Quad Flat Package) [特点] 引脚间距较小及细,常用于大规模或超大规模集成电路封装。必须采用SMT(表面安装技术)进行焊接。操作方便,可靠性高。芯片面积与封装面积的比值较大。 小型外框封装-SOP (Small Outline Package) [特点] 适用于SMT安装布线,寄生参数减小,高频应用,可靠性较高。引脚离芯片较远,成品率增加且成本较低。芯片面积与封装面积比值约为1:8 小尺寸J型引脚封装-SOJ (Smal Outline J-lead) 有引线芯片载体-LCC (Leaded Chip Carrier) 据1998年统计,DIP在封装总量中所占份额为15%,SOP在封装总量中所占57%,QFP则占12%。预计今后DIP的份额会进一步下降,SOP也会有所下降,而QFP会维持原有份额,三者的总和仍占总封装量的80%。 以上三种封装形式又有塑料包封和陶瓷包封之分。塑料包封是在引线键合后用环氧树脂铸塑而成,环氧树脂的耐湿性好,成本也低,所以在上述封装中占有主导地位。陶瓷封装具有气密性高的特点,但成本较高,在对散热性能、电特性有较高要求时,或者用于国防军事需求时,常采用陶瓷包封。 PLCC是一种塑料有引脚(实际为J形引脚)的片式载体封装(也称四边扁平J形引脚封装QFJ (quad flat J-lead package)),所以采用片式载体是因为有时在系统中需要更换集成电路,因而先将芯片封装在一种载体(carrier)内,然后将载体插入插座内,载体和插座通过硬接触而导通的。这样在需要时,只要在插座上取下载体就可方便地更换另一载体。 LCC称陶瓷无引脚式载体封装(实际有引脚但不伸出。它是镶嵌在陶瓷管壳的四侧通过接触而导通)。有时也称为CLCC,但通常不加C。在陶瓷封装的情况下。如对载体结构和引脚形状稍加改变,载体的引脚就可直接与PCB板进行焊接而不再需要插座。这种封装称为LDCC即陶瓷有引脚片式载体封装。 TAB封装技术是先在铜箔上涂覆一层聚酰亚胺层。然后用刻蚀方法将铜箔腐蚀出所需的引脚框架;再在聚酰亚胺层和铜层上制作出小孔,将金属填入铜图形的小孔内,制作出凸点(采用铜、金或镍等材料)。由这些凸点与芯片上的压焊块连接起来,再由

集成电路封装形式介绍(图解) BGA BGFP132 CLCC CPGA DIP EBGA 680L FBGA FDIP FQFP 100L JLCC BGA160L LCC

LDCC LGA LQFP LQFP100L Metal Qual100L PBGA217L PCDIP PLCC PPGA PQFP QFP SBA 192L TQFP100L TSBGA217L TSOP

CSP SIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征和DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也和DIP基本相同. S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP. SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征和DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚. 用于高速的且大规模和超大规模集成电路. SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为 1.27mm. MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm. QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为 1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上. SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部和PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm. LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高 速,高频集成电路封装. PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装. SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为 1.27mm. BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚. 焊球的节距通常为1.5mm,1.0mm,0.8mm,和PGA相比,不会出现针脚变形问题. CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等. TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并和布线相连接的封装.和其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上. 介绍:

Take the market need as the guidance,Take the technical innovation as the motive. 内容: ?失效分析处理流程 ?生产伙伴的失效分析设备 ?昊宏失效分析设备情况 ?仓库条件

生产控制分析(24小时) 芯片设计失效分析(24小时) QA 部门成立问题分析小组 (12小时) 接收客户投诉信息(24小时)要求流片、封装、测试公司做失效分析试验(由供应商控制) 客户 市场部补货发出(12小时) 初步失效分析(48小时) FAE 提供解决方案(72小时) 输出失效分析报告(12小时)方案一方案二 方案三 记录失效分析过程,给出明确的失效分析结论和改进措施 SOP5 SOP2 SOP3 SOP4SOP1 SOP6 解决芯片设计失效(根据设计周期确定) SOP7 } SOP8

接收客户投诉信息 SOP1 1.QA部收到客户正式的产品投诉后,应填写《产品失效信息表》 1.1投诉反馈内容必须完整,至少应包括以下内容 1.1.1填写投诉表序号、顾客名称/代号、产品的编号; 1.1.2投诉何种缺陷或问题; 1.1.3对应的出货日期及出货数量; 1.1.4不良率有多少(或提供批量及不良数); 1.1.5顾客方在什么环节发现该问题。 1.2必要时,须包括以下内容 1.2.1顾客是否对产品进行了试验或特殊处理; 1.2.2如果顾客有进行试验或特殊处理,须了解客户的试验条件及 处理过程; 1.2.3顾客的组装工艺。 1.3如有附件/样品,须在反馈表上注明 1.3.1“有附件/样品”字样; 1.3.2在附件/样品上标识相应的投诉序号; 1.3.3如分析后需要把样品返还顾客,请注明“需返还顾客”字 样,并注明返还流程。

芯片封装方式大全 各种IC 封装形式图片 BGA Ball Grid Array EBGA680L LBGA160L PBGA217L Plastic Ball Grid Array SBGA192L QFP Quad Flat Package TQFP100L SBGA SC-705L SDIP SIP Single Inline Package SO Small Outline Package

TSBGA680L CLCC CNR Communication and Networking Riser Specification Revision1.2 CPGA Ceramic Pin Grid Array DIP Dual Inline Package SOJ32L SOJ SOP EIAJ TYPE II14L SOT220 SSOP16L SSOP TO18

DIP-tab Dual Inline Package with Metal Heatsink FBGA FDIP FTO220 Flat Pack HSOP28 ITO220 TO220 TO247 TO264 TO3 TO5 TO52 TO71

ITO3p JLCC LCC LDCC LGA LQFP PCDIP PGA Plastic Pin Grid Array TO72 TO78 TO8 TO92 TO93 TO99 TSOP Thin Small Outline Package

PLCC 详细规格 PQFP PSDIP LQFP100L 详细规格 METAL QUAD 100L 详细规格 PQFP100L 详细规格 QFP Quad Flat Package TSSOP or TSOP II Thin Shrink Outline Package uBGA Micro Ball Grid Array uBGA Micro Ball Grid Array ZIP Zig-Zag Inline Package TEPBGA288L TEPBGA C-Bend Lead

塑封料\环氧塑封料工艺选择和封装失效分析流程 一环氧塑封料的工艺选择 1.1预成型料块的处理 (1)预成型塑封料块一般都储存在5℃-10℃的环境中,必会有不同程度的吸潮。因此在使用前应在干燥的地方室温醒料,一般不低于16小时。 (2)料块的密度要高。疏松的料块会含有过多的空气和湿气,经醒料和高频预热也不易挥发干净,会造成器件包封层内水平增多。 (3)料块大小要适中,料块小,模具填充不良;料块大,启模困难,模具与注塑杆沾污严重并造成材料的浪费。 1.2模具的温度 生产过程中,模具温度控制在略高于塑封料玻璃化温度Tg时,能获得较理想的流动性,约160℃-180℃。模具温度过高,塑封料固化过快,内应力增大,包封层与框架粘接力下降。同时,固化过快也会使模具冲不满;模具温度过低,塑封料流动性差,同样会出现模具填充不良,包封层机械强度下降。同时,保持模具各区域温度均匀是非常重要的,因为模具温度不均匀,会造成塑封料固化程度不均匀,导致器件机械强度不一致。 1.3注塑压力 注塑压力的选择,要根据塑封料的流动性和模具温度而定,压力过小,器件包封层密度低,与框架黏结性差,易发生吸湿腐蚀,并出现模具没有注满塑封料提前固化的情况;压力过大,对内引线冲击力增大,造成内引线被冲歪或冲断,并可能出现溢料,堵塞出气孔,产生气泡和填充不良。 1.4注模速度 注模速度的选择主要根据塑封料的凝胶化时间确定。凝胶化时间短,注模速度要稍快,反之亦然。注模要在凝胶化时间结束前完成,否则由于塑封料的提前固化造成内引线冲断或包封层缺陷。 1.5塑封工艺调整 对工艺调整的同时,还应注意到预成型料块的保管、模具的清洗、环境的温湿度等原因对塑封工序的影响。 2塑封料性能对器件可靠性的影响 2.1塑封料的吸湿性和化学粘接性 对塑封器件而言,湿气渗入是影响其气密性导致失效的重要原因之一。湿气渗入器件主要有两条途径:

IC BGA Ball Grid Array EBGA 680L LBGA 160L PBGA 217L Plastic Ball Grid Array SBGA 192L QFP Quad Flat Package TQFP 100L SBGA SC-70 5L SDIP SIP Single Inline Package SO Small Outline

TSBGA 680L CLCC CNR Communication and Networking Riser Specification Revision 1.2 CPGA Ceramic Pin Grid Array DIP Dual Inline Package Package SOJ 32L SOJ SOP EIAJ TYPE II 14L SOT220 SSOP 16L SSOP

DIP-tab Dual Inline Package with Metal Heatsink FBGA FDIP FTO220 Flat Pack HSOP28 ITO220 TO18 TO220 TO247 TO264 TO3 TO5 TO52

ITO3p JLCC LCC LDCC LGA LQFP PCDIP PGA Plastic Pin Grid Array TO71 TO72 TO78 TO8 TO92 TO93 TO99

PLCC PQFP PSDIP LQFP 100L METAL QUAD 100L PQFP 100L QFP Quad Flat Package TSOP Thin Small Outline Package TSSOP or TSOP II Thin Shrink Outline Package uBGA Micro Ball Grid Array uBGA Micro Ball Grid Array ZIP Zig-Zag Inline Package TEPBGA 288L TEPBGA

芯片封装大全

1、BGA(ball grid array) 球形触点陈列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以 代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸 点陈列载体(PAC)。引脚可超过200,是多引脚LSI 用的一种封装。 封装本体也可做得比QFP(四侧引脚扁平封装)小。例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。而且BGA 不用担心QFP 那样的引脚变形问题。 该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可 能在个人计算机中普及。最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有 一些LSI 厂家正在开发500 引脚的BGA。 BGA 的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为, 由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。 美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为 GPAC(见OMPAC 和GPAC)。 2、BQFP(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装。QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以 防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和ASIC 等电路中采用 此封装。引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。 3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。 4、C-(ceramic) 表示陶瓷封装的记号。例如,CDIP 表示的是陶瓷DIP。是在实际中经常使用的记号。 5、Cerdip 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有 玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。引脚中心 距2.54mm,引脚数从8 到42。在日本,此封装表示为DIP-G(G 即玻璃密封的意思)。 6、Cerquad 表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。带有窗 口的Cerquad 用于封装EPROM 电路。散热性比塑料QFP 好,在自然空冷条件下可容许1.5~ 2W 的功率。但封装成本比塑料QFP 高3~5 倍。引脚中心距有1.27mm、0.8mm、0.65mm、0.5mm、0.4mm 等多种规格。引脚数从32 到368。 7、CLCC(ceramic leaded chip carrier) 带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。 带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。此封装也称为 QFJ、QFJ-G(见QFJ)。 8、COB(chip on board)

IC封装样品失效分析概述 Angus 2011-12-05

IC封装样品失效分析 FA (Failure Analysis),失效分析不仅有助于提高产品可靠性,而且可以带来很高的经济效益,是IC生产中不可缺少的部分。 按照分析目的或分析手段,FA可分为: PFA(Physical Failure Analysis), 是主要做物理、材料方面的失效分析EFA(Electrical Failure Analysis),是以电学测试为主的失效分析,

IC封装样品失效分析 Cu pad on substrate Pillar Bump 失效分析的目的:分析失效现象,确定失效原因,提出改善建议,提高产品可靠性如何做失效分析:先简单后复杂,先外后内,先无损后有损

IC封装样品失效分析 1.X-Ray (X射线检测) 2.C-SAM (超声波检测) 3.Microscope (显微镜检测) 4.SEM & EDX(扫描电镜及能谱检测) 5. Decapsulation(开帽检查) 6.Cross-Section (Polish&FIB) 7.EFA(EMMI, OBIRCH,InGaAs)

1.X-Ray (X射线检测) X射线是1895年由伦琴发现的,因此也叫伦琴射线。 X射线肉眼不可见,但可是照相底片感光,具有很强的穿透力。 X射线本质上是一种波长很短的电磁波,波长范围0.01~ 10nm,介于紫外线与γ射线之间。 左图为X射线的产生原理图: 1.在阴极灯丝1与阳极4之间加直流高压(上万伏), 2.灯丝产生大量热电子, 3.电子在高压电场作用下,冲击阳极上的靶材5, 4.靶材受电子激发产生X射线。 灯丝的材质通常为钨,靶材的材质有Ti、Cu、Mo等

可靠性失效分析常见思路 失效分析在生产建设中极其重要,失效分析的限期往往要求很短,分析结论要正确无误,改进措施要切实可行。 1 失效分析思路的内涵 失效分析思路是指导失效分析全过程的思维路线,是在思想中以机械失效的规律(即宏观表象特征和微观过程机理)为理论依据,把通过调查、观察和实验获得的失效信息(失效对象、失效现象、失效环境统称为失效信息)分别加以考察,然后有机结合起来作为一个统一整体综合考察,以获取的客观事实为证据,全面应用推理的方法,来判断失效事件的失效模式,并推断失效原因。因此,失效分析思路在整个失效分析过程中一脉相承、前后呼应,自成思考体系,把失效分析的指导思路、推理方法、程序、步骤、技巧有机地融为一体,从而达到失效分析的根本目的。 在科学的分析思路指导下,才能制定出正确的分析程序;机械的失效往往是多种原因造成的,即一果多因,常常需要正确的失效分析思路的指导;对于复杂的机械失效,涉及面广,任务艰巨,更需要正确的失效分析思路,以最小代价来获取较科学合理的分析结论。总之,掌握并运用正确的分析思路,才可能对失效事件有本质的认识,减少失效分析工作中的盲目性、片面性和主观随意性,大大提高工作的效率和质量。因此,失效分析思路不仅是失效分析学科的重要组成部分,而且是失效分析的灵魂。 失效分析是从结果求原因的逆向认识失效本质的过程,结果和原因具有双重性,因此,失效分析可以从原因入手,也可以从结果入手,也可以从失效的某个过程入手,如“顺藤摸瓜”,即以失效过程中间状态的现象为原因,推断过程进一步发展的结果,直至过程的终点结果“;顺藤找根”,即以失效过程中间状态的现象为结果,推断该过程退一步的原因,直至过程起始状态的直接原因“;顺瓜摸藤”,即从过程中的终点结果出发,不断由过程的结果推断其原因“顺;根摸藤”,即从过程起始状态的原因出发,不断由过程的原因推断其结果。再如“顺瓜摸藤+顺藤找根”、“顺根摸藤+顺藤摸瓜”、“顺藤摸瓜+顺藤找根”等。 2 失效分析的主要思路 常用的失效分析思路很多,笔者介绍几种主要思路。 “撒大网”逐个因素排除的思路 一桩失效事件不论是属于大事故还是小故障,其原因总是包括操作人员、机械设备系统、材料、制造工艺、环境和管理6个方面。根据失效现场的调查和对背景资料(规划、设计、制造说明书和蓝图)

新版PFMEA-过程失效模式与影响分析实战训练 ●课程背景 德国汽车工业协会(VDA QMC)在德国柏林召开股东会议,并正式宣布新版AIAG-VDA FMEA标准发布!这是一个历史性时刻,历经了长时间汽车行业专家的反复研讨和修订,第一版的AIAG-VDA标准终于正式发布!本次培训将根据最新发布的AIAG-VDA FMEA 要求,系统地讲解新版FMEA的背景,重要变化点以及企业如何应对等,并对新的AIAG-VDA FMEA七步法进行详细讲解,帮助企业迅速掌握新版FMEA的使用。FMEA是1960 年代美国太空计划所发展出来的一套手法,为了预先发现产品或流程的任何潜在可能缺点,并依照其影响效应,进行评估与针对某些高风险系数之项目,预先采取相关的预防措施避免可能产生的损失与影响。近年来广为企业界做为内部预防改善与外部对供货商要求的工具,是从事产品设计及流(制)程规划相关人员不得不熟悉的一套运用工具。FMEA是系统化的工程设计辅助工具,主要利用表格方式协助进行工程分析,使其在工程设计时早期发现潜在缺陷及其影响程度,及早谋求解决之道,避免失效之发生或降低影响,提高系统之可靠度。因此尽早了解与推动失效分析技术,是业界进军国际市场必备的条件之一! ●培训对象 研发总监、经理、工程师;质量总监、质量经理、质量主管、质量工程师、质量技术员;技术总监、经理、工程师、技术员;产吕流程总监、经理、工程师、技术员;生产经理、生产主管以及所有工程师(PE,ME,QA,SQE等)。 ●培训时间 1-2天 ●课程收获 1.了解最新版PFMEA的背景及主要变化点

2.理解和掌握新版PFMEA的七步法 3.预先考虑正常的用户使用和制造过程中会出现的失效 4.有助于降低成本提升效益,预防不良品的发生 5.建立产品可靠度保证系统,具备整体的概念 6.认识失效的类型及其影响 7.熟悉并运用失效模式与效应分析手法预防产品设计与制程规划可能发生的不良现象 8.累积公司相关不良模式与效应处理之工程之知识库,不断改进产品可靠性 课程大纲 第一章FMEA的发展过程 一.了解FMEA 二.FMEA定义 三.FMEA的目的 四.什么时候用FMEA 五.新版PFMEA的主要变化 1.七步法代替以前的“填表法” 2.全新的SOD评分标准 3.全新的措施优先级AP取代RPN 4.增加了优化措施的状态跟踪 5.全新的表格等 第二章PFMEA简介 一.PFMEA的时间顺序 二.PFMEA集体的努力 三.成功的PFMEA小组 四.PFMEA小组的守则 五.PFMEA小组决定的标准/模式 第三章执行新版PFMEA和实例 一.执行新版PFMEA的步骤

高铁及轨道交通轴承失效分析方法 洛阳轴研科技股份有限公司 概述 高速铁路作为现代社会的一种新的运输方式,在安全、快捷、经济、环保等方面都具有比较明显的优势。进入新世纪以来,中国铁路决定将高铁及轨道交通等客运高速作为实现现代化的一个主要方向。依照自主创新,中国高铁从无到有,经过十多年的高速铁路建设,我国高速铁路运营总里程将突破1.3万公里,同时我国轨道交通技术装备逐步提高并实现了国产化,但作为基础精密件的轴承,我国目前主要依靠进口。高速铁路客车轴承的高可靠性性及长寿命要求,一致制约着我国高铁轴承的研发。近年来,出于对研发、运行安全以及经济等多方面的考虑做了大量的高铁及轨道交通轴承的失效分析。通过失效分析,找出故障产生的原因,并采取有效措施进行预防和控制,防止突发性事故的出现,把故障造成的损失降低到最低,从而提高产品使用的安全可靠性,充分发挥其价值,这是一项十分重要的工作。 1.失效分析的概念 轴承在运转一定时间后,由于制造、安装、使用、维护等方面的原因使其丧失(或局部丧失)规定功能,从而导致故障或不能正常工作的现象称为失效。 失效有以下几种形式: (1)完全不能工作。如零件材料的疲劳、断裂等; (2)仍然可以继续工作,但已不能得到预期令人满意的性能。如轴承运转时的工作温度上升、振动和噪声增加等; (3)已经不能保证可靠或安全的继续使用,必须拆卸进行修理。 按照一定的方法分析失效的性质和发生原因、研究失效的处理方法和预防措施的技术及管理活动被人们称之为失效分析。 “失效”与“废品”具有不同的含义,“废品”是不符合技术规范、标准和图纸要求的而又不能返修利用的产品。“失效”的产品不一定是“废品”,而“废品”也谈不上失效。轴承的失效按其寿命可分为正常失效和早期失效两种。分析工作主要是针对早期失效的轴承,找出其失效的原因,提出改进措施,以提高轴承运转的寿命和可靠性。

封装常规失效分析流程 1,接受上级或客户不良品信息反馈及分析请求,并了解客户相关信息。(指失效模式,参数值,客户抱怨内容,型号,批号,失效率,所占比例等,与正常品相比不同之处) 2,记录各项信息内容,以在长期记录中形成信息库,为今后的分析工作提供经验值。 3,收信工艺信息,包括与此产品有关的生产过程中的人,机,料,法,环变动的情况(老员工,新员工,班次,人员当时的工作状态,机台状况,工夹具,所采用的原材料,工艺参数的变动,环境温湿度的变动等)通常有:装片机号,球焊机号,包封机号,后固化烘箱号,去飞边机号,软化线号,是否二次软化,测试机台,测试参数,料饼品种型号,引线条供应者及批号,金丝品种及型号,供应者等。 4,失效确认,可用自已的测试机检测功能、开短路,以确认客户反映情况是否属实。 5,对于非开短路情况,如对于漏电流大的产品要彻底清洗(用冷热纯水或有机溶剂如丙酮)后再进行下述烘烤试验:125度烘烤24小时或175度烘烤4小时以上,烘箱关电源后门打开45度角缓慢冷却1小时后再测其功能,如功能变好,则极有可能是封装或者测试问题,对封装工艺要严查。 6,对于开短路情况,观察开短路测试值是开路还是短路,还是芯片不良,如是开路或短路,则要注意是第几脚开路或短路,待开帽后用万用表测量该脚所连的金丝的压区与脚之间的电阻,以判断该脚球焊是否虚焊。 7,对于大芯片薄形封装产品要注意所用材料(如料饼,导电胶)是否确当,产品失效是否与应力和湿气有关(125度烘烤24小时或175度烘烤4小时以上,烘箱关电源后,门打开45度角缓慢冷却1小时后再测其功能,如功能变好,则极有可能是封装或者测试的问题,对封装工艺要严查,如检查去飞边方式,浸酸时间等。) 8,80倍以上显微镜观察产品外形特征,特别是树脂休是否有破裂,裂缝,鼓泡膨胀。(注胶口,脚与脚之间树脂体和导电物) 9,对所有失效样品进行X-RAY检查,观察金丝情况,并和布线图相比较,以判断布线是否错误。如发现错误要加抽产品确认失效总数并及时反映相关信息给责任人。 10,C-SAM即SAT,观察产品芯片分层情况。判断规范另见。样品数量为10只以内/批。 11,开帽:对于漏电流大的产品采用机械方式即干开帽形式,其它情况用强酸即湿开帽形式。切开剖面观察金丝情况,及金球情况,表面铝线是否受伤,芯片是否有裂缝,光刻是否不良,是否中测,芯片名是否与布线图芯片名相符。样品数量为5只/批。对于开短路和用不导电胶装片的产品要用万用表检测芯片地线和基岛之间电阻检查装片是否有问题。对于密间距产品要测量铝线宽度,确认所用材料(料饼,导电胶,金丝)是否确当开帽后应该再测试,根据结果进一步分析。 12,腐球:观察压区硅层是否破裂,严重氧化(用王水或氢氧化钠或氢氧化钾),腐球时注意要腐透(金丝彻底脱离芯片或溶化掉),不能用细针去硬拨金丝以免造成人为压区损坏。

失效分析程序简述 机械失效常常会出现多个机件发生失效,特别是机械事故发生的时候,往往有大量机件同时遭到破坏,情况相当复杂,而失效原因也错综复杂、多种多样。因此,需要有正确的失效分析思路和合理的失效分析步骤。失效分析的实施步骤和程序旨在保证失效分析顺利有效地进行,但是机械产品的失效常常是千变万化,很难制定一个统一的失效分析程序。因此,其细节的制定应根据失效事件的具体情况(失效设备的类型及其失效的严重性等) 、失效分析的目的与要求(是为机理研究、技术改进,还是为法律仲裁等) 、以及有关合同或法规的规定来决定。 下面介绍一般通用的失效分析实施步骤和程序,原则上可供参考和引用。图1 示出了推荐的失效分析实施步骤和程序的流程图。 图1 失效分析实施步骤和程序

1 保护失效现场 保护失效现场的一切证据,维持原状、完整无缺和真实不伪,是保证失效分析得以顺利有效地进行的先决条件。失效现场的保护范围视机械设备的类型及其失效发生的范围而定。 2 失效现场取证和收集背景材料 失效现场取证应由授权的失效分析人员执行,并授权收集一切有关的背景材料。失效现场取证可用摄影、录像、录音和绘图及文字描述等方式进行记录。 失效现场取证所应注意观察和记录的项目主要有: (1) 失效部件及碎片的名称、尺寸大小、形状和散落方位。 (2) 失效部件周围散落的金属屑和粉末、氧化皮和粉末、润滑残留物及一切可疑的杂物和痕迹。 (3) 失效部件和碎片的变形、裂纹、断口、腐蚀、磨损的外观、位置和起始点,表面的材料特征,如烧伤色泽、附着物、氧化物和腐蚀生成物等。 (4) 失效设备或部件的结构和制造特征。 (5) 环境条件(失效设备的周围景物、环境温度、湿度、大气和水质) 。 (6) 听取操作人员及佐证人介绍事故发生时情况(录音记录) 。 在观察和记录时要按照一定顺序,避免出现遗漏。例如观察和记录时由左向右、由上向下、由表及里和由低倍到高倍等。 所应收集的背景材料通常有: (1) 失效设备的类型、制造厂名、制造日期、出厂批号,用户、安装地点、投入运行日期、操作人员、维修人员、运行记录、维修记录、操作规程和安全规程。 (2) 该设备的设计计算书及图纸、材料检验记录、制造工艺记录、质量控制记录、验收记录和质量保证合同及其技术文件,还有使用说明书。 (3) 有关的标准、法规及其他参考文献。 (4) 收集同类或相似部件过去曾发生过的失效情况。 3 制定失效分析计划