作者:败转头

作品编号44122544:GL568877444633106633215458

时间:2020.12.13

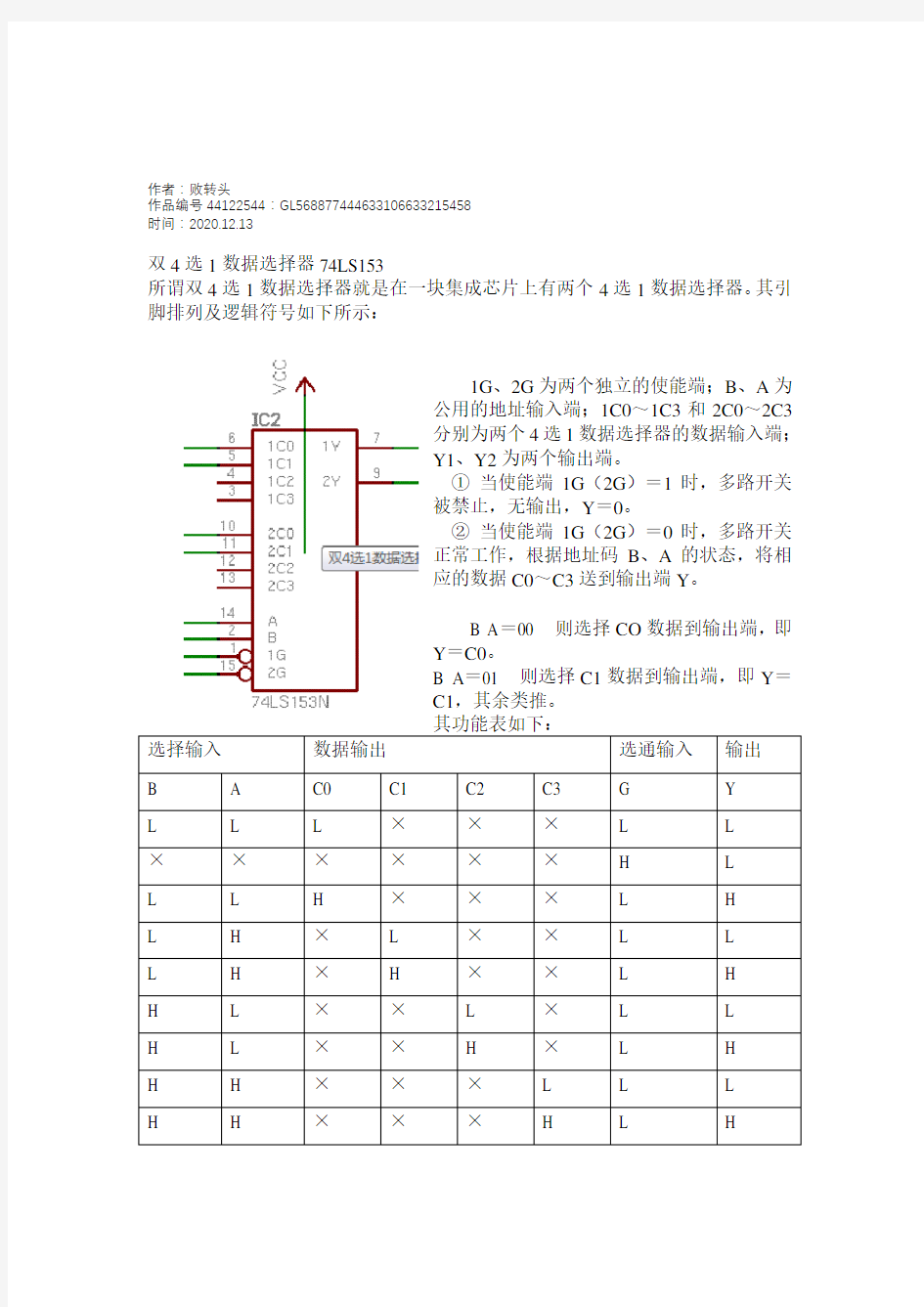

双4选1数据选择器74LS153

所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。其引脚排列及逻辑符号如下所示:

1G、2G为两个独立的使能端;B、A为

公用的地址输入端;1C0~1C3和2C0~2C3

分别为两个4选1数据选择器的数据输入端;

Y1、Y2为两个输出端。

①当使能端1G(2G)=1时,多路开关

被禁止,无输出,Y=0。

②当使能端1G(2G)=0时,多路开关

正常工作,根据地址码B、A的状态,将相

应的数据C0~C3送到输出端Y。

B A=00 则选择CO数据到输出端,即

Y=C0。

B A=01 则选择C1数据到输出端,即Y=

C1,其余类推。

选择输入数据输出选通输入输出

B A C0 C1 C2 C3 G Y

L L L ×××L L

××××××H L

L L H ×××L H

L H ×L ××L L

L H ×H ××L H

H L ××L ×L L

H L ××H ×L H

H H ×××L L L

H H ×××H L H

作者:败转头

作品编号44122544:GL568877444633106633215458 时间:2020.12.13

《集成电路设计实践》报告 题目:8选1数据选择器 院系:自动化学院电子工程系 专业班级:微电121班 学生学号:3120433003 学生姓名:王瑜 指导教师姓名:王凤娟职称:讲师起止时间:2015-12-21---2016-1-9 成绩:

一、设计任务 1) 依据8选1数据选择器的真值表,给出八选一MUX电路图,完成由电路图到晶体管级的转化(需提出至少2种方案); 2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间; 3) 遵循设计规则完成晶体管级电路图的版图,流程如下:版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图); 4) 版图检查与验证(DRC检查); 5) 针对自己画的版图,给出实现该电路的工艺流程图。 二、电路设计方案的确定 数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示 数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路,函数发生器及数码比较器

等,常见的数据比较器有2选1,4选1,8选1,16选1电路。 示意图 在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器。

数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。 本次设计的是8选1数据选择器。选择控制端(地址端)为K2,K1,K0,按二进制译码,从8个输入数据D0-D7中,选择一个需要的数据送到输出端Y。 根据多路开关的开关状态(地址码)K2,K1,K0的状态选择D0-D7中某一个通道的数据输送到输出端Y。 如:K2K1K0=000,则选择D0数据到输出端,即Y=D0。 如:K2K1K0=001,则选择D1数据到输出端,即Y=D1,其余类推。 8选1 MUX功能表如下: K2 K1 K0 Y 0 0 0 D0 0 0 1 D1 0 1 0 D2 0 1 1 D3 1 0 0 D4 1 0 1 D5 1 1 0 D6 1 1 1 D7

Verilog HDV 数字设计与综合 实验报告 微电子0901班 姓名:袁东明 _ 学号:_04094026 一、实验课题: 1.八选一数据选择器 2.四位数据比较器 二、八选一数据选择器Verilog程序: 2.1主程序 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out); input [2:0] a,b,c,d,e,f,g,h; input s0,s1,s2; output [2:0] out; reg [2:0] out; always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin case({s0,s1,s2}) 3'd0 : out=a;

3'd1 : out=b; 3'd2 : out=c; 3'd3 : out=d; 3'd4 : out=e; 3'd5 : out=f; 3'd6 : out=g; 3'd7 : out=h; endcase end endmodule 2.2激励程序 module sti; reg [2:0] A,B,C,D,E,F,G,H; reg S0,S1,S2; wire [2:0] OUT; option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT); initial begin A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;

四选一数据选择器源程序 Library ieee; Use ieee.std_logic_1164.all; Entity mux4_2 is Port (din: in std_logic_vector(3 downto 0); a,b : in std_logic; S: out std_logic); End; Architecture with_when of mux4_2 is Signal sel : std_logic_vector(1 downto 0); Begin Sel<=a&b; S<=din(0) when sel=“00”else din(1)when sel= “01” else din(2)when sel= “10” else din(3);---见程序说明。 Architecture with_select of mux4 is Signal sel :std_logic_vector(1 downto 0); begin sel<=a&b; with sel select s<=din(0) when “00”, s<=din(1) when “01”,

s<=din(2) when “10”, s<=din(3) when “11”, …Z?when others; End; 程序说明: 1.本程序中含有两个结构体,with_when和with_select,max+plus软 件系统自动执行几何位置处于最后的机构体with_select. 2.结构体with_when是用并行条件信号赋值语句描述四选一数据选 择器。注意,最后一个输出din(3)不含有when子句;在s表达式中只有一个分号(;)。 3.结构体with_select.是用并行选择信号赋值语句描述四选一数据选 择器。注意,选择信号赋值语句中选择条件与case语句相似,不允许条件重叠和涵盖不全。由于a,b的值除了‘1’‘0’外,还有其他7个值,所以要用when others代表其他值,以穷尽所有可能值。 4.同一个设计任务,可以用不同的语句进行描述, 5.本程序中din为输入4位矢量信号。 实例2 3线----8线译码器 一、设计任务 描述一个3线-8线译码器,使能端为g1、g2a、g3b,地址选择端为a、 b、c,输出端为总线y。 二、算法设计

8选1数据选择器74LS151 简介 74LS151是一种典型的集成电路数据选择器,为互补输出的8选1数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。 74LS151引脚图 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。 (2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。

74LS151功能表 数据选择器的应用 数据选择器除实现有选择的传送数据外,还有其他用途,下面介绍几种典型应用。 (1)逻辑函数产生器 从74LS151的逻辑图可以看出,当使能端G=0时,Y是C、B、A和输入数据D0~D7的与或函数。 式中mi是C、B、A构成的最小项。显然。当Di=1时,其对应的最小项mi在与或表达式中出现,当Di=0时,对应的最小项就不出现。利用这一点,不难实现组合逻辑函数。 已知逻辑函数,利用数据选择器构成函数产生器的过程是,将函数变换成最小项表达式,根据最小项表达式确定各数据输入端的二元常量。将数据选择器的地址信号C、 B、A作为函数的输入变量,数据输入D0~D7,作为控制信号,控制各最小项在输出 逻辑函数中是否出现,使能端G始终保持低电平,这样8选1数据选择器就成为一个3变量的函数产生器。

实验四数据选择器 一、实验目的 1. 熟悉中规模集成数据选择器的逻辑功能及测试方法。 2. 学习用集成数据选择器进行逻辑设计。 二、实验原理 数据选择器是常用的组合逻辑部件之一。它由组合逻辑电路对数字信号进行控制来完成较复杂的逻辑功能。它有若干个数据输入端D0、D1、…,若干个控制输入端A0、A1、…和一个输出端Y0。在控制输入端加上适当的信号,即可从多个输入数据源中将所需的数据信号选择出来,送到输出端。使用时也可以在控制输入端上加上一组二进制编码程序的信号,使电路按要求输出一串信号,所以它也是一种可编程序的逻辑部件。 中规模集成芯片74LS153为双四选一数据选择器,引脚排列如图7—1所示,其中D0,D1,D2,D3为四个数据输入端,Y为输出端,A1,A2为控制输入端(或称地址端)同时控制两个四选一数据选择器的工作,G为工作状态选择端(或称使能端)。74LS153的逻辑功能如表7—1所示,当1 =G G时电路不工作,此 1= 2 ) ( 时无论A1、A0处于什么状态,输出Y总为零,即禁止所有数据输出,当( =G G时,电路正常工作,被选择的数据送到输出端,如A1A0=01,则选1= ) 2 中数据D1输出。 图7—1 图7—2 表7—1

当G =0时,74LS153的逻辑表达式为 中规模集成芯片74LS151为八选一数据选择器,引脚排列如图7—2所示。其中D 0—D 7为数据输入端,)(Y Y 为输出端,A 2、A 1、A 0为地址端,74LS151的逻辑功能如表7—2所示。逻辑表达式为 数据选择器是一种通用性很强的中规模集成电路,除了能传递数据外,还可用它设计成数码比较器,变并行码为串行及组成函数发生器。本实验内容为用数据选择器设计函数发生器。 用数据选择器可以产生任意组合的逻辑函数,因而用数据选择器构成函数发生器方法简便,线路简单。对于任何给定的三输入变量逻辑函数均可用四选一数据选择器来实现,同时对于四输入变量逻辑函数可以用八选一数据选择器来实现。应当指出,数据选择器实现逻辑函数时,要求逻辑函数式变换成最小项表达式,因此,对函数化简是没有意义的。 表7—2 例:用八选一数据选择器实现逻辑函数 CA BC AB F +== D A A D A A D A A D A A Y 3 1 2 1 1 1 1 +++= D A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y 7 2 6 1 2 5 1 2 4 1 2 3 1 2 2 1 2 1 1 2 1 2 +++ ++++=

1.4’b1001<<2=(6‘b100100),4’b1001>>2=(4’b0010 )。 2、完整的条件语句将产生(组合逻辑电路)电路,不完整的条件语句将产生(时序逻辑电路)电路。 3、用EDA技术进行电子系统设计的目标是最终完成(专用集成电路ASIC)的设计。 4、可编程器件分为(现场可编程列阵FPGA)和(复杂可编程逻辑器件 PLD) 5、系统函数和任务函数的首字符标志为($),预编译指令首字符标志为(#)。 6、一个基本的Verilog-HDL程序由(Verilog-HDL )模块构成。 7、EDA技术在应用设计领域主要包含哪四个方面的内容(HDL)、(PLD )、( EDA工具软件)、(EDA开发系统) 8、EDA技术的基本特征主要有哪5个方面:(自顶向下的设计方法)、(采用硬件描述语言)、(高层综合和优化).(并行工程)、(开放性和标准化) 9、当前最流行的并成为IEEE标准的硬件描语言是( VHDI )和( Verilog-HDL) 10、一个完整的Verilog-HDL设计模块包括:(模块关键字和模块名)、(端口列表)、(端口定义)、(功能描述)这4部分。 11Verilog-HDL模块的I/O端口声明用来声明模块端口定义中各端口数据流动方向,包括(输入端口)、(输出端口)、和(双向端口) 12、Verilog-HDL语言的三种常用的模型描述方法为(行为描述)、(数据描述)和(结构描述) 13、Verilog-HDL的数值集合由哪四种基本的值组成( 0)、(1 )、 x)、( z ) 14、10’hxf=( 10’xxxxxx1111 ) 10’hzf=( 10’zzzzzz1111 ) 15、若a=5’b10x01,b=5’b10x01,则a= =b的结果为( X )、a= = =b的结果为( 1 ) 16、Wire[15:0] wire-b表示连线宽度为(16 )位,其最高位为(15),最低位为(0)。 17、若A=5’b11011,B=5’b10101,则有&A=(0)|B=(1) ~A=(5’b00100)A&B(5’b10001) 18、若A=8’b1000_0100则A<<3的结果为(11’b10000100000)A>>3的结果为(8’b00010000) 19、对于Verilog-HDL语言中的关键字,在建模时都必须(小)写。 20、if(a) out1<=int1; else out1<=int2;当a= (1)执行out1<=int1 ;当a=(0)执行out1<=int2 二、选择题: 21、在verilog语言中整型数据与( C )位寄存器数据在实际意义上是相同的。 A、8 B、16 C、32 D、64 22、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。 A.FPGA全称为复杂可编程逻辑器件; B.FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 23. 子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化( B )。 ①流水线设计②资源共享③逻辑优化④串行化 ⑤寄存器配平⑥关键路径法 A.①③⑤B.②③④C.②⑤⑥D.①④⑥ 24、下列标识符中,(A)是不合法的标识符。 A、9moon B、State0 C、Not_Ack_0 D、signall 25、下列语句中,不属于并行语句的是:(D ) A、过程语句 B、assign语句 C、元件例化语句 D、case语句 26、在verilog中,下列语句哪个不是分支语句?( D ) A.if-else B、case C、casez D、repeat 27、下列标示符哪些是合法的( B ) A、$time B、_date C、8sum D、mux# 28、如果线网类型变量说明后未赋值,起缺省值是( D ) A、x B、1 C、0 D、z 29、现网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A )

用数据选择器设计组合逻辑电路 一、用一片四选一数据选择器实现逻辑函数:BC C A C AB Y ++=//// 要求写出分析与计算过程并画出连线图。 四选一数据选择器的功能表及逻辑图如下图所示。(10分) 解一: (1)选A 、B 作为数据选择器的地址码A 1、A 0,将逻辑函数变形为: ) ()()1()(//////////////////C AB C AB B A C B A ABC BC A BC A C B A C AB BC C A C AB Y +++=++++=++= (2)将变形后的逻辑函数与四选一数据选择器的输出逻辑式进行比较得: 013/0120/11/0/10A A D A A D A A D A A D Y +++= C D C D D C D ====3/21/0;;1; (3)连接电路:

解二: (1)、写出四选一数据选择器的逻辑表达式:(2分) S A A D A A D A A D A A D Y ?+++=)(013/0120/11/0/10 (2)、把所求逻辑函数的表达式变形:(4分) C AB C AB B A C B A ABC BC A BC A C B A C AB BC C A C AB Y )()(1)()(//////////////////++?+=++++=++= (3)、确定电路连接:(4分) 将上述两个表达式进行比较,可知应令: 1=S ,即0/=S 01;A B A A == C D C D D C D ====3/21/0;;1; (4)、画出连接图:( 2分)

二、试用一片四选一数据选择器实现逻辑函数: ' +' ' = Y' + B C A AC BC A 要求写出详细的设计过程并画出连线图。四选一数据选择器的功能表及逻辑图如图(a)、(b)所示。(10分) 解: (1)、把所求逻辑函数的表达式变形:(4分) (2)、与四选一数据选择器的逻辑表达式进行比较,确定电路连接:(4分)(3)、画出连接图:( 2分)

8选1数据选择器74LS151 74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。838电子(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。新艺图库 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。工作原理ab126计算公式大全 74LS151功能表:

在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。 数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。 1.逻辑特性 (1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。 (2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即 数据选择器的原理 o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择 一个需要的数据送到输出端Q,为使能端,低电平有效。 图74LS151引脚排列 使能端=1时,不论A2~A0状态如何,均无输出(Q=0,=1),多路开关被禁止。 1)使能端=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7 中某一个通道的数据输送到输出端Q。 如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。 如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。 数据选择器的定义及功能 数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示。 下面以4选1数据选择器为例,说明工作原理及基本功能。其逻辑图为: 功能表为: 为了对4个数据源进行选择,使用两位地址码BA产生4个地址信号。由BA等于00、01、10、11分别控制四个与门的开闭。显然,任何时候BA只有一种可能的取值,所以只有一个与门打开,使对应的那一路数据通过,送达Y端。输入使能端G是低电平有效,当G=1时,所有与门都被封锁,无论地址码是什么,Y总是等于0;当G=0时 ,封锁解除,由地址码决定哪一个与门打开。 同样原理,可以构成更多输入通道的数据选择器。被选数据源越多,所需地址码的位数也越多,若地址输入端为N,可选输入通道数为2n。 二、集成电路数据选择器 1.74LS151集成电路数据选择器的功能 74LS151是一种典型的集成电路数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。其逻辑图和引脚图分别如下所示:由逻辑图可知,该逻辑电路的基本结构为“与一或一非”形式。输入使能G为低电平有效。输出Y的

实验五 数据选择器及应用 [实验目的] 1、掌握数据选择器的工作原理及逻辑功能。 2、熟悉74LS153和74LS151的管脚排列和测试方法。 3、学习用数据选择器构成组合逻辑电路的方法。 [实验仪器及元器件] THD-1型数字电路实验箱,数字万用表,双踪示波器,集成电路(74LS00 四-2输入与非门、4LS32四-2输入或门、4LS86四-2输入异或门、 74LS153双四选一数据选择器、74LS151 八选一数据选择器),信号线(电缆),各种导线。 [实验任务] 1、用双四选一数据选择器74LS153实现一位全减器。 2、用双四选一数据选择器74LS153设计一个四位奇偶校验器。 3、用八选一数据选择器74LS151设计一个多数表决电路。 4、用Multisim8进行仿真,并在实验仪器上实现。 [实验原理] 数据选择器又称多路转换器或多路开关,其功能是在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其 送到一个公共输出端。数据选择器的功能类似一个多掷开关,如图4-23所示,图中有四路数据D 0 ~ D 3通过选择控制信号A 1、A 0(地址码)从四路数据中选中某一路数据送至输出端Y 。 一个n 个地址端的数据选择器,具有2n 个数据选择功能。例如:数据选择器(74LS153),n = 2,可 完成四选一的功能;数据选择器(74LS151),n = 3,可 完成八选一的功能。 1、双四选一数据选择器74LS153 所谓双4选1数据选择器就是在一块集成芯片上 有两个4选1 数据选择器。集成芯片引脚排列如图 A 1 A 0 地址码 D 0 D D D 数 据输 入 Y 输 出 图4-23 四选一数据选择器 4-24 74LS153引脚排列

实验二 4选1数据选择器的设计 实验学时:2学时 实验类型:设计 实验要求:必做 一、实验目的 通过实验让学生掌握组合逻辑电路的EDA原理图输入设计法,通过电路的仿真和硬件验证,让学生进一步了解4选1数据选择器的功能。 二、实验原理 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关。数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。数据选择器的电路结构一般由于活门阵列而成,也有用传输门开关和门电路混合而成的。 图1 4选1数据选择器原理图 图1是一个4选1数据选择器,d3—d0是数据输入端,s1和s0是控制输入端,y是4选1数据输出端。 三、实验内容 设计并实现一个4选1数据选择器,要求根据原理图写出它的逻辑关系,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

四、实验步骤 1)在Maxplus2的图形编辑方式下,从prim元件库中调出4选1数据选择器电路所需要的元件。并按照图1所示的原理电路,完成4选1数据选择器原理图的输入设计。 2)保存好原理图文件,以为文件名保存在工程目录中。执行Compiler命令对设计文件进行编译。执行Create Default Symbol命令,可为4选1数据选择器生成一个元件符号。 3)在波形编辑方式下,编辑的波形文件,并完成输入信号d3,d2,d1和d0,控制信号s1和s0电平的设置。波形文件编辑结束后以为波形文件名存盘。执行仿真器Simulator命令,仿真开始,观察仿真波形进行设计电路的功能验证。 五、实验结果 1. 4选1数据选择器的逻辑功能及真值表 2.仿真波形

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8” 的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在随后弹 出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对话框中 选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save As 命 令保存。

四.综合适配 1.选择Processing =>Start Compilation命令,检查发现无程序语法错误。 2.执行Tools =>Netlist Viewer =>RTL Viewe, 生成RTL图。 五.模拟仿真 1.在 File 菜单下,点击 New 命令。在随后弹出的对话框中,切换到 Other Files 页。选中 Vector Waveform File 选项,点击 OK 按钮。 2.选择命令 Edit=>End Time ,时间设置为30000ns , 进入到波形编辑界 面。在 Edit 菜单下,点击Insert Node or Bus… 命令,或在结点名字区连续双击鼠标左键两次,在新出现的框图中点击Node Finder出现结点查找器窗口搜索结点名, 在上一个框图中点击 Node Finder… 按钮后,打开Node Finder 对话框。点击 List 按钮,列出电路所有的端子。点击 >> 按钮,全部加入。点击 OK 按钮,确认。 3.回到 Insert Node or Bus 对话框,点击 OK 按钮,确认。 4.编辑输入激励信号波形.选中 a 信号,在 Edit 菜单下,选择 Value => Clock… 命令。在随后弹出的对话框的 Period 栏目中设定参数为10ns,点击 OK 按钮,重复前面的操作,设置输入信号b的参数为20ns ,c信号的参数为30ns,d信号的参数为40ns,e信号的参数为50ns,f信号的参数为60ns,g信号的参数为70ns,h信号的参数为80ns,输入激励信号波形编辑完毕。同样的,s[0]、s[1]、s[2]的参数分别设置为10ns、20ns、30ns。 5.功能仿真:(1)Processing=>Generate Functional Simulation Netlist

电子设计技术课程设计 四位加法器 姓名:黄政 学号:2011059605 班级:通信工程zb421101 指导教师:郑雪娇 2013年12月26日 1

一、设计目的 1. 熟练使用Verilog HDL语言在mux plusⅡ软件平台上编写程序,完成编译工作。 2.学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用,了解VHDL程序的基本结构。 3.掌握使用EDA工具设计数字系统的设计思路和设计方法。学习VHDL基本逻辑电路的综合设计应用。 4.学习实验开发系统的使用方法。 二、设计内容 1、设计并调试好一个4选1数据选择器。 2、仿真、分析结果、绘制波形 三、设计过程 1、程序的设计 打开mux plusⅡ,单击file,选择new ,选择Editor file类型。进行文本编辑,编辑完成后并以“max4_1.vhd”(注意后缀是.Vhd)为文件名,存在自己建立的工程目录D:\(自己的文件夹)内。进行存盘操作时,系统在弹出的存盘操作对话框中,自动保留了上一次存盘时的文件名和文件目录,不要随意单击“OK”按钮结束存盘,一定要填入正确的文件名并选择正确的工程目录后,才能单击“OK”按钮存盘,这是上机实验时最容易忽略和出错的地方。程序设计内容如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX41A IS PORT(D3,D2,D1,D0,A1,A0,EN:IN STD_LOGIC; Y:OUT STD_LOGIC); END ENTITY MUX41A; ARCHITECTURE ONE OF MUX41A IS BEGIN Y<=D0 WHEN A1='0' AND A0='0' AND EN='1' ELSE D1 WHEN A1='0' AND A0='1' AND EN='1' ELSE D2 WHEN A1='1' AND A0='0' AND EN='1'

8选1数据选择器74L S15 1 74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。? 选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。 (1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。838电子(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。 如:CBA=000,则选择D0数据到输出端,即Y=D0。新艺图库 如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。工作原理ab126计算公式大全 74LS151功能表: 在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。 数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。 1.逻辑特性 (1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。 (2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即 数据选择器的原理 o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择 一个需要的数据送到输出端Q,为使能端,低电平有效。

深圳大学实验报告 实验课程名称:数字逻辑与数字系统 实验项目名称:数据选择器 学院:计算机与软件学院 报告人:陈文强学号:2012150295 班级:6班同组人:陈亚伟 指导教师:俞航老师 实验时间:2013-11-4 实验报告提交时间:2013-11-17

一、 说明 数据选择器是常用的组合逻辑电路之一。它有若干个数据输入端D0、D1……,若干个控制输入端、A0、A1、……和一个输出端Y 。在控制输入端加上适当的信号,即可从多个数据输入源中将所需的数据信号选择出来,送到输出端。使用时也可以在控制输入端上加上一组二进制编码程序的信号,使电路按要求输出一串信号,所以它也是一种可编程序地逻辑部件,也可以用来构成逻辑函数发生器,其方法简便,线路简单。4选1数据选择器的逻辑表达式为 10100112103Y=A A D+A A D A A D A A D ++ 所以对于任意给定的三输入变量的逻辑函数均可用4选1数据选择器来实现。同理,8选1数据选择器的逻辑表达式为 21021202110000112103204205216217Y=A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A D +++++++所以对于任意给定的四输入变量的逻辑函数均可用8选1数据选择器来实现。采用比较法用数据选择器实现单输出函数的设计步骤如下: (1) 选择接到数据选择端的函数变量。 (2) 写出数据选择器输出的逻辑表达式。 (3) 将要实现的逻辑函数转换为标准与或表达式。 (4) 对照数据选择器输出表达式和待实现函数的表达式,确定数据输入端的值。 (5) 连接电路。 二、 实验仪器与材料 RXB-1B 数字电路实验箱 器件 74LS00 四2输入与非门 74LS153 双4选1数据选择器 三、 实验任务 任务一:双4选1数据选择器74LS153功能测试 将双4选1数据选择器74LS153插入实验系统的IC 空插座中。按图2.2.1接线,把数据输入端1D3、1D2、1D0、控制输入端A1、A0和能使IST 接至DLE —6型数字电路实验箱的任意7个逻辑电平开关,输出1Y 接至实验箱电平显示器的任一LED ,设计表2.2.1中的输入状态并将结果填入表2.2.1中。 输入 输出 使能端 地址端 数据端 Y Y 1ST A1 A0 D3 D2 D1 D0 理论值 实测值 表2.2.1

4选1的数据选择器 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mux41 is port(a,b,c,d:in std_logic; s:in std_logic_vector(1 downto 0); y:out std_logic); end; architecture one of mux41 is begin y<= a when s=0 else b when s=1 else c when s=2 else d; end; 16选1数据选择器 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity mux161 is port(ain,bin,cin,din,ein,fin,gin,hin,iin,jin,kin,lin,min,nin,oin,pin:in std_logic; s1,s2:in std_logic_vector(1 downto 0); y:out std_logic); end; architecture one of mux161 is component mux41 port(a,b,c,d:in std_logic; s:in std_logic_vector(1 downto 0); y:out std_logic); end component; signal e,f,g,h:std_logic; begin u1:mux41 port map(ain,bin,cin,din,s1,e); u2:mux41 port map(ein,fin,gin,hin,s1,f); u3:mux41 port map(iin,jin,kin,lin,s1,g); u4:mux41 port map(min,nin,oin,pin,s1,h); u5:mux41 port map(e,f,g,h,s2,y); end;

DM74150,DM74151A Data Selectors/Multiplexers General Description These data selectors/multiplexers contain full on-chip decod-ing to select the desired data source.The150selects one-of-sixteen data sources;the151A selects one-of-eight data sources.The150and151A have a strobe input which must be at a low logic level to enable these devices.A high level at the strobe forces the W output high and the Y output (as applicable)low. The151A features complementary W and Y outputs, whereas the150has an inverted(W)output only. The151A incorporates address buffers which have sym-metrical propagation delay times through the complementary paths.This reduces the possibility of transients occurring at the output(s)due to changes made at the select inputs,even when the151A outputs are enabled(i.e.,strobe low).Features n150selects one-of-sixteen data lines n151A selects one-of-eight data lines n Performs parallel-to-serial conversion n Permits multiplexing from N lines to one line n Also for use as Boolean function generator n Typical average propagation delay time,data input to W output 15011ns 151A9ns n Typical power dissipation 150200mW 151A135mW n Alternate Military/Aerospace device(54150,54151A)is available.Contact a Fairchild Semiconductor Sales Office/Distributor for specifications. Connection Diagrams Dual-In-Line Package DS006546-1 Order Number54150DQMB,54150FMQB, DM54150J or DM74150N See Package Number J24A,N24A or W24C Dual-In-Line Package DS006546-2 Order Number54151ADMQB,54151AFMQB, DM54151AJ,DM54151AW or DM74151AN See Package Number J16A,N16E or W16A

电学实验报告模板 实验原理 数据选择器的功能类似一个单刀多掷开关,如图1所示。数据选择器在地址码的控制下,从多路数据输入中选择其中一个并将其送到一个公共的输出端。 图1 数据选择器示意图 1. 4选1数据选择器

图2 4选1数据选择器及其逻辑 图2所示为4选1数据选择器及其逻辑。该电路有4路输入数据和为地址输入。为使能控制端,当时,数据选择器正常工作;当时,数据选择器的输出被锁定在“0”,不能选择。 由图2(b)可以得到该数据选择器的逻辑函数式为 (1) 2. 用4选1数据选择器扩展成8选1数据选择器 8选1数据选择器有8路数据输入,3位地址输入。如果用4选1数据选择器实现8选1,需要2片4选1数据选择器,如图所示。其中,是通过4选1数据选择器的使能控制端接入的。由图5并根据式(1),可以得到 显然实现了8选1的逻辑功能。

图5 用4选1数据选择器扩展成8选1数据选择器实验仪器

实验内容及步骤 1. 测试和验证74HC153的逻辑功能 (1)集成电路芯片74HC153引脚图 74HC153是双4选1数据选择器,芯片内部包含两个独立的、完全相同的4选1数据选择器。图7-5所示为引脚图。每一个4选1数据选择器都设置了一个使能控制端。两个4选1数据选择器共享地址输入端。 图6 74HC151引脚图 (2)测试和验证74HC153的逻辑功能 按图7连接电路。实验数据记录在表7-1。验证74HC153的逻辑功能。

图7 测试74HC151的逻辑功能实验电路 表1 (3)用一片74HC153扩展成8选1数据选择器

图8 74HC153扩展成8选1数据选择器实验电路按图8连接电路。实验数据记录在表2。验证电路的逻辑功能。 表2

? 2000 Fairchild Semiconductor Corporation DS006416 https://www.doczj.com/doc/b216770267.html, August 1986Revised March 2000 DM74LS253 3-STATE Data Selector/Multiplexer DM74LS253 3-STATE Data Selector/Multiplexer General Description Each of these Schottky-clamped data selectors/multiplex-ers contains inverters and drivers to supply fully comple-mentary, on-chip, binary decoding data selection to the AND-OR gates. Separate output control inputs are pro-vided for each of the two four-line sections. The 3-STATE outputs can interface directly with data lines of bus-organized systems. With all but one of the common outputs disabled (at a high impedance state), the low impedance of the single enabled output will drive the bus line to a HIGH or LOW logic level. Features s 3-STATE version of DM74LS153 with same pinout s Schottky-diode-clamped transistors s Permit multiplexing from N-lines to one line s Performs parallel-to-serial conversion s Strobe/output control s High fanout totem-pole outputs s Typical propagation delay Data to output 12 ns Select to output 21 ns s Typical power dissipation 35 mW Ordering Code: Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code. Connection Diagram Function Table Address Inputs A and B are common to both sections.H = HIGH Level L = LOW Level X = Don't Care Z = High Impedance (OFF) Order Number Package Number Package Description DM74LS253M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow DM74LS253N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Select Data Inputs Output Output Inputs Control B A C0C1C2C3G Y X X X X X X H Z L L L X X X L L L L H X X X L H L H X L X X L L L H X H X X L H H L X X L X L L H L X X H X L H H H X X X L L L H H X X X H L H