用三极管实现逻辑电平转换

用三极管实现3V与5V混合系统中逻辑器接口问题

3V与5V混合系统中逻辑器接口问题

在电路设计当中,往往会遇到电压匹配问题,因为电路中往往不只只有一个电平信号,大部分包括3.3V,5V或者12V,但是有时候需要用到3.3V和5V的通信或者对联,这其中就存在一个电平匹配的问题,当然可以用一种很简单的方法,就是用244芯片来解决,但是有没有更简单易行的方法呢?

我在设计的过程中,也经常遇到这种问题,下面我们就通过三极管的开关作用来实现电路中多电平的共用。

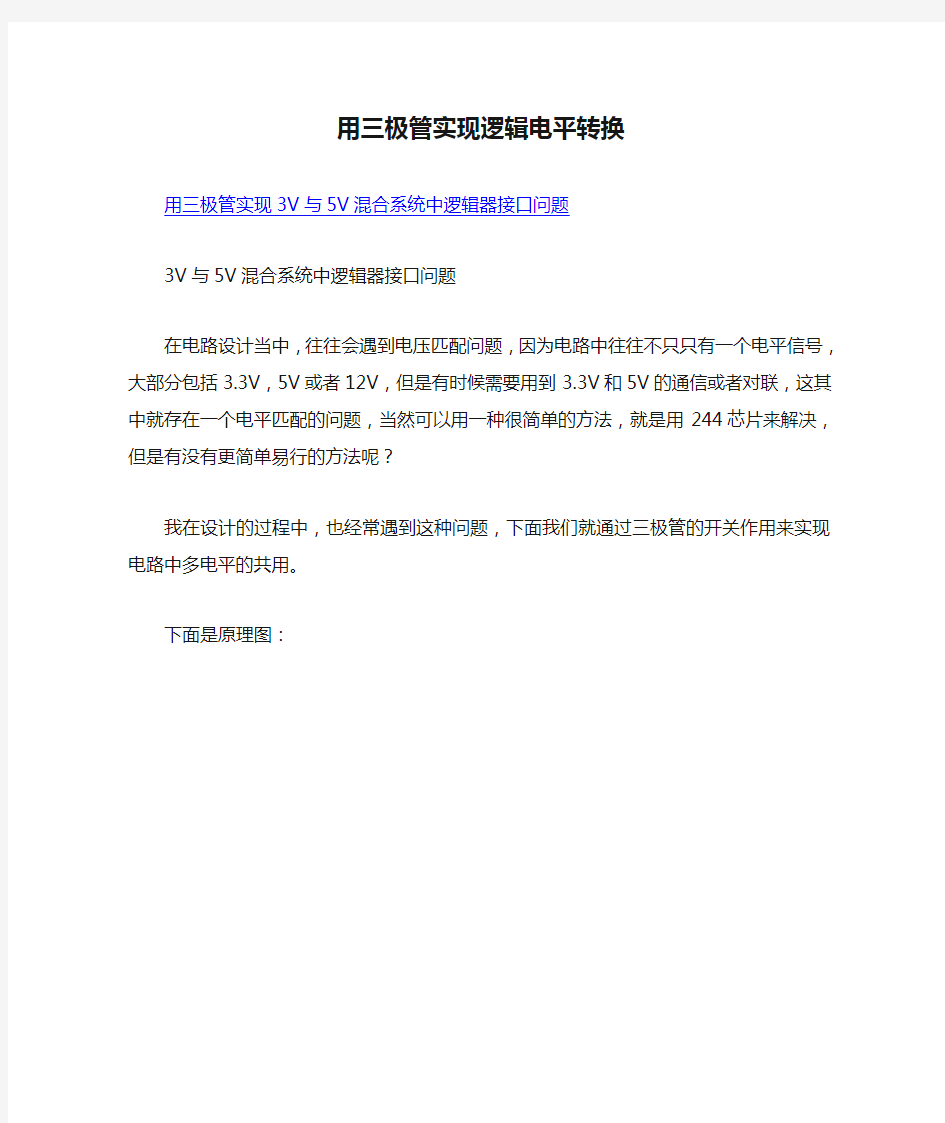

下面是原理图:

我们来首先分析一下这个电路的原理。

原理其实很简单,两个三极管和4个电阻就组成了3V到5V的电平转换功能。

5V信号从Uin输入,当Uin为高电平的时候,Q1导通,此时节电3的电压被拉底,Q2就截止,Uout输出3V,这就是实现了5V输入,3V输出的效果;当Uin为低电平的时候,Q1处于截止状态,节电3的为3V,此时Q2导通,Uout输出低电平。刚好和输入的状态相吻合,但是幅度变为3V。

再看看波形图:

以上是对5V转3V的,其实3V转5V的道理是一样的,只需要把给三极管偏置电压的VCC 换成5V的,输入3V的话,输出就是5V的了!

另外,R3一般情况下可以直接短接,因为经过了R1的限流。

如果文章中有什么不对的地方,恳请斧正,我们的目的是交流促进学习!

如果有的朋友需要电路图的实例的话,可以提供给大家!本电路时用MUlitisim 9.0进行仿真的。

(注:本资料素材和资料部分来自网络,仅供参考。请预览后才下载,期待您的好评与关注!)

详解电平种类与电平转换 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟 1) 类似。适用于器件输出刚好为 OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作3.3V→5V电平转换。 ——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。 廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那个字母 T 就表 示 TTL 兼容)。 (4) 超限输入降压法(5V→3.3V,3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采 用 3.3V 供电,就可以实现5V→3.3V电平转换。 (5) 专用电平转换芯片 最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种 5V 逻辑器件,其输入是 3.3V 电平,只要在选择器件时选择输入为 TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。

常见TTL电平转换电路 ------设计参考 1.二、三级管组成的TTL/CMOS电平转换电路,优点是价格非常低,缺点是要求使用在 信号频率较低的条件下。 建议上拉电阻为10K时,可使用在信号频率为几百Khz以下的环境中,曾经在960Khz 的串口通信中做过测试。上拉电阻越小,速率越高,但是电路的功耗也越高,在低功耗要求高的电路中需要慎重考虑。在选择二、三极管时,尽量选用结电容小,开关速率高的。 A ) 图1所示电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V。二极管选用高速肖特基二极管,并且V F尽量小,例如RB521S。 图1 B ) 图2电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V,否则PNP管可能关不断。如果对输出低电平电压幅度有较严格的要求,PNP管则选用饱和压降小些的管子。PNP管也不如NPN的通用。VCC_OUT是输出信号的电源电压。 图2

C ) 图3是NPN管组成的转换电路,对输入和输出电平的谁高谁低没有要求,适用性很好。其中VCC_IN是输入信号的电源电压,VCC_OUT是输出信号的电源电压。转换后输出的低电平VOL=Vin_Lmax+Vsat,Vin_Lmax为输入信号低电平的最高幅值,Vsat为NPN管的饱和压降,如果对输出低电平电压幅度有较严格的要求,NPN管则选用饱和压降小些的管子,以满足一般电路中VOL<0.8V的要求。 图3 2.OC/OD输出的反相器组成的电平转换电路。 图4,由2级反相器组成,反相器必须是OC/OD输出的。反相器的电源与输入信号的电平相同或者相匹配,最后的输出电平由上拉电阻上拉到输出信号的目标电平上。上拉电阻的取值直接影响功耗和可适用的信号频率。 图4

我们知道,在电路系统的各个子模块进行数据交换时可能会存在一些问题导致信号无法正常、高质量地“流通”,例如有时电路子模块各自的工作时序有偏差(如CPU与外设)或者各自的信号类型不一致(如传感器检测光信号)等,这时我们应该考虑通过相应的接口方式来很好地处理这个问题。 下面就电路设计中7个常用的接口类型的关键点进行说明一下: (1)TTL电平接口:这个接口类型基本是老生常谈的吧,从上大学学习模拟电路、数字电路开始,对于一般的电路设计,TTL电平接口基本就脱不了“干系”!它的速度一般限制在30MHz以内,这是由于BJT的输入端存在几个pF的输入电容的缘故(构成一个LPF),输入信号超过一定频率的话,信号就将“丢失”。它的驱动能力一般最大为几十个毫安。正常工作的信号电压一般较高,要是把它和信号电压较低的ECL电路接近时会产生比较明显的串扰问题。 (2)CMOS电平接口:我们对它也不陌生,也是经常和它打交道了,一些关于CMOS 的半导体特性在这里就不必啰嗦了。许多人都知道的是,正常情况下CMOS的功耗和抗干扰能力远优于TTL。但是!鲜为人知的是,在高转换频率时,CMOS系列实际上却比TTL消耗更多的功率,至于为什么是这样,请去问半导体物理理论吧。由于CMOS的工作电压目前已经可以很小了,有的FPGA内核工作电压甚至接近1.5V,这样就使得电平之间的噪声容限比TTL小了很多,因此更加加重了由于电压波动而引发的信号判断错误。众所周知,CMOS电路的输入阻抗是很高的,因此,它的耦合电容容量可以很小,而不需要使用大的电解电容器了。由于CMOS 电路通常驱动能力较弱,所以必须先进行TTL转换后再驱动ECL电路。此外,设计CMOS接口电路时,要注意避免容性负载过重,否则的话会使得上升时间变慢,而且驱动器件的功耗也将增加(因为容性负载并不耗费功率)。 (3)ECL电平接口:这可是计算机系统内部的老朋友啊!因为它的速度“跑”得够快,甚至可以跑到几百MHz!这是由于ECL内部的BJT在导通时并没有处于饱和状态,这样就可以减少BJT的导通和截止时间,工作速度自然也就可以提上去了。But,这是要付出代价的!它的致命伤:功耗较大!它引发的EMI问题也就值得考虑了,抗干扰能力也就好不到哪去了,要是谁能够折中好这两点因素的话,那么他(她)就该发大财了。还有要注意的是,一般ECL集成电路是需要负电源供电的,也就是说它的输出电压为负值,这时就需要专门的电平移动电路了。 (4)RS-232电平接口:玩电子技术的基本没有谁不知道它的了(除非他或她只是电子技术专业的“门外汉”)。它是低速串行通信接口标准,要注意的是,它的电平标准有点“反常”:高电平为-12V,而低电平为+12V。So,当我们试图通过计算机与外设进行通信时,一个电平转换芯片MAX232自然是少不了的了。但是我们得清醒地意识到它的一些缺点,例如数据传输速度还是比较慢、传输距离也较短等。 (5)差分平衡电平接口:它是用一对接线端A和B的相对输出电压(uA-uB)来表示信号的,一般情况下,这个差分信号会在信号传输时经过一个复杂的噪声环境,导致两根线上都产生基本上相同数量的噪声,而在接收端将会把噪声的能量

5V-3.3V电平转换方法 在实际电路设计中,一个电路中会有不同的电平信号。 方案一:使用光耦进行电平转换 首先要根据要处理的信号的频率来选择合适的光耦。高频(20K~1MHz)可以用高速带放大整形的光藕,如6N137/TLP113/TLP2630/4N25等。如果是20KHz以下可用TLP521。然后搭建转换电路。如将3.3V信号转换为5V信号。电路如下图: CP是3.3V的高速信号,通过高速光耦6N137转换成5V信号。如果CP接入的是5V 的信号VCC=3.3V,则该电路是将5V信号转换成3.3V信号。优点:电路搭建简单,可以调制出良好的波形,另外光耦还有隔离作用。缺点:对输入信号的频率有一定的限制。 方案二:使用三极管搭建转换电路 三极管的开关频率很高,一般都是几百兆赫兹,但是与方案一相比,电路搭建相对麻烦,而且输出的波形也没有方案一的好。 电路如下图: 其中C1为加速电容,R1为基极限流电阻,R2为集电极上拉电阻,R3将输入端下拉到地,保证在没有输入的情况下,输出端能稳定输出高电平。同时在三极管截止时给基区过量的电荷提供泄放回路缩短三极管的退饱和时间。 优点:开关频率高,在不要求隔离,考虑性价比的情况下,此电路是很好的选择。 缺点:输出波形不是很良好。 方案三:电阻分压 这里分析TTL电平和COMS电平的转换。首先看一下TTL电平和CMOS电平的区别。 TTL电平:输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2。最小输入高电平>=2.0V,输入低电平<=0.8,噪声容限是0.4V。 CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且有很宽的噪声容限。 下面的电路是将5V的TTL电平转换成3V的TTL电平

在各个领域中常用芯片汇总 1. 音频pcm编码DA转换芯片cirrus logic的cs4344,cs4334,4334是老封装,据说已经停产,4344封装比较小,非常好用。还有菲利谱的8211等。 2. 音频放大芯片4558,833,此二芯片都是双运放。为什么不用324等运放个人觉得应该是对音频的频率响应比较好。 3. 74HC244和245,由于244是单向a=b的所以只是单向驱动。而245是用于数据总线等双向驱动选择。同时245的封装走线非常适合数据总线,它按照顺序d7-d0。 4. 373和374,地址锁存器,一个电平触发,一个沿触发。373用在单片机p0地址锁存,当然是扩展外部ram的时候用到62256。374有时候也用在锁数码管内容显示。 5. max232和max202,有些为了节约成本就用max202,主要是驱动能力的限制。 6. 网络接口变压器。需要注意差分信号的等长和尽量短的规则。 7. amd29系列的flash,有bottom型和top型,主要区别是loader区域设置在哪里?bottom型的在开始地址空间,top型号的在末尾地址空间,我感觉有点反,但实际就是这么命名的。 8. 164,它是一个串并转换芯片,可以把串行信号变为并行信号,控制数码管显示可以用到。 9. sdram,ddrram,在设计时候通常会在数据地址总线上加22,33的电阻,据说是为了阻抗匹配,对于这点我理论基础学到过,但实际上没什么深刻理解。 10. 网卡控制芯片ax88796,rtl8019as,dm9000ae当然这些都是用在isa总线上的。 11. 24位AD:CS5532,LPC2413效果还可以 12. 仪表运放:ITL114,不过据说功耗有点大 13. 音频功放:一般用LM368 14. 音量控制IC. PT2257/9. 15. PCM双向解/编码ADC/DAC CW6691.

CAN总线/RS232智能电平转换器的设计 1 引言CAN,全称为Controller Area Network,即控制器局域网,是一种国际标准的,高性价的现场总线,在自动控制领域具有重要作用。CAN 是一种多主方式的串行通讯总线,具有较高的实时性能,因此,广泛应用于汽车工业、航空工业、工业控制、安全防护等领域。由于PC 机无CAN 接口,因此,PC 机与智能节点构成CAN 总线系统可采用RS232/CAN、并口 /CAN、USB/CAN、ISA 卡/CAN 以及PCI 卡/CAN 方式接入。而采用 RS232/CAN 接入时,需采用CAN/RS232 接口标准转换。针对这一问题,提出了CAN/RS232 智能电平转换器设计方案,以SJAl000 作为独立CAN 控制器,完成CAN 通信协议。并在SJAl000 与驱动器之间连接高速光耦,从而实 现总线各点间的电气隔离。2 硬件电路设计CAN/RS232 智能电平转换器硬件电路主要由微处理器AT89C52、独立CAN 通讯控制器SJAl000、CAN 总线驱动器82C250、高速光电耦合器6N136、TTL 电平与RS232 电平转换器 ICL232、LED 数码管显示电路以及为SJAl000 提供初始地址的拨码电路组成,其结构框图如图1 所示。3 CAN 控制器SJAlOOOSJAl000 是一款独立CAN 控制器,应用于移动目标和工业局域区域网控制领域。该器件是Philips 公司 CAN 控制器PCA82C200 的替代产品。SJAl000 具有两种工作模式,本设计采用PeliCAN 工作模式。3.1 SJAl000 与AT89C52 的接口设计SJAl000 与AT89C52 的接口电路如图2 所示。AT89C52 负责sJAl000 的初始化,控制SJAl000 来实现数据的接收和发送等通讯任务。SJAl000 的ADO~AD7 连接至AT89C52 的P0 端口,CS 连接至AT89C52 的P3.4(AT89C52 的定时器T0 不起作用)。当P3.4 为0 时,AT89C52 选中SJAl000,并通过访问外部RAM 低地址区实现P0 端口的读/写操作,从而对SJAl000 相应寄存器执行读/写操

1概要 随着通讯速度的提升,出现了很多差分传输接口,以提升性能,降低电源功耗和成本。早期的技术,诸如emitter-coupled logic(ECL),使用不变的负电源供电,在当时用以提升噪声抑制。随着正电压供电技术发展,诸如TTL和CMOS技术,原先的技术优点开始消失,因为他们需要一些-5.2V或-4.5V的电平。在这种背景下,ECL转变为positive/pseduo emitter-coupled logic (PECL),简化了板级布线,摒弃了负电平供电。PECL要求提供800mV的电压摆幅,并且使用5V对地的电压。LVPECL类似于PECL也就是3.3V供电,其在电源功耗上有着优点。 当越来越多的设计采用以CMOS为基础的技术,新的高速驱动电路开始不断涌现,诸如current mode lo gic(CML),votage mode logic(VML),low-voltage differential signaling(LVDS)。这些不同的接口要求不同的电压摆幅,在一个系统中他们之间的连接也需要不同的电路。 本应用手册主要内容为:TI的不同的SERDES器件,输入输出结构,多种高速驱动器,以及偏置和终端电路。 在不同的接口之间,往往采用交流耦合的方式(ac-coupling),从而可以独立的对驱动器和接收器进行处理。 1. 不同接口之间的转换 2. 不同信号电平的转换 3. 不同地之间的转换 2各信号电平 第一步首先是理解各个接口点逻辑电平,主要讨论LVPECL,CML,VML,以及LVDS。 表一为这些接口的输出电平。 项目LVPECL CML VML LVDS VOH 2.4V 1.9V 1.65V 1.4V VOL 1.6V 1.1V 0.85V 1V 输出电压(单 800mV 800mV 800mV 400mV 端) 1.25V 1.2V 共模电压2V 1.5V (VCC-0.2V)1 表一,各接口电平规范 图一 3输入输出结构 在上文中提到了关于LVPECL,CML,VML以及LVDS驱动器,这些都是基于CMOS技术的。这个部分介绍各个种类的输入输出结果。 3.1 LVPECL接口

2013年1月8日 15:17 源文档

不同逻辑电平器件的互连问题分析 1:逻辑器件的互连总则 在不同逻辑电平器件之间进行互连时主要考虑以下几点: ?电平关系,必须保证在各自的电平范围内工作,否则,不能满足正常逻辑功能,严重时会烧毁芯片。 ?驱动能力,必须根据器件的特性参数仔细考虑,计算和试验,否则很可能造成隐患,在电源波动,受到干扰时系统就会崩溃。 ?时延特性,在高速信号进行逻辑电平转换时,会带来较大的延时,设计时一定要充分考虑其容限。 选用电平转换逻辑芯片时应慎重考虑,反复对比。通常逻辑电平转换芯片为通用转换芯片,可靠性高,设计方便,简化了电路,但对于具体的设计电路一定要考虑以上三种情况,合理选用。 对于数字电路来说,各种器件所需的输入电流、输出驱动电流不同,为了驱动大电流器件、远距离传输、同时驱动多个器件,都需要审查电流驱动能力:输出电流应大于负载所需输入电流;另一方面,TTL、CMOS、ECL等输入、输出电平标准不一致,同时采用上述多种器件时应考虑电平之间的转换问题。 我们在电路设计中经常遇到不同的逻辑电平之间的互连,不同的互连方法对电路造成以下影响: ?对逻辑电平的影响。应保证合格的噪声容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax ≥0.4V),并且输出电压不超过输入电压允许范围。 ?对上升/下降时间的影响。应保证Tplh和Tphl满足电路时序关系的要求和EMC的要求。 ?对电压过冲的影响。过冲不应超出器件允许电压绝对最大值,否则有可能导致器件损坏。

TTL和CMOS的逻辑电平关系如下图所示: 图1: TTL和CMOS的逻辑电平关系图 图2:低电压逻辑电平标准 3.3V的逻辑电平标准如前面所述有三种,实际的3.3V TTL/CMOS逻辑器件的输入电平参数一般都使用LVTTL或3.3V逻辑电平标准(一般很少使用LVCMOS输入电平),输出电平参数在

Application Report SCEA044–June2010 A Guide to Voltage Translation With TXS-Type Translators Dave Moon,Aeysha Sultana High Volume Linear ABSTRACT Modern trends are driving the need for lower supply voltages across many system-level designs.As most processor voltage levels continue to decrease in the interest of achieving the lowest possible power consumption,peripheral devices maintain a need for higher voltage levels,creating potential for voltage discontinuities within a system.To remedy this mixed voltage system incompatibility,a voltage translator can be used. Texas Instruments High Volume Linear group offers a wide-range of voltage level translators.A variety of architectures provide solutions for different application environments including dual-supply direction-controlled,auto-direction sensing,and application-specific memory card interface translators. The information in this application report is intended to help system designers understand the architecture and operation of the TXS-type auto-direction sensing translator family Contents 1The Need For Voltage-Level Translation (2) 2Auto-Direction Sensing Voltage Translator Architecture (2) 3Input Driver Requirements With TXS-Type Translators (6) 4Driving External Loads With TXS-Type Translators (7) 5Output Enable Control (7) 6Conclusion (7) List of Figures 1Digital Switching Levels (2) 2Basic TXS0101,TXS0102,and TXS0104Architecture (3) 3Transfer Characterisitics of an N-Channel Transistor (3) 4Basic TXS0108E Architecture (4) 5TXS0108E During Low-to-High Signal Transition (5) 6TXS0108E During High-to-Low Signal Transition (6) 1 SCEA044–June2010A Guide to Voltage Translation With TXS-Type Translators Copyright?2010,Texas Instruments Incorporated

电平信号及接口电路 ——————————————————————————————————— 摘要:介绍了目前数字信号设计中,IC芯片常用电平的原理、应用及各种电平信号相互转换的实现方法,PCB布线技巧等。 关键词:TTL、CMOS、ECL、PECL、LVPECL、LVDS、CML 概述 随着数据传输业务需求的增加,如何高质量的解决高速IC 芯片间的互连变得越来越重要。从目前发展来看,芯片主要有以下几种接口电平:TTL(LVTTL)、CMOS、ECL、PECL、LVPECL、LVDS等,其中PECL、LVPECL、LVDS主要应用在高速芯片的接口,不同电平间是不能直接互连的,需要相应的电平转换电路和转换芯片,了解各种电平的结构及性能参数对分析电路是十分必要有益的,本文正是从各种电平信号的性能参数开始,结合参考资料对电平信号的互连进行介绍。 图1 常用电平信号 图1展示了各种电平信号的差异:方波的振幅表示逻辑高低电平值,括号中的电压值表示电源电压值。 下面先介绍一下电路的相关基本概念: (1)输出高电平(VOH):逻辑电平为1的输出电压,相应的输出电流用I OH表示。 (2)输出低电平(VOL):逻辑电平为0的输出电压,相应的输出电流用I OL表示。 (3)输入高电平(VIH):逻辑电平为1的输入电压,相应的输入电流用I IH表示。 (4)输入低电平(VIL):逻辑电平为0的输入电压,相应的输入电流用I IL表示。 (5)关门电平(V OFF):保证输出为标准高电平V SH(出厂时厂家给出)的条件下所允许的最大 输入低电平值。 (6)开门电平(V ON):保证输出为标准低电平V SL(出厂时厂家给出)的条件下所允许的最小输 入高电平值。 (7)低电平噪声容限(V NL):是保证输出高电平的前提下,允许叠加在输入低电平上的最大噪 声电压,其数值为关门电平V OFF与输入最小低电平的差值。 (8)高电平噪声容限(V NH):是保证输出低电平的前提下,允许叠加在输入高电平上的最大噪 声电压,其数值为输入最大低电平与开门电平V ON的差值。 (9) 输出差分信号

3.3V转5V的双向电平转换电路 说说所有的电平转换方法,你自己参考~ (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母 T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如74HC 系列为20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种5V 逻辑器件,其输入是3.3V 电平,只要在选择器件时选择输入为TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。 (9) 比较器法 算是凑数,有人提出用这个而已,还有什么运放法就太恶搞了。 那位说的可以~但我分析你也不是非要芯片不可吧?尽量节约成本啊~ 3.3V转5V 电平转换方法参考 电平转换

1. 简介 在今天的电子电路系统中电压电平的转换基本成为了必须。例如:一 个ASIC的供电为VccA,而I/O器件的供电为VccB。为了使它们之间正常通信,就需要一个如图1的电平转换(level-translation)方案。 输入电平限值和器件的输出电平主要根据器件采用的工艺技术和供电 。图2显示了不同的供电和元件技术的限值范围。为了成功的实现两个 器件的接口,一定要保证以下的条件: ■驱动器件的Voh必须大于接收器件的Vih ■驱动器件的Vol必须小于接收器件的Vil ■驱动器件的输出电压范围不能超过接收器件的可容忍的I/O电 压范围

2. 双电源电平转换器件(Dual-Supply Level Translators) 2.1 特性 双电源的器件是为了满足两类总线或不同供电器件之间的异步通讯的 。这类器件采用双电源:VccA为A端(A side)供电,VccB为B端供电。对于数据从A到B或B到A都能传输的双向的电平转换器件,方向取决于输入pin DIR的逻辑电平。如果器件有OE控制,在OE有无效时 A端和B端的总线隔离。 TI的双电源器件有各种位宽的应用并几乎覆盖了当前出现的全部的供 电应用。这些器件灵活,易用并能实现双向转换,对于许多电平转换 的应用都是理想的选择(译者注:强!)。它们的电流驱动能力可以 使其适合长线及重载的应用。 SN74AVCB324245是一种32位双电源电平转换器件(由四组8位端口组成)。图3显示了SN74AVCB324245的1.8V转3.3V的一个端口,同

时另一个端口实现3.3V到1.8V的转换。 双电源器件的优点: ●可以在不同电压结点间灵活的转换 ●具有电流驱动的能力 ●具有不同的位宽 2.2 产品列表

常用的电平转换方案 TTL、CMOS、ECL等电路的高低电平阀值不同,他们之间逻辑连接需要电平转换;还有,就是接口与接口之间的,如RS232与485之间,USB与串口之间等等,由于这些接口协议里面定义的电平不同,所以也需要电平转换。 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 图1. 电阻-二极管拓扑,是在同一根信号线上实现双向转换的可选技术之一

图2. 分立/数字晶体管是实现双向转换的另外一种选择 (数据入和数据出也被称为主入从出(MISO)和主出从入(MOSI)。SPI能够使用超过20Mbp的时钟信号,使用CMOS推挽逻辑。由于SPI是单向的,没有必要在同一根信号线上实现双向转换。这使电平转换变得简单一些,因为 可以采用电阻与二极管(图1)或分立/数字晶体管(图2)等简单方案。I2C、SMBusTM和1-Wire 接口为双向、漏极开路拓?扑。I2C有3个速度范围:≤ 100kbps的标准模式,≤ 400kbps的快速模式,≤ 3.4Mbps的高速模式。双向总线的电平转换更加困难,因为必须在同一根数据线上进行双向转换。基于电阻-二极管或集电极/漏极开路的单级晶体管转换器的简单拓扑由于固有的单向性,无法满足要求。 ) (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作 3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用 3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

逻辑电平转换器 在新一代电子产品设计中,TTL或5V CMOS电平已不再占据逻辑电路统治地位。随着低电压逻辑的引入,系统内部常常出现输入/输出逻辑不协调的问题,从而提高了系统设计的复杂性。例如,当1.8V的数字电路与工作在3.3V的模拟电路进行通信时,需要首先解决两种电平转换问题,本文介绍了不同逻辑电平之间的转换方法。 1 逻辑电平转换的必要性 型号I/O通道数单向/双向 Rx/Tx V L范围Vcc范围独立使能速率 MAX3001 8 双向,8/8 1.2V~5.5V 1.65V~5.5V Yes 4Mbps MAX3370 1 双向,1/1 1.65V~ 5.5V 2.5V~5.5V No 2Mbps MAX3371 1 双向,1/1 1.65V~ 5.5V 2.5V~5.5V Yes 2Mbps MAX3372/3 2 双向,2/2 1.2~5.5V 1.65V~5.5V Yes 230kbps MAX3374 MAX3375 MAX3376 2 单向,2/0 单向,1/1 单向,0/2 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3377 MAX3378 4 双向,4/4 1.2~5.5V 1.65V~5.5V Yes 230kbps MAX3379 4 单向,4/0 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3390 4 单向,3/1 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3391 4 单向,2/2 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3392 4 单向,1/3 1.2~5.5V 1.65V~5.5V Yes 16Mbps MAX3393 4 单向,0/4 1.2~5.5V 1.65V~5.5V Yes 16Mbps 随着不同工作电压的数字IC的不断涌现,逻辑电平转换的必要性更加突出,电平转换方式也将随逻辑电压、数据总线的形式(例如4线SPI、32位并行数据总线等)以及数据传输速率的不同而改变。现在虽然许多逻辑芯片都能实现较高的逻辑电平至较低逻辑电平的转换(如将5V电平转换至3V电平),但极少有逻辑电路芯片能够较低的逻辑电平转换成较高的逻辑电平(如将3V逻辑转换至5V逻辑)。另外,电平转换器虽然也可以用晶体管甚至电阻——二极管的组合来实现,但因受寄生电容的影响,这些方法大大限制了数据的传输速率。

3.3v和5v双向电平转换芯片 74LVC4245,8位电平转换 74LVC4245A,8位双向 NLSX4373,2位电平转换 NLSX4014,4位电平转换 NLSX4378,4位电平转换 NLSX3018,8位电平转换 max3002,8路双向 TXB0104?(她好像有一个系列?0102?0104?0106?0108), ADG3308 74HCT245:三态输出的八路总线收发器 SN74AVCH2T45 SN74AVC16T245:具有可配置电压转换和3 态输出的16 位双电源总线收发器 SN74LVC2T45DCT:双位双电源总线收发器可配置电压转换和三态输出 SN74LVC4245A:8位 德州仪器宣布推出SN74LVC1T45、SN74LVC2T45、SN74AVC8T245及SN74AVC20T245四款新型双电源电平转换收发器。该新品能够在 1.5V、1.8V、2.5V、3.3V 与5V 电压节点之间进行灵活的双向电平转换,而且可提供全面的可配置性。如果采用AVC 技术,则每条轨可从 1.4V 配置为 3.6V;而采用LVC 技术时则可从1.65V 配置为5.5V。适用于便携式消费类电子产品、网络、数据通信以及计算应用领域。 日前,德州仪器(TI)宣布推出四款新型的双电源电平转换器--AVC1T45、AVC2T45、AVC16T245及AVC32T245,从而进一步扩展其电平转换产品系列。这些转换器能够在互不兼容的I/O之间进行通信。这四款器件均支持1.2V、1.5V、1.8V、2.5V与3.3V节点之间的双向电平转换。在混合信号环境中,可以使用这些电压电平的任意组合,从而提高这些器件的灵活性。 1位AVC1T45与2位AVC2T45可根据需要在电路板上集成单或双转换器功能,而不是通过较高位宽的器件进行路由,这有助于简化电路板布线作业(board routing),可适用于便携式手持应用的转换要求。AVC16T245与AVC32T245是TI当前16位与32位双电源转换功能的改进版本。这些器件能够提供较低的功耗(AVC16T245的功耗为25μA,而AVCA164245的功耗则为40μA)。该类器件的总线控制选件无需外部上拉/下拉电阻器。TI还提供全面的IBIS模型支持。 SN74AVC1T45与SN74AVC2T45以及总线控制版本SN74AVCH1T45与SN74AVCH2T45均采用NanoStar 与NanoFree芯片级封装。这些器件现已推出,并可提供样片。批量为千套时,预计1T45器件的最低零售单价为0.24美元,而2T45器件的最低零售单价为0.35美元。 SN74AVC16T245和总线控制版本SN74AVCH16T245采用56球栅VFBGA封装。该器件现已推出,并可提

IIC的5V和3.3V电平转换的经典电路 在电平转换器的操作中要考虑下面的三种状态: 1 没有器件下拉总线线路。“低电压”部分的总线线路通过上拉电阻Rp上拉至3.3V。MOS-FET 管的门极和源极都是3.3V,所以它的VGS 低于阀值电压,MOS-FET 管不导通。这就允许“高电压”部分的总线线路通过它的上拉电阻Rp拉到5V。此时两部分的总线线路都是高电平,只是电压电平不同。 2 一个3.3V 器件下拉总线线路到低电平。MOS-FET 管的源极也变成低电平,而门极是3.3V。VGS上升高于阀值,MOS-FET 管开始导通。然后“高电压”部分的总线线路通过导通的MOS-FET管被3.3V 器件下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。 3 一个5V 的器件下拉总线线路到低电平。MOS-FET 管的漏极基底二极管“低电压”部分被下拉直到VGS 超过阀值,MOS-FET 管开始导通。“低电压”部分的总线线路通过导通的MOS-FET 管被5V 的器件进一步下拉到低电平。此时,两部分的总线线路都是低电平,而且电压电平相同。 这三种状态显示了逻辑电平在总线系统的两个方向上传输,与驱动的部分无关。状态1 执行了电平转换功能。状态2 和3 按照I2C 总线规范的要求在两部分的总线线路之间实现“线与”的功能。 除了3.3V VDD1 和5V VDD2 的电源电压外,还可以是例如:2.5V VDD1 和12V VDD2。在正常操作中,VDD2必须等于或高于VDD1(在开关电源时允许VDD2 低于VDD1)。

MOS-N 场效应管双向电平转换电路-- 适用于低频信号电平转换的简单应用 如上图所示,是MOS-N 场效应管双向电平转换电路。 双向传输原理: 为了方便讲述,定义 3.3V 为 A 端,5.0V 为 B 端。 A端输出低电平时(0V),MOS管导通,B端输出是低电平(0V) A端输出高电平时(3.3V),MOS管截至,B端输出是高电平(5V) A端输出高阻时(OC),MOS管截至,B端输出是高电平(5V) B端输出低电平时(0V),MOS管内的二极管导通,从而使MOS管导通,A端输出是低电平(0V)B端输出高电平时(5V),MOS管截至,A端输出是高电平(3.3V) B端输出高阻时(OC),MOS管截至,A端输出是高电平(3.3V) 优点: 1、适用于低频信号电平转换,价格低廉。 2、导通后,压降比三极管小。 3、正反向双向导通,相当于机械开关。 4、电压型驱动,当然也需要一定的驱动电流,而且有的应用也许比三极管大。

TTL和CMOS电平总结 TTL和CMOS电平总结 TTL——Transistor-Transistor Logic HTTL——High-speed TTL LTTL——Low-power TTL STTL——Schottky TTL LSTTL——Low-power Schottky TTL ASTTL——Advanced Schottky TTL ALSTTL——Advanced Low-power Schottky TTL FAST(F)——Fairchild Advanced schottky TTL CMOS——Complementary metal-oxide-semiconductor HC/HCT——High-speed CMOS Logic(HCT与TTL电平兼容) AC/ACT——Advanced CMOS Logic(ACT与TTL电平兼容)(亦称ACL) AHC/AHCT——Advanced High-speed CMOS Logic(AHCT与TTL电平兼容) FCT——FACT扩展系列,与TTL电平兼容 FACT——Fairchild Advanced CMOS Technology 1,TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平 是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。 2,CMOS电平: 1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。 3,电平转换电路: 因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需 要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。哈哈 4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱 动门电路。 5,TTL和COMS电路比较: 1)TTL电路是电流控制器件,而coms电路是电压控制器件。 2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。 COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。 COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常