内存的工作原理及时序介绍

第一部分:工作原理

DRAM基本组成

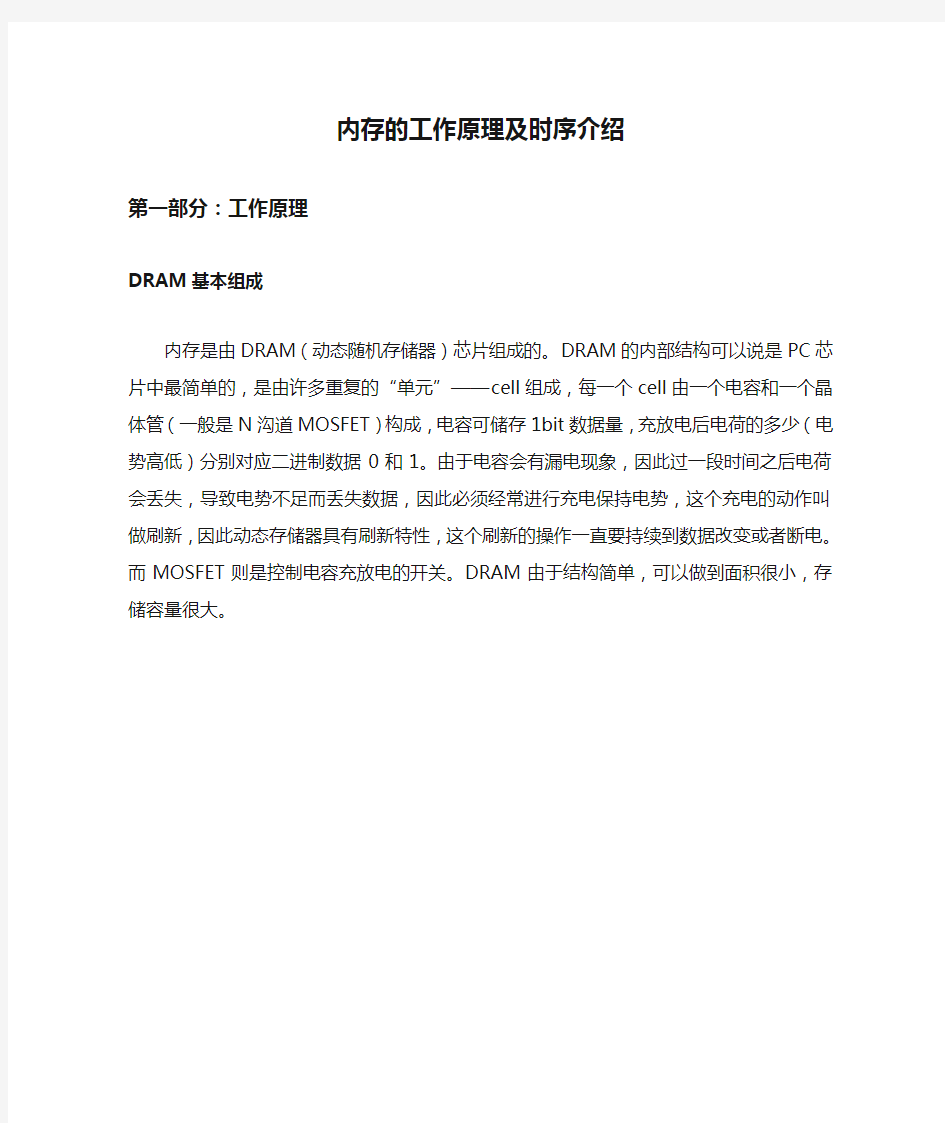

内存是由DRAM(动态随机存储器)芯片组成的。DRAM的内部结构可以说是PC芯片中最简单的,是由许多重复的“单元”——cell组成,每一个cell由一个电容和一个晶体管(一般是N沟道MOSFET)构成,电容可储存1bit数据量,充放电后电荷的多少(电势高低)分别对应二进制数据0和1。由于电容会有漏电现象,因此过一段时间之后电荷会丢失,导致电势不足而丢失数据,因此必须经常进行充电保持电势,这个充电的动作叫做刷新,因此动态存储器具有刷新特性,这个刷新的操作一直要持续到数据改变或者断电。而MOSFET则是控制电容充放电的开关。DRAM由于结构简单,可以做到面积很小,存储容量很大。

内存地址

内存中的cell按矩阵形排列,每一行和每一列都会有一个对应的行地址线路(正规叫法叫做word line)和列地址线路(正规叫法是bit line),每个具体的cell就挂接在这样的行地址线路和列地址线路上,对应一个唯一的行号和列号,把行号和列号组合在一起,就是内存的地址。

上图是Thaiphoon Burner的一个SPD dump,每个地址是一个字节。不过我们可以把这些数据假设成只有一个bit,当成是一个简单的内存地址表,左边竖着的是行地址,上方横着的是列地址。例如我们要找第七行、倒数第二列(地址为7E)的数据,它就只有一个对应的值:FD。当然了,在内存的cell中,它只能是0或者1。

寻址

数据要写入内存的一个cell,或者从内存中的一个cell读取数据,首先要完成对这个cell的寻址。寻址的过程,首先是将需要操作的cell的对应行地址信号和列地址信号输入行/列地址缓冲器,然后先通过行解码器(Row Decoder)选择特定的行地址线路,以激活特定的行地址。每一条行地址线路会与多条列地址线路和cell相连接,为了侦测列地址线路上微弱的激活信号,还需要一个额外的感应放大器(Sense Amplifier)放大这个信号。当行激活之后,列地址缓冲器中的列地址信号通过列解码器(Column Decoder)确定列地址,并被对应的感应放大器通过连接IO线路,这样cell就被激活,并可供读写操作,寻址完成。从行地址激活,到找到列地址这段时间,就是tRCD。

内存cell的基本操作

内存中的cell可以分为3个基本操作,数据的储存、写入与读取。为了便于理解,我不打算直接从电路控制上对cell操作进行说明,而是希望通过模型类比来达到说明问题的目的,如有不严谨之处,高手勿怪。要对内存cell进行读写操作,首先要完成上述寻址过程,并且电容的充电状态信号要被感应放大器感应到,并且放大,然后MOSFET打开,电容放电,产生电势变化,把电荷输送到IO线路,导致线路的电势也变化。当然,这只是个简单的描述,以下我们先来了解硅晶体中“电容”的结构和MOSFET的控制原理。

硅晶体中的“电容”

这里之所以“电容”两个字被打上引号,是因为硅晶体中并没有真正意义上的电容。硅晶体中的电容是由两个对置的触发器组成的等效电容。例如两个非门(Nor Gate)用如下图的方式对接。它可以通过周期性施加特定的输入信号,以把电荷保留在电路中,充当电容的作用。如下图,两个非门的输入端R和S互相交替做0和1输入,就可以把电荷储存在电路中。整

个动态过程就是这样:

而R和S的波形就是如下图所示,刚好互为反相,差半个周期:

要让电容放电,我们只需要把R和S同时输入1或者0即可。因此这种电容的逻辑关系很简单:在同一时刻R和S输入状态不同(即存在电势差)时,电容为充电状态;在同一时刻R 和S输入状态相同(即电势差为0)时,电容为放电状态。

MOSFET的控制原理——水库模型

要说明这个MOSFET的控制原理,我们借助一个水库的模型来说明。MOSFET有三个极,分别是源极(Source)、漏极(Drain)和栅极(Gate)。下图左边就是一个MOSFET的电路图,右边是我们画出的一个水库模型。

图中S为源极,D为漏极,G为栅极。S极连接着电容,D级连接列地址线路,并接到数据IO,G则是控制电荷流出的阀门,连接行地址线路。电容在充电后电势会改变,这样S极的电势就会跟着改变,与D极形成电势差,而G极的电势,就决定了S极有多少电荷可以流入D极。由于电子是带负电荷,因此电子越多电势就越低。为了不至于混淆概念,我们把水池顶部电势定为0V,水池底部电势定为5V(仅举例说明,DRAM中的电容实际电压未必是5V)。当电子数量越多时,电势越低,接近0V,电子数量越少时,电势越高,接近5V。

用水库模型说明,就是左边的水池水量升高(电容充电后),当阀门关闭时,左边的水是不会往右边流的。然后阀门打开(降低,电势升高),左边的水就可以往右边流,阀门的高度就决定了有多少水能流去右边的水道(但是在数字电路中,MOSFET只有开和关两种状态,因此下文提到的打开MOSFET就是全开);同样道理如果右边水多,阀门打开之后也可以向左边流。因此在水库模型中,电容就充当了左边的水池,而MOSFET的栅极就充当了阀门,列地址线路和IO则充当了右边的水道。

储存数据

MOSFET栅极电势为0V时,电容的电荷不会流出,因此数据就可以保存我们可以用2.5V为参考分界线,电容电势低于2.5V时,表示数据0,电势高于2.5V时,表示数据1。例如上一楼水库模型的左图,电容中储存的电子数高于一半的高度,电势低于2.5V,因此可以表示数据0。但以上只是理论情况,实际上电容会自然漏电,电子数量会逐渐减少,电势就会逐渐升高,当电势升高到2.5V以上时,数据就会出错,因此每隔一段时间必须打开MOSFET 往电容中充电,以保持电势,这就是刷新。因此,数据的储存主要就是对电容中电势的保持操作。

写入数据

数据写入的操作分为写入0和写入1两种情况。写入前,电容原有的情况可能是高电势与低电势的状态,我们不用管它。写入0和写入1对cell的操作不尽相同,我们分别来看。

先来看写入0的操作。写入开始时,IO线路上电势为0(水道处于水位最高点),MOSFET 栅极电势升高到5V(水库阀门降到最低),阀门打开,电容中的电势就跟着降低(水位升高),直到接近0V(水池被灌满),写入0完成,栅极电势降回0V,阀门关闭。

再看写入1的操作。写入开始时,IO线路上的电势为5V(水道水位为最低点),MOSFET栅极电势升高到5V(水库阀门降到最低),阀门打开,电容中的电势跟着升高(水流出并降低水位)到接近5V,写入1完成,栅极电势回到0V,阀门关闭。

读取数据

读取的时候,对漏极的电压操作跟写入有些不同。因为水道中的水比水池中的多,或者说水道的容量比水池要大得多。如果水道(漏极)的水为满或者空,在阀门打开的时候很容易出现水道的水倒灌进水池的现象,或是水池的水全部流去水道,这样就有可能导致电容中的电势状态改变,电容对应储存的0或者1也会改变。所以读取数据的时候,IO线路的电压应为1/2的满电势,即2.5V。

读取也同样分读取0和1两种情况。在读取之前,电容中的电势应该是大于或者小于2.5V

的,分别代表存储了1和0。由于刷新机制的存在,应该不会允许出现等于2.5V的情况。

首先看读取0操作。电容中为低电势(假设为0V,水池为高水位),IO线路上电势升高至2.5V(这时水道水位比水池低),MOSFET栅极电势升高到5V(水库阀门降到最低),阀门打开,电容中电势升高(水位降低),但由于水道容量较大,因此水位不会升高太多,但是总归也会有个电势的变低,最终电容与IO线路上的电势都变成0-2.5V的一个中间值,并且接近2.5V(假设为2.3V)。这时候感应放大器检测到IO线路上电势低于2.5V,因此识别出0读出。

再看读取1操作。电容中为高电势(假设为5V,水池空),IO线路上电势升高至2.5V(这时候水道水位比水池高),MOSFET栅极电势升高到5V(水库阀门降到最低),阀门打开,电容中电势降低(水位升高),但由于水道容量较大,水位不会降低太多,不过多少也会降低一点(电势会升高),假设升高到2.7V。这时候感应放大器检测到IO线路的电势高于2.5V,识别出1读出。

以上讲述的只是从cell到内存IO线路的读写操作,至于CPU-IMC-内存的读写操作,不在本文讨论范围。

第二部分:时序介绍

时序及相关概念

以下我把时序分为两部分,只是为了下文介绍起来作为归类,非官方分类方法。

第一时序:CL-tRCD-tRP-tRAS-CR,就是我们常说的5个主要时序。

第二时序:(包含所有XMP时序)

在讲时序之前,我想先让大家明白一些概念。内存时钟信号是方波,DDR内存在时钟信号上升和下降时各进行一次数据传输,所以会有等效两倍传输率的关系。例如DDR3-1333的实际工作频率是666.7MHz,每秒传输数据666.7*2=1333百万次,即1333MT/s,也就是我们说的等效频率1333MHz,再由每条内存位宽是64bit,那么它的带宽就是:1333MT/s*64bit/8(8bit是一字节)=10667MB/s。所谓时序,就是内存的时钟周期数值,脉冲信号经过上升再下降,到下一次上升之前叫做一个时钟周期,随着内存频率提升,这个周期会变短。例如CL9的意思就是CL这个操作的时间是9个时钟周期。

另外还要搞清楚一些基本术语:

Cell:颗粒中的一个数据存储单元叫做一个Cell,由一个电容和一个N沟道MOSFET组成。Bank:8bit的内存颗粒,一个颗粒叫做一个bank,4bit的颗粒,正反两个颗粒合起来叫做一个bank。一根内存是64bit,如果是单面就是8个8bit颗粒,如果是双面,那就是16个4bit 的颗粒分别在两面,不算ECC颗粒。

Rank:内存PCB的一面所有颗粒叫做一个rank,目前在Unbuffered台式机内存上,通常一面是8个颗粒,所以单面内存就是1个rank,8个bank,双面内存就是2个rank,8个bank。Bank与rank的定义是SPD信息的一部分,在AIDA64中SPD一栏可以看到。

DIMM:指一条可传输64bit数据的内存PCB,也就是内存颗粒的载体,算上ECC芯片,一条DIMM PCB最多可以容纳18个芯片

第一时序

CAS Latency(CL):CAS即Column Address Strobe,列地址信号,它定义了在读取命令发出后到数据读出到IO接口的间隔时间。由于CAS在几乎所有的内存读取操作中都会生效(除非是读取到同一行地址中连续的数据,4bit颗粒直接读取间隔3个地址,8bit颗粒直接读取间隔7个地址,这时候CAS不生效),因此它是对内存读取性能影响最强的。如下图,蓝色的Read表示读取命令,绿色的方块表示数据读出IO,中间间隔的时间就是CL。

已知CL时钟周期值CAS,我们可以使用以下公式来计算实际延迟时间tCAS:

tCAS(ns)=(CAS*2000)/内存等效频率

例如,DDR3-1333 CL9内存实际CAS延迟时间=(9*2000)/1333=13.50 ns

或者反过来算,假如已知你的内存可以在7.5ns延迟下稳定工作,并且你想要DDR3-2000的频率,那么你可以把CL值设为8T(实际上8ns,大于7.5ns即可),如果你想要DDR3-1600的频率,那么你的CL值可以设到6T(实际7.5ns)。

这个公式对于所有用时钟周期表示延迟的内存时序都可以用。

说到这个公式,我想顺便说说大家对频率和时序的纠结问题。首先来回顾一下DDR一代到三代的一些典型的JEDEC规范,并按照上边那个公式算一下它的CL延迟时间:

DDR-400 3-3-3-8:(3*2000)/400=15 ns

DDR2-800 6-6-6-18:(6*2000)/800=15 ns

DDR3-1333 9-9-9-24:刚才算了是13.5 ns

再来看看每一代的超频内存的最佳表现(平民级,非世界纪录):

DDR1 Winbond BH-5 DDR-500 CL1.5:(1.5*2000)/500=6 ns

DDR2 Micron D9GMH DDR2-1400 CL4:(4*2000)/1400=5.71 ns

DDR3 PSC A3G-A DDR3-2133 CL6:(6*2000)/2133=5.63 ns

发现什么?不管是哪一代内存,随着频率提升,CL周期也同步提升,但是最后算出来的CL 延迟时间却差不多。那么到了DDR4,JEDEC规范频率去到DDR4-4266,如果按照差不多的延迟,那么按照13ns多一些来算,那么CL值将达到28T!如果按照我们的极限超频延迟来算,DDR4-4266下的延迟也将达到12T。所以到了下一代DDR4,两位数的时钟周期将不可

避免。

所以,我想说的是,不要再去想什么DDR3的频率,DDR2的时序,在频宽严重过剩,IMC 成为瓶颈的今天,它对性能没太多的提升。

DRAM RAS to CAS Delay(tRCD):RAS的含义与CAS类似,就是行(Row)地址信号。它定义的是在内存的一个rank(内存的一面)之中,行地址激活(Active)命令发出之后,内存对行地址的操作所需要的时间。每一个内存cell就是一个可存储数据的地址,每个地址都有对应的行号和列号,每一行包含1024个列地址,当某一行地址被激活后,多个CAS请求会被发送以进行读写操作。简单的说,已知行地址位置,在这一行中找到相应的列地址,就可以完成寻址,进行读写操作,从已知行地址到找到列地址过去的时间就是tRCD。当内存中某一行地址被激活时,我们称它为“open page”。在同一时刻,同一个rank可以打开8个行地址(8个bank,也就是8个颗粒各一个)。下图显示一个行地址激活命令发出,到寻找列地址并发出读取指令,中间间隔的时间就是tRCD。tRCD值由于是最关键的寻址时间,它对内存最大频率影响最大,一般想要上高频,在加电压和放宽CL值不奏效的时候,我们都要放宽这个延迟。

DRAM RAS Precharge Time(tRP):RAS预充电时间。它定义的是前一个行地址操作完成并在行地址关闭(page close)命令发出之后,准备对同一个bank中下一个行地址进行操作,tRP 就是下一个行地址激活信号发出前对其进行的预充电时间。由于在行地址关闭命令发出之前,一个rank中的多个行地址可能正在被读写,tRP对内存性能影响不如CL和tRCD。虽然tRP的影响会随着多个行地址激活与关闭信号频繁操作一个bank而加大,但是它的影响会被bank interleaving(bank交叉操作)和command scheduling(命令调配)所削弱。交叉读写会交替使用不同的bank进行读写,减少对一个bank的操作频率;命令调配则是由CPU 多线程访问不同的内存地址,同样是减少对一个bank的频繁操作次数。例如SNB CPU的内存控制器可以对读写操作命令进行有效地重新分配,以使得行地址激活命中率最大化(如果重复激活一个已经处于激活状态的行地址,那就是RAS激活命令未命中),所以tRP在SNB

平台对性能的影响不大,并且放宽它有可能可以帮助提升稳定性。下图显示的是一个即将被激活的行地址开始预充电,到它被激活间隔的时间,就是tRP。

DRAM RAS Active Time(tRAS):行地址激活的时间。它其实就是从一个行地址预充电之后,从激活到寻址再到读取完成所经过的整个时间,也就是tRCD+tCL的意思。这个操作并不会频繁发生,只有在空闲的内存新建数据的时候才会使用它。太紧的tRAS值,有可能会导致数据丢失或不完整,太宽的值则会影响内存性能,尤其是在内存使用量增加的时候。所以一般为了稳定性,我们设置tRAS≥tRTP+tRCD+CL即可(tRTP不是tRP,将在第二时序中介绍),尤其是PCB不好或者跑高频的时候,多几个周期比较稳妥。

DRAM Command Mode(Command Rate,CR):首命令延迟,也就是我们平时说的1T/2T模式。是指从选定bank之后到可以发出行地址激活命令所经过的时间。CR可能对性能的影响有比较大的变数:如果CPU所需要的数据都在内存的一个行地址上,就不需要进行重复多次的bank选择,CR的影响就很小;但是如果一个rank中同时多个bank要激活行地址,或者不同的rank中不同bank需要同时激活的时候,CR对性能的影响就会提升。但是随着内存频率的提升,CR=1T/2T的时间差越短,它的影响就会越来越小,这就是我们看到DDR1的时候1T/2T对性能影响挺大,但是到了DDR3影响就很小的其中一个原因。但是为了性能最大化,我们尽量把CR设为1T,但是如果bank数很多的时候,例如插满四条内存,就有32个bank,bank选择随机性增大,1T的首命令时间可能会不稳定。

所以,内存的基本读取操作的时序角度流程就是把上面那三张图合起来:预充电-激活行地址并寻找列地址-发送读取命令-读出数据,这四步操作中间的三个延迟就分别是tRP、tRCD 和CL。和我们常说的时序顺序刚好是反过来的。

第二时序——XMP

DRAM CAS Write Latency(tWCL):列地址写入延迟,也就是DRAM的最小写入操作时间,与CL刚好是读写对应关系,一般跟CL值设为同一个值就是可以稳定的。由于内存读取之前必须先写入,所以这个值可以说与CL一样重要。但是在BIOS里一般没得设置,可能是与CL 绑定了。

DRAM Row Cycle Time(tRC):行周期时间。定义了同一bank两次行激活命令所间隔的最小时间,或者说是一个bank中完成一次行操作周期(Row Cycle)的时间,即tRP+tRAS(预充电加上激活的整个过程),tRC设得太紧可能会直接点开不了机,一般只要能进系统再多加一两个周期都是可以稳定的。下图显示的就是tRC的时间。

DRAM Row Refresh Cycle Time(tRFC):行地址刷新周期,定义了一个bank中行地址刷新所需要的时间。重提一下刷新的含义,由于cell中电容的电荷在MOSFET关闭之后一段时间就会失去,为了维持数据,每隔很短一段时间就需要重新充电。这里多提一句,Intel平台和AMD平台对tRFC的含义不一样,AMD平台的tRFC是DRAM刷新延迟时间,单位是ns,通常有90/110/160/300几个值可以调整,也就是说它的tRFC时钟周期会随着频率的提升而提升;而Intel平台的单位则直接是时钟周期,相反地延迟时间会随着频率的提升而降低。容量大的bank行地址和cell会更多,刷新时间也更长,因此tRFC也要更高。另外,tRFC如果太快会导致数据出错,太慢则影响性能,但可以增加稳定性。

DRAM Refresh Interval(tREFI):内存刷新时间间隔,也就是内存的刷新命令生效前要经过的时间。刷新的时间间隔一般取决于内存颗粒的容量(density),容量越大,就越需要频繁刷新,tREFI值就要越低。另外tREFI的时间也会受到内存工作温度与内存电压(Vdimm)影响,因为温度越高电容漏电越快。一般在AMD主板的BIOS里,这个值只有3.9us和7.8us可选,而在SNB平台,则是按时钟周期算,例如DDR3-1333下默认值为5199T,换算过来就是2000/1333x5199=7800ns,也就是7.8us。一般DRAM颗粒的spec中都是规定工作温度大于85度时采用3.9us。

DRAM RAS to RAS Delay(tRRD):行地址间延迟,定义的是同一rank不同bank间两个连续激活命令的最短延迟,在DDR3时代一般最小是4T。它的作用和CR有点像,不过比CR更多的时候对性能有较大的影响,所以这个时序可尽量缩小。

DRAM Write Recovery Time(tWR):内存写入恢复时间,它定义了内存从写入命令发出(从开始写入算起)到下一次预充电间隔的时间,也就是tRP的前一个操作。如果这个时间设得太短,可能会导致前一次写入未完成就开始下一次预充电,进行寻址,那么前一次写入的数据就会不完整,造成丢数据的情况。这个周期也是第二时序中比较长的,DDR3-2000一般需要10-14个周期,甚至更高。

DRAM Read to Precharge Time(tRTP):与tWR类似,定义了同一rank上内存从读取命令发出到tRP之前的间隔时间,但是它在读取完成并且行地址关闭之后才会生效。单颗128MB 的内存颗粒可以在DDR3-2000下运行在4到6个时钟周期,如果bank容量增大时,这个时序有可能要放宽。

DRAM Four Active Window(tFAW):它定义了同一rank中允许同时发送大于四个行激活命令的间隔时间,因此最小值应该不小于tRRD的四倍。在DDR3上,tRRD的最小值是4T,因此tFAW的最小值就是16T。这个tFAW由于是在一个rank中大于四个bank同时激活之后才生效,因此在内存不是很繁忙的时候,它对性能的影响并不是很大。但是对一些频繁读写内存的操作(例如SuperPI 32M),tFAW对性能的影响可能会加大。由于现在内存用满的几率非常非常小,两根双面的内存更是有4个rank,配合上interleaving,一个rank中同时激活大于四个bank的几率应该不大,所以通常我们把它设为tRRD的四倍应该就不会出问题。

DRAM Write to Read Delay(tWTR):内存写-读延迟,它定义的是内存写入命令发出后到下一个读取命令之间的时间间隔,最小为4T,与tRTP类似,提升内存的频率或者容量提升时,这个值需要提高。

结语

看完以上内容,我们已经对时序有了个大致的了解,现在应该可以知道一些时序设置时要注意什么了。比如tFAW要设为tRRD的四倍,tRAS不能设太低等等。还是那句话,内存是辅助CPU超频的,时序设置只是为了放开内存更多的超频空间,时序本身对性能的影响很小,并且随着频率的提升,或者bank数的增加,这种影响可能会进一步减小。具体不同的内存颗粒也会有不同的设置情况,还请大家多关注本站的颗粒汇总以及最新内存颗粒测试报告!

RAM工作原理 实际的存储器结构由许许多多的基本存储单元排列成矩阵形式,并加上地址选择及读写控制等逻辑电路构成。当CPU要从存储器中读取数据时,就会选择存储器中某一地址,并将该地址上存储单元所存储的内容读走。 早期的DRAM的存储速度很慢,但随着内存技术的飞速发展,随后发展了一种称为快速页面模式(Fast Page Mode)的DRAM技术,称为FPDRAM。FPM内存的读周期从DRAM阵列中某一行的触发开始,然后移至内存地址所指位置的第一列并触发,该位置即包含所需要的数据。第一条信息需要被证实是否有效,然后还需要将数据存至系统。一旦发现第一条正确信息,该列即被变为非触发状态,并为下一个周期作好准备。这样就引入了“等待状态”,因为在该列为非触发状态时不会发生任何事情(CPU必须等待内存完成一个周期)。直到下一周期开始或下一条信息被请求时,数据输出缓冲区才被关闭。在快页模式中,当预测到所需下一条数据所放位置相邻时,就触发数据所在行的下一列。下一列的触发只有在内存中给定行上进行顺序读操作时才有良好的效果。 从50纳秒FPM内存中进行读操作,理想化的情形是一个以6-3-3-3形式安排的突发式周期(6个时钟周期用于读取第一个数据元素,接下来的每3个时钟周期用于后面3个数据元素)。第一个阶段包含用于读取触发行列所需要的额外时钟周期。一旦行列被触发后,内存就可以用每条数据3个时钟周期的速度传送数据了。 FP RAM虽然速度有所提高,但仍然跟不上新型高速的CPU。很快又出现了EDO RAM和SDRAM等新型高速的内存芯片。 介绍处理器高速缓存的有关知识 所谓高速缓存,通常指的是Level 2高速缓存,或外部高速缓存。L2高速缓存一直都属于速度极快而价格也相当昂贵的一类内存,称为SRAM(静态RAM),用来存放那些被CPU频繁使用的数据,以便使CPU不必依赖于速度较慢的DRAM。 最简单形式的SRAM采用的是异步设计,即CPU将地址发送给高速缓存,由缓存查找这个地址,然后返回数据。每次访问的开始都需要额外消耗一个时钟周期用于查找特征位。这样,异步高速缓存在66MHz总线上所能达到的最快响应时间为3-2-2-2,而通常只能达到4-2-2-2。同步高速缓存用来缓存传送来的地址,以便把按地址进行查找的过程分配到两个或更多个时钟周期上完成。SRAM在第一个时钟周期内将被要求的地址存放到一个寄存器中。在第二个时钟周期内,SRAM把数据传送给CPU。由于地址已被保存在一个寄存器中,所以接下来同步SRAM就可以在CPU读取前一次请求的数据同时接收下一个数据地址。这样,同步SRAM 可以不必另花时间来接收和译码来自芯片集的附加地址,就“喷出”连续的数据元素。优化的响应时间在66MHz总线上可以减小为2-1-1-1。 另一种类型的同步SRAM称为流水线突发式(pipelined burst)。流水线实际上是增加了一个用来缓存从内存地址读取的数据的输出级,以便能够快速地访问从内存中读取的连续数据,而省去查找内存阵列来获取下一数据元素过程中的延迟。流水线对于顺序访问模式,如高速缓存的行填充(linefill)最为高效。 什么是ECC内存 ECC是Error Correction Coding或Error Cheching and Correcting的缩写,它代表具有自动纠错功能的内存。目前的ECC存储器一般只能纠正一位二进制数的错误。 Intel公司的82430HX芯片组可支持ECC内存,所以采用82430HX芯片的主板一般都可以安装使用ECC 内存,由于ECC内存成本比较高,所以它主要应用在要求系统运算可靠性比较高的商业计算机

全面教你认识内存参数 内存热点 Jany 2010-4-28

内存这样小小的一个硬件,却是PC系统中最必不可少的重要部件之一。而对于入门用户来说,可能从内存的类型、工作频率、接口类型这些简单的参数的印象都可能很模糊的,而对更深入的各项内存时序小参数就更摸不着头脑了。而对于进阶玩家来说,内存的一些具体的细小参数设置则足以影响到整套系统的超频效果和最终性能表现。如果不想当菜鸟的话,虽然不一定要把各种参数规格一一背熟,但起码有一个基本的认识,等真正需要用到的时候,查起来也不会毫无概念。 内存种类 目前,桌面平台所采用的内存主要为DDR 1、DDR 2和DDR 3三种,其中DDR1内存已经基本上被淘汰,而DDR2和DDR3是目前的主流。 DDR1内存 第一代DDR内存 DDR SDRAM 是 Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM 的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。 DDR2内存 第二代DDR内存

DDR2 是 DDR SDRAM 内存的第二代产品。它在 DDR 内存技术的基础上加以改进,从而其传输速度更快(可达800MHZ ),耗电量更低,散热性能更优良。 DDR3内存 第三代DDR内存 DDR3相比起DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好更为省电;DDR2的4bit 预读升级为8bit预读。DDR3目前最高能够1600Mhz的速度,由于目前最为快速的DDR2内存速度已经提升到800Mhz/1066Mhz的速度,因而首批DDR3内存模组将会从1333Mhz的起跳。 三种类型DDR内存之间,从内存控制器到内存插槽都互不兼容。即使是一些在同时支持两种类型内存的Combo主板上,两种规格的内存也不能同时工作,只能使用其中一种内存。 内存SPD芯片 内存SPD芯片

[XXXX大学XXX学院XXX班] QQ等即时通讯软件 的应用研究 [ ] [学号: ] [摘要:即时通讯系统是当前一个热门应用软件,文中介绍了国内主流的即时通讯系统的设计与实现,通过对服务器及客户端架构的分析和设计、TCP/UDP协议等关键技术的应用, 说明了即时通讯软件的基本原理。]

QQ等即时通讯软件的应用研究 XXX大学XXX学院,XXX,学号:XXXXXXX 摘要:即时通讯系统是当前一个热门应用软件,文中介绍了国内主流的即时通讯系统的设计与实现,通过对服务器及客户端架构的分析和设计、TCP/UDP协议等关键技术的应用, 说明了即时通讯软件的基本原理。 关键词:即时通讯系统、TCP、UDP、服务器、客户端 正文: 一、IM技术概念 IM技术全称Instant Messaging,中文翻译“即时通讯”,它是一种使人们能在网上识别在线用户并与他们实时交换消息的技术,是电子邮件发明以来迅速崛起的在线通讯方式。IM的出现和互联网有着密不可分的关系,IM完全基于TCP/IP网络协议族实现,而TCP/IP协议族则是整个互联网得以实现的技术基础。最早出现即时通讯协议是IRC(Internet Relay Chat),但是可惜的是它仅能单纯的使用文字、符号的方式通过互联网进行交谈和沟通。随着互连网变得高度发达,即时通讯也变得远不止聊天这么简单,自1996年第一个IM产品ICQ发明后,IM的技术和功能也开始基本成型,语音、视频、文件共享、短信发送等高级信息交换功能都可以在IM工具上实现,于是功能强大的IM软件便足以搭建一个完整的通信交流平台。目前最具代表性的几款的IM通讯软件有MSN、Google Talk、Yahoo、Messenger 、腾讯QQ等。 二、即时通讯系统实现及关键技术 1、即时通讯软件服务器的实现 系统由Login Server负责接收IM Server的连接, 可以实现多个IM Server

D D R 系列系列内存内存内存详解及硬件详解及硬件 设计规范 By: Michael Oct 12, 2010 haolei@https://www.doczj.com/doc/df10185068.html,

目录 1.概述 (3) 2.DDR的基本原理 (3) 3.DDR SDRAM与SDRAM的不同 (5) 3.1差分时钟 (6) 3.2数据选取脉冲(DQS) (7) 3.3写入延迟 (9) 3.4突发长度与写入掩码 (10) 3.5延迟锁定回路(DLL) (10) 4.DDR-Ⅱ (12) 4.1DDR-Ⅱ内存结构 (13) 4.2DDR-Ⅱ的操作与时序设计 (15) 4.3DDR-Ⅱ封装技术 (19) 5.DDR-Ⅲ (21) 5.1DDR-Ⅲ技术概论 (21) 5.2DDR-Ⅲ内存的技术改进 (23) 6.内存模组 (26) 6.1内存模组的分类 (26) 6.2内存模组的技术分析 (28) 7.DDR 硬件设计规范 (34) 7.1电源设计 (34) 7.2时钟 (37) 7.3数据和DQS (38) 7.4地址和控制 (39) 7.5PCB布局注意事项 (40) 7.6PCB布线注意事项 (41) 7.7EMI问题 (42) 7.8测试方法 (42)

摘要: 本文介绍了DDR 系列SDRAM 的一些概念和难点,并分别对DDR-I/Ⅱ/Ⅲ的技术特点进行了论述,最后结合硬件设计提出一些参考设计规范。 关键字关键字::DDR, DDR, SDRAM SDRAM SDRAM, , , 内存模组内存模组内存模组, , , DQS DQS DQS, DLL, MRS, ODT , DLL, MRS, ODT , DLL, MRS, ODT Notes : Aug 30, 2010 – Added DDR III and the PCB layout specification - by Michael.Hao

即时通讯调研报告(一) 摘要:本文简述了技术通讯的发展现状,以及发展趋势 1概述 1.1 IM技术概念 IM技术全称Instant Messaging,中文翻译“即时通讯”,它是一种使人们能在网上识别在线用户并与他们实时交换消息的技术,是电子邮件发明以来迅速崛起的在线通讯方式。IM 的出现和互联网有着密不可分的关系,IM完全基于TCP/IP网络协议族实现,而TCP/IP协议族则是整个互联网得以实现的技术基础。最早出现即时通讯协议是IRC(Internet Relay Chat),但是可惜的是它仅能单纯的使用文字、符号的方式通过互联网进行交谈和沟通。随着互连网变得高度发达,即时通讯也变得远不止聊天这么简单,自1996年第一个IM产品ICQ发明后,IM的技术和功能也开始基本成型,语音、视频、文件共享、短信发送等高级信息交换功能都可以在IM工具上实现,于是功能强大的IM软件便足以搭建一个完整的通信交流平台。目前最具代表性的几款的IM通讯软件有MSN、Google Talk、Yahoo Messenger、腾讯QQ等。 1.2 IM技术原理和工作方式 典型的IM工作方式如下:登陆IM通讯中心(IM通讯服务器),获取一个自建立的历史的交流对象列表(好友列表),然后自身标志为在线状态,当好友列表中的某人在任何时候登录上线并试图通过你的计算机联系你时,IM系统会发一个消息提醒你,然后你能与他建立一个聊天会话通道进行各种消息如键入文字、通过语音等的交流。 从技术上来说,IM的基本技术原理如下: 1.IM服务器 2.登陆或注销 3.用户A通过列表找到B,用户B获得的消息并与之交谈 4.通过IM服务器指引建立与B单独的通讯通道 第一步,用户A输入自己的用户名和密码登录IM服务器,服务器通过读取用户数据库来验证用户身份,如果验证通过,登记用户A的IP地址、IM客户端软件的版本号及使用

内存的物理结构和工作原理 内存也叫主存,是PC系统存放数据与指令的半导体存储器单元,也叫主存储器(Main Memory),通常分为只读存储器(ROM-Read Only Memory)、随机存储器(RAM-Red Access Memory)和高速缓存存储器(Cache)。我们平常所指的内存条其实就是RAM,其主要的作用是存放各种输入、输出数据和中间计算结果,以及与外部存储器交换信息时做缓冲之用。 下面是结构: 1、PCB板 内存条的PCB板多数都是绿色的。如今的电路板设计都很精密,所以都采用了多层设计,例如4层或6层等,所以PCB板实际上是分层的,其内部也有金属的布线。理论上6层PCB板比4层PCB板的电气性能要好,性能也较稳定,所以名牌内存多采用6层PCB板制造。因为PCB板制造严密,所以从肉眼上较难分辩PCB板是4层或6层,只能借助一些印在PCB板上的符号或标识来断定。 2、金手指 黄色的接触点是内存与主板内存槽接触的部分,数据就是靠它们来传输的,通常称为金手指。金手指是铜质导线,使用时间长就可能有氧化的现象,会影响内存的正常工作,易发生无法开机的故障,所以可以隔一年左右时间用橡皮擦清理一下金手指上的氧化物。 3、内存芯片 内存的芯片就是内存的灵魂所在,内存的性能、速度、容量都是由内存芯片组成的。 4、内存颗粒空位 5、电容 PCB板上必不可少的电子元件就是电容和电阻了,这是为了提高电气性能的需要。电容采用贴片式电容,因为内存条的体积较小,不可能使用直立式电容,但这种贴片式电容性能一点不差,它为提高内存条的稳定性起了很大作用。 6、电阻 电阻也是采用贴片式设计,一般好的内存条电阻的分布规划也很整齐合理。7、内存固定卡缺口:内存插到主板上后,主板上的内存插槽会有两个夹子牢固的扣住内存,这个缺口便是用于固定内存用的。 8、内存脚缺口 内存的脚上的缺口一是用来防止内存插反的(只有一侧有),二是用来区分不同的内存,以前的SDRAM内存条是有两个缺口的,而DDR则只有一个缺口,不能混插。 9、SPD SPD是一个八脚的小芯片,它实际上是一个EEPROM可擦写存贮器,这的容量有256字节,可以写入一点信息,这信息中就可以包括内存的标准工作状态、速度、响应时间等,以协调计算机系统更好的工作。从PC100时代开始,PC100规准中就规定符合PC100标准的内存条必须安装SPD,而且主板也可

即时通讯四种协议简述 IM(Instant Messaging)正在被广泛地采用,特别是在公司与它们的客户互动联接方案上。为了解决即时通讯的标准问题,IETF成立了专门的工作小组,研究和开发与IM相关的协议。 目前IM有四种协议:即时信息和空间协议(IMPP)、空间和即时信息协议(PRIM)、针对即时通讯和空间平衡扩充的进程开始协议SIP(SIMPLE)以及XMPP。PRIM与XMPP、SIMPLE类似,但已经不再使用了。 IMPP主要定义必要的协议和数据格式,用来构建一个具有空间接收、发布能力的即时信息系统。到目前为止,这个组织已经出版了三个草案RFC,但主要的有两个:一个是针对站点空间和即时通讯模型的(RFC 2778);另一个是针对即时通讯/空间协议需求条件的(RFC2779)。RFC2778是一个资料性质的草案,定义了所有presence和IM服务的原理。RFC2779定义了IMPP的最小需求条件。另外,这个草案还就presence服务定义了一些条款,如运行的命令、信息的格式,以及presence服务器如何把presence的状态变化通知给客户。 SIMPLE是目前为止制定的较为完善的一个。SIMPLE和XMPP两个协议,都符合RFC2778和RFC2779 。SIMPLE计划利用SIP来发送presence信息。SIP是IETF中为终端制定的协议。SIP一般考虑用在建立语音通话中,一旦连接以后,依靠如实时协议(RTP)来进行实际上的语音发送。???但SIP不仅仅能被用在语音中,也可以用于视频。SIMPLE 被定义为建立一个IM进程的方法。SIMPLE在2002年夏季得到额外的信任,目前,微软和IBM 都致力于在它们的即时通讯系统中实现这个协议。 SIMPLE小组致力于进程模式的操作,这将提升运行效率,使基于SIP的机制能够进行会议和三方

详解内存工作原理及发展历程 RAM(Random Access Memory)随机存取存储器对于系统性能的影响是每个PC 用户都非常清楚的,所以很多朋友趁着现在的内存价格很低纷纷扩容了内存,希望借此来得到更高的性能。不过现在市场是多种内存类型并存的,SDRAM、DDR SDRAM、RDRAM等等,如果你使用的还是非常古老的系统,可能还需要EDO DRAM、FP DRAM(块页)等现在不是很常见的内存。 虽然RAM的类型非常的多,但是这些内存在实现的机理方面还是具有很多相同的地方,所以本文的将会分为几个部分进行介绍,第一部分主要介绍SRAM 和异步DRAM(asynchronous DRAM),在以后的章节中会对于实现机理更加复杂的FP、EDO和SDRAM进行介绍,当然还会包括RDRAM和SGRAM等等。对于其中同你的观点相悖的地方,欢迎大家一起进行技术方面的探讨。 存储原理: 为了便于不同层次的读者都能基本的理解本文,所以我先来介绍一下很多用户都知道的东西。RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用有格子的书架存放书籍一样,不但要放进去还要能够在需要的时候准确的调用出来,虽然都是书但是每本书是不同的。对于RAM等存储器来说也是一样的,虽然存储的都是代表0和1的代码,但是不同的组合就是不同的数据。 让我们重新回到书和书架上来,如果有一个书架上有10行和10列格子(每行和每列都有0-9的编号),有100本书要存放在里面,那么我们使用一个行的编号+一个列的编号就能确定某一本书的位置。如果已知这本书的编号87,

XMPP协议即时通讯(Openfire服务器版) 一、什么是XMPP XMPP(Extensible Messageing and Presence Protocol:可扩展消息与存在协议)是目前主流的IM(IM:instant messaging,即时消息)协议之一。 XMPP是一种基于标准通用标记语言的子集XML的协议,它继承了在XML 环境中灵活的发展性。 XMPP中定义了三个角色,客户端,服务器,网关。通信能够在这三者的任意两个之间双向发生。 服务器同时承担了客户端信息记录,连接管理和信息的路由功能。网关承担着与异构即时通信系统的互联互通,异构系统可以包括SMS(短信),MSN,ICQ 等。 XMPP即时通信协议,采用C/S体系结构。基本的网络形式是客户端连接到服务器,然后由服务器去连接到另一个客户端进行两个客户端之间的通信。 而他们传输的是XML流。 XMPP工作原理说明: 所有从一个客户端到另一个客户端的消息和数据都要通过服务器。 1、客户端连接服务器 2、服务器利用本地目录系统的证书对其认证 3、客户端制定目标地址,让服务器告知目标状态 4、服务器查找,连接并进行相互认证 5、客户端间进行交互 二、搭建服务器(Openfire) 通过上述的了解,我们知道要想进行通信,我们必须要有一个服务器。服务器端采用Openfire作为服务器。 允许多个客户端同时登录并且并发的连接到一个服务器上。 服务器对每个客户端的连接进行认证,对认证通过的客户端创建会话,客户端与服务器端之间的通信就在该会话的上下文中进行。 首先安装Openfire

点击继续

点击安装 安装成功后再偏好设置中就会有Openfire的图标。点击Openfire的图标

DRAM内存原理 1. 内存基础 不管你信不信,RDRAM (Rambus、DDR SDRAM甚至是EDO RAM它们在本质上讲是一样的。RDRAM、DDR RAM、SDRAM、EDO RAM都属于 DRAM(Dynamic RAM,即动态内存。所有的DRAM基本单位都是由一个晶体管和一个电容器组成。请看下图: 上图只是DRAM一个基本单位的结构示意图:电容器的状态决定了这个DRAM 单位的逻辑状态是1还是0,但是电容的被利用的这个特性也是它的缺点。一个电容器可以存储一定量的电子或者是电荷。一个充电的电容器在数字电子中被认为是逻辑上的1,而“空”的电容器则是0。电容器不能持久的保持储存的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。电容器可以由电流来充电——当然这个电流是有一定限制的,否则会把电容击穿。同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容这个时间很短,只有大约0.2-0.18微秒,但是这个期间内存是不能执行存取操作的。

DRAM制造商的一些资料中显示,内存至少要每64ms刷新一次,这也就意味着内存有1%的时间要用来刷新。内存的自动刷新对于内存厂商来说不是一个难题,而关键在于当对内存单元进行读取操作时保持内存的内容不变——所以DRAM单元每次读取操作之后都要进行刷新:执行一次回写操作,因为读取操作也会破坏内存中的电荷,也就是说对于内存中存储的数据是具有破坏性的。所以内存不但要每64ms 刷新一次,每次读操作之后也要刷新一次。这样就增加了存取操作的周期,当然潜伏期也就越长。 SRAM,静态(StaticRAM不存在刷新的问题,一个SRAM基本单元包括4个晶体管和2个电阻。它不是通过利用电容充放电的特性来存储数据,而是利用设置晶体管的状态来决定逻辑状态——同CPU中的逻辑状态一样。读取操作对于SRAM不是破坏性的,所以SRAM不存在刷新的问题。 SRAM不但可以运行在比DRAM高的时钟频率上,而且潜伏期比DRAM短的多。SRAM仅仅需要2到3个时钟周期就能从CPU缓存调入需要的数据,而DRAM 却需要3到9个时钟周期(这里我们忽略了信号在CPU、芯片组和内存控制电路之间传输的时间。前面也提到了,SRAM需要的晶体管的数目是DRAM 的4倍,也就是说成本比DRAM高至少是4倍,在目前的售价SRAM每M价格大约是DRAM的8倍,是RAMBUS内存的2到3倍。不过它的极短的潜伏期和高速的时钟频率却的确可以带来更高的带宽。 结构和功能(SDRAM 内存最基本的单位是内存“细胞”——也就是我们前面展示给大家DRAM 基本单元示意图所示的部分,下面我们对这个部分通称为DRAM基本单元。每个DRAM 基本单元代表一个“位”——Bit(也就是一个比特,并且有一个由列地址和行地址定义的唯一地址。8个比特组成一个字节,它可代表256种组合(即2的八次幂,字节是内存中最小的可寻址单元。DRAM基本单元不能被单独寻址——否则现在的内存将会更加复杂,而且也没有必要。很多DRAM基本单元连接到同一个列线(Row line和同一个行线(Column line,组成了一个矩阵结构,这个矩阵结构就是一个Bank。大部

Flash 存储芯片工作原理: Flash 芯片并不是像光盘那样把信息刻上去的。为了更加清楚地说明,我首先让你知道计算机的信息是怎样储存的。计算机用的是二进制,也就是0与1。在二进制中,0与1可以组成任何数。而电脑的器件都有两种状态,可以表示0与1。比如三极管的断电与通电,磁性物质的已被磁化与未被磁化,物质平面的凹与击,都可以表示0与1。硬盘就是采用磁性物质记录信息的,磁盘上的磁性物质被磁化了就表示1,未被磁化就表示0,因为磁性在断电后不会丧失,所以磁盘断电后依然能保存数据。而内存的储存形式则不同,内存不是用磁性物质,而是用RAM 芯片。现在请你在一张纸上画一个“田”,就是画一个正方形再平均分成四份,这个“田”字就是一个内存,这样,“田”里面的四个空格就是内存的储存空间了,这个储存空间极小极小,只能储存电子。。好,内存现在开始工作。内存通电后,如果我要把“1010”这个信息保存在内存(现在画的“田”字)中,那么电子就会进入内存的储存空间里。“田”字的第一个空格你画一点东西表示电子,第二个空格不用画东西,第三个空格又画东西表示电子,第四个格不画东西。这样,“田”的第一格有电子,表示1,第二格没有,表示0,第三格有电子,表示1,第四格没有,表示0,内存就是这样把“1010”这个数据保存好了。电子是运动没有规律的物质,必须有一个电源才能规则地运动,内存通电时它很安守地在内存的储存空间里,一旦内存断电,电子失去了电源,就会露出它乱杂无章的本分,逃离出内存的空间去,所以,内存断电就不能保存数据了。再看看U 盘,U 盘里的储存芯片是Flash 芯片,它与RAM 芯片的工作原理相似但不同。现在你在纸上再画一个“田”字,这次要在四个空格中各画一个顶格的圆圈,这个圆圈不是表示电子,而是表示一种物质。好,Flash 芯片工作通电了,这次也 是保存“1010”这个数据。电子进入了“田”的第一个空格,也就是芯片的储存空间。电子把里面的物质改变了性质,为了表示这个物质改变了性质,你可以把“田”内的第一个圆圈涂上颜色。由于数据“1010”的第二位数是0,所以Flash 芯片的第二个空间没有电子,自然里面那个物质就不会改变了。第三位数是1,所以“田”的第三个空格通电,第四个不通电。现在你画的“田”字,第一个空格的物质涂上了颜

一文详解SRAM特点和原理 基本简介SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM (Dynamic Random Access Memory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,且功耗较大。所以在主板上SRAM存储器要占用一部分面积。 主要规格一种是置于CPU与主存间的高速缓存,它有两种规格:一种是固定在主板上的高速缓存(Cache Memory );另一种是插在卡槽上的COAST(Cache On A STIck)扩充用的高速缓存,另外在CMOS芯片1468l8的电路里,它的内部也有较小容量的128字节SRAM,存储我们所设置的配置数据。还有为了加速CPU内部数据的传送,自80486CPU 起,在CPU的内部也设计有高速缓存,故在PenTIum CPU就有所谓的L1 Cache(一级高速缓存)和L2Cache(二级高速缓存)的名词,一般L1 Cache是内建在CPU的内部,L2 Cache是设计在CPU的外部,但是PenTIum Pro把L1和L2 Cache同时设计在CPU的内部,故PenTIum Pro的体积较大。最新的Pentium II又把L2 Cache移至CPU内核之外的黑盒子里。SRAM显然速度快,不需要刷新的操作,但是也有另外的缺点,就是价格高,体积大,所以在主板上还不能作为用量较大的主存。 基本特点现将它的特点归纳如下: ◎优点,速度快,不必配合内存刷新电路,可提高整体的工作效率。 ◎缺点,集成度低,功耗较大,相同的容量体积较大,而且价格较高,少量用于关键性系统以提高效率。 ◎SRAM使用的系统: ○CPU与主存之间的高速缓存。 ○CPU内部的L1/L2或外部的L2高速缓存。 ○CPU外部扩充用的COAST高速缓存。 ○CMOS 146818芯片(RTCMOS SRAM)。

P2P技术 技术原理 什么是对等网络(P2P)技术?P2P技术属于覆盖层网络(Overlay Network)的范畴,是相对于客户机/服务器(C/S)模式来说的一种网络信息交换方 式。在C/S模式中,数据的分发采用专门的服务器,多个客户端都从此服务器获取数据。这种模式的优点是:数据的一致性容易控制,系统也容易管理。但是此种 模式的缺点是:因为服务器的个数只有一个(即便有多个也非常有限),系统容易出现单一失效点;单一服务器面对众多的客户端,由于CPU能力、内存大小、网 络带宽的限制,可同时服务的客户端非常有限,可扩展性差。P2P技术正是为了解决这些问题而提出来的一种对等网络结构。在P2P网络中,每个节点既可以从 其他节点得到服务,也可以向其他节点提供服务。这样,庞大的终端资源被利用起来,一举解决了C/S模式中的两个弊端。 对等网络的基本结构 (1)集中式对等网络(Napster、QQ) 集中式对等网络基于中 央目录服务器,为网络中各节目提供目录查询服务,传输内容无需再经过中央服务器。这种网络,结构比较简单,中央服务器的负担大大降低。但由于仍存在中央节 点,容易形成传输瓶颈,扩展性也比较差,不适合大型网络。但由于目录集中管理,对于小型网络的管理和控制上倒是一种可选择方案。 (2)无结构分布式网络(Gnutella) 无结构分布式网络与集中式的最显著区别在于,它没有中央服务器,所有结点通过与相邻节点间的通信,接入整个网络。在无结构的网络中,节点采用一种查询包的 机制来搜索需要的资源。具体的方式为,某节点将包含查询内容的查询包发送到与之相邻的节点,该查询包以扩散的方式在网络中蔓延,由于这样的方式如果不加节 制,会造成消息泛滥,因此一般会设置一个适当的生存时间(TTL),在查询的过程中递减,当TTL值为0时,将不再继续发送。 这种无结构的方式,组织方式比较松散,节点的加入与离开比较自由,当查询热门内容时,很容易就能找到,但如果需求的内容比较冷门,较小的TTL不容易找 到,而较大的TTL值又容易引起较大的查询流量,尤其当网络范围扩展到一定规模时,即使限制的TTL值较小,仍然会引起流量的剧增。但当网络中存在一些拥 有丰富资源的所谓的类服务器节点时,可显著提高查询的效率。 (3)结构化分布式网络(第三代P2P Pastry、Tapestry、Chord、CAN) 结构化分布式网络,是近几年基于分布式哈希表(Distributed

硬盘内部硬件结构和工作原理详解 一般硬盘正面贴有产品标签,主要包括厂家信息和产品信息,如商标、型号、序列号、生产日期、容量、参数和主从设置方法等。这些信息是正确使用硬盘的基本依据,下面将逐步介绍它们的含义。 硬盘主要由盘体、控制电路板和接口部件等组成,如图1-1所示。盘体是一个密封的腔体。硬盘的内部结构通常是指盘体的内部结构;控制电路板上主要有硬盘BIOS、硬盘缓存(即CACHE)和主控制芯片等单元,如图1-2所示;硬盘接口包括电源插座、数据接口和主、从跳线,如图1-3所示。 图1-1 硬盘的外观 图1-2 控制电路板 图1-3 硬盘接口 电源插座连接电源,为硬盘工作提供电力保证。数据接口是硬盘与主板、内存之间进行数据交换的通道,使用一根40针40线(早期)或40针80线(当前)的IDE接口电缆进行连接。新增加的40线是信号屏蔽线,用于屏蔽高速高频数据传输过程中的串扰。中间的主、从盘跳线插座,用以设置主、从硬盘,即设置硬盘驱动器的访问顺序。其设置方法一般标注在盘体外的标签上,也有一些标注在接口处,早期的硬盘还可能印在电路板上。 此外,在硬盘表面有一个透气孔(见图1-1),它的作用是使硬盘内部气压与外部大气压保持一致。由于盘体是密封的,所以,这个透气孔不直接和内部相通,而是经由一个高效过滤器和盘体相通,用以保证盘体内部的洁净无尘,使用中注意不要将它盖住。

1.2 硬盘的内部结构 硬盘的内部结构通常专指盘体的内部结构。盘体是一个密封的腔体,里面密封着磁头、盘片(磁片、碟片)等部件,如图1-4所示。 图1-4 硬盘内部结构 硬盘的盘片是硬质磁性合金盘片,片厚一般在0.5mm左右,直径主要有1.8in (1in=25.4mm)、2.5in、3.5in和5.25in 4种,其中2.5in和3.5in盘片应用最广。盘片的转速与盘片大小有关,考虑到惯性及盘片的稳定性,盘片越大转速越低。一般来讲,2.5in硬盘的转速在5 400 r/min~7 200 r/ min之间;3.5in 硬盘的转速在4 500 r/min~5 400 r/min之间;而5.25in硬盘转速则在3 600 r/min~4 500 r/min之间。随着技术的进步,现在2.5in硬盘的转速最高已达15 000 r/min,3.5in硬盘的转速最高已达12 000 r/min。 有的硬盘只装一张盘片,有的硬盘则有多张盘片。这些盘片安装在主轴电机的转轴上,在主轴电机的带动下高速旋转。每张盘片的容量称为单碟容量,而硬盘的容量就是所有盘片容量的总和。早期硬盘由于单碟容量低,所以,盘片较多,有的甚至多达10余片,现代硬盘的盘片一般只有少数几片。一块硬盘内的所有盘片都是完全一样的,不然控制部分就太复杂了。一个牌子的一个系列一般都用同一种盘片,使用不同数量的盘片,就出现了一个系列不同容量的硬盘产品。 盘体的完整构造如图1-5所示。

微信技术原理及应用前景 微信是腾讯公司于2011年1月21日推出的一个为智能终端提供即时通讯服务的免费应用程序,微信支持跨通信运营商、跨操作系统平台通过网络快速发送免费(需消耗少量网络流量)语音短信、视频、图片和文字,同时,也可以使用通过共享流媒体内容的资料和基于位置的社交插件“摇一摇”、“漂流瓶”、“朋友圈”、”公众平台“、”语音记事本“等服务插件。 微信提供公众平台、朋友圈、消息推送等功能,用户可以通过“摇一摇”、“搜索号码”、“附近的人”、扫二维码方式添加好友和关注公众平台,同时微信将内容分享给好友以及将用户看到的精彩内容分享到微信朋友圈。截至2013年11月注册用户量已经突破6亿,是亚洲地区最大用户群体的移动即时通讯软件。 微信技术是一种基于即时通信技术原理的一种,即时通信是一种基于网络的通信技术, 涉及到IP/TCP/UDP/Sockets、P2P、C/S、多媒体音视频编解码/传送、Web Service等多种技术手段。无论即时通信系统的功能如何复杂,它们大都基于相同的技术原理,主要包括客户/服务器(C/S)通信模式和对等通信(P2P)模式。 而在微信技术原理中,主要是运用对等通信模式,而且其是非对称中心结构。每一个客户(Peer)都是平等的参与者,承担服务使用者和服务提供者两个角色。客户之间进行直接通信,同时由于没有中央节点的集中控制,系统的伸缩性较强,也能避免单点故障,提高系统的容错性能。但由于P2P网络的分散性、自治性、动态性等特点,造成了某些情况下客户的访问结果是不可预见的。例如,一个请求可能得不到任何应答消息的反馈。当前使用的IM系统大都组合使用了C/S和P2P模式。在登录IM进行身份认证阶段是工作在C/S方式,随后如果客户端之间可以直接通信则使用P2P方式工作,否则以C/S方式通过IM服务器通信,如下图所示: 使用微信可以通过网络快速发送语音短信、视频等。其原理与腾讯QQ类似。当登陆微信时,不管是TCP还是UDP协议,微信都会有一个TCP来保持其在

聊天室介绍: ---- 聊天室基本原理是,抛开OGI和WWW服务器,根据HTML规范,接收到浏览器的请求以后,模仿WWW服务器的响应,将聊天内容发回浏览器。在浏览器看来就像浏览一个巨大的页面一样始终处于页面联接状态,这就是一个专门的聊天服务器,一个简化了的WWW服务器。 ----这样相比CGI方式来说,聊天室的优点就很明显: 不需要专门的WWW服务器,在聊天服务器里完成必要的工作,避开耗时的CGI 过程。 如果使用单进程服务器,就不需要每次产生新进程。 数据交换完全在内存中进行,不用读写文件。 不需要定时刷新,减少屏幕的闪烁,减少对服务器的请求次数。 ----下面我们来看看具体实现流程。 一、聊天服务器实现流程 ----用户数据输入都是通过URL传送,下面是几个URL实例,结合后面客户端流程,可以更好地理解系统结构。 ----这是一个用户名密码均为…aaa''''的聊天用户登录系统,说了一句话“hello”,然后退出所产生的一系列请求,其中密码用系统函数crypt加密过: 二、客户端具体登录过程 ---- 我们先看看聊天界面: ----聊天界面由三个frame组成,其中chat帧是聊天内容显示部分,talk帧是用户输入部分,包括内容输入、动作、过滤以及管理功能都在这一帧输入,names是在线名单显示部分,这一部分是定时刷新的。 ---- 让我们从浏览器的角度来看看进入聊天室的过程。 ---- 1.首先浏览器请求页面: ---- 此时产生了一个连接到服务器聊天端口的联接,并发送了一行数据: ----2.服务器生成一个session ID,验证密码以后,发回: ----然后服务器关闭联接。 ----3.浏览器收到以上文件后,将会依次打开三个联接(其中的$sid和$encrypt_pass是变量):----这三个联接中的第一个联接chat在整个聊天过程中都是保持联接的,这样从浏览器角度来看,就是一个始终下载不完的大页面,显示效果上就是聊天内容不是靠刷新来更新,而是不断地向上滚动。通过察看代码可以看到,然后就是不断增加的聊天内容. ---- 另外两个联接在页面发送完毕以后,就关闭了。 ---- 这样一次登录聊天室实际上有四次联接,但登录完成以后,只有chat帧的是保持联接的,用于接收来自服务器的聊天信息,这是聊天室的关键所在。 ----在服务器端储存了所有参加聊天的客户的chat,当有人发言时,服务器就向所有chat发送聊天内容。 ---- Talk与names帧的html实际上和普通的form是一样的。 ---- 4.在用户登录以后,服务器端保存了一张包括用户信息的表格: ---- 在perl实现中,我们使用哈希结构储存信息,以session ID 作为key索引。这样的存储结构便于存取数据,回收空间。每个客户信息是一个数组: [name,passwd,privilige,filter,login_time,color]:储存chat帧联接name:用户名passwd:密码privilige:权限filter:某个用户的过滤列表的引用(reference)login_time:记录登录时间,以便以后清除一些超时联接color:用户聊天颜色 ----以上用户数据大部分是在login阶段,用户通过密码验证以后填入的。只有chat要等到chat帧显示以后才得到。如果超过一定时间,还是没有填入,说明浏览器取得主框架以后连接中断了,这时候就需要删除该用户数据。

内存工作原理及发展历程 RAM(Random Access Memory)随机存取存储器对于系统性能的影响是每个PC用户都非常清楚的,所以很多朋友趁着现在的内存价格很低纷纷扩容了内存,希望借此来得到更高的性能。不过现在市场是多种内存类型并存的,SDRAM、DDR SDRAM、RDRAM等等,如果你使用的还是非常古老的系统,可能还需要EDO DRAM、FP DRAM(块页)等现在不是很常见的内存。 虽然RAM的类型非常的多,但是这些内存在实现的机理方面还是具有很多相同的地方,所以本文的将会分为几个部分进行介绍,第一部分主要介绍SRAM和异步DRAM (asynchronous DRAM),在以后的章节中会对于实现机理更加复杂的FP、EDO和SDRAM 进行介绍,当然还会包括RDRAM和SGRAM等等。对于其中同你的观点相悖的地方,欢迎大家一起进行技术方面的探讨。 存储原理: 为了便于不同层次的读者都能基本的理解本文,所以我先来介绍一下很多用户都知道的东西。RAM主要的作用就是存储代码和数据供CPU在需要的时候调用。但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用有格子的书架存放书籍一样,不但要放进去还要能够在需要的时候准确的调用出来,虽然都是书但是每本书是不同的。对于RAM等存储器来说也是一样的,虽然存储的都是代表0和1的代码,但是不同的组合就是不同的数据。 让我们重新回到书和书架上来,如果有一个书架上有10行和10列格子(每行和每列都有0-9的编号),有100本书要存放在里面,那么我们使用一个行的编号+一个列的编号就能确定某一本书的位置。如果已知这本书的编号87,那么我们首先锁定第8行,然后找到第7列就能准确的找到这本书了。在RAM存储器中也是利用了相似的原理。 现在让我们回到RAM存储器上,对于RAM存储器而言数据总线是用来传入数据或者传出数据的。因为存储器中的存储空间是如果前面提到的存放图书的书架一样通过一定的规则定义的,所以我们可以通过这个规则来把数据存放到存储器上相应的位置,而进行这种定位的工作就要依靠地址总线来实现了。对于CPU来说,RAM就象是一条长长的有很多空格的细线,每个空格都有一个唯一的地址与之相对应。如果CPU想要从RAM中调用数据,它首先需要给地址总线发送地址数据定位要存取的数据,然后等待若干个时钟周期之后,数据总线就会把数据传输给CPU。下面的示意图可以帮助你很好的理解这个过程。

图1-1 硬盘的外观 图1-2 控制电路板 图1-3 硬盘接口 电源插座连接电源,为硬盘工作提供电力保证。数据接口是硬盘与主板、内存之间进行数据交换的通道,使用一根40针40线(早期)或40针80线(当前)的IDE 接口电缆进行连接。新增加的40线是信号屏蔽线,用于屏蔽高速高频数据传输过程中的串扰。中间的主、从盘跳线插座,用以设置主、从硬盘,即设置硬盘驱动器的访问顺序。其设置方法一般标注在盘体外的标签上,也有一些标注在接口处,早期的硬盘还可能印在电路板上。 此外,在硬盘表面有一个透气孔(见图1-1),它的作用是使硬盘内部气压与外部大气压保持一致。由于盘体是密封的,所以,这个透气孔不直接和内部相通,而是经由一个高效过滤器和盘体相通,用以保证盘体内部的洁净无尘,使用中注意不要将它盖住。 1.2 硬盘的内部结构 硬盘的内部结构通常专指盘体的内部结构。盘体是一个密封的腔体,里面密封着磁头、盘片(磁片、碟片)等部件,如图1-4所示。

图1-4 硬盘内部结构 硬盘的盘片是硬质磁性合金盘片,片厚一般在0.5mm左右,直径主要有1.8in (1in=25.4mm)、2.5in、3.5in和5.25in 4种,其中2.5in和3.5in盘片应用最广。盘片的转速与盘片大小有关,考虑到惯性及盘片的稳定性,盘片越大转速越低。一般来讲,2.5in硬盘的转速在5 400 r/min~7 200 r/ min之间;3.5in硬盘的转速在4 500 r/min~5 400 r/min之间;而5.25in硬盘转速则在3 600 r/min~4 500 r/min之间。随着技术的进步,现在2.5in硬盘的转速最高已达15 000 r/min,3.5in硬盘的转速最高已达12 000 r/min。 有的硬盘只装一张盘片,有的硬盘则有多张盘片。这些盘片安装在主轴电机的转轴上,在主轴电机的带动下高速旋转。每张盘片的容量称为单碟容量,而硬盘的容量就是所有盘片容量的总和。早期硬盘由于单碟容量低,所以,盘片较多,有的甚至多达10余片,现代硬盘的盘片一般只有少数几片。一块硬盘内的所有盘片都是完全一样的,不然控制部分就太复杂了。一个牌子的一个系列一般都用同一种盘片,使用不同数量的盘片,就出现了一个系列不同容量的硬盘产品。 盘体的完整构造如图1-5所示。

工作流定义 业务过程(Business process)是指为了实现某一业务、战略目标而组合在一起的一组过程或活动。而工作流是业务过程的自动化处理,在业务流程处理过程中,根据一组定义好的处理规则,可以把相关的信息、文档、任务或业务从一个参与者传递到另一个活动的参与者。 简单地说,工作流就是一系列相互衔接、自动进行的业务活动或任务。 在现代化的组织管理活动中,组织机构与流程运作构成了现代企业内部的垂直管理线路和水平管理线路。其中垂直管理线路明确了组织成员的分工(企业的战略目标、部门的职能和岗位责任等),水平管理线路明确了组织成员的协作,这种既分工又合作的方式,就构成了企业横向与纵向结合的经营与管理模式。 通过现代化的工作流软件技术手段,将这些管理线路规范化、标准化和流程自动化,从而有效地提高业务运作效率,降低成本,为实现企业的战略目标提供保障。 返回 https://www.doczj.com/doc/df10185068.html,工作流管理系统概述 https://www.doczj.com/doc/df10185068.html,工作流管理系统(https://www.doczj.com/doc/df10185068.html, WorkFlow)参照工作流管理联盟(WfMC)标准设计,以业务管理为核心(BPM),以工作流平台技术为依托,可以帮助企业快速构建高效、柔性的业务流程管理系统; https://www.doczj.com/doc/df10185068.html,工作流系统具有独立的框架级工作流引擎服务器,由UCML直接生成C#源码,客户可以方便扩展。 https://www.doczj.com/doc/df10185068.html,工作流管理系统不但涵盖了流程开发、发布、管理配置、运行、监控的整个过程,还提供流程KPI接口,方便对流程五要素指标(时间、质量、数量、风险、成本)及其他KPI指标的采集,为业务流程的管理、监督、考核和优化提供依据。 返回 https://www.doczj.com/doc/df10185068.html,工作流管理系统详细介绍 https://www.doczj.com/doc/df10185068.html,工作流管理系统涵盖了从流程开发、发布、管理配置、运行、监控的整个过程,包括如下几个组成部分: ?可视化的工作流开发环境?工作流引擎与服务 ?WEB客户端管理?可视化的流程监控 ?标准的工作流服务组件?流程套路生产线 可视化的工作流开发环境