双向移位寄存器

摘要:系统使用EDA技术设计了具有移位功能的寄存器,采用硬件描述语言VHDL进行设计,然

后进行编程,时序仿真。软件基于Verilog语言实现了双向32位移位寄存器的控制功能。通过本设

计熟悉QuartusII环境下的硬件描述操作流程,掌握基本的Verilog语法与编写风格。

关键字:EDA;Verilog;32位双向移位寄存器

1.引言

随着社会的发展,科学技术也在不断的进步。特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为EDA服务;

(2)硬件电路与软件设计过程已高度渗透;

(3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;

(4)数字系统的芯片化实现手段已成主流。

因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言VHDL对32位双向移位寄存器进行编程实现。

2.课程设计的目的

在计算机中常要求寄存器有移位功能。如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。因此,移位寄存器的设计是必要的。

本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课程设计更加深入的了解移位寄存器的功能。了解EDA技术,并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关知识理论联系实际,掌握所学的课程知识。通过对移位寄存器的设计,巩固和综合运用所学知识,提高对计算机组成原理的理解。

3.课程设计的内容

本课程设计是带有32位双向移位寄存器。CLK是移位时钟信号,load是并行数据预置使能信号,QB是串行输出端口。此移位寄存器的工作方式是:当CLK的上升沿到来时过程被启动,如果这时预置使能load为低电平,LEFT_RIGHT为低电平,循环右移;如果预置使能load为低电平,LEFT_RIGHT 为高电平,循环左移。

4 Verilog HDL介绍

4.1Verilog语言的特点

(1)与其他的硬件描述语言相比,VHDL具有更强的行为描述能力,从而决定了他成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。

(3)VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和已有设计的再利用功能。符合市场需求的大规模系统高效,高速的完成必须有多人甚至多个代发组共同并行工作才能实现。

(4)对于用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表。

(5)VHDL对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。

4.2 .Verilog HDL的设计流程

4.2.1设计规范的定义

明确设计的目的,进行设计的总体规划。分析设计要求,以及自己要达到的设计目的和目标。

4.2.2 采用Verilog HDL进行设计描述

这部分包括设计规划和程序的编写。设计规划主要包括设计方式的选择及是否进行模块划分。设计方式一般包括直接设计,自顶向下和自底向下设计。

4.2.3 Verilog HDL程序仿真

对于某些人而言,仿真这一步似乎是可有可无的。但是对于一个可靠的设计而言,任何设计最好都进行仿真,以保证设计的可靠性。另外,对于作为一个独立的设计项目而言,仿真文件的提供足可以证明你设计的完整性。

4.2.4 综合优化和布局布线

综合指的是将设计描述转化成底层电路的表示形式,其结果是一个网表或者是一组逻辑方程;优化,这个主要是为了提高程序的执行效率及减少资源的利用;布局布线,指的是将逻辑关系转化成电路连接的方式。

4.2.5 仿真

这一步主要是为了确定你的设计在经过布局布线之后,是不是还满足你的设计要求。

5.总体设计方案

5.1移位寄存器的工作原理

用VHDL语言描述任意分频数的分频器,并实现占空比任意设置.每当系统时钟上升沿到来时,计数器就加计数一位(可任意设置为N位),当计数值到达预定值时就对分频时钟翻转.这样就会得到一个连续的时钟脉冲.

当移位信号到来时,移位寄存器就对存储的二进制进行移位操作.移位寄存方式可自行设置(可

左移,右移,一位移,多位移位寄存)。移位寄存器需要将寄存器中的各位数据在移位控制信号的作用下,依次向高位或是低位移动移位。

移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

5.2基本设计思路

在EDA课程学习过程中,我们学习了移位寄存器的设计,从而实现但方向的数据移动;也学习模式可控制的移位寄存器的设计。

该设计是设计一个双向的32位的移位寄存器。要求,该寄存器有一个异步清零端,低电平有效。还有一个load装载数据的信号输入,用于预置数据,还有一个控制左移或是右移的信号输入

LEFT_RIGHT。因此,我们可以通过所学知识,设置CLK为移位时钟信号,LOAD为数据预置使能信号,QB是串行输出信号。三十二位双向移位寄存器工作原理框图如表一。

表一双向32位移位寄存器功能表

6.32双向移位寄存器的设计

6.1 双向移位寄存器的设计

双向移位寄存器可以在移位寄存器的基础之上添加移位模式控制数来控制。通过移位模式控制数的工作时序来控制其移位方向。本设计中预置的移位模式控制数为LEFT_RIGHT,若上升沿到来时,LEFT_RIGHT送入的是低电平,则循环右移;LEFT_RIGHT送入的是高电平,则循环左移。这样通过控制端LOAD的的控制,以及移位模式控制数LEFT_RIGHT的时序显示,即可实现双向移位寄存器的功能。如图一所示为双向移位寄存器工作模式简图

D1 D2 D3 D4 D5 …D31 D32

LEFT_RIGHT=0 右移输入输出LEFT_RIGHT=1 左移输出输入

图一双向移位寄存器工作模式简图

6.2 32位双向移位寄存器的设计

根据设计要求以及功能表可做如下设计:

当移位时钟信号CLK的上升沿到来时过程被启动,如果这时预置使能LOAD为高电平,LEFT_RIGHT 为低电平,则输入端口处的32位二进制数被同步置入移位寄存器中,用作循环右移输出的初始值;如果这时预置使能LOAD为高电平,LEFT_RIGHT为高电平,则输入端口处的32位二进制数被同步置入移位寄存器中,用作循环左移的初始值;如果预置使能LOAD为低电平,则执行以下语句: REG[30:0]<=REG[31:1];

此语句表明:一个时钟周期后将上一时钟周期移位寄存器中的高32位二进制数,即以当前值REG[7:1]更新此寄存器的低七位REG[30:0]。他们并不会自我覆盖,且其串行移空的最高位始终由最初预置数的最高位填补。将上一时钟周期移位寄存器中的最低位,即当前值REG[0]向QB输出。随着CLK脉冲的连续到来,就完成了将预置输入的数据逐位向左或向右串行输出的功能,即将寄存器中的最低位首先输出。所编程序见附录一。

由功能表可知设计需满足:当使能端LOAD为高电平时,寄存器内数不移动,即输出Q为输入D 的预置数,也就是说使能端LOAD为低电平有效。当CLK有上升沿来到时,使能信号LOAD为低电平,LEFT_RIGHT为低电平时,系统循环右移;当LEFT_RIGHT为高电平时,系统循环左移。

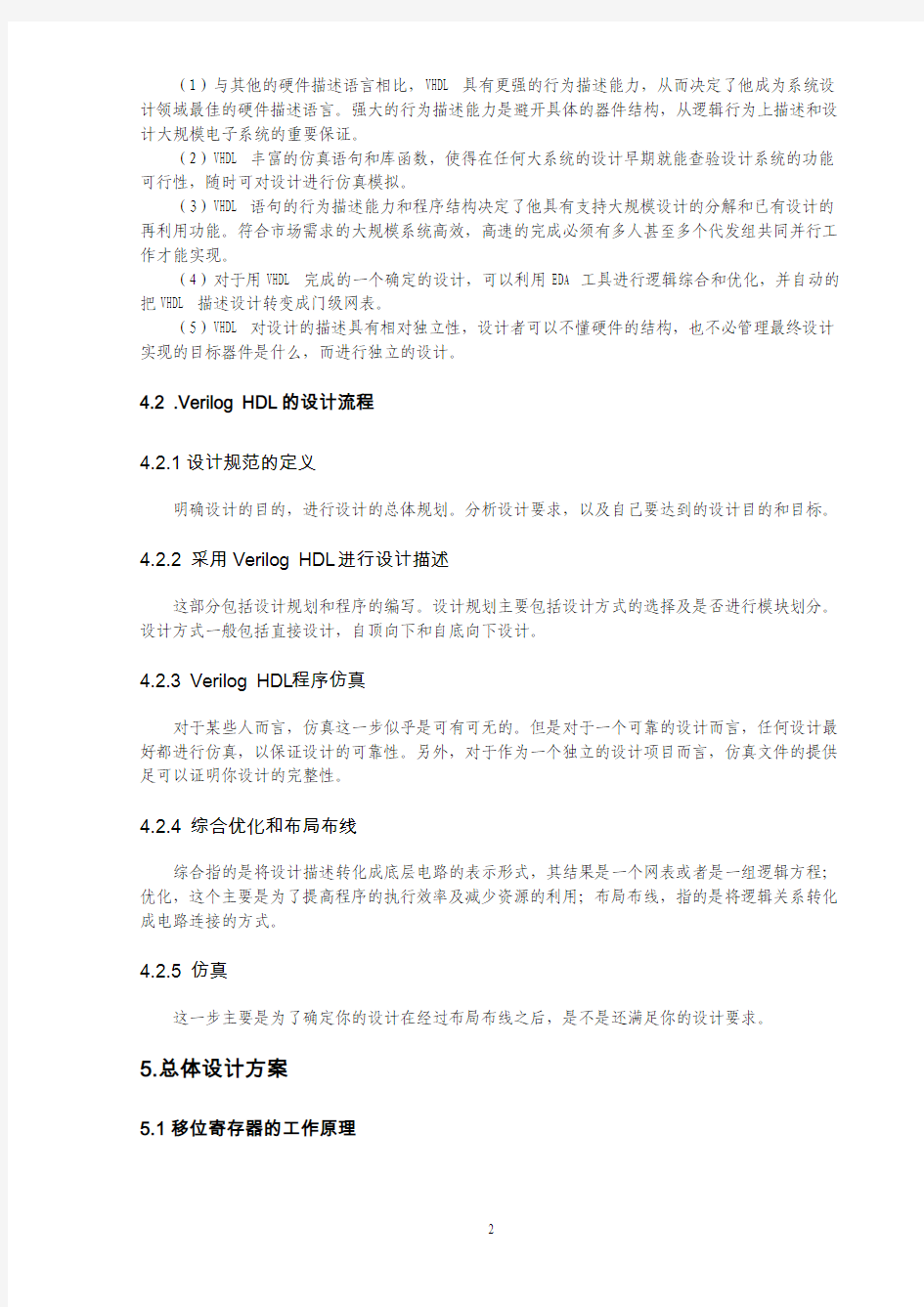

图二所示为其综合RTL图打包后的原理图

wanglei inst

CLK LOAD C0

LEFT_RIGHT D[31..0]QB[31..0]

CN

图二 32位双向移位寄存器

由原理图可得,双向32位移位寄存器输入、输出引脚分别为 CLK:移位时钟输入信号 LOAD:预置是能信号 C0:进位输入

D:待加载移位数据输入

LEFT_RIGHT:移位模式控制字 D[31..0]:数据输入总线端口 QB[31..0]:数据输出总线端口 CN:进位输出

由程序生成的内部RTL 电路图如下图3所示:

图3 三十二位双向移位寄存器RTL电路图

7.系统仿真

在QuartuaII中建立shift工程,添加Verilog文件,编写源代码后,进行全编译。编译成功后,即可对定义的模块进行功能仿真。仿真步骤查看相关QuartusII书籍。本设计中,将所有定义的引脚添加入仿真环境中,对输入数据进行强制设定,运行后观察输出波形及其时序图见图4。

图4 仿真波形时序图

对其仿真图进行仿真分析:这里我们通过考察其带进位循环左移操作的工作模式来了解此次双向移位寄存器的设计。Case语句中的两个语句,尽管属于并行执行的顺序语句,但它们的赋值不会发生原数据的覆盖情况。例如,当顺序执行REG[0]<=C0和REG[31:0]<=REG[30:0]后,并不会发生REG[1]=C0的情况,因为他们是同时被更新的。对于其仿真波形,在CLK的第一个上升沿处,

LEFT_RIGHT=101,此边沿将D的数据加载于寄存器中;在此后的三个上升沿,LEFT_RIGHT都等于001,即执行带进位循环左移操作。在第二个上升沿后,将进位输入的C0的1移入寄存器最低位,其余左移一位,最高位被移出,进入CN。另需注意最后一个上升沿后执行的是自循环右移,即将此前寄存器中的数据右移一位,期间将移出的最低位补入右移结果的最高位。

8.总结与体会

经过一学期的学习以及在课下对相关知识的查阅,我终于完成了32位双向移位寄存器的设计和实现及相关论文。从开始接到课程设计题目到系统的实现,再到论文文章的完成,每走一步对我来说都是新的尝试与挑战,这也是我在大学期间独立完成的一项比较大的项目。在这段时间里,我学到了很多知识也有很多感受,从课程设计,EDA,VHDL等相关知识很不了解的状态,我开始了独立的学习和试验,查看相关的资料和书籍,让自己头脑中模糊的概念逐渐清晰,使自己非常稚嫩作品一步步完善起来,每一次改进都是我学习的收获,每一次试验的成功都会让我兴奋好一段时间。

虽然我的论文作品不是很成熟,还有很多不足之处,但我可以自豪的说,这里面的每一段代码,都有我的劳动。为了编写程序,我把课本读了好多遍,当看着自己的程序,自己成天相伴的系统能够健康的运行,真是莫大的幸福和欣慰。我相信其中的酸甜苦辣最终都会化为甜美的甘泉。

这次做论文的经历也会使我受益匪浅,我感受到做论文是要真真正正用心去做的一件事情,是真正的自己学习的过程和研究的过程,没有学习就不可能有研究的能力,没有自己的研究,就不会有所突破,那也就不叫论文了。希望这次的经历能让我在以后学习中激励我继续进步。

通过这次EDA作业的设计,真心感觉自己的能力与知识量大大不足,刚开始为难的真是无从下手,但我并没有放弃,在网上,去图书馆以及对所学课本的再阅读,终于还是有了思路,再加上在遇到不会时虚心向同学请教,最终完成了本次的论文。

参考文献

[1]康华光.电子技术基础数字部分[M].北京:高等教育出版社, 2006

[2]赵艳华,曹丙霞,张睿.基于Quartus II的FPGA/CPLD设计与应用[M].北京:电子工业出版社, 2009

[3] 庄严. EDA技术与数字系统设计.北京:电子工业出版社.2009

附录1

32位双向移位寄存器程序

module wanglei(CLK,LOAD,C0,LEFT_RIGHT,D,QB,CN);

output CN;output [31:0] QB;

input CLK,LOAD,C0,LEFT_RIGHT;

input [31:0] D;

reg[31:0] REG;

reg CY;

always @(posedge CLK)begin

if(LOAD==0)

case(LEFT_RIGHT)

0:begin REG[0]<=C0;REG[31:1]<=REG[30:0];CY<=REG[31];end 1:begin REG[7]<=C0;REG[30:0]<=REG[31:1];CY<=REG[0];end default:begin REG<=REG;CY<=CY;end

endcase

else begin REG<=REG;CY<=CY;end

end

assign QB=REG;assign CN=CY;

endmodule

《EDA课程设计》 32位并进并出移位寄存器设计 学院:物理电气信息学院 专业:通信工程 姓名:杨小花 学号:12010245315 指导老师:杨泽林 完成日期:2012.12.11

32位并进并出移位寄存器设计 (杨小花12010245315 通信工程专业) 摘要:EDA技术作为现代电子设计技术的核心,它依赖强大的计算机,在EDA工具软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑简化、逻辑分割、逻辑综合,以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。随着基于EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。关键字:EDA技术;VHDL语言;移位寄存器 一、实验原理 用一个8位移位寄存器,再增加一些电路,如4个8位锁存器等,设计成为一个能为32位二进制数进行不同方式移位的移位寄存器。8位是CPU设计中常用的移位寄存器模块,是用CASE语句设计的并行输入输出的移位寄存器模块。设计中有四种循环:带进位循环左移,带进位循环右移,自循环左移和自循环右移。其中带进位循环左移的原理是,每一次最高位移出进入输出进位,而最低位是设置的进位输入,带进位循环右移原理是,每一次最低位移出进入输出进位,而最高位是设置的进位输入,子循环左移的原理是,每一次循环,最高位进入到最低位,依次循环,自循环右移原理是,每一次最低位进入到最高位,依次循环。 二、实验步骤 1、建立一个工程项目,设置路径,项目名和顶层实体名一致; 2、设计一个8位移位寄存器电路;

3、设计一个8位锁存器电路; 4、运用元件调用声明语句和元件例化语句完成顶层设计。 三、实验程序 1、八位移位寄存器程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY SHIFTIS PORT ( CLK,CO: IN STD_LOGIC; --时钟和进位输入 MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位模式控制字 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); -- 待加载移位的数据 QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --移位数据输出 CN : OUT STD_LOGIC); --- 进位输出 END SHIFT; ARCHITECTURE behav OF SHIFT IS SIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL CY : STD_LOGIC; BEGIN PROCESS(CLK,CO,MD) BEGIN IF CLK'EVENT AND CLK='1' THEN CASE MD IS

移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、原理说明 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。按代码的移位方向可分为左移、右移和可逆移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同又可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图8-3-3-1所示。 其中 D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入 C为直接无条件清零端; 端,S L为左移串行输入端;S1、S0为操作模式控制端;R CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和R C端的控制作用如表8-3-3-1。 图8-3-3-1 CC40194的逻辑符号及引脚功能 表8-3-3-1 CC40194功能表

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图8-3-3-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图8-3-3-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。其状态表如表8-3-3-2所示。 表8-3-3-2 环形计数器状态表 图 8-3-3-2 环形计数器 如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。 图8-3-3-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

实验四 一、实验名称 32位并进/并出移位寄存器设计 二、实验原理 用一个8位移位寄存器,再增加一些电路,如4个8位锁存器等,设计成为一个能为32位二进制数进行不同方式移位的移位寄存器。 三、实验步骤 1、建立一个工程项目,设置路径,项目名和顶层实体名一致; 2、设计一个8位移位寄存器电路; 3、设计一个8位锁存器电路; 4、运用元件调用声明语句和元件例化语句完成顶层设计。 四、实验程序 1、八位移位寄存器程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY jicun IS PORT ( CLK,CO: IN STD_LOGIC; --时钟和进位输入 MD : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位模式控制字 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); -- 待加载移位的数据 QB : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --移位数据输出 CN : OUT STD_LOGIC); --- 进位输出 END jicun; ARCHITECTURE behav OF jicun IS SIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL CY : STD_LOGIC; BEGIN

PROCESS(CLK,CO,MD) BEGIN IF CLK'EVENT AND CLK='1' THEN CASE MD IS WHEN "001"=> REG(0)<=CO; ---带进位循环左移 REG(7 DOWNTO 1)<= REG(6 DOWNTO 0);CY<=REG(7); WHEN "010" => REG(0)<=REG(7); ---自循环左移 REG(7 DOWNTO 1)<= REG(6 DOWNTO 0); WHEN "011"=>REG(7)<=REG(0); ---自循环右移 REG(6 DOWNTO 0)<=REG(7 DOWNTO 1); WHEN "100" =>REG(7)<=CO; ---带进位循环右移 REG(6 DOWNTO 0)<=REG(7 DOWNTO 1);CY<=REG(0); WHEN "101" =>REG(7 DOWNTO 0)<=D(7 DOWNTO 0); --加载待移数 WHEN OTHERS=>REG<=REG;CY<=CY;--保持 END CASE; END IF; END PROCESS; QB(7 DOWNTO 0)<=REG(7 DOWNTO 0);CN<=CY; END behav; 2、锁存器程序 library ieee ; use ieee.std_logic_1164.all ; entity suocun is port(d : in std_logic_vector(7 downto 0) ; q: out std_logic_vector(7 downto 0); clk : in std_logic ); end suocun ; architecture one of suocun is signal q1: std_logic_vector(7 downto 0);

第三章习题参考答案 1.画出以1)(2 4 6 +++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。 解:由1)(2 46+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++=Λ,故 (1)逻辑框图: (2)状态图: 状态圈-1: 状态圈-2: 状态圈-3: 状态圈-4: 状态圈-5: 状态圈-6: 状态圈-7: 状态圈-8:

状态圈-9: 状态圈-10: 状态圈-11: 状态圈-12: 2.已知图3-2所示的7级线性反馈移位寄存器: 图3-2 (1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。 (3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为: k k k k a a a a ++=+++357 ()0≥k 。 联接多项式为:7 4 2 1)(x x x x f +++=。 特征多项式为:7531)(~ x x x x f +++=

(2)状态转移矩阵:? ? ???? ? ?? ? ? ??0100000 101000000010001000100 000001000000011000000。 (3)输出序列:)111111111(ΛΛ=- a 。 3.设5级线性反馈移位寄存器的联接多项式为1)(2 5 ++=x x x f ,初态为(10101)。求输出序列a 。 解:由联接多项式得,反馈函数为:41521),,,(x x x x x f +=Λ。故以)10101(为初态的状态转移图为: 10101 01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a 44444443444444421一个周期 0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n F 2,∈?βα,令),,,(110-=n a a a Λα, ),,,(110-=n b b b Λβ,有: ),,,(),,,()(121110∑=--==n i i n i n f f a c a a a a a T T ΛΛα, ),,,(),,,()(1 21110∑=--==n i i n i n f f b c b b b b b T T ΛΛβ。 ) ()() ,,,(),,,() )(,,,() ,,,()(1 211 2112211111100βαβαf f i n n i i i n n i i n i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑ΛΛΛΛ 对 2F k ∈?, ))((),,,(),,,()(1 21110ααf i n n i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ΛΛ。 故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n F 2上的线性变换。

实验五移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3 为并行输入端;Q 、Q 1 、Q 2 、Q 3 为并行输出端;S R 为右 移串行输入端,S L 为左移串行输入端;S 1 、S 为操作模式控制端;R C为直接无 条件清零端;CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3 ),左移 (方向由Q 3→Q ),保持及清零。 S 1、S 和R C端的控制作用如表10-1。

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态Q Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q 0Q 1 Q 2 Q 3 将依次变为0100→0010→0001→1000 →……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图10-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 图 10-2环形计数器 如果将输出Q O 与左移串行输入端S L 相连接,即可达左移循环移位。 (2)实现数据串、并行转换

双向移位寄存器 摘要:系统使用EDA技术设计了具有移位功能的寄存器,采用硬件描述语言VHDL进行设计,然 后进行编程,时序仿真。软件基于Verilog语言实现了双向32位移位寄存器的控制功能。通过本设 计熟悉QuartusII环境下的硬件描述操作流程,掌握基本的Verilog语法与编写风格。 关键字:EDA;Verilog;32位双向移位寄存器 1.引言 随着社会的发展,科学技术也在不断的进步。特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为EDA服务; (2)硬件电路与软件设计过程已高度渗透; (3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用; (4)数字系统的芯片化实现手段已成主流。 因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。 移位寄存器正在向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超高速硬件描述语言VHDL对32位双向移位寄存器进行编程实现。 2.课程设计的目的 在计算机中常要求寄存器有移位功能。如在进行乘法时,要求将部分积右移;在将并行传送的数转换成串行数时也需要移位。因此,移位寄存器的设计是必要的。 本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课程设计更加深入的了解移位寄存器的功能。了解EDA技术,并掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关知识理论联系实际,掌握所学的课程知识。通过对移位寄存器的设计,巩固和综合运用所学知识,提高对计算机组成原理的理解。 3.课程设计的内容 本课程设计是带有32位双向移位寄存器。CLK是移位时钟信号,load是并行数据预置使能信号,QB是串行输出端口。此移位寄存器的工作方式是:当CLK的上升沿到来时过程被启动,如果这时预置使能load为低电平,LEFT_RIGHT为低电平,循环右移;如果预置使能load为低电平,LEFT_RIGHT 为高电平,循环左移。 4 Verilog HDL介绍 4.1Verilog语言的特点

Data sheet acquired from Harris Semiconductor SCHS025D ? Revised October 2003 The CD4015B-series types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic package (E suffix), 16-lead small-outline packages (M, M96, MT, and NSR suffixes), and 16-lead thin shrink small-outline packages (PW and PWR suffixes). Copyright 2003, Texas Instruments Incorporated

PACKAGING INFORMATION Orderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)CD4015BE ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU Level-NC-NC-NC CD4015BF ACTIVE CDIP J 161None Call TI Level-NC-NC-NC CD4015BF3A ACTIVE CDIP J 161None Call TI Level-NC-NC-NC CD4015BM ACTIVE SOIC D 1640Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIM CD4015BM96 ACTIVE SOIC D 162500Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIM CD4015BMT ACTIVE SOIC D 16250Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIM CD4015BNSR ACTIVE SO NS 162000Pb-Free (RoHS)CU NIPDAU Level-2-260C-1YEAR/Level-1-235C-UNLIM CD4015BPW ACTIVE TSSOP PW 1690Pb-Free (RoHS)CU NIPDAU Level-1-250C-UNLIM CD4015BPWR ACTIVE TSSOP PW 162000Pb-Free (RoHS)CU NIPDAU Level-1-250C-UNLIM (1)The marketing status values are defined as follows: ACTIVE:Product device recommended for new designs. LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect. NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design. PREVIEW:Device has been announced but is not in production.Samples may or may not be available. OBSOLETE:TI has discontinued the production of the device. (2)Eco Plan -May not be currently available -please check https://www.doczj.com/doc/155982285.html,/productcontent for the latest availability information and additional product content details. None:Not yet available Lead (Pb-Free). Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes. Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight. (3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis. PACKAGE OPTION ADDENDUM https://www.doczj.com/doc/155982285.html, 28-Feb-2005Addendum-Page 1

实验八移位寄存器功能测试及应用 一、实验目的: 1.掌握中规模4位双向寄存器逻辑功能及使用方法。 2.熟悉移位寄存器的应用,实现数据的串行、并行转换和构成环形计数器 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS194一片。 三、预习要求及思考题 1.预习要求: 1) 复习有关寄存器有关内容。 2)熟悉74LS194逻辑功能及引脚排列。 3)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题: 1) 使寄存器清零,除采用输入低电平外,可否采用右移或左移的方法?可否使用 并行送数法?若可行,如何进行操作? 2) 环行计数器的最大优点和缺点是什么? 四、实验原理 1.位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相 同,可互换使用,其逻辑符号及引脚图如图8-1所示。 图8-1 74LS194的逻辑符号图及引脚功能图. 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入端;S L为左移串行输入端;S0、S1为操作模式控制端;C R为直接无条件清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和C R端的控制作用如表8-1

8位数码扫描显示电路设计 一、实验目的 学习硬件扫描显示电路的设计; 二、实验原理 动态数码扫描显示方式是利用了人眼的视觉暂留效应,把八个数码管按一定顺序进行点亮,当点亮的频率不大时,我们看到的是数码管一个个的点亮,然而,当点亮频率足够大时,我们看到的不再是一个一个的点亮,而是全部同时显示,与传统方式得到的视觉效果完全一样。因此我们只要给数码管这样一个扫描频率,那么就可以实现两个以上的数码管同时点亮。而这个频率我们可以通过一个计数器来产生,只要计数频率足够大,就可以实现我们的要求。事实上,因为数码管点亮不是瞬间就可以的,它也需要一定的时间,该时间与数码管的选择有关系。为了折中这一对矛盾,实验中一般可将计数频率选择在100Hz左右。 图示8位数码扫描显示电路,其中每个数码管的8 个段:h、g、f、e、d、c、b、a(h 是小数点)都分别连在一起,8 个数码管分别由8 个选通信号k1、k2、… k8 来选择。被选通的数码管显示数据,其余关闭。如在某一时刻,k3 为高电平,其余选通信号为低电平,这时仅k3 对应的数码管显示来自段信号端的数据,而其它7 个数码管呈现关闭状态。根据这种电路状况,如果希望在8 个数码管显示希望的数据,就必须使得8 个选通信号k1、k2、… k8 分别被单独选通,并在此同时,在段信号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。 实验参考扫描显示程序中clk 是扫描时钟;SG 为7 段控制信号,由高位至低位分别接g、f、e、d、c、b、a 7个段;BT 是位选控制信号,接图5-2 中的8 个选通信号:k1、k2、… k8 。程序中CNT8 是一个3 位计数器,作扫描计数信号,由进程P2 生成;进程P3 是7 段译码查表输出程序,进程P1 是对8 个数码管选通的扫描程序,例如当CNT8 等于

实验五 移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用 — 实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 图10-1 CC40194的逻辑符号及引脚功能 其中 D 0、D 1 、D 2 、D 3为并行输入端;Q 0、Q 1、Q 2、Q 3为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端;S 1、S 0 为操作模式控制端; R C 为直接无条件清零端;CP 为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q 0→Q 3),左移(方向由Q 3→Q 0),保持及清零。 S 1、S 0和R C 端的控制作用如表10-1。 表10-1

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q 3和右移串行输入端S R 相连接,设初始状态 Q 0Q 1 Q 2 Q 3 =1000,则在时钟脉冲作用下Q Q 1 Q 2 Q 3 将依次变为0100→0010→0001 →1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数

实验七 移位寄存器及其应用 一、实验目的 1. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2. 熟悉移位寄存器的应用——环形计数器。 二、实验原理 1. 移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又有右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图 1所示。 图 1 74LS194的逻辑符号及其引脚排列 其中D 3、D 2、D 1、D 0为并行输入端, Q 3、Q 2、Q 1、Q 0为并行输出端;S R 为右移串行输入端,S L 为左移串行输入端,S 1、S 0为操作模式控制端;CR 为直接无条件清零端;CP 为时钟脉冲输入端。74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q 3→Q 0),左移(方向由Q 0→Q 3),保持及清零。S 1、S 0和CR 端的控制作用如表 1所示。 表 1

2.移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计致器和串行累加器的线路及其原理。 (1) 环形计数器:把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图2所示,把输出端Q 0和右移串行输入端S R 相连接,设初始状态Q 3 Q 2 Q 1 Q =1000, 则在时钟脉冲作用下Q 3Q 2 Q 1 Q 将依次变为0100→0010→0001→1000→……,可见它是具 有四个有效状态的计数器,这种类型的计效器通常称为环形计数器。图2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

8位数码扫描显示电路设计 1 2 一、实验目的 3 学习硬件扫描显示电路的设计; 二、实验原理 4 5 动态数码扫描显示方式是利用了人眼的视觉暂留效应,把八个数码管6 按一定顺序进行点亮,当点亮的频率不大时,我们看到的是数码管一个7 个的点亮,然而,当点亮频率足够大时,我们看到的不再是一个一个的8 点亮,而是全部同时显示,与传统方式得到的视觉效果完全一样。因此9 我们只要给数码管这样一个扫描频率,那么就可以实现两个以上的数码管同时点亮。而这个频率我们可以通过一个计数器来产生,只要计数频 10 11 率足够大,就可以实现我们的要求。事实上,因为数码管点亮不是瞬间12 就可以的,它也需要一定的时间,该时间与数码管的选择有关系。为了折中这一对矛盾,实验中一般可将计数频率选择在100Hz左右。 13 14 图示8位数码扫描显示电路,其中每个数码管的8 个段:h、g、f、e、 15 d、c、b、a(h 是小数点)都分别连在一起,8 个数码管分别由8 个选 16 通信号k1、k2、… k8 来选择。被选通的数码管显示数据,其余关闭。 17 如在某一时刻,k3 为高电平,其余选通信号为低电平,这时仅k3 对应18 的数码管显示来自段信号端的数据,而其它7 个数码管呈现关闭状态。 根据这种电路状况,如果希望在8 个数码管显示希望的数据,就必须使 19 20 得8 个选通信号k1、k2、… k8 分别被单独选通,并在此同时,在段信21 号输入口加上希望在该对应数码管上显示的数据,于是随着选通信号的扫变,就能实现扫描显示的目的。 22 23 实验参考扫描显示程序中clk 是扫描时钟;SG 为7 段控制信号,由高

7.3.3移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用——实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图10-1所示。 2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图10-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表7-29所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图7-52 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 表

图 7-52 环形计数器 (2)实现数据串、并行转换 第一串行/并行转换器串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。图10-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。电路中S0端接高电平1,S1受Q7控制,二片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式,当Q7=0时,S1=1,有S1S0=10,则串行送数结束,标志着串行输入的数据已 图10-3 七位串行 / 并行转换器 串行/并行转换的具体过程如下: 转换前,R C端加低电平,使1、2两片寄存器的内容清0,此时S1S0=11,寄存器执行并行输入工作方式。当第一个CP脉冲到来后,寄存器的输出状态Q0~Q7为01111111,与此同时S1S0变为01,转换电路变为执行串入右移工作方式,串行输入数据由1片的S R端加入。随着CP 脉冲的依次加入,输出状态的变化可列成表10-3所示。 表10-3 由表10-3可见,右移操作七次之后,Q7变为0,S1S0又变为11,说明串行输入结束。这时,串行输入的数码已经转换成了并行输出了。 当再来一个CP脉冲时,电路又重新执行一次并行输入,为第二组串行数码转换作好了准备。 第二,并行/串行转换器,并行/串行转换器是指并行输入的数码经转换电路之后,换成串行输出。图10-4是用两片CC40194(74LS194)组成的七位并行/串行转换电路,它比图10-3多了两只与非门G1和G2,电路工作方式同样为右移。

TL F 5964CD4035BM CD4035BC 4-Bit Parallel-In Parallel-Out Shift Register February 1988 CD4035BM CD4035BC 4-Bit Parallel-In Parallel-Out Shift Register General Description The CD4035B 4-bit parallel-in parallel-out shift register is a monolithic complementary MOS (CMOS)integrated circuit constructed with P-and N-channel enhancement mode transistors This shift register is a 4-stage clocked serial reg-ister having provisions for synchronous parallel inputs to each stage and serial inputs to the first stage via JK logic Register stages 2 3 and 4are coupled in a serial ‘‘D’’flip-flop configuration when the register is in the serial mode (parallel serial control low) Parallel entry via the ‘‘D’’line of each register stage is per-mitted only when the parallel serial control is ‘‘high’’ In the parallel or serial mode information is transferred on positive clock transitions When the true complement control is ‘‘high’’ the true con-tents of the register are available at the output terminals When the true complement control is ‘‘low’’ the outputs are the complements of the data in the register The true com-plement control functions asynchronously with respect to the clock signal JK input logic is provided on the first stage serial input to minimize logic requirements particularly in counting and se-quence-generation applications With JK inputs connected together the first stage becomes a ‘‘D’’flip-flop An asyn-chronous common reset is also provided Features Y Wide supply voltage range 3 0V to 15V Y High noise immunity 0 45V DD (typ )Y Low power TTL Fan out of 2driving 74L compatibility or 1driving 74LS Y 4-stage clocked operation Y Synchronous parallel entry on all 4stages Y JK inputs on first stage Y Asynchronous true complement control on all outputs Y Reset control Y Static flip-flop operation master slave configuration Y Buffered outputs Y Low power dissipation 5m W (typ )(ceramic)Y High speed to 5MHz Applications Y Automotive Y Alarm systems Y Data terminals Y Industrial controls Y Instrumentation Y Remote metering Y Medical electronics Y Computers Logic Diagram TL F 5964–1 P S e 0e serial mode T C e 1e true outputs TG e transmission gate TL F 5964–2 Input to output is a)A bidirectional low impedance when control input 1is low and control input 2is high b)An open circuit when control input 1is high and control input 2is low C 1995National Semiconductor Corporation RRD-B30M105 Printed in U S A