串行接口同步通信协议

[摘要]:接口在微型计算机系统的设计和应用中占有极为重要的地位。在微型计算机系统中,CPU要与存储器和输入/输出设备之间交换信息,这些信息的交换要借助接口来实现。接口是沟通微处理机和外部设备之间的桥梁,它减轻了CPU的负担,使CPU能够充分的发挥任务管理和逻辑判断作用,使CPU和外部设备能更加协调的完成输入/输出工作,从而提高整机的工作效率和系统功能。串行接口是使用串行方式进行数据传输的输入/输出接口,根据在串行通信中数据的定时的不同,串行通信可分为同步通信和异步通信。同步通信中为保证通信的正确,发送装置和接收装置事先必须有一个双方共同遵守的协议,这就是串行接口同步通信协议。

[关键词]:输入/输出接口,串行接口,同步通信,协议,SDLC/HDLC 规程

一、串行接口

在计算机领域内,有两种数据传送方式:串行传送和并行传送。并行数据传送中,数据在多条并行1比特宽的传输线上同时由源传送到目的,这种传送方式也称为比特并行或字节串行。串行数据传送中,数据在单条1比特宽的传输线上,1比特1比特

的按顺序分时传送。

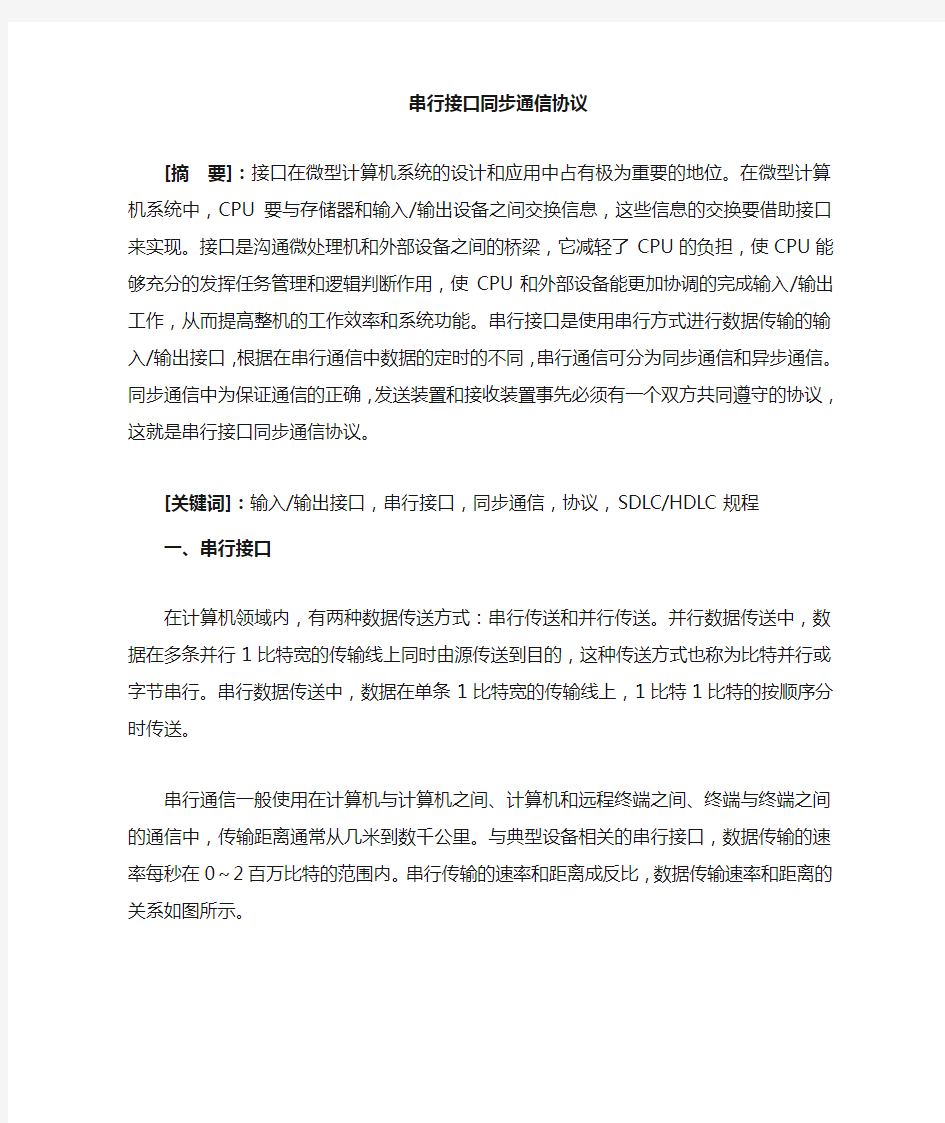

串行通信一般使用在计算机与计算机之间、计算机和远程终端之间、终端与终端之间的通信中,传输距离通常从几米到数千公里。与典型设备相关的串行接口,数据传输的速率每秒在0~2百万比特的范围内。串行传输的速率和距离成反比,数据传输速率和距离的关系如图所示。

串行通信接口的信号电平常采用RS-232-C信号电平或20mA 电流环路操作方法。

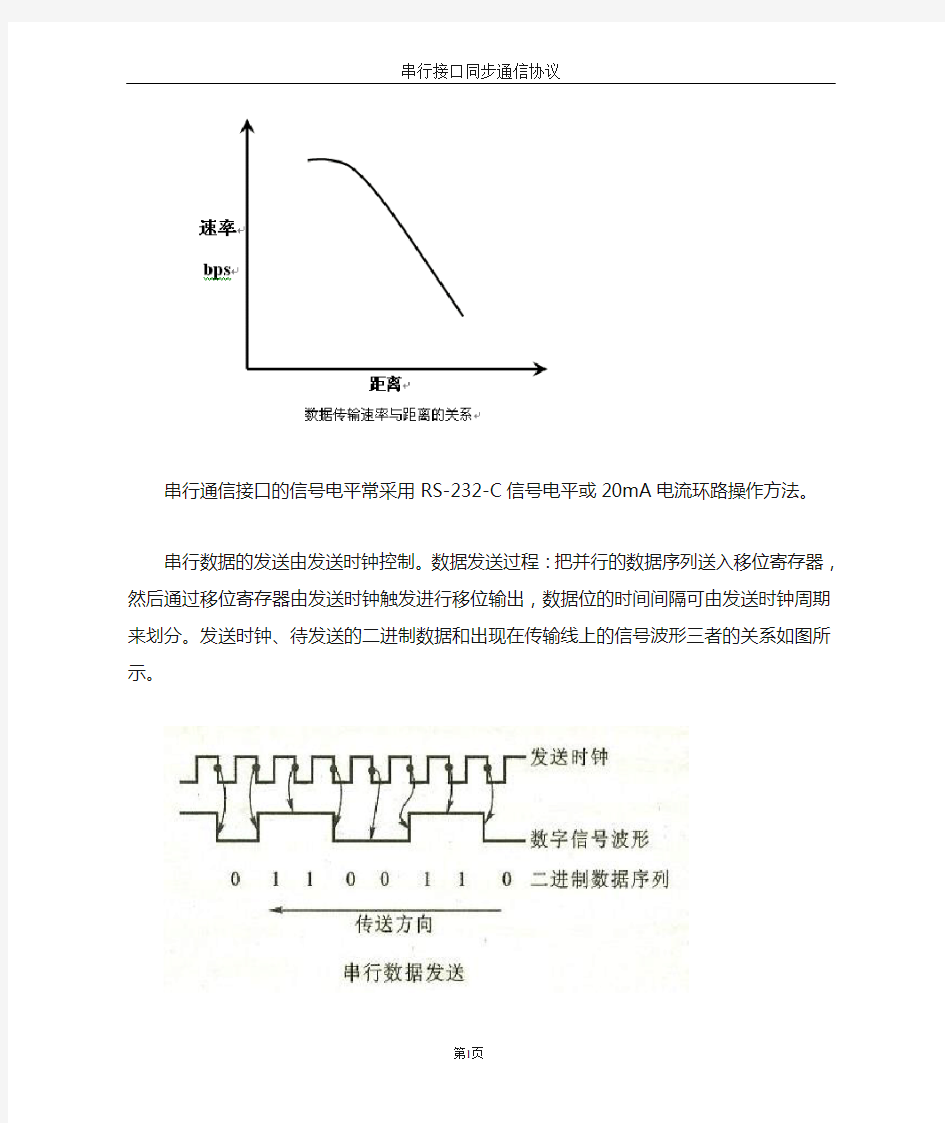

串行数据的发送由发送时钟控制。数据发送过程:把并行的数据序列送入移位寄存器,然后通过移位寄存器由发送时钟触发进行移位输出,数据位的时间间隔可由发送时钟周期来划分。发送时钟、待发送的二进制数据和出现在传输线上的信号波形三者的关系如图所示。

串行数据的接收由接收时钟检测,接收数据的过程:把由传输线送来的串行数据序列由接收时钟作为输入移位寄存器的触发脉冲,逐位打入移位寄存器,接收过程就是将串行数据序列逐位移入移位寄存器而装配成为并行数据序列的过程。接收时钟、传输线上送来的数字信号波形和接收器检测到的二进制数据序列三者的对应关系如图所示。

二、同步传送

高速通信要求采用同步传送。同步通信如果具有适当的电气连接,很容易达到500kbps的传输速度。

同步通信发送端和接收端必须用共同的时钟源才能保持它们之间的准确同步。同步传输时,每个字符没有起始位和停止位,它不是用起始位来标志字符的开始,而是用一串特定的二进制序列,称为同步字符,去通知接收器串行数据的第一位何时到达。然后,串行数据信息以连续的形式发送,每个时钟周期发送1位数据。接收器搜索到同步字符后,才开始接收数据位。因此,同步传输时数据成批连续发送,信息字符间不留空隙,它严格按照约定的速率发送和接收。发送器在发送数据过程中,如果出现没有准备好发送数据的情况,发送装置就会发送同步字符来填充。同步传送的成批数据称为数据流或数据场。

同步传送为保持发送端和接收端的同步,发送器和接收器不能采用独立的局部时钟,接收时钟是从接收数据流分离出来的。为达到接收和发送的准确同步,其中一个方法是采用编码和解码的原理,即在发送端利用编码器把要发送的数据和发送时钟组合在一起,通过传输线发送到接收端,在接收端再用解码器从数据流中分离出接收时钟。常用的编码解码器有曼彻斯特编码解码。

三、同步通信规程

同步通信规程可以分为两类,一类是面向字符型的规程,另

一类是面向比特型的规程。

(一)面向字符型的规程

面向字符型的规程于1960年就制定了。这类规程又分为基本型和扩充型两种,扩充型又分为全双工会话型和代码透明型。国际标准化组织ISO制定的基本型通信规程BASIC,以及IBM公司制定的双同步通信规程BISYNC都是面向字符型的通信规程。

这种规程的特点是:规定几个字符作为传输控制的专用字符,信息长度是8的整数倍,传输速率为200~4800bps。

(二)面向比特型的通信规程

面向比特型的通信规程是1969年由IBM公司首先提出的。这种规程的特点是没有规定专用的传输控制字符,而是由一些比特组合作为传输控制用,其信息长度可变,而且不是字符编码的整数倍,其传输速率可达到2400bps以上。

面向比特型的通信规程有:IBM公司制定的同步数据链路控制规程SDLC,ISO制定的高级数据链路控制规程HDLC,美国国家标准化协会ANSI制定的先进数据通信规程ADCCP,CCITT的建议书也是HDLC的变体之一。

1、SDLC/HDLC规程

SDLC/HDLC规程是当前同步通信普遍采用的规程,有很多可编程通用串行I/O接口支持这类规程,它将很有可能成为最广泛应用的网络物理层协议,特别是很多单片机都配备支持这种规程的串行I/O通道。

SDLC和HDLC两种规程的格式是一样的,只是在某些技术细节上两者有区别。

SDLC/HDLC规程是以帧为单位传送信息的。一帧信息是若干场组成的。首先是起到同步字符作用的标志场,简称为F场;其后跟着地址场,简称为A场;地址场后是控制场,简称为C场;控制场后才是信息场,简称为I场;再后是16位的帧校验场,简称为FC场;最后是结束标志。由此看出,SDLC/HDLC规程的标志字符是帧的边界,接收器搜索到标志符后开始一帧信息的接收。以结束标志来作为一帧的结束,接收器一旦收到结束标志,前面的16位就用作CRC循环冗余校验码,以便确定前面传送过程中是否出现了错误。

SDLC/HDLC规程的所有场都是由最低有效位开始传送的。

(1)SDLC/HDLC规程的标志场

SDLC/HDLC规程的标志符是一个字节长,其格式为01111110,即两个0中间夹着6个连续的1。一帧信息以标志符为起始,并以标志符作为结束。

为了使数据具有透明性,即任何数据均能传输,又要使标志符具有唯一性,即在数据序列中不能再出现标志符格式的序列,在发送一方要采用“0比特插入技术”,即发送方发送信息帧时,对于除标志符以外的所有信息,只要遇到5个连续的1,就在其后自动的插入1个0。接收时为恢复信息的原来格式,在接收方面要采用“0比特删除技术”,即除标志符外,当连续接收到5

个1时,就自动删除1个0。“0比特插入/删除技术”分别由发送器和接收器用硬件方法来实现。按规程规定,插入的0不参加CRC循环冗余校验。

(2)SDLC/HDLC规程的地址场和控制场

SDLC规程的地址场和控制场都是1个字节长,而HDLC规程的地址场可以为任意字节,控制场可以为1个字节或2个字节。

接收方通过检查每一个地址字节的第一位确定地址字节数。若第一位为0,则后面还跟有1个地址字节;若第一位为1,则此字节就是最后一个地址字节。控制场的字节数也是通过检查第一个字节的第一位确定的。若第一位为0,则控制场是2个字节长;否则就是1个字节长。

当由SDLC/HDLC规程支持的网络实现通信时,都是由一个主站和一个或多个次站组成,次站之间不能直接通信。次站通常不只一个,每个次站分配有地址,主站发向次站的信息帧必须有次站的地址,即地址场。各个次站都可以收到主站发出的地址场,然后与自己的地址相比较,只有与主站发出的地址一致时,次站才能可是接收信息场。

(3)SDLC/HDLC规程的信息场

控制场后跟着信息场,信息场就是要传送的信息。信息场的长度可以从0位到存储器能够处理的最大位数,即信息的长度不是字符的整数倍。信息场可以是任意数目和任意模式的二进制位。

(4)SDLC/HDLC规程的帧校验场

在信息场后紧跟着两个字节的CRC校验场。SDLC/HDLC规程只能用CRC进行差错校验,其生成多项式为:X16+X12+X5+1,是16位的,CRC字符是两个字节。

除了标志场和自动插入的0比特之外,所有信息均参加CRC 计算。

(5)SDLC/HDLC规程的异常结束标志

SDLC/HDLC规程不允许信息中间有空白,也不能像其它同步规程那样,当信息跟不上的时候自动插入同步字符。所以要求发送器在数据发送的开头就必须将全部数据都准备在缓冲区中。若发送过程中数据没有准备好,则发送器将会作无数据发送处理,即发送一个异常结束字符,或称为失效字符。接收器收到异常结束字符后,自动将本帧作废。

在SDLC规程中,异常结束字符是8个连续的1;在HDLC规程中,异常结束字符是7个连续的1。

在异常结束字符中不能使用“0比特插入/删除技术”。

SDLC/HDLC规程规定,当一帧结束而发送器仍处于开放时,发送器可以发送连续的标志符序列,表示器件空闲状态。当发送器被禁止时,传输线就出现连续的高电平,表示线路空闲。

2、几种常用的同步串行传输格式

同步通信由于采用的同步手段和同步字符的不同,存在着不同的格式结构。

对同步字符的检测和同步控制,在串行I/O接口芯片内部进行,称为内同步。内同步又分为单同步和双同步两种,单同步只有一个字节的同步字符,双同步有两个字节的同步字符。SDLC/HDLC规程就是内同步的一种。

外同步是指对同步字符的检测在串行接口电路芯片外部进行的,当外部硬件电路检测到同步字符时,就给串行接口发来一个同步信号SYNC,当I/O接口接收到同步信号后,立即开始接收信息。

几种同步串行传输格式如图所示。

四、结束语

在微型计算机串行同步通信中,通信协议是为了保证串行同步通信的正确,发送装置和接收装置事先约定的一个要求双方共同遵守的协议。在串行接口同步通信协议的约束下,发送方与接

收方有条不紊的进行信息的传送。其中SDLC协议和HDLC协议是使用最为广泛的串行接口同步通信协议。

参考文献:

[1]《微型计算机接口技术》李大友主编高等教育出版社

[2]《SDLC/HDLC协议》章铭著

[3]《微型计算机接口》韩涛著

微机原理与应用实验报告6 实验9 串行通信技术 实验10A 模拟信号转换接口 实验报告

实验九串行通信技术 一、实验目的 1. 了解异步串行通信原理; 2. 掌握MSP430异步串行通信模块及其编程方法; 二、实验任务 1. 了解MSP430G2553实验板USB转串口的通信功能,掌握串口助手的使用 (1)利用PC机的串口助手程序控制串口,实现串口的自发自收功能 为实现PC串口的自发自收功能,须现将实验板上的扩展板去下,并将单片机板上的BRXD和BTXD用杜邦线进行短接,连接图如下所示: 由此可以实现PC串口的自收自发功能。 (2)思考题:异步串行通信接口的收/发双方是怎么建立起通信的 首先在异步通信中,要求接收方和发送方具有相同的通信参数,即起始位、停止位、波特率等等。在满足上面条件的情况下,发送方对于每一帧数据按照起始位数据位停止位的顺序进行发送,而接收方则一直处于接受状态,当检测到起始位低电平时,看是采集接下来发送方发送过来的数据,这样一帧数据(即一个字符)传送完毕,然后进行下一帧数据的接受。这样两者之间就建立起了通信。 2. 查询方式控制单片机通过板载USB转串口与PC机实现串行通信 (1)硬件连接图

(2)C语言程序 采用SMCLK=1.0MHz时,程序如下:

其中SMCLK=1MHz,波特率采用的是9600,采用低频波特方式,则N=1000000/9600=104.1666…,故UCA0BR1=0,UCA0BR0=104,UCBRS=1; 当采用外部晶振时,时钟采用默认设置即可,程序如下:

也是采用了低频波特率方式,所以关于波特率设置的相关计算和上面是一样的。 (3)思考:如果在两个单片机之间进行串行通信,应该如何设计连线和编程? 由于在上面的连线中将单片机上的P1.2和BRXD相连,P1.1和BTXD相连,所以若要在两个单片机之间进行通信,首先应该将两个单片机的P1.2和P1.1交叉相连,并根据上面的程序进行相同的关于端口和波特率相关的设置即可实现两个单片机之间的通信。 3. (提高)利用PC机RS232通信接口与单片机之间完成串行通信 (1)硬件连接图 在实验时,采用了将PC机的串口com1直接连接至MSP430F149的孔型D9连接器上,G2553单片机的输出引脚P1.1和P1.2分别与F149单片机上的URXD1和UTXD1相连接,连接图如下所示:

2.5 UART串口通信设计实例(1) 接下来用刚才采用的方法设计一个典型实例。在一般的嵌入式开发和FPGA设计中,串口UART是使用非常频繁的一种调试手段。下面我们将使用Verilog RTL编程设计一个串口收发模块。这个实例虽然简单,但是在后续的调试开发中,串口使用的次数比较多,这里阐明它的设计方案,不仅仅是为了讲解RTL编程,而且为了后续使用兼容ARM9内核实现嵌入式开发。 串口在一般的台式机上都会有。随着笔记本电脑的使用,一般会采用USB转串口的方案虚拟一个串口供笔记本使用。图2-7为UART串口的结构图。串口具有9个引脚,但是真正连接入FPGA开发板的一般只有两个引脚。这两个引脚是:发送引脚TxD和接收引脚RxD。由于是串行发送数据,因此如果开发板发送数据的话,则要通过TxD线1 bit接着1 bit 发送。在接收时,同样通过RxD引脚1 bit接着1 bit接收。 再看看串口发送/接收的数据格式(见图2-8)。在TxD或RxD这样的单线上,是从一个周期的低电平开始,以一个周期的高电平结束的。它中间包含8个周期的数据位和一个周期针对8位数据的奇偶校验位。每次传送一字节数据,它包含的8位是由低位开始传送,最后一位传送的是第7位。

这个设计有两个目的:一是从串口中接收数据,发送到输出端口。接收的时候是串行的,也就是一个接一个的;但是发送到输出端口时,我们希望是8位放在一起,成为并行状态(见图2-10)。我们知道,串口中出现信号,是没有先兆的。如果出现了串行数据,则如何通知到输出端口呢?我们引入“接收有效”端口。“接收有效”端口在一般情况下都是低电平,一旦有数据到来时,它就变成高电平。下一个模块在得知“接收有效”信号为高电平时,它就明白:新到了一个字节的数据,放在“接收字节”端口里面。

串行接口同步通信协议 [摘要]:接口在微型计算机系统的设计和应用中占有极为重要的地位。在微型计算机系统中,CPU要与存储器和输入/输出设备之间交换信息,这些信息的交换要借助接口来实现。接口是沟通微处理机和外部设备之间的桥梁,它减轻了CPU的负担,使CPU能够充分的发挥任务管理和逻辑判断作用,使CPU和外部设备能更加协调的完成输入/输出工作,从而提高整机的工作效率和系统功能。串行接口是使用串行方式进行数据传输的输入/输出接口,根据在串行通信中数据的定时的不同,串行通信可分为同步通信和异步通信。同步通信中为保证通信的正确,发送装置和接收装置事先必须有一个双方共同遵守的协议,这就是串行接口同步通信协议。 [关键词]:输入/输出接口,串行接口,同步通信,协议,SDLC/HDLC 规程 一、串行接口 在计算机领域内,有两种数据传送方式:串行传送和并行传送。并行数据传送中,数据在多条并行1比特宽的传输线上同时由源传送到目的,这种传送方式也称为比特并行或字节串行。串行数据传送中,数据在单条1比特宽的传输线上,1比特1比特

的按顺序分时传送。 串行通信一般使用在计算机与计算机之间、计算机和远程终端之间、终端与终端之间的通信中,传输距离通常从几米到数千公里。与典型设备相关的串行接口,数据传输的速率每秒在0~2百万比特的范围内。串行传输的速率和距离成反比,数据传输速率和距离的关系如图所示。 串行通信接口的信号电平常采用RS-232-C信号电平或20mA 电流环路操作方法。 串行数据的发送由发送时钟控制。数据发送过程:把并行的数据序列送入移位寄存器,然后通过移位寄存器由发送时钟触发进行移位输出,数据位的时间间隔可由发送时钟周期来划分。发送时钟、待发送的二进制数据和出现在传输线上的信号波形三者的关系如图所示。

双机串行通信的设计与实现 一、设计要求 1.单机自发自收串行通信。接收键入字符,从8251A 的发送端发送,与同 一个8251A 的接收端接收,然后在屏幕上显示出来。 2.双机串行通信,在一台PC 机键入字符,从8251A 的发送端发送给另一台PC 机,另一台PC 机的8251A 的接收端接收,然后在屏幕上显示出来。 二、所用设备 IBM-PC 机两台(串行通信接口8251A 两片,串行发送器MC1488 和串行接收器MC1489 各两片,定时器/计数器8253,终端控制器8259 等),串口线一根 串行直连电缆用于两台台电脑通过串行口直接相连,电缆两 端的插头都是9 针的母插头: 三、硬件方案 1.设计思想 计算机传输数据有并行和串行两种模式。在并行数据传输方式中,使用8 条或更多的导线来传送数据,虽然并行传送方式的速度很快,但由于信号的衰减或失真等原因,并行传输的距离不能太长,在串行通信方式中,通信接口每次由CPU 得到8 位的数据,然后串行的通过一条线路,每次发送一位将该数据放送出去。 串行通信采用两种方式:同步方式和异步方式。同步传输数据时,一次传 送一个字节,而异步传输数据是一次传送一个数据块。 串口是计算机上一种非常通用设备串行通信的协议。大多数计算机包含两

个基于RS232 的串口。串口按位(bit)发送和接收字节。尽管比按字节(byte)的并行通信慢,但是串口可以在使用一根线发送数据的同时用另一根线接收数据。典型地,串口用于ASCII 码字符的传输。通信使用3 根线完成:(1)地线,(2)发送,(3)接收。由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。其他线用于握手,但是不是必须的。串口通信最重要的参数是波特率、数据位、停止位和奇偶校验。对于两个进行通行的端口,这些参数必须匹配: RS-232(ANSI/EIA-232 标准)是IBM-PC 及其兼容机上的串行连接标准。可用于许多用途,比如连接鼠标、打印机或者Modem,同时也可以接工业仪器仪表。用于驱动和连线的改进,RS-232 只限于PC 串口和设备间点对点的通信。 IBM PC 及其兼容机提供了一种有较强的硬件依赖性,但却比较灵活的串行口I/O 的方法,即通过INT 14 调用ROM BIOS 串行通信口的例行程序。该例行程序。该例行程序包括将串行口初始化为指定的字节结构和传输速率,检查控制器的状态,读写字符等功能。 14 号中断的功能总结如下: 串行口服务(Serial Port Service——INT 14H) 00H —初始化通信口03H —读取通信口状态 01H —向通信口输出字符04H —扩充初始化通信口 02H —从通信口读入字符 (1)、功能00H:初始化通信口 入口参数:AH=00H DX=初始化通信口号(0=COM1,1=COM2,……)

串口通讯设计之 V e r i l o g实现 Revised as of 23 November 2020

串口通讯设计之V e r i l o g实现 FPGA串口模块是将由RS-485发送过来的数据进行处理,提取出8位有效数据,并按异步串口通讯的格式要求输出到MAX3223的12脚。FPGA选用Xilinx公司的SpartanII系列xc2s50。此部分为该设计的主体。如上所述,输入数据的传输速率为700k波特率。为了使FPGA能够正确地对输入数据进行采样,提高分辨率能力和抗干扰能力,采样时钟必须选用比波特率更高的时钟,理论上至少是波特率时钟的2倍。 1 串口通信基本特点随着多微机系统的应用和微机网络的发展,通信功能越来越显得重要。串行通信是在一根传输线上一位一位地传送信息.这根线既作数据线又作联络线。串行通信作为一种主要的通信方式,由于所用的传输线少,并且可以借助现存的电话网进行信息传送,因此特别适合于远距离传送。在串行传输中,通信双方都按通信协议进行,所谓通信协议是指通信双方的一种约定。约定对数据格式、同步方式、传送速度、传送步骤、纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。异步起止式的祯信息格式为:每祯信息由四部分组成: 位起始位。 ~8位数据位。传送顺序是低位在前,高位在后.依次传送。c.一位校验位,也可以没有。d.最后是1位或是2位停止位。 FPGA(Field Pmgrammable Gate Array)现场可编程门阵列在数字电路的设计中已经被广泛使用。这种设计方式可以将以前需要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活性。本文详细介绍了已在实际项目中应用的基于FPGA的串口通讯设计。 本设计分为硬件电路设计和软件设计两部分,最后用仿真验证了程序设计的正确性。 2 系统的硬件设计 本方案的异步串行通信的硬件接口电路图如图1所示,主要由四部分组成:RS-485数据发送模块、FPGA 串口模块、MAX3223和DB9。各部分功能简述如下: RS-485数据发送模块是将前续电路的数据发送到FPGA,供本电路处理,亦即本电路的输入。RS485是符合RS-485和RS-4225串口标准的低功耗半双工收发器件,有和5V两种,在本设计中选用了的器件SP3485。 在本设计中。485的7脚和8脚与前端信号相连接,用于接收输入的数据。数据格式是这样的:一帧数据有25位,报头是16个高电平和1个低电平,接下来是 8位有效的数据。传输速率为700k波特率。2脚是使能端,与FPGA的I/O口相连,由FPGA提供逻辑控制信号。1脚和4脚也与FPGA相连,由 FPGA对输入数据进行处理。 FPGA串口模块是将由RS-485发送过来的数据进行处理,提取出8位有效数据,并按异步串口通讯的格式要求输出到MAX3223的12脚。FPGA选用Xilinx公司的Spartan II系列xc2s50。此部分为该设计的主体。如上所述,输入数据的传输速率为700k波特率。为了使FPGA能够正确地对输入数据进行采样,提高分辨率能力和抗干扰能力,采样时钟必须选用比波特率更高的时钟,理论上至少是波特率时钟的2倍。在本设计中选用4倍于波特率的时钟,利用这种4倍于波特率的接收时钟对串行数据流进行检测和定位采样,接收器能在一个位周期内采样4次。如果没有这种倍频关系,定位采样频率和传送波特率相同,则在一个位周期中,只能采样一次,分辨率会差。比如,为了检测起始位下降沿的出现,在起始位的前夕采样一次之后,下次采样要到起始位结束前夕才进行。而假若在

摘要 进入21世纪之后,数字化浪潮正在席卷全球,数字信号处理器DSP(Digital Signal Processor)正是这场数字化革命的核心,无论在其应用的广度还是深度方面,都在以前所未有的速度向前发展。数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。 DSP可以代表数字信号处理技术(Digital Signal Processing),也可以代表数字信号处理器(Digital Signal Processor)。前者是理论和计算方法上的技术,后者是指实现这些技术的通用或专用可编程微处理器芯片。 本文就是就是基于DSP原理及应用编写设计的同步串口通信在TMS320C643上实现。其集成开发环境为CCS,工作平台是SEED-DTK 。CCS 是TI公司推出的用于开发DSP芯片的集成开发环境,它采用Windows风格界面,集编辑、编译、链接、软件仿真、硬件调试以及实时跟踪等功能于一体,极大地方便了DSP芯片的开发与设计,是目前使用最为广泛的DSP开发软件之一。SEED-DTK(DSP Teaching Kit)是一套可以满足大学本科、研究生和教师科研工作的综合实验设备。SEED-DTK 是我公司在总结以往产品的基础上,以独特的多DSP 结构、强大的DSP 主板功能、丰富的外围实验电路、精心设计的实验程序、精湛的产品工艺形成的高性能产品。 关键字:同步串口通信 DSP CCS SEED-DTK

目录 一.功能描述 ---------------------------------------------------------- 3二.概要设计 ---------------------------------------------------------- 3 2.1 McBSP 介绍------------------------------------------------- 3 2.2 设计目的------------------------------------------------------ 4 2.3 设计概要------------------------------------------------------ 4三.详细设计 ---------------------------------------------------------- 4 3.1 实验程序功能与结构说明 -------------------------------- 4 3.2 程序流程图 ---------------------------------------------------- 5四.调试过程及效果 ------------------------------------------------- 5 4.1 实验准备------------------------------------------------------ 5 4.2 调试过程及效果 -------------------------------------------- 6 4.2.1 创建源文件 -------------------------------------------- 6 4.2.2 创建工程文件 ----------------------------------------- 7 4.2.2 设置编译与连接选项 -------------------------------- 8 4.2.3 工程编译与调试 ------------------------------------ 10 五.存在问题 -------------------------------------------------------- 12 六. 心得-------------------------------------------------------------- 12 七.参考文献 -------------------------------------------------------- 12 附录(源程序) ----------------------------------------------------- 13

几种串行通信接口标准详解 在数据通信、计算机网络以及分布式工业控制系统中,经常采用串行通信来交换数据和信息。1969年,美国电子工业协会(EIA)公布了RS-232C作为串行通信接口的电气标准,该标准定义了数据终端设备(DTE)和数据通信设备(DCE)间按位串行传输的接口信息,合理安排了接口的电气信号和机械要求,在世界范围内得到了广泛的应用。但它采用单端驱动非差分接收电路,因而存在着传输距离不太远(最大传输距离15m)和传送速率不太高(最大位速率为20Kb/s)的问题。远距离串行通信必须使用Modem,增加了成本。在分布式控制系统和工业局部网络中,传输距离常介于近距离(<20m=和远距离(>2km)之间的情况,这时RS-232C(25脚连接器)不能采用,用Modem又不经济,因而需要制定新的串行通信接口标准。 1977年EIA制定了RS-449。它除了保留与RS-232C兼容的特点外,还在提高传输速率,增加传输距离及改进电气特性等方面作了很大努力,并增加了10个控制信号。与RS-449同时推出的还有RS-422和RS-423,它们是RS-449的标准子集。另外,还有RS-485,它是RS-422的变形。RS-422、RS-423是全双工的,而RS-485是半双工的。 RS-422标准规定采用平衡驱动差分接收电路,提高了数据传输速率(最大位速率为10Mb/s),增加了传输距离(最大传输距离1200m)。 RS-423标准规定采用单端驱动差分接收电路,其电气性能与RS-232C几乎相同,并设计成可连接RS-232C和RS-422。它一端可与RS-422连接,另一端则可与RS-232C连接,提供了一种从旧技术到新技术过渡的手段。同时又提高位速率(最大为300Kb/s)和传输距离(最大为600m)。 因RS-485为半双工的,当用于多站互连时可节省信号线,便于高速、远距离传送。许多智能仪器设备均配有RS-485总线接口,将它们联网也十分方便。 串行通信由于接线少、成本低,在数据采集和控制系统中得到了广泛的应用,产品也多种多样 一.RS-232-C详解 串行通信接口标准经过使用和发展,目前已经有几种。但都是在RS-232标准的基础上经过改进而形成的。所以,以RS-232C为主来讨论。RS-323C标准是美国EIA(电子工业联合会)与BELL等公司一起开发的1969年公布的通信协议。它适合于数据传输速率在0~20000b/s范围内的通信。这个标准对串行通信接口的有关问题,如信号线功能、电器特性都作了明确规定。由于通行设备厂商都生产与RS-232C制式兼容的通信设备,因此,它作为一种标准,目前已在微机通信接口中广泛采用。 在讨论RS-232C接口标准的内容之前,先说明两点: 首先,RS-232-C标准最初是远程通信连接数据终端设备DTE(Data Terminal Equipment)与数据通信设备DCE(Data Communication Equipment)而制定的。因此这个标准的制定,并未考虑计算机系统的应用要求。但目前它又广泛地被借来用于计算机(更准确的说,是计算机接口)与终端或外设之间的近端连接标准。显然,这个标准的有些规定及和计算机系统是不一致的,甚至是相矛盾的。有了对这种背景的了解,我们对RS-232C 标准与计算机不兼容的地方就不难理解了。 其次,RS-232C标准中所提到的“发送”和“接收”,都是站在DTE立场上,而不是站在DCE的立场来定义的。由于在计算机系统中,往往是CPU和I/O设备之间传送信息,两者都

1. OLED只能写入,不能读出。4线串行模式:D0——串行时钟线CLK,D1——串行数据线DA TA,P/S——模式选择、高为并行、低为串行。 并行模式需要使用全部数据及控制脚,串行模式只需要CLK、DA TA、RES、DC、CS共5个控制脚(WR、RD不用了)。 2.最常用配置方式: 3.同步串行通讯:时钟线、数据线,通过时钟保持数据同步。异步串行通讯:只有一根数据线,通过波特率保证数据同步。无线通信一般均为异步串行通信(一根天线)。 4.串行总线分三类:单总线(1—Wire)、SPI总线、I2C总线。单总线:用一根线数据收发和时钟信号,可以提供电源。SPI总线3根或4根线组成,数据收发,器件选择,时钟信号。I2C总线,两根线,数据收发,时钟信号。单总线特点:一、单总线芯片通过一根信号线传递控制信号、地址信号、数据信号。二、每个单总线芯片都有全球唯一序列号,当多个单总线芯片挂在一根总线上,根据不同序列号选择访问。三、单总线芯片在总线上可以获得电源。SPI:同步串行外设接口。SPI总线一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效的从机选择线SS。系统主机与从设备串行方式,高位在前,低位在后。SPI从设备MISO与系统主机MOSI相连,SPI从设备MOSI与系统主机MISO相连。SPI从设备用独立的片选信号控制信号使能端。片选无效时输出高阻态以不影响其他SPI设备工作。 1.OLED串行通信SPI 4—wire:CS低电平,同步时钟上升沿有效,传送8位数据。SPI 3 —wire:CS低电平,同步时钟上升沿有效,传送D/C共9位数据。 2.OLED4线串行SPI方式。一、使用的信号线有:CS(OLED片选信号)、RET(硬件复 位OLED)、DC(命令/数据标志(0:读写命令,1:读写数据))、SCLK(串行时钟线,D0信号线作为串行时钟线)、SDIN(串行数据线,D1信号线作为串行数据线)。二、模块的D2需要悬空,其他引脚可以接到GND。三、在此模式下,只能往模块写数据而不能读数据。四、在此模式下,每个数据长度均为8位,在SCLK的上升沿,数据从SDIN 移入到SSD1306,并且高位在前。DC线还是用作命令或数据的标志线。写操作时序:

1 绪论 1.1 研究背景 通信是指不同的独立系统利用线路互相交换数据,它的主要目的是将数据从一端传送到另一端,实现数据的交换。在现代工业控制中,通常采用计算机作为上位机与下层的实时控制与监测设备进行通讯。现场数据必须通过一个数据收集器传给上位机,同样上位机向现场设备发命令也必须通过数据收集器。串行通信因其结构简单、执行速度快、抗干扰能力强等优点,已被广泛应用于数据采集和过程控制等领域。 计算机与外界的信息交换称为通信。基本的通信方式有并行通信和串行通信两种。串行通信是指一条信息额各位数据被逐位按顺序传送的通信方式。串行通信的特点是:数据位传送,按位顺序进行,最少只需要一根传输线即可完成,成本低但传送速度快,串行通信的距离可以从几米到几千米。 随着计算机技术尤其是单片微型机技术的发展,人们已越来越多地采用单片机来对一些工业控制系统中如温度、流量和压力等参数进行监测和控制。PC机具有强大的监控和管理能力,而单片机则具有快速及灵和的控制特点,通过PC 机的RS-232串行接口与外部设备进行通信,是许多测控系统中常用的一种通信解决方案。而随着USB接口技术的成熟和使用的普及,由于USB 接口有着 RS-232(DB-9)串口无法比拟的优点,RS-232(DB-9)串口正在逐步地为USB 接口所替代。而在现在的大多数笔记本电脑中,出于节省物理空间和用处不大等原因,RS-232(DB-9)串口已不再设置,这就约束了基于RS-232(DB-9)串口与PC 机联络的单片机设备的使用围。当前USB接口逐步取代RS-232(DB-9)串口已是大势所趋,单片机同计算机的USB通信在实际工作中的应用围也将越来越广。本文所介

课程设计 课程名称_电子技术综合设计与实训 题目名称基于VHDL的串行同步通信SPI设计学生学院_ 自动化____________ 专业班级_电子信息科学与技术____ 学号__3107001554__________ 学生姓名____陈振添_____________ 指导教师____蔡述庭__________ 2009年12 月21 日

广东工业大学课程设计任务书 题目名称基于VHDL的串行同步通信SPI设计 学生学院自动化 专业班级电子信息科学与技术 姓名陈振添 学号3107001554 一、课程设计的内容 设计一个同步串行通讯SPI 二、课程设计的要求与数据 设计要求包括: 1.深入了解串行通信的方案内容和协议,思考设计方法。 2.设计串行通信方案,并写好传输程序VHDL。 3.下载到DE2板调试,检测其可行性。 三、课程设计应完成的工作 1. 利用VHDL语言编程实现SPI; 2. 利用DE2板对所设计的思想进行验证; 3. 总结VHDL设计结果,撰写课程设计报告。

四、课程设计进程安排 五、应收集的资料及主要参考文献 [1] PIC单片机原理及应用(第3版)北京航天航空大学出版社 [2] 黄智伟,王彦·FPGA系统设计与实践[M]·北京:电子工业出版社,2005 发出任务书日期:年月日指导教师签名: 计划完成日期:年月日基层教学单位责任人签章:主管院长签章:

摘要 本设计是用Quartus作为开发环境,以DE2板为硬件平台实现的SPI同步串行通讯。设计过程方便。根据接收和发送两个主要部分实现了SPI的基本功能。此外,该设计还实现了波特率发生器,数码管显示的功能。用DE2板实现具有电路简洁,开发周期短的优点。充分利用了EDA设计的优点。开发过程用了VHDL硬件描述语言进行描述,从底层设计,分模块进行,充分提高了设计者的数字逻辑设计的概念。 关键词:SPI,同步串行通讯,Quartus,DE2板,VHDL硬件描述语言。

------分隔线---------------------------- 这里所讲的同步传输和异步传输不同于VC 串口编程时的同步和异步,这里只讲串口硬件层传输的两种模式,有关VC 串口编程的同步模式和异步模式我将另外写一篇文章。 这里所讲的同步和异步是从硬件层级来讲的。首先要知道什么串行传输,串行传输是指数据的二进制代码在一条物理信道上以位为单位按时间顺序逐位传输的方式。串行传输时,发送端逐位发送,接收端逐位接受,同时,还要对所接受的字符进行确认,所以收发双方要采取同步措施(即判断什么时候有数据,数据是什么,什么时候结束传输)。 同步措施有两种,一种在传输的每个(帧)数据前(数据可能是5~8位)加一个起始位,后面加一位校验位及一位或两位的停止位组成一帧数据,这各方式称为异步传输;另一种是在一次传输(可能是多个字节)前加同步字节,可能不止一个字节,最后加校验字节或代表结束标志的字节,这种方式称为同步传输方式。 异步传输 异步传输将比特分成小组进行传送,小组可以是8位的1个字符或更长。发送方可以在任何时刻发送这些比特组,而接收方从不知道它

们会在什么时候到达。一个常见的例子是计算机键盘与主机的通信。按下一个字母键、数字键或特殊字符键,就发送一个8比特位的ASCII 代码。键盘可以在任何时刻发送代码,这取决于用户的输入速度,内部的硬件必须能够在任何时刻接收一个键入的字符。 异步传输存在一个潜在的问题,即接收方并不知道数据会在什么时候到达。在它检测到数据并做出响应之前,第一个比特已经过去了。这就像有人出乎意料地从后面走上来跟你说话,而你没来得及反应过来,漏掉了最前面的几个词。因此,每次异步传输的信息都以一个起始位开头,它通知接收方数据已经到达了,这就给了接收方响应、接收和缓存数据比特的时间;在传输结束时,一个停止位表示该次传输信息的终止。按照惯例,空闲(没有传送数据)的线路实际携带着一个代表二进制1的信号,异步传输的开始位使信号变成0,其他的比特位使信号随传输的数据信息而变化。最后,停止位使信号重新变回1,该信号一直保持到下一个开始位到达。例如在键盘上数字“1”,按照8比特位的扩展ASCII编码,将发送“00110001”,同时需要在8比特位的前面加一个起始位,后面一个停止位。 异步传输的实现比较容易,由于每个信息都加上了“同步”信息,因此计时的漂移不会产生大的积累,但却产生了较多的开销。在上面的例子,每8个比特要多传送两个比特,总的传输负载就增加25%。对于数据传输量很小的低速设备来说问题不大,但对于那些数据传输量很大的高速设备来说,25%的负载增值就相当严重了。因此,异步传输常用于低速设备。

RS-485串行接口标准 1、平衡传输 RS-485数据信号采用差分传输方式,也称作平衡传输,它使用一对双绞线,将其中一线定义为A,另一线定义为B,通常情况下,发送驱动器A、B之间的正电平在+2~+6V,是一个逻辑状态,负电平在-2~6V,是另一个逻辑状态。另有一个信号地C,在RS-485中还有一“使能”端,而在RS-422中这是可用可不用的。“使能”端是用于控制发送驱动器与传输线的切断与连接。当“使能”端起作用时,发送驱动器处于高阻状态,称作“第三态”,即它是有别于逻辑“1”与“0”的第三态。 接收器也作与发送端相对的规定,收、发端通过平衡双绞线将AA与BB对应相连,当在收端AB之间有大于+200mV的电平时,输出正逻辑电平,小于-200mV时,输出负逻辑电平。接收器接收平衡线上的电平范围通常在200mV至6V之间。 2、RS-485电气规定 由于RS-485是从RS-422基础上发展而来的,所以RS-485许多电气规定与RS-422相仿。如都采用平衡传输方式、都需要在传输线上接终接电阻等。RS-485可以采用二线与四线方式,二线制可实现真正的多点双向通信,而采用四线连接时,与RS-422一样只能实现点对多的通信,即只能有一个主(Master)设备,其余为从设备,但它比RS-422有改进,无论四线还是二线连接方式总线上可多接到32个设备。 RS-485与RS-422的不同还在于其共模输出电压是不同的,RS-485是-7V至+12V之间,而RS-422在-7V至+7V之间,RS-485接收器最小输入阻抗为12k剑 鳵S-422是4k健; 旧峡梢运礡S-485满足所有RS-422的规范,所以RS-485的驱动器可以用在RS-422网络中应用。 RS-485与RS-422一样,其最大传输距离约为1219米,最大传输速率为10Mb/s。平衡双绞线的长度与传输速率成反比,在100kb/s速率以下,才可能使用规定最长的电缆长度。只有在很短的距离下才能获得最高速率传输。一般100米长双绞线最大传输速率仅为1Mb/s RS-485需要2个终接电阻,其阻值要求等于传输电缆的特性阻抗。在矩距离传输时可不需终接电阻,即一般在300米以下不需终接电阻。终接电阻接在传输总线的两端。 在MCU之间中长距离通信的诸多方案中、RS-485因硬件设计简单、控制方便、成本低廉等优点广泛应用于工厂自动化、工业控制、小区监控、水利自动报测等领域、但RS-485总线在抗干扰、自适应、通信效率等方面仍存在缺陷、一些细节的处理不当常会导致通信失败甚至系统瘫痪等故障、因此提高RS-485总线的运行可靠性至关重要、 1 RS-485接口电路的硬件设计

三、SPI是英文Serial Peripheral Interface的缩写,中文意思是串行外围设备接口,SPI是Motorola公司推出的一种同步串行通讯方式,是一种三线同步总线,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 SPI概述 SPI:高速同步串行口。3~4线接口,收发独立、可同步进行. SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB 的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如AT91RM9200. SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI 和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT或INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。 SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。 (1)SDO –主设备数据输出,从设备数据输入 (2)SDI –主设备数据输入,从设备数据输出 (3)SCLK –时钟信号,由主设备产生 (4)CS –从设备使能信号,由主设备控制 其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。 接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO 线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。 要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。 在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。 最后,SPI接口的一个缺点:没有指定的流控制,没有应答机制确认是否接收到数据。 AT91RM9200的SPI接口主要由4个引脚构成:SPICLK、MOSI、MISO及/SS,其中SPICLK是整个SPI总线的公用时钟,MOSI、MISO作为主机,从机的输入输出的标志,MOSI是主机的输出,从机的输入,MISO 是主机的输入,从机的输出。/SS是从机的标志管脚,在互相通信的两个SPI总线的器件,/SS管脚的电平低的是从机,相反/SS管脚的电平高的是主机。在一个SPI通信系统中,必须有主机。SPI总线可以配置成单主单从,单主多从,互为主从。 SPI的片选可以扩充选择16个外设,这时PCS输出=NPCS,说NPCS0~3接4-16译码器,这个译码器是需要外接4-16译码器,译码器的输入为NPCS0~3,输出用于16个外设的选择。 [编辑本段] SPI协议举例

┊┊┊┊┊┊┊┊┊┊┊┊┊装┊┊┊┊┊订┊┊┊┊┊线┊┊┊┊┊┊┊ 摘要 虚拟仪器是现代计算机技术同仪器技术深层次结合的全新概念仪器,实质是利用计算机显示器的显示功能模拟传统仪器的控制面板,以多种形式表达输出测量结果,利用计算机强大的软件功能实现信号数据的运算、分析和处理,完成各种测试功能的一种计算机仪器系统。 本文介绍了利用LabVIEW语言来实现上、下位机之间通信的方法,并从软、硬件两个方面阐述了设计思想。从实现PC机PC机之间的串口通信出发,先实现双PC机之间的数据发送、返还和接收,进而设计了以PC机作为上位机,以飞思卡尔8位单片机作为下位机的基于labview软件的串口通信系统。经过实验调试,系统达到了预期的通信目标。 应用先进的虚拟仪器软件LABVIEW,大大降低了串口通讯复杂程度,减小了软件设计的工作量,能够大大降低投资成本。在实际应用中有巨大的使用价值。 关键词:虚拟仪器;Labview ;串口通信;单片机

┊┊┊┊┊┊┊┊┊┊┊┊┊装┊┊┊┊┊订┊┊┊┊┊线┊┊┊┊┊┊┊ Design of the serial communication system Based on LabVIEW Abstract Virtual instrument is the modern computer technology combined with the instrumentation of the new concept of deep-level instruments,in real terms is the use of analog computer monitors display control panel,traditional instruments,in various forms to express the output measurements,using computer software features to achieve a strong signal Operation data, analysis and processing,to complete a variety of testing capabilities of a computer instrument system This article describes the use of LabVIEW to implement the language, the next method of communication between the crew and from the software and hardware are two aspects of the design. PC-PC, from the implementation of serial communication between the departure, the first to achieve double the data between the PC, send and return, receive, and then designed a PC, as the host computer to Freescale 8-bit microcontroller based on a lower machine LabVIEW software serial communication system. After experimental debugging, the system achieved the desired communication goals. The application of advanced virtual instrument software LabVIEW, greatly reduces the complexity of serial communication, reduce the workload of the software design can greatly reduce the investment cost. In practice, there is tremendous value in use. Keywords: virtual instrument; Labview; serial communication; microcontroller

第9章串行接口及串行通信技术 U 难点 ?串行通信的四种工作方式 @要求 掌握: ?串行通信的控制寄存器 ?串行通信的工作方式0和方式1 了解: ?串行通信的基础知识 ?串行通信的工作方式2和方式3 9.1 串行通信的基础知识 9.2 MCS-51单片机串行通信的控制寄存器 9.3 MCS-51单片机串行通信工作方式 9.1 串行通信的基础知识 串行数据通信要解决两个关键技术问题,一个是数据传送,另一个是数据转换。所谓数据传送就是指数据以什么形式进行传送。所谓数据转换就是指单片机在接受数据时,如何把接收到的串行数据转化为并行数据,单片机在发送数据时,如何把并行数据转换为串行数据进行发送。 9.1.1 数据传送 单片机的串行通信使用的是异步串行通信,所谓异步就是指发送端和接收端使用的不是同一个时钟。异步串行通信通常以字符(或者字节)为单位组成字符帧传送。字符帧由发送端一帧一帧地传送,接收端通过传输线一帧一帧地接收。 1. 字符帧的帧格式 字符帧由四部分组成,分别是起始位、数据位、奇偶校验位、停止位。如图9.1所示: 1)起始位:位于字符帧的开头,只占一位,始终位逻辑低电平,表示发送端开始发送一帧数据。 2)数据位:紧跟起始位后,可取5、6、7、8位,低位在前,高位在后。 3)奇偶校验位:占一位,用于对字符传送作正确性检查,因此奇偶校验位是可选择的,共有三种可能,即奇偶校验、偶校验和无校验,由用户根据需要选定。 4)停止位:末尾,为逻辑“1”高电平,可取1、1.5、2位,表示一帧字符传送完毕。 图9.1 字符帧格式 异步串行通信的字符帧可以是连续的,也可以是断续的。连续的异步串行通信,是在一个字符格式的停止位之后立即发送下一个字符的起始位,开始一个新的字符的传送,即帧与帧之间是连续的。而断续的异步串行通信,则是在一帧结