1 引言 数字下变频DDC(digital down lonvwrsionl作为系统前端A/D转换器与后端通用DSP器件间的桥梁,通过降低数据流的速率,将低速数据送给后端通用DSP器件处理,其性能的优劣将对整个软件无线电系统的稳定性产生直接影响。采用专用DDC器件完成数字下变频,虽具有抽取比大、性能稳定等优点,但价格昂贵,灵活性不强,不能充分体现软件无线电的优势。FPGA工艺发展迅速,处理能力大大增强,相对于ASIC,DSP,其具有吞吐量高、开发周期短、可实现在线重构诸多优势。基于这些优点,FPGA在软件无线电的研发中具有重要作用。 2 数字下变频系统 数字下变频器在软件无线电系统中完成的功能结构如图1所示,其中包括直接数字频率合成器DDS(direct digital synthesizer)、数字混频器、FIR滤波器、抽取等模块。原始模拟中频信号经A/D转换器带通采样后得到数字中频信号,输入DDC后先与DDS产生的两路正交本振信号相乘(数字混频),将数字中频搬移到基带。混频后得到的数据率和采样率一致,后级FIR滤波器要达到该处理速率。硬件实现相当困难,因此首先通过抽取模块大大降低数据速率,然后使用高阶FIR低通滤波器对整个信道整形滤波。滤波输出的两路正基带信号交由下一级DSP器件进行处理。 2.1 混频器的FPGA实现 数字混频器将原始采样信号与查找表生成的正、余弦波形分别相乘,最终得到两路互为正交的信号。由于输入信号的采样率较高,因此要求混频器的处理速度大于等于信号采样率。单通道的数字下变频系统需要两个数字混频器.也就是乘法器。XC2V1000器件内嵌64个18×18位硬件乘法器,其最高工作频率为500 MHz,因此采用硬件乘法器完全能够满足混频器的设计要求。使用Xilinx公司的Multiplier IP核可以轻松实现硬件乘法器的配置。该设计中采用两路14位的输入信号,输出信号也为14位。图2为混频器的结构图。

2005 年 2 月 JOURNAL OF CIRCUITS AND SYSTEMS February , 2005 文章编号:1007-0249 (2005) 01-0123-04 数字下变频及抽取的FPGA 实现* 侯永宏, 侯春萍, 曹达仲, 戴居丰 (天津大学 电子信息工程学院,天津 300072) 摘要:在FPGA 上实现了对高频窄带数字信号的下变频和取样率转换,由于完全避免了需要大量逻辑资源的乘法器和数字振荡器,其结构大为简化,再加上采用了流水处理结构,使其处理速度超过100M 样点每秒,此外它还具有结构简单,重配置能力强的优点,具有广阔的应用前景。 关键词:积分梳状滤波器;抽取;现场可编程门阵列(FPGA ) 中图分类号:TN911.25 文献标识码:A 1 导言 全数字接收机的目标是设计一个支持多制式、多模式的,灵活、开放的通用数字接收机,它的发展趋势是将宽带A/D 尽可能靠近天线端,以简化接收机的模拟电路,而将接收机的各种功能用软件来实现。这样就对数字信号处理器(DSP )带来了巨大的处理压力。 现场可编程门阵列(FPGA ),能实现高速运算,且具有很强的重新配置能力,因此在全数字接收机中常用FPGA 配合DSP 工作。FPGA 负责对前端高速中频或射频信号进行处理,DSP 负责低速基带信号的处理[1]。 用FPGA 实现一个乘法器会消耗大量的逻辑资源,例如用Spartan Xilinx 系列实现一个16位并行乘法器需要213个CLB (Configurable Logic Block )[2];采用串行乘法器可以减少所需逻辑资源,但处理速度会急剧下降。所以如何减少乘法器的数目和提高处理速度是目前数字信号处理IC 设计的一个主要课题。 2 数字下变频 所谓下变频就是将信号从较高的频带搬移到较低的频带,以利于信号的分析与处理。如果数字带通信号为: s c s l s nT f nT x nT x π2cos )()(= (1) 其中:T s 为采样频率。 数字下变频实际上就是将上述信号乘以一个本地载波,然后通过一个带通或低通滤波器,即可以得到下变频后的信号。如果本地载波的频率与信号载波相等,得到的就是低通基带信号。 s o s b nT f nT x t x π2cos )()(= (2) 取c o f f =,如果c s f f 4=,且不考虑相位误差的话,有: L L 4 3πcos \cos π \2πcos \ cos0π2cos π2cos ==s c s o nT f nT f 此时本地载波信号的取值实际上是:1、0、-1、0、1。这样混频器就可以避免复杂的振荡器和乘法器,而用简单的组合逻辑和取反电路实现。具体实现为:1)将输入信号每隔2个取2补码,形成一个新的数据流;2)将新数据流每隔一个置0,所得输出就是混频后的信号。在上面提到的及后面的电路设计中,假定数模转换器的输出用2的补码表示。 3 防混迭滤波 混频后的有用信号频谱搬移到零频附近,相对于信号频率来讲,采样率非常高,因此可以通过抽 * 收稿日期:2003-12-08 修订日期:2004-05-05

用FPGA实现数字下变频 杨力生,谭晓衡,杨士中 (重庆大学通信工程学院,重庆 400044) 摘要:在接收信号的数字化、软化的实现中,数字下变频起着重要的作用。本文首先介绍了数字下变频的组成结构,然后详细分析了数字下变频的工作原理,描述了在实现数字下变频时,设计方案所采用的高效滤波器——CIC滤波器和多相抽取滤波器的结构和原理。最后,用通过Simulink对数字下变频的性能进行了仿真。在仿真的基础上使用Insight公司的FPGA开发系统,用测试电路实测了数字下变频的性能。 关键词:数字下变频器;FPGA;CIC数字滤波器;多相滤波器 Realize Digital Downconversion by FPGA YANG Li-sheng, TAN Xiao-heng, YANG Shi-zhong (Communication Engineering School, Chongqing University, Chongqing400044, China) Abstract: Digital downcoversion plays a key role in the digitized and software-oriented process of the received signal. First, the architecture of the digital downconvertor (DDC) is introduced.Then the operational principle of DDC is analysed.At the same time, the efficient structure of digital filter is described in which DDC is adopted.Finally, the performance simulation results of the DDC is given by Simulink, and on this base,the perfomance of DDC is tested with the FPGA devoloping system of Insight corp. Keywords:Digital downcovertor; FPGA;CIC digital filter;Polyphase filter 一、序言 在数字接收机中,数字下变频器(DDC)一般执行信道的访问功能。DDC接收经过高速采样的中频信号,将所需的频带下变为基带。现代基站收发器为了支持多载波环境或实现下变频,以便将很多窄带信道组合成一个宽带的数字信号,常常需要大量的DDC。DDC通常位于信号处理链的前端,靠近A/D,一般要求DDC 支持100 MSPS以上的采样率。 数字下变频由数字振荡器、数字乘法器、数字滤波器三部分组成,其组成的系统框图如图1所示。

收稿日期:2004-09-16 第22卷 第12期 计 算 机 仿 真 2005年12月 文章编号:1006-9348(2005)12-0303-04 用M ATLAB 在FPGA 芯片中实现数字下变频设计 贾雪琴,李强,王旭,李景宏 (东北大学信息科学与工程学院,辽宁沈阳110004) 摘要:数字下变频在接收系统的数字化和软件化过程中起到了至关重要的作用。该文研究了高倍抽取的数字下变频设计,重点分析了基于级联积分梳状滤波器和级联半带滤波器的多级抽样频率算法。采用最新的设计软件Systemgenerator 软件可以方便地在MAT LAB 中实现算法仿真并可生成FPG A 芯片的下载文件,简化了设计流程,降低了开发成本和周期。提出了一种基于计算机IS A 总线的系统验证方法。用Systemgenerator 设计和仿真基于FPG A 芯片的的硬件设计有效地验证了算法并降低了试验成本,是一种好方法。 关键词:数字下变频;半带滤波器;级联积分梳状滤波器;现场可编程门阵列中图分类号:T N998 文献标识码:A Rea liza tion of D ig ita l D own Conversion i n FPGA Ch ip by Usi ng M ATLAB J I A Xue -qin,L IQ iang,WAN G Xu,L I J ing -hong (College of Infor mation Science &Engineering,Northeastern University,Shenyang L iaoning 110004,China )ABSTRACT:D igital down conversion p lays a key role in the digitized and soft ware -oriented p rocess of the receiver system.This paper studies the high deci m ation ratio of digital down converter,and especially analyzes the multi -stage deci mation algorithm based on C I C filter and HB filter . It w ill reduce the cost and the development ti m e by using the newest Systemgenerator which can si m ulate the design and download it to FPG A easily .And verifying the design w ith an IS A bus of computer w ill save lots of money,effectively .U singMAT LAB design and si mulation hardware p rojects based on FPG A is a good method .KEYWO RD S:DDC;HB -filter;C I C -filter;FPG A 1 序言 现代数字信号处理中,为了满足系统的性能而使用可变 频率来实现数字信号处理的过程,称为多速率数字信号处理(multirate digital signal p rocessing ),而其中以数字下变频(DDC )技术应用最为广泛。它将采样后的数据传输速率降低到最小,使信号接收系统的数字化和软件化得以实现。与早期的由分立式器件组合而成的下变频器相比,目前市场上出现了多种集成下变频器(如:AD6620,HSP50124b 等),广泛应用于无线电通讯和数据采集等领域。 本文提出一种采用FPG A 器件来实现数字下变频的方案。与集成器件相比,FPG A 芯片在速度和灵活性上都有很大的提高。并且,使用FPG A 器件实现的下变频器可以更加方便的采用软件方法对射频链路上引入的干扰进行有效的补偿,同时也可将存储器、控制器等外围器件集成到芯片内部,提 高了整个系统的稳定性和集成度。 本设计选用Xilinx 公司的Spartan3系列芯片为设计对象,采用Xilinx 公司与M athwork 公司合作的Systemgenerator 软件进行设计与仿真。该软件的使用,使得Xilinx 公司提供的IPcore 和M atlab 中的si m ulink 工具得到完美结合,令计算结果可以更加直观的表现出来。并且,可以将设计模型直接编译成可在FPG A 器件中布局布线的网表文件。成功地解决了算法研究人员和硬件实现工程师之间的工作协调问题,使得用户能够以最快的速度将他们的算法得到硬件实现。 2 数字下变频原理与实现 如图1所示,数字下变频器主要由数字混频器和数字滤波器组两部分组成。混频器部分由DDS 和两路乘法器组成,数字滤波器部分主要由级联积分梳状滤波器(以下称C I C 滤波器),半带滤波器(以下称HB 滤波器)和后级F I R 滤波器组成的链路构成。2.1 混频器 软件无线电系统接收到的数据是对自然信号调制产生 — 303—

*收稿日期:2006-09-11 文章编号:1008-8652(2007)02-84-06一种基于FPGA 的数字下变频方法 涂维政 刘书明 (西安电子科技大学 西安 710071) =摘要> 提出用FPGA 器件实现一个完整的数字下变频系统的方法,给出VerilogH DL 语言 的描述,实现高效的运算结构,减小了运算量,提高了系统性能。本系统已经在某型气象雷达的数字接收系统中得到采用,参数得到验证,性能优良。 关键词:FPGA ;VerilogH DL;欠采样技术;数字下变频;多抽样率系统 中图分类号:T N74211 文献标识码:A A Method of Digital Down Converting Based on FPGA T u Weizheng Liu Shuming (X idian Univ ersity ,X i .an,710071) Abstract :A method of using FPGA device to realize dig ital dow n converting system is presented,and the descr iptio n of Verilog H DL language is g iv en so that the hig h efficiency operational structure is fu-l filled,and the oper and is reduced and the system perform ance is enhanced.T his m ethod has been adopted in the digital receiving subsy stem of a certain m eteoro logical radar,and the specificatio ns are verified and the perfo rmance is perfect. Keywords :FPGA;Verilog H DL;under sampling techno log y;digital dow n converter;multiple sam -pling rate system 随着数字技术的飞速进步和发展,FPGA 器件因其高速、可编程、模块化的特点而被大量采用。同时,诸如数字下变频等一系列新的数字信号处理方法的提出,为降低系统成本提供了可能,相关的多抽样率系统理论,更是大大的降低了数字系统的运算量,明显的提升了系统性能。 本文论述数字下变频技术的一种FPGA 实现方法,用比较低的系统成本,实现比较高的谱分辨率的数字接收系统,完成对气象信号的有效处理。实际的系统选用48M H z 时钟对60MH z 的雷达中频信号采样,然后经过FPGA 的数字下变频及其滤波处理,得到信号的包络和相位信息。 1 欠采样技术 为了降低对ADC 器件的要求,对于低通、带通信号,可以用带通信号的采样方法,在低于奈奎斯特采样率时进行数模转换:只要采样率不低于两倍信号带宽f h -f l ,时域的采样就不会导致信号频谱的混叠,如公式(1)所示: 2f h N +1[f S [2f l N (1)其中,N 为自然数,且1[N [f l f h -f l 。84

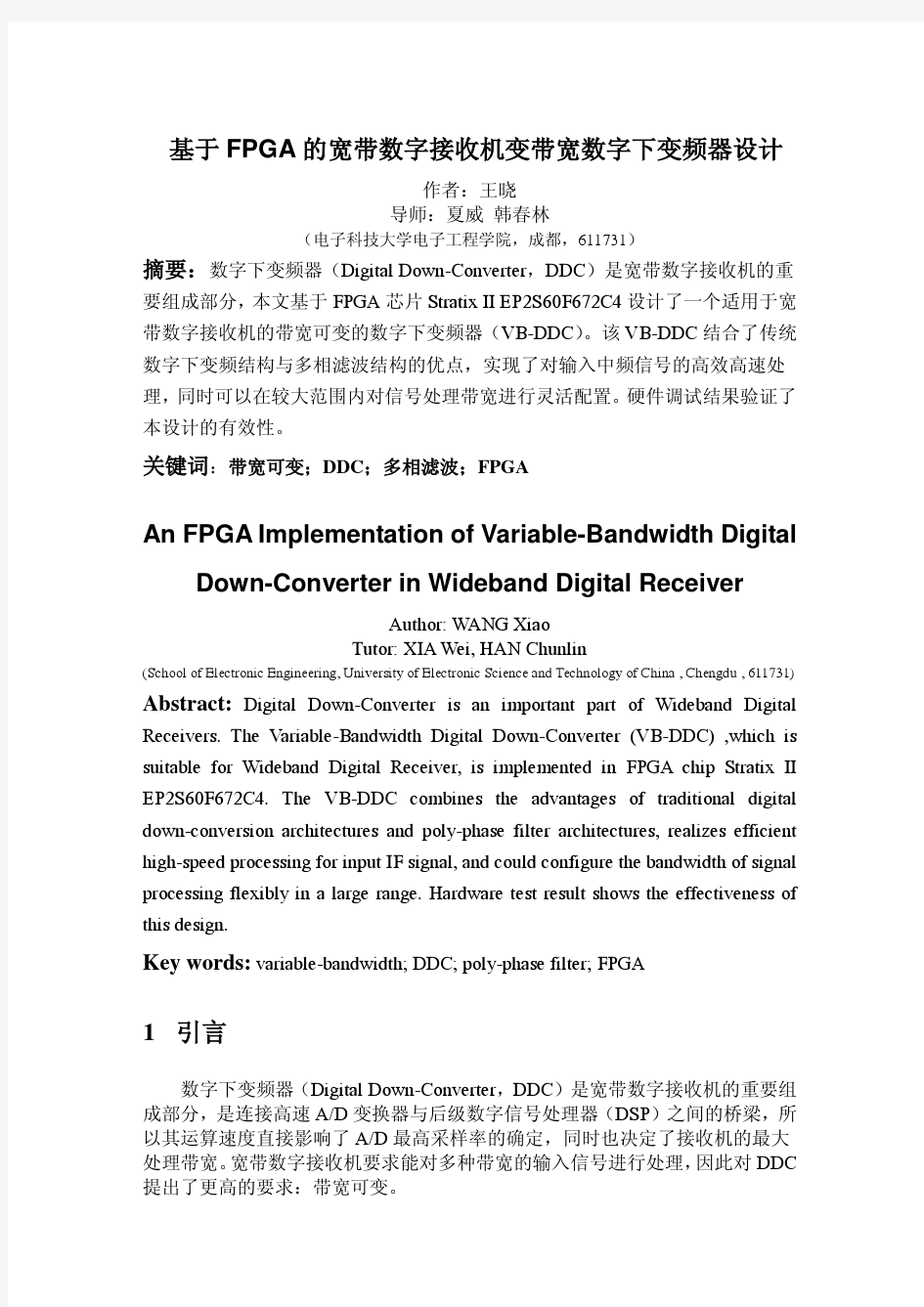

数字中频的基本原理和FPGA 的实现 1.基本原理 数字中频主要分两部分,数字上变频(DUC )和数字下变频(DDC)。它们的主要功能是相反,但原理和实现的方法是十分相似。在R8905项目中由于采用了零中频技术,数字上变频和下变频有一些差别,数字上变频没有了NCO 模块。另外为了降低输出信号的峰均比又加入了削峰模块CFR,而CGC 模块的引入则是补偿削峰所引起的功率损失。 图1 数字上变频模块框图 在数字下变频中RSSI 模块是信号的功率检测模块,它配合AGC 电路将信号的输出功率稳定在一定范围内。 图2 数字下变频模块框图 在DDC 和DUC 中主要使用3种滤波器分别是RRC,HB 和CIC ,它们个自有个自的特点。 RRC 滤波器一般来讲阶数比较多,多用于低频处。由于它的阶数比较多,所以可以得到比较锐利的带通特性,但它所用的乘法器比较多。CIC 滤波器不需要乘法器,但它的带内不是很平坦,适合用在高频处。而HB 滤波器的特性正好在它们之间,它有约一半的系数是0可以讲乘法器的个数减少一半。 削峰模块CFR 实际上也是一组滤波器,它的功能是将CDMA 信号中的峰值信号减小一些,以减小输出信号的峰均比,使射频功率放大器的效率更高。削峰的模块框图如图3

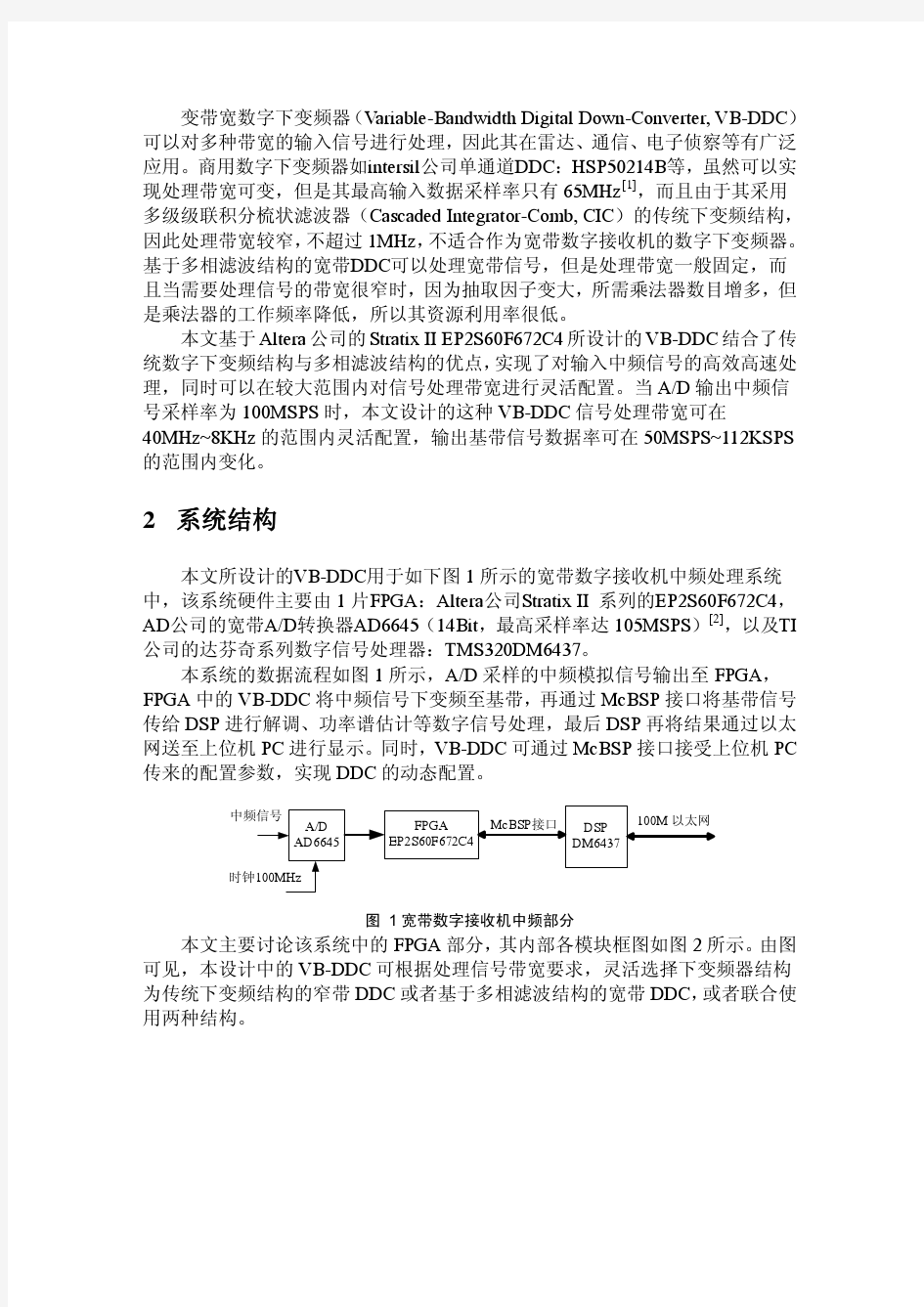

图3 单级削峰示意图 削峰的原理是这样的一个复信号(I,Q)如果它的模大于某个门限,就将其减去这个门限得到一个复信号(dI,dQ),否则(dI,dQ)=(0,0)。将(dI,dQ)送到fir滤波器中,fir滤波器是一个低通滤波器将峰值限定在一定的带宽内,防止影响临道。将原信号(I,Q)减去滤波后的信号(fir_i,fir_q)就得到了削峰的值。如果有必要这这样的削峰可以连续做几次,在R8905设计中削峰用了两次。 2.滤波器的设计 由于在滤波的同时还有内插和抽取,所以充分利用这一特性可以减少FPGA使用的资源。 另外滤波器的系数一般都是对称的,可以将头和尾的数相加再乘滤波器的系数,这样可以大大减少乘法器的使用。以R8905中的上变频RRC为例来说明: 设a(n)为RRC滤波器的系数而x(n)为3.84M输入数据则考虑了内插后的滤波器的数学表达式为 y=a(0)*x(n)+a(1)*0+a(2)*x(n-1)+.........+a(n-1)*0+a(0)*x(0) =a(0)*(x(n)+x(0)) +a(2)*( x(n-1)+x(1))...... 其FPGA实现的逻辑框图如下