在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。

访问CP15寄存器的指令

MCR ARM寄存器到协处理器寄存器的数据传送

MRC 协处理器寄存器到ARM寄存器的数据传送

MCR指令和MRC指令只能在处理器模式为系统模式时执行,在用户模式下执行MCR 指令和MRC指令将会触发未定义指令的异常中断。

MCR指令

MCR指令将ARM处理器的寄存器中的数据传送到协处理器寄存器中。如果协处理器不能成功地执行该操作,将产生未定义的指令异常中断。

指令语法格式

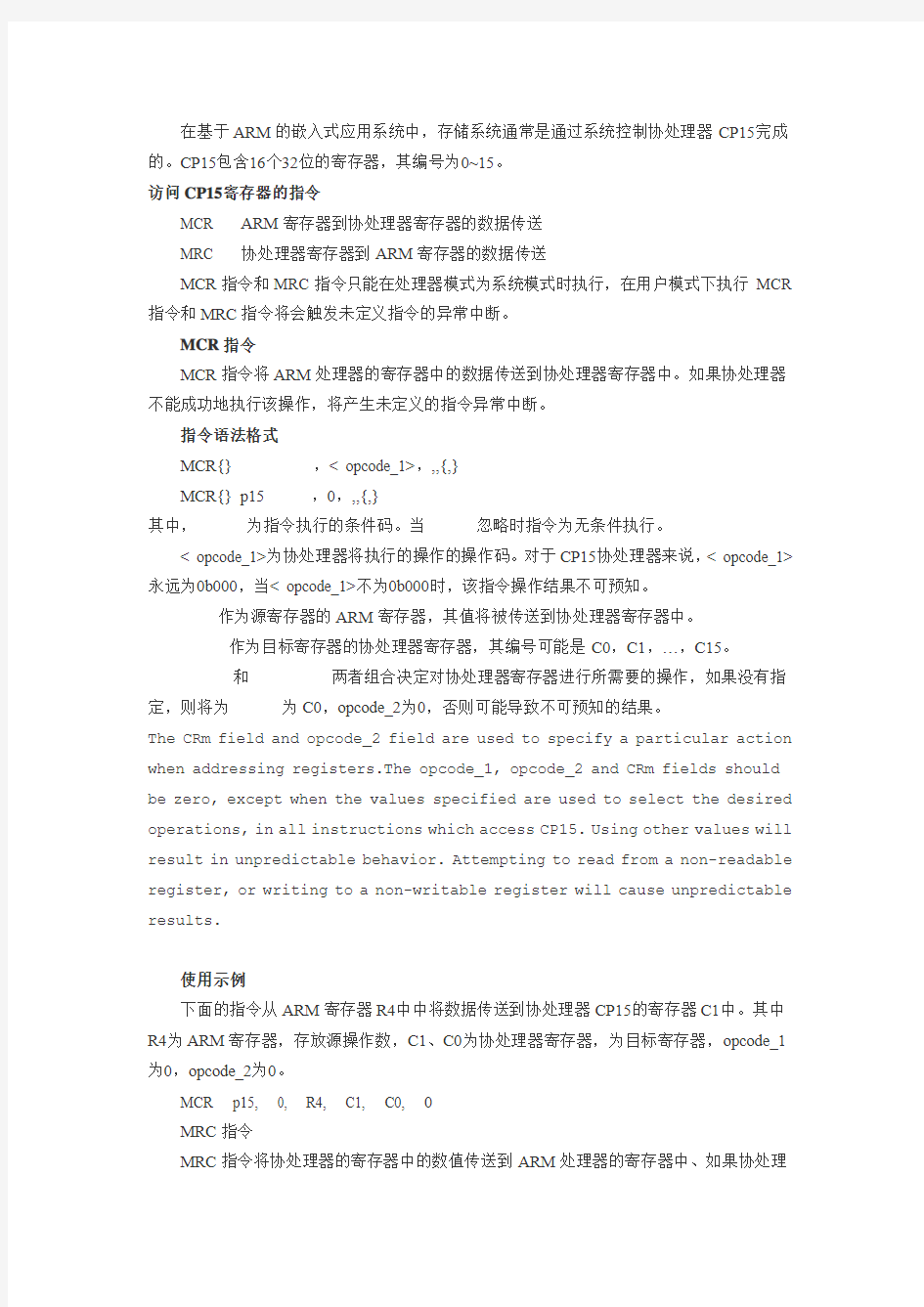

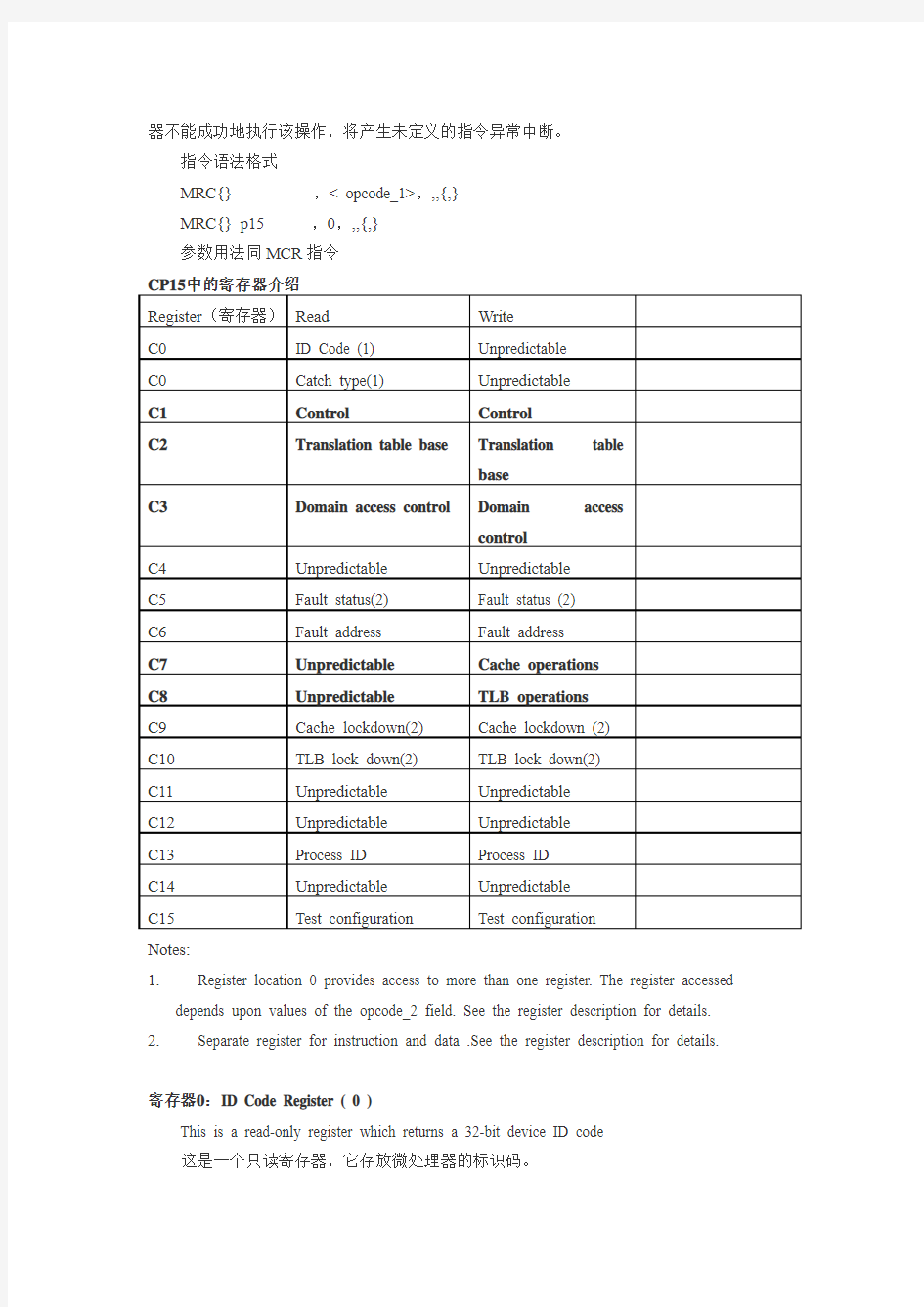

MCR{ ,< opcode_1>, MCR{ 其中, < opcode_1>为协处理器将执行的操作的操作码。对于CP15协处理器来说,< opcode_1>永远为0b000,当< opcode_1>不为0b000时,该指令操作结果不可预知。 The CRm field and opcode_2 field are used to specify a particular action when addressing registers.The opcode_1, opcode_2 and CRm fields should be zero, except when the values specified are used to select the desired operations, in all instructions which access CP15. Using other values will result in unpredictable behavior. Attempting to read from a non-readable register, or writing to a non-writable register will cause unpredictable results. 使用示例 下面的指令从ARM寄存器R4中中将数据传送到协处理器CP15的寄存器C1中。其中 R4为ARM寄存器,存放源操作数,C1、C0为协处理器寄存器,为目标寄存器,opcode_1为0,opcode_2为0。 MCR p15, 0, R4, C1, C0, 0 MRC指令 MRC指令将协处理器的寄存器中的数值传送到ARM处理器的寄存器中、如果协处理 器不能成功地执行该操作,将产生未定义的指令异常中断。 指令语法格式 MRC{ ,< opcode_1>, MRC{ 参数用法同MCR指令 CP15中的寄存器介绍 Register(寄存器)Read Write C0ID Code (1)Unpredictable C0Catch type(1)Unpredictable C1Control Control C2Translation table base Translation table base C3Domain access control Domain access control C4Unpredictable Unpredictable C5Fault status(2)Fault status (2) C6Fault address Fault address C7Unpredictable Cache operations C8Unpredictable TLB operations C9Cache lockdown(2)Cache lockdown (2) C10TLB lock down(2)TLB lock down(2) C11Unpredictable Unpredictable C12Unpredictable Unpredictable C13Process ID Process ID C14Unpredictable Unpredictable C15Test configuration Test configuration Notes: 1.Register location 0 provides access to more than one register. The register accessed depends upon values of the opcode_2 field. See the register description for details. 2.Separate register for instruction and data .See the register description for details. 寄存器0:ID Code Register ( 0 ) This is a read-only register which returns a 32-bit device ID code 这是一个只读寄存器,它存放微处理器的标识码。 The ID code register is accessed by reading CP15 register 0 with the opcode_2 field set to any value other than 1(the CRm field should be zero when reading). For example: MRC p15, 0, Rd, C0, C0, 0 ID Code内容如下: Register bits Function Value [31:24]Implementor0x41(‘A’,表示Arm公司) [23:20]Specification revision0x1 [19:16]Architecture version(4T)0x2(ARM体系版本4T) [15:4]Part number0x920 [3:0]Layout revision0x0 寄存器0:Cache type register ( 1 ) This is a read-only register which contains information about the size and architecture of the caches, allowing operating systems to establish how to perform such operations as cache cleaning and lockdown. 这个只读寄存器包含了高速缓存的大小和类型。 The cache type register is accessed by reading CP15 register 0 with the opcode_2 field set to 1.for example: MRC p15, 0, Rd, C0, C0, 1; returns cache details The format of cache type register (寄存器的数据格式如下) Register bits Function Value [31:29]Reserved000 [28:25]Cache type (缓存类型)0110 [24]Harvard/Unified1(defines Harvard cache) [23:21]Reserved000 [20:18]Data Cache size(数据缓存大小)101(defines 16KB) [17:15]Data Cache associativity110(defines 64 way) [14]Reserved0 [13:12]Data Cache words per line10(defines 8 words per line) [11:9]Reserved000 [ 8:6]Instruction Cache size(指令缓存大小)101(defines 16KB) [5:3]Instruction Cache Associativity110(defines 64 way) [2]Reserved0 [1:0]Instruction Cache per line10(defines 8 words per line) 寄存器1:Control register 对该寄存器读写指令如下: MRC p15, 0, Rd, c1, c0, 0 ; read control register MCR p15, 0, Rd, c1, c0, 0 ; write control register 该寄存器功能如下表 Registe bits Name Function Value 31iA bit Asynchronous clock select见时钟模式表 30nF bit notFastBus select见时钟模式表 29:15-Reserved Read = Unpredictable Write = should be zero 14RR bit Round robin replacement0 = Random replacement 1 = Round robin replacement 13V bit Base location of exception register(异常寄存器基地址)0 = Low address = 0x0000 0000 1 = High address = 0xFFFF 0000 12I bit Instruction cache enable0 = Instruction cache disable 1 = Instruction cache enable 11:10-Reserved Read = 00 Write = 00 9R bit ROM protection见图1 8S bit System protection见图1 7 B bit Big-endian/little-endian0 = Little-endian operation 1 = Big-endian operation 6:3- Reserved Read = 1111 Write = 1111 2 C bit Data cache enable0 = data cache disable 1 = data cache enable 1 A bit Alignment fault enable Data address alignment fault checking (地址对齐检查) 0 = 禁用地址对齐检查功能 1 = 使能地址对齐检查功能 0M bit MMU enable0 = MMU disable 1 = MMU enable 时钟模式表 Clocking mode(时钟模式)iA nF Fastbus mode (快速总线模式)00 Reserved10 Synchronous (同步模式)01 Asynchronous (异步模式)11 寄存器2:Translation Table Base(TTB) Register Register bits Function 31:14 Pointer to first level translation table base . Read /write 13:0 Reserved Read = Unpredictable Write = Should be zero 访问C2寄存器指令如下: MRC p15, 0, Rd, C2, C0, 0 ; Read TTB register MCR p15, 0, Rd, C2, C0, 0 ; Write TTB register 该寄存器存放第一级转换表基地址。写入时,位[13:0]必须为0,读出时,位[13:0]的值不可预知。 寄存器3:Domain Access Control Register 寄存器3是可读写的域访问控制寄存器,分为16组,每组占用2个位 访问该寄存器的指令如下: MRC p15, 0, Rd, C3, C0, 0 ; Read domain 15:0 access permissions MCR p15, 0, Rd, C3, C0, 0 ; Read domain 15:0 access permissions Interpreting Access Control Bits in Domain Access Control Register 寄存器4:保留 对该寄存器的读写会产生不可预料的结果。 寄存器5:Fault Status Register 寄存器6:Fault Address Register 寄存器7:Cache Operations 该寄存器是只写寄存器,用于管理指令缓存和数据缓存。 对该寄存器的写操作所实现的功能,是通过MCR指令中的opcode_2和CRm两者的组合来选择的,具体组合如下。 寄存器8:TLB Operations Register 8 is a write-only register used to manage the translation lookaside buffer(TLBs),the instruction TLB and the data TLB. Five TLB operations are defined and the function to be performed is selected by the opcode_2 and CRm fields in the MCR instruction used to write CP15 register 8.Writing other opcode_2 or CRm values id unpredictable. Reading from CP15 register 8 is unpredictable. Function Data instruction Invalidate TLB(s) SBZ MCR p15,0,Rd,c8,c7,0 Invalidate I TLB SBZ MCR p15,0,Rd,c8,c5,0 Invalidate I TLB single entry (using MVA) MVA format MCR p15,0,Rd,c8,c5,1 Invalidate D TLB SBZ MCR p15,0,Rd,c8,c6,0 Invalidate D TLB single entry (using MVA) MVA format MCR p15,0,Rd,c8,c6,1 以下是MMU的初始化实例: ARM访问CP15寄存器的指令(中文版详解) 访问CP15寄存器指令的编码格式及语法说明如下: 31 28 27 24 23 21 2 19 16 15 12 11 8 7 5 4 3 0 cond 1 1 1 0 opcod e_1 L cr n rd 1 1 1 1 opcod e_2 1 crm 说明: 指令说明语法格式 mcr 将ARM处理器的寄存器中的数据 写到CP15中的寄存器中mcr{ mrc 将CP15中的寄存器中的数据读 到ARM处理器的寄存器中mcr{ 4.1.2 CP15寄存器介绍 CP15的寄存器列表如表4-1所示。 表4-1 ARM处理器中CP15协处理器的寄存器 寄存器编号基本作用在MMU中的作用在PU中的作用 0 ID编码(只读)ID编码和cache类型 1 控制位(可读写)各种控制位 2 存储保护和控制地址转换表基地址Cachability的控制位 3 存储保护和控制域访问控制位Bufferablity控制位 4 存储保护和控制保留保留 5 存储保护和控制内存失效状态访问权限控制位 6 存储保护和控制内存失效地址保护区域控制 7 高速缓存和写缓存高速缓存和写缓存控 制 8 存储保护和控制TLB控制保留 9 高速缓存和写缓存高速缓存锁定 10 存储保护和控制TLB锁定保留 11 保留 12 保留 13 进程标识符进程标识符 14 保留 15 因不同设计而异因不同设计而异因不同设计而异 CP15的寄存器C0 CP15中寄存器C0对应两个标识符寄存器,由访问CP15中的寄存器指令中的 opcode_2编码对应的标识符号寄存器 0b000 主标识符寄存器 0b001 cache类型标识符寄存器 其他保留 1)主标识符寄存器 访问主标识符寄存器的指令格式如下所示: mrc p15, 0, r0, c0, c0, 0 ;将主标识符寄存器C0,0的值读到r0中 ARM不同版本体系处理器中主标识符寄存器的编码格式说明如下。 ARM7之后处理器的主标识符寄存器编码格式如下所示: 31 24 23 20 19 16 15 4 3 0 产品主编号处理器版本号 由生产商确定产品子编号ARM体系版本 号 位说明 位[3: 0] 生产商定义的处理器版本号 位[15: 4] 生产商定义的产品主编号,其中最高4位即位[15:12]可能的取值为0~7但不能是0或7 位[19: 16] ARM体系的版本号,可能的取值如下: 0x1 ARM体系版本4 0x2 ARM体系版本4T 0x3 ARM体系版本5 0x4 ARM体系版本5T 0x5 ARM体系版本5TE 其他由ARM公司保留将来使用 位[23: 20] 生产商定义的产品子编号,当产品主编号相同时,使用子编号来区分不同的产品子类,如产品中不同的高速缓存的大小等 位[31: 24] 生产厂商的编号,现在已经定义的有以下值: 0x41 =A ARM公司 0x44 =D Digital Equipment公司 0x69 =I intel公司 ARM7处理器的主标识符寄存器编码格式如下所示: 31 24 23 22 16 15 4 3 0 由生产商确定 A 产品子编号产品主编号处理器版本号 位说明 位[3: 0] 生产商定义的处理器版本号 位[15: 4] 生产商定义的产品主编号,其中最高4位即位[15:12]的值为0x7 位[22: 16] 生产商定义的产品子编号,当产品主编号相同时,使用子编号来区分不同的产品子类,如产品中不同的高速缓存的大小等 续表位说明 位[23] ARM7支持下面两种ARM体系的版本号: 0x0 ARM体系版本3 0x1 ARM体系版本4T 位[31: 24] 生产厂商的编号,现在已经定义的有以下值: 0x41 =A ARM公司 0x44 =D Digital Equipment公司 0x69 =I Intel公司 ARM7之前处理器的主标识符寄存器编码格式如下所示: 31 24 23 22 16 15 4 3 0 由生产商确定 A 产品子编号产品主编号处理器版本号 位说明 位[3: 0] 生产商定义的处理器版本号 位[15: 4] 生产商定义的产品主编号,其中最高4位即为[15:12]的值为0x7 位[22: 16] 生产商定义的产品子编号,当产品主编号相同时,使用子编号来区分 不同的产品子类,如产品中不同的高速缓存的大小等 位[23] ARM7支持下面两种ARM体系的版本号: 0x0 ARM体系版本3 0x1 ARM体系版本4T 位[31: 24] 生产厂商的编号,现在已经定义的有以下值: 0x41 =A ARM公司 0x44 =D Digital Equipment公司 0x69 =I intel公司 2)cache类型标识符寄存器 访问cache类型标识符寄存器的指令格式如下所示: mrc p15, 0, r0, c0, c0, 1 ;将cache类型标识符寄存器C0,1的值读到r0中 ARM处理器中cache类型标识符寄存器的编码格式如下所示: 31 29 28 25 24 23 12 11 0 0 0 0 属性字段S 数据cache相关属性指令cache相关属性 位说明 位[28: 25] 指定控制字段位[24: 0]指定的属性之外的cache的其他属性,详见表 4-2 位[24] 定义系统中的数据cache和指令cache是分开的还是统一的: 0 系统的数据cache和指令cache是统一的; 1 系统的数据cache和指令cache是分开的 位[23: 12] 定义数据cache的相关属性,如果位[24]为0,本字段定义整个cache 的属性 位[31: 24] 定义指令cache的相关属性,如果位[24]为0,本字段定义整个cache 的属性 其中控制字段位[28:25]的含义说明如下: 表4-2 cache类型标识符寄存器的控制字段位[28:25] cache内容清除方法cache内容锁定方法 编码cache类 型 0b0000 写通类型不需要内容清除不支持内容锁定 0b0001 写回类型数据块读取不支持内容锁定 0b0010 写回类型由寄存器C7定义不支持内容锁定 0b0110 写回类型由寄存器C7定义支持格式A 0b0111 写回类型由寄存器C7定义支持格式B 控制字段位[23:12]和控制字段位[11:0]的编码格式相同,含义如下所示: 11 9 8 6 5 3 2 1 0 0 0 0 cache容量cache相联特性M 块大小cache容量字段bits[8: 6]的含义如下所示: 编码M=0时含义(单位KB)M=1时含义(单位KB) 0b000 0.5 0.75 0b001 1 1.5 0b010 2 3 0b011 4 6 0b100 8 12 0b101 16 24 0b110 32 48 0b111 64 96 cache相联特性字段bits[5: 3]的含义如下所示: 编码M=0时含义M=1时含义 0b000 1路相联(直接映射)没有cache 0b001 2路相联3路相联 0b010 4路相联6路相联 0b011 8路相联12路相联 0b100 16路相联24路相联 0b101 32路相联48路相联 0b110 64路相联96路相联 0b111 128路相联192路相联 cache块大小字段bits[1: 0]的含义如下所示: 编码cache块大小 0b00 2个字(8字节) 0b01 4个字(16字节) 0b10 8个字(32字节) 0b11 16个字(64字节) CP15的寄存器C1 访问主标识符寄存器的指令格式如下所示: mrc p15, 0, r0, c1, c0{, 0} ;将CP15的寄存器C1的值读到r0中 mcr p15, 0, r0, c1, c0{, 0} ;将r0的值写到CP15的寄存器C1中CP15中的寄存器C1的编码格式及含义说明如下: 31 16 1 5 1 4 13 12 11 10 9 8 7 6 5 4 3 2 1 0 附加L 4 R R V I Z F R S B L D P W C A M 位说明 M 0:禁止MMU或者PU;1:使能MMU或者PU A 0:禁止地址对齐检查;1:使能地址对齐检查 C 0:禁止数据/整个cache;1:使能数据/整个cache W 0:禁止写缓冲;1:使能写缓冲 P 0:异常中断处理程序进入32位地址模式;1:异常中断处理程序进入26位地址模式 D 0:禁止26位地址异常检查;1:使能26位地址异常检查 L 0:选择早期中止模型;1:选择后期中止模型 B 0:little endian;1:big endian S 在基于MMU的存储系统中,本位用作系统保护 R 在基于MMU的存储系统中,本位用作ROM保护 F 0:由生产商定义 Z 0:禁止跳转预测功能;1:使能跳转预测指令 I 0:禁止指令cache;1:使能指令cache V 0:选择低端异常中断向量0x0~0x1c;1:选择高端异常中断向量0xffff0000~ 0xffff001c RR 0:常规的cache淘汰算法,如随机淘汰;1:预测性淘汰算法,如round-robin 淘汰算法 L4 0:保持ARMv5以上版本的正常功能;1:将ARMv5以上版本与以前版本处理器兼容,不根据跳转地址的bit[0]进行ARM指令和Thumb状态切换:bit[0] 等于0表示ARM指令,等于1表示Thumb指令 附加: CP15的寄存器C2 CP15中的寄存器C2保存的是页表的基地址,即一级映射描述符表的基地址。其编码格如下所示: 31 一级映射描述符表的基地址(物理地址) ?CP15的寄存器C3 CP15中的寄存器C3定义了ARM处理器的16个域的访问权限。 31 D1 5 D1 4 D1 3 D1 2 D1 1 D1 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 ?CP15的寄存器C5 CP15中的寄存器C5是失效状态寄存器,编码格式如下所示: 31 9 8 7 4 3 0 UNP/SBZP 0 域标识状态标识 其中,域标识bit[7:4]表示存放引起存储访问失效的存储访问所属的域。 状态标识bit[3:0]表示放引起存储访问失效的存储访问类型,该字段含义如表4-3所示(优先级由上到下递减)。 表4-3 状态标识字段含义 引起访问失效的原因状态标识域标识C6 终端异常(Terminal Exception)0b0010 无效生产商定义 中断向量访问异常(Vector Exception) 0b0000 无效有效 地址对齐0b00x1 无效有效 一级页表访问失效0b1100 无效有效 二级页表访问失效0b1110 有效有效 基于段的地址变换失效0b0101 无效有效 基于页的地址变换失效0b0111 有效有效 基于段的存储访问中域控制失效0b1001 有效有效 基于页的存储访问中域控制失效0b1101 有效有效 基于段的存储访问中访问权限控制失 效 0b1111 有效有效 基于页的存储访问中访问权限控制失 效 0b0100 有效有效 基于段的cache预取时外部存储系统 失效 0b0110 有效有效 基于页的cache预取时外部存储系统0b1000 有效有效 失效 基于段的非cache预取时外部存储系 0b1010 有效有效 统失效 ?CP15中的寄存器C6 CP15中的寄存器C5是失效地址寄存器,编码格式如下所示: 31 失效地址(虚拟地址) ?CP15中的寄存器C7 CP15的C7寄存器用来控制cache和写缓存,它是一个只写寄存器,读操作将产生不可预知的后果。 访问CP15的C7寄存器的指令格式如下所示: mcr p15, 0, ?CP15中的寄存器C8 CP15的C8寄存器用来控制清除TLB的内容,是只写寄存器,读操作将产生不可预知的后果。 访问CP15的C8寄存器的指令格式如下所示: mcr p15, 0, ?CP15中的寄存器C9 CP15的C9寄存器用于控制cache内容锁定。 访问CP15的C9寄存器的指令格式如下所示: mcr p15, 0, mrc p15, 0, 如果系统中包含独立的指令cache和数据cache,那么对应于数据cache和指令cache分别有一个独立的cache内容锁定寄存器, CP15的C9寄存器有A、B两种编码格式。编码格式A如下所示: 31 32-W 31-W cache组内块序号index 0 其中index表示当下一次发生cache未命中时,将预取的存储块存入cache中该块对应的组中序号为index的cache块中。此时序号为0~index-1的cache块被锁定,当发生cache 替换时,从序号为index到ASSOCIATIVITY的块中选择被替换的块。 编码格式B如下所示: 31 30 W W-1 L 0 cache组内块序号index 位说明 L=0 当发生cache未命中时,将预取的存储块存入cache中该块对应的组中序号为index的cache块中 续表位说明 L=1 如果本次写操作之前L=0,并且index值小于本次写入的index,本次写操作执行的结果不可预知;否则,这时被锁定的cache块包括序号为 0~index-1的块,当发生cache替换时,从序号为index到 ASSOCIATIVITY的块中选择被替换的块 CP15的寄存器C10 CP15的C10寄存器用于控制TLB内容锁定。 访问CP15的C10寄存器的指令格式如下所示: mcr p15, 0, mrc p15, 0, 如果系统中包含独立的指令TLB和数据TLB,那么对应于数据TLB和指令TLB分别有一个独立的TLB内容锁定寄存器, C10寄存器的编码格式如下: 31 30 32-W 31-W 32-2W 31-2W 1 0 可被替换的条目起始地址的base 下一个将被替换的条目地址 0 P victim 位说明 victim 指定下一次TLB没有命中(所需的地址变换条目没有包含在TLB中)时,从内存页表中读取所需的地址变换条目,并把该地址变换条目保存在TLB中地址 victim处 base 指定TLB替换时,所使用的地址范围,从(base)到(TLB中条目数-1);字段victim的值应该包含在该范围内 P 1:写入TLB的地址变换条目不会受使整个TLB无效操作的影响,一直保持有效; 0:写入TLB的地址变换条目将会受到使整个TLB无效操作的影响 CP15的寄存器C13 C13寄存器用于快速上下文切换FCSE。 访问CP15的C13寄存器的指令格式如下所示: mcr p15, 0, mrc p15, 0, C13寄存器的编码格式如下所示: 31 25 24 PID 0 其中,PID表示当前进程的所在的进程空间块的编号,即当前进程的进程标识符,取值为 0~127。 0:MVA(变换后的虚拟地址)= VA(虚拟地址),禁止FCSE(快速上下文切换技术),系统复位后PID=0; 非0:使能FCSE。 内外部环境和相关方要求识别控制程序 1.目的 识别公司质量/环境管理体系存在的,会影响到体系管理内外部环境因素和相关方要求。2.范围 本程序适用于在公司质量/环境管理体系活动中,识别内外部存在的机会和风险,及应对措施的建立和评价过程。 3.职责 3.1总经理:负责内外部环境和相关方要求管理所需资源的提供。 3.2 管理者代表:负责组织落实内外部环境和相关方要求的定期识别和评审。 3.3各部门:负责参与内外部环境和相关方要求识别和评审; 4.定义 4.1内部环境:企业内部环境,例如组织使命、资源、内部管理、内部绩效等。 4.2外部环境:例如法律、技术、竞争、市场、文化、社会和经济环境有关的因素等。 4.3相关方:人或组织,能影响组织的某个决策或活动,或被其影响,及认为自身会被其影响。如:客户、外部供方、行业组织等。 5.程序 5.1 公司内外部环境因素和相关方要求的识别对象 5.1.1 在分析外部环境因素对公司质量/环境体系的影响时:可考虑: a. 宏观经济因素:如汇率、国家经济、CPI指数、信贷; b. 市场竞争因素:如市场占有率、可替代产品、行业标杆企业状况、顾客趋势等; c. 社会因素:如本地就业数据、教育水平、工作时间、假期等; d. 政治因素:如政治稳定性、本地基础设施、政府公共服务等; e. 法规因素:如产品法规、有害物质法规、劳工法规等; f. 技术因素:如新科技、新技术、新材料、专利有效期等; 5.1.2 在分析内部环境因素对公司质量/环境体系的影响时:可考虑: a. 公司使命:如愿景、目标、义务; b. 公司资源:如:财务、人力、环境、基础设施、知识储备; c. 公司管理:如组织架构、决策过程; d. 公司运营绩效:产品先进性、生产交付能力、体系能力、客户评价、质量管理绩效、合规性等。 5.1.3 在分析相关方要求时,可考虑: ARM处理器中CP15协处理器的寄存器 注意: You can only access CP15 registers with MRC and MCR instructions in a privileged mode (只能在特权模式下,对cp15进行MRC,MCR操作)。 1.访问CP15寄存器的指令 访问CP15寄存器指令的编码格式及语法说明如下: 31 28 27 24 23 21 20 19 16 15 12 11 8 7 5 4 3 0 cond 1 1 1 0 opcode_1 L Cr n Rd 1 1 1 1 opcode_2 1 Cr m 说明: Opcode_1 :协处理器行为操作码,对于CP15来说,永远为0b000,否则结果未知。 Rd:处理器核心的寄存器名称,不能是r15/pc,否则,结果未知。 Crn:作为目标寄存器的协处理器寄存器名称,编号为C0~C15。 Crm:协处理器中附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将Crm设置为c0,否则结果未知。 Opcode_2 :提供附加信息,比如寄存器的版本号或者访问类型,用于区分同一个编号的不同物理寄存器,可以省略或者将其设置为0,否则结果未知。 指令语法格式说明: mcr :将ARM处理器的寄存器中的数据写到CP15中的寄存器中 mcr{ 数字电路与微处理器基础实验 实验1 单片机开发系统的使用 一.实验目的: 1. 熟悉实验环境。 2. 熟练掌握程序编写、调试、下载和运行的基本方法。 3. 掌握单片机I/O端口的控制和简单应用技术。 4. 掌握移位和软件延时程序的编写和应用。 二.实验设备: 1. PC机一台; 2. 51单片机实验装置一套。 三.实验内容: 1. 利用单片机及8个发光二极管等器件,制作一个单片机控制的流水灯系统。单片机的P3.0—P3.7接8个发光二极管,运行程序,则单片机控制8个发光二极管进行流水灯操作,流水灯从左到右依次点亮,反复显示。发光二极管的闪烁时间由延时函数控制。(流水灯编号从左到右依次为L1—L8) 2. 利用单片机及8个发光二极管等器件,制作一个单片机控制的发光二极管显示系统。单片机的P 3.0—P3.7接8个发光二极管,运行程序,则单片机控制高四位和第四位的发光二极管交替显示。 3. 利用单片机及8个发光二极管等器件,制作一个单片机控制的发光二极管显示系统。单片机的P3.0—P3.7接8个发光二极管,运行程序,则单片机控制奇数位和偶数位的发光二极管交替显示。 4. 选作题:利用单片机及8个发光二极管等器件,制作一个单片机控制的流水灯系统。单片机的P3.0—P3.7接8个发光二极管,运行程序,则单片机控制8个发光二极管进行流水灯操作,流水灯从右到左依次点亮,反复显示。 5. 选作题:按照下图改变流水灯的方式,编程实现。或者按照自己的设计,改变流水灯的方式,并编程实现。 四.实验报告要求: 1.写明实验名称,实验目的; 2.列出实验仪器名称、型号; 3.简述实验原理,画出本实验相关的电路原理图; 4.编程序清单(注释语句),调试结果及说明; 5. 实验分析和实验体会。 6. 注意实验报告格式,独立完成,避免雷同; 7. A4纸排版,左侧装订。并认真填写实验报告封皮。 “微处理器系统原理与嵌入式系统设计”第一章习题解答 1.1 什么是程序存储式计算机? 程序存储式计算机指采用存储程序原理工作的计算机。 存储程序原理又称“·诺依曼原理”,其核心思想包括: ●程序由指令组成,并和数据一起存放在存储器中; ●计算机启动后,能自动地按照程序指令的逻辑顺序逐条把指令从存储器中 读出来,自动完成由程序所描述的处理工作。 1.2 通用计算机的几个主要部件是什么? ●主机(CPU、主板、存); ●外设(硬盘/光驱、显示器/显卡、键盘/鼠标、声卡/音箱); 1.3 以集成电路级别而言,计算机系统的三个主要组成部分是什么? 中央处理器、存储器芯片、总线接口芯片 1.4 阐述摩尔定律。 每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。 1.5 讨论:摩尔定律有什么限制,可以使用哪些方式克服这些限制?摩尔定律还会持续多久?在摩尔定律之后电路将如何演化? 摩尔定律不能逾越的四个鸿沟:基本大小的限制、散热、电流泄露、热噪。具体问题如:晶体管体积继续缩小的物理极限,高主频导致的高温…… 解决办法:采用纳米材料、变相材料等取代硅、光学互联、3D、加速器技术、多核…… (为了降低功耗与制造成本,深度集成仍是目前半导体行业努力的方向,但这不可能永无止,因为工艺再先进也不可能将半导体做的比原子更小。用作绝缘材料的二氧化硅,已逼近极限,如继续缩小将导致漏电、散热等物理瓶颈,数量集成趋势终有终结的一天。一旦芯片上线条宽度达到纳米数量级时,相当于只有几个分子的大小,这种情况下材料的物理、化学性能将发生质的变化,致使采用现行工艺的半导体器件不能正常工作,摩尔定律也就要走到它的尽头了。业界专家预计,芯片性能的增长速度将在今后几年趋缓,一般认为摩尔定律能再适用10年左右,其制约的因素一是技术,二是经济。) 2.9如果GDT寄存器值为0013000000FFH,装人LDTR的选择符为0040H,试问装人描述符高速缓存的LDT描述符的起始地址是多少? 解:GDT寄存器的高32位和低16位分别为GDT的基址和段限,所以:GDT的基址=00130000H LDTR选择符的高13位D15~D3=000000001000B是该LDT描述符在GDT中的序号,所以: LDT描述符的起始地址= GDT的基址 十LDT描述符相对于GDT基址的偏移值 =00130000H+8×8=00130040H 2.10假定80486工作在实模式下,(DS)=1000H, (SS)=2000H, ( SI ) = El07FH, ( BX )=0040H, (BP) = 0016H,变量TABLE的偏移地址为0100H。请间下列指令的源操作数字段是什么寻址方式?它的有效地址(EA)和物理地址(PA)分别是多少? (1)MOV AX,[1234H ] (2) MOV AX, TABLE (3) MOV AX,[BX+100H] (4) MOV AX,TABLE[BPI[SI] 解:(1)直接寻址,EA=1234H , PA =(DS)×16+EA=11234H。 (2)直接寻址,EA= O100H,PA= (DS)×16+EA=10100H。 (3)基址寻址,EA=( EBX)+100H =0140H,PA= (DS) × 16+EA=10140H。 (4)带位移的荃址加变址寻址。(EA)= (BP)+[SI]十TABLE的偏移地址=0195H PA=(SS)×16+EA=20195H} 2.11下列指令的源操作数字段是什么寻址方式? (1)MOV EAX , EBX (2)MOV EAX,[ ECX] [EBX ] (3) MOV EAX,[ESI][EDX * 2] (4)MOV EAx,[ ESI*8] 解:(1)寄存器寻址。 (2)基址加变址寻址。 (3)基址加比例变址寻址。 (4)比例变址寻址。 2.12分别指出下列指令中源操作和目的操作数的寻址方式。 式表示出EA和PA。 (1)MOV SI,2100H (2)MOV CX, DISP[BX] (3) MOV [SI] ,AX (4)ADC AX,[BX][SI] (5)AND AX,DX (6) MOV AX,[BX+10H] (7) MOV AX,ES:[BX] (8) MOV Ax, [BX+SI+20H] (9) MOV [BP ].CX (10) PUSH DS 解:(1) 源操作数是立即数寻址;目的操作数是寄存器寻址。 (2)源操作数是基址寻址,EA=(BX)+DISP,PA=(DS)×16+(BX)+DISP 目的操作数是寄存器寻址。 (3)源操作数是寄存器寻址; 目的操作数是寄存器间接寻址,EA=(SI).PA=(DS) × 16十(SI)。 (4)操作数是基址加变址寻址,EA= (BX)+(SI).PA= (DS) × 16十(BX)+(SI) 目的操作数是寄存器寻址。 (5)源操作数和目的操作数均为寄存器寻址。 (6)源操作数是基址寻址,EA=(BX)+10H.PA= (DS) × 16十(BX)+10H 目的操作数是寄存器寻址。 (7)源操作数是寄存器间接寻.EA= (Bx).PA= (ES) × 16+(BX) 相关方控制程序 1.目的 对与公司质量、环境、职业健康安全有关的相关方施加影响,并进行必要的管理,确保体系有效运行。 2.范围 适用于公司相关方的管理工作。 3.职责 3.1企业运营中心和相关部门负责外来参观、联系业务人员的管理并施加影响。 3.2物资采购部负责对供应商的管理并施加影响。 3.3装备部负责对外承包方进行管理并施加影响。 3.4安全部负责对进入本公司的外来人员和车辆进行管理。 4.工作程序 4.1相关方分类 4.1.1 供应商:包括原材料和机配件等辅助材料供应商。 4.1.2 外承包方:包括建筑安装工程承包商、固体废弃物处理承包方、外加工单位。 4.1.3 运输方:包括运输公司等。 4.1.4 外来人员:来厂参观、联系业务等人员。 4.2对相关方的管理 各部门应及时识别本部门的相关方,建立各自主要相关方清单,并施加影响,对其信息交流应有相关记录,将公司 对环境、职业健康安全的要求通告相关方。 4.2.1 对供应商的管理 物资采购部每年对主要供应商进行合格供方评价的同时,应进行质量、环境、 职业健康安全方面的评价,在采购物料时,应优先采购通过 ISO9001、ISO14001、OHSMS18001认证企业生产的产品。在采 购过程中应向供应商索要: a.一般原材料、机配件产品说明书; b.劳保用品的“三证”(生产许可证、产品合格证、安全鉴定证); c.危险化学品、油料的安全技术说明书(MSDS)。 4.2.2 对外承包方的管理 a.装备部与施工单位的合同书中,应有保证其施工过程中避免或减 少环境影响以保证职业健康安全和包括对进入施工现场的人 员进行培训的承诺。通报公司环境、 安全方面的规定,并要求其执行; b.装备部在进行技改、基建安装工程等项目的同时,办理好“三同 在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。 访问CP15寄存器的指令 MCR ARM寄存器到协处理器寄存器的数据传送 MRC 协处理器寄存器到ARM寄存器的数据传送 MCR指令和MRC指令只能在处理器模式为系统模式时执行,在用户模式下执行MCR 指令和MRC指令将会触发未定义指令的异常中断。 MCR指令 MCR指令将ARM处理器的寄存器中的数据传送到协处理器寄存器中。如果协处理器不能成功地执行该操作,将产生未定义的指令异常中断。 指令语法格式 MCR{ “微处理器系统原理与嵌入式系统设计”第三章习题解答 3.1处理器有哪些功能?说明实现这些功能各需要哪些部件,并画出处理器的基本结构图。 处理器的基本功能包括数据的存储、数据的运算和控制等功能。其有5个主要功能:①指令控制②操作控制③时间控制④数据加工⑤中断处理。其中,数据加工由ALU 、移位器和寄存器等数据通路部件完成,其他功能由控制器实现。处理器的基本结构图如下: 寄存器组 控制器 整数单元 浮点单元 数据通路 处理器数据传送 到内存数据来自内存数据传送到内存指令来自内存 3.2处理器内部有哪些基本操作?这些基本操作各包含哪些微操作? 处理器基本操作有:取指令、分析指令、执行指令。 取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。 分析指令:对当前取得的指令进行分析,指出它要求什么操作,并产生相应的操作控制命令。 执行指令:根据分析指令时产生的“操作命令”形成相应的操作控制信号序列,通过运算器、存储器及输入/输出设备的执行,实现每条指令的功能,其中包括对运算结果的处理以及下条指令地址的形成。 3.3什么是冯·诺伊曼计算机结构的主要技术瓶颈?如何克服? 冯·诺伊曼计算机结构的主要技术瓶颈是数据传输和指令串行执行。可以通过以下方案克服:采用哈佛体系结构、存储器分层结构、高速缓存和虚拟存储器、指令流水线、超标量等方法。 3.5指令系统的设计会影响计算机系统的哪些性能? 指令系统是指一台计算机所能执行的全部指令的集合,其决定了一台计算机硬件主要性能和基本功能。指令系统一般都包括以下几大类指令。:1)数据传送类指令。(2)运算类指令 包括算术运算指令和逻辑运算指令。(3)程序控制类指令 主要用于控制程序的流向。 (4)输入/输出类指令 简称I/O 指令,这类指令用于主机与外设之间交换信息。 因而,其设计会影响到计算机系统如下性能: 数据传送、算术运算和逻辑运算、程序控制、输入/输出。另外,其还会影响到运算速度以及兼容等。 3.9某时钟速率为2.5GHz 的流水式处理器执行一个有150万条指令的程序。流水线有5段,并以每时钟周期1条的速率发射指令。不考虑分支指令和乱序执行带来的性能损失。 a)同样执行这个程序,该处理器比非流水式处理器可能加速多少? b)此流水式处理器是吞吐量是多少(以MIPS 为单位)? a.=51p T nm S T m n =≈+-串流水 速度几乎是非流水线结构的5倍。 b.2500M IPS p n T T =≈流水 3.10一个时钟频率为2.5 GHz 的非流水式处理器,其平均CPI 是4。此处理器的升级版本引入了5级流水。然而,由于如锁存延迟这样的流水线内部延迟,使新版处理器的时钟频率必须降低到2 GHz 。 (1) 对一典型程序,新版所实现的加速比是多少? (2) 新、旧两版处理器的MIPS 各是多少? (1)对于一个有N 条指令的程序来说: 非流水式处理器的总执行时间s N N T 990 106.1)105.2/()4(-?=??= 5级流水处理器的总执行时间s N N T 991 10)4(2)102/()15(-?+=?-+= 加速比=42.310 +=N N T T ,N 很大时加速比≈3.2 (2)非流水式处理器CPI=4,则其执行速度=2500MHz/4=625MIPS 。 5级流水处理器CPI=1,则其执行速度=2000 MHz /1=2000 MIPS 。 3.11随机逻辑体系结构的处理器的特点是什么?详细说明各部件的作用。 随机逻辑的特点是指令集设计与硬件的逻辑设计紧密相关,通过针对特定指令集进行 相关方管理控制程序 (ISO45001-2018/ISO14001/ISO9001) 1.0目的 对相关方施加影响,使其了解本公司的一体化管理体系方面的事宜,以促使其自觉保证产品质量、保护环境和减少职业健康安全风险。 2.0适用范围 适用于对本公司的职业健康安全环境绩效有关的或受其职业健康安全环境绩效影响的个人或团体,如物料供应商、外包商等相关方进行评估并对其施加影响。 3.0引用标准 3.1《质量管理体系要求》、 3.2《环境管理体系要求及使用指南》、 3.3《职业健康安全管理体系要求及使用指南》 4.0职责 4.1安委会、采购部、工程部、人事行政部负责组织有关部门对受其职业健康安全环境绩效影响的个人或团体相关方进行评估并对其施加影响。 4.2各部门参与相关方进行评估并对其施加影响。 5.0管理内容 5.1公司可望施加影响的相关方主要有: a) 提供产品外协外包服务的承包方; b) 提供物资供应商主要有油品、化学品、劳动保护用品、防护用品、有毒有害物资的供方; c) 为公司处理固体废弃物的承包方; d) 个人,组织的员工、顾客、访问者、临时工作人员、合同方人员; e) 合同方、有关政府部门。 5.2 与相关方的评估 5.2.1安委会负责组织各有关部门对相应相关方进行评估: 与公司的重要环境因素和健康安全风险相关联的,或可能造成重大环境污染、或重大健康安全事故,确定相关方环境、安全问题,制定出应重点施加影响的内容(其中供方可分为施加影响的单位和暂不施加影响的单位),填写“重点施加影响相关方一览表”; 5.3 对相关方的影响 5.3.1对需重点施加影响的相关方,由采购部对物资供应商、为公司处理固体废弃物的承包方等相关方施加影响主要通过以下方式: 5.3.1.1安委会负责对固体废弃物处置的承包方进行评估确认并施加影响,要求固体废弃物处置的承包方遵守中华人民共和国固体废物污染环境防治法,对建筑垃圾、生活垃圾处理符合法规要求。确保对垃圾的处理不会造成新的污染。 5.3.1.2采购部对为本公司提供产品的供方进行评价、审查、监督、管理并要求供方执行下述环保措施: a) 供方的评价:供方提供资料。 b) 组织有关生产单位参加,对供方的安全管理活动进行监督、检查评价,有条件的进行现场评价。 c) 对供方评价的内容: (1) 供方的环境状况及生产工艺 微控制器原理及应用答案 【篇一:单片机原理及应用课后完整答案】 txt>第一章 1. 为什么计算机要采用二进制数?学习十六进制数的目的是什么? 在计算机中,由于所采用的电子逻辑器件仅能存储和识别两种状态 的特点,计算机内部一切信息存储、处理和传送均采用二进制数的 形式。可以说,二进制数是计算机硬件能直接识别并进行处理的惟 一形式。十六进制数可以简化表示二进制数。 2. (1) 01111001 79h (2) 0.11 0.ch (3) 01111001.11 79.ch (4) 11101010.101 0ea.ah (5)01100001 61h (6) 00110001 31h 3. (1) 0b3h 4. (1)01000001b65 (2) 110101111b 431 (3)11110001.11b 241.75 (4)10000011111010b 8442 5. (1) 00100100 00100100 00100100(2) 10100100 11011011 11011100(3)1111 1111 1000 00001000 0001 (4)10000000 110000000 10000000 (5) 10000001 11111110 11111111(6)100101110 111010010111010011 6. 00100101b 00110111bcd 25h 7. 137 11989 8.什么是总线?总线主要有哪几部分组成?各部分的作用是什么?总线是连接计算机各部件之间的一组公共的信号线。一般情况下, 可分为系统总线和外总线。 系统总线应包括:地址总线(ab)控制总线(cb)数据总线(db)地址总线(ab):cpu根据指令的功能需要访问某一存储器单元或外 部设备时,其地址信息由地址总线输出,然后经地址译码单元处理。地址总线为16位时,可寻址范围为216=64k,地址总线的位数决定 了所寻址存储器容量或外设数量的范围。在任一时刻,地址总线上 的地址信息是惟一对应某一存储单元或外部设备。 相关方管理控制程序文档编制序号:[KK8UY-LL9IO69-TTO6M3-MTOL89-FTT688] 目的 采取适宜方式,使相关方的HSE行为符合或适合于本所要求,保持和改善本所的HSE绩效。 适用范围 本程序用于对本所外部的相关方,在其活动、产品和服务过程中,产生的环境影响和存在的环境因素、危险源与风险进行的管理。 职责 管理者代表负责制订本程序,并监督实施情况。 各部门负责:识别、更新本部门的相关方的环境因素和危险源,并列出清单;管理本部门对口的相关方;对不符合管理要求的本部门相关方采取纠正和预防措施。 工作程序 各部门应识别出本部门与相关方有关的相关环境因素和危险源,列出清单,评价其重要性,并按要求及时更新。将重要变动及时通报给相关方。 本所HSE的主要相关方包括顾客/业主,为本所提供服务和产品的单位或个人,进入本所的外来人员: a)外来参访人员、配合本所或帮助本所完成服务的委托机构、分包服务方 b)各部门涉及的可能对本所HSE管理造成影响的其它组织和个人。主要相关方包括工 程建设单位/产品顾客和业主、供方和承包方等。 各部门应及时针对不同的相关方,采取不同的手段施加影响: a)将有关的HSE要求传达至工程/产品的业主或顾客,以自身行为影响其HSE绩效。 b)对参与服务或委委托单位,传达HSE要求,通过沟通和协议,使其配合HSE的管 理。 a)应从绿色环保、节约资源能源等施加影响,垃圾处理、化粪池清运等单位应有明确的 书面规定,签订环境管理协议或要求供方、承包方做出环境承诺。 b)优先选择绿色环保、节能高效的产品,负责采购的各归口部门应保存相关证明文件的 复印件或原件。 c)优先选择取得ISO14001、GB/T28001及其他HSE产品或体系认证、管理良好、无HSE 违法表现的供方、承包方。通过招标方式进行选择时,将HSE要求作为评分标准之一,列入评标准则。 d)对非一次性的长期合作的供方、承包方,归口管理部门负责建立供方、承包方HSE表 现档案,作为以后继续合作及付款安排的参考依据之一。 e)对可能存在重大HSE风险的供方、承包方,应要求其提供符合法律、法规要求的资质 证明文件和从业人员资格证明文件,各归口管理部门负责保存相关文件的复印件。 f)对HSE表现良好的供方、承包方,在结算付款方面给与优先安排。 g)对在HSE方面方面表现恶劣,或发生HSE事故,或在供应期/承包期受到区级以上行政 执法机关环境、安全、质量处罚的供方或承包方,只要有可能,就不准再采购其产品或服务。 对于有管理程序、执行程序、合同、协议进行控制的相关方,应首先将有关管理要求明确。 对于实施行政管理的相关方,均应从水、气污染物、噪声、固体废弃物、生态、资源利用等方面考虑其可能造成的环境影响,并提出控制要求。 本所对相关方的HSE要求应书面传达,并注意签收,保存相关记录。 各部门对相关方落实环境管理要求的情况应进行检查,检查要求按有关的法律法规和程序文件确定。检查要形成记录。 ARM920T的CP15协处理器 ARM920T的MMU和Cache都集成在CP15协处理器中,MMU和Cache的联系非常密切,本节首先从总体上介绍MMU、Cache和CPU核是如何协同工作的,后面两节分别讲解MMU和Cache的细节。三星公司的S3C2410是一种很常见的采用ARM920T的芯片,涉及到具体的芯片时我们以S3C2410为例。 以下是CP15协处理器的寄存器列表(摘自[S3C2410用户手册]),和CPU核的r0到r15寄存器一样,协处理器寄存器也是用0到15来编号,在指令中用4个bit来表示寄存器编号,有些协处理器寄存器有影子寄存器,这种情况下对同一个编号的寄存器使用不同的选项读或者写实际上访问的是不同的寄存器,后文用到某个寄存器时会详细说明它的功能。 表1. CP15协处理器的寄存器列表 对CP15协处理器的操作使用mcr和mrc两条协处理器指令,这两条指令的记法是从后往前看:mcr是把r(CPU核寄存器)中的数据传送到c(协处理器寄存器)中,mrc则是把c(协处理器寄存器)中的数据传送到r(CPU核寄存器)中。对CP15协处理器的所有操作都是通过CPU核寄存器和CP15寄存器之间交换数据来完成的。下图是协处理器的指令格式(摘自[S3C2410用户手册])。 图8. 协处理器指令格式 和其它ARM指令一样,Cond是条件码,bit 20是L位,表示该指令是读还是写,如果L=1就表示Load,从外面读到CPU核中,也就是mrc指令,如果L=0就表示Store,也就是mcr指令。[11:8]这四个位是协处理器编号,CP15的编号是15,因此是4个1。CRn是CP15寄存器编号,Rd是CPU核寄存器编号,各占4个位。对于CP15协处理器,规定opcode1应该为0,opcode2和CRm是指令的选项,具体含义取决于不同的寄存器。 虽然这里介绍了协处理器的寄存器编号和相关指令,但读者只需了解对协处理器是这样进行操作的就可以了,我们的重点是讲解MMU和Cache的基本概念,具体各种操作的指令该怎么写可以参考[S3C2410用户手册]。 MMU是如何把VA映射成PA的呢?从图4 “进程地址空间是独立的”来看,好像是有一张VA转PA的表,给一个VA查表就可以查到PA,实际上并不是这么简单,通常要有一个多级的查表过程,对于ARM体系结构是两级查表,对于一些64位体系结构则需要更多级。看下面的图示。 图9. Translation Table Walk 首先将32位的VA[3]分成三段,前两段[31:20]和[19:12]作为两次查表的索引,第三段[11:0]作为页内的偏移。查表的步骤如下: 1 CP15协处理器的TTB寄存器(看看表1 “CP15协处理器的寄存器列表”中这是第几个寄存器?)中保存着第一级页表(Translation Table)的基地址,这个基地址指的是PA,也就是说页表是直接按这个地址存在物理内存中的。 2 以TTB中的内容为基地址,以VA[31:20]为索引在表中查出一项(想一下这个表中一共有多少项?),这个表项中保存着第二级页表(Coarse Page Table)的基地址,同样是物理地址,也就是说第二级页表也是直接按这个地址存在物理内存中的。 苏州大学微控制器原理期末复习 一、选择题( 20 X 1’ ) 1.以下芯片系列中,没有单片机的系列是( ) A. PIC系列 B. X86系列 C. AVR系列 D. ARM系列 2.微控制器是指( ) A.微处理器 B.微型计算机 C.单板机 D.单片机 3.在ARM 技术定义的AMBA(Advanced Microcontroller Bus Architecture ) 总线规范中,定义了用于高性能系统模块连接的( )总线。 A. ASB B. APB C. BB (Bus Bridge) D. AHB 4.在 ARM 技术定义的AMBA (Advanced Microcontroller Bus Architecture )总线规范中定义了用于较低性能外设简单连接的( )总线。 A.ASB B.APB C.BB(Bus Bridge) D.AHB 5.AMBA (Advanced Microcontroller Bus Architecture )是()标准。 A.片上总线 B.控制总线 C.外设总线 D.系统总线 6.ARM Cortex-M0+处理器中的 LR(R14)是( ) A.通用寄存器 B.程序计数寄存器 C.连接寄存器 D.特殊功能寄存器 7. ARM Cortex-MO+处理器中的 PC(R15)是( ) A.通用宵存器 B.程序计数寄存器 C.连接寄存器 D.特殊功能寄存器 8.基本存储单元由()个连续的二进制位构成, A.8 B.16 C. 32 D. 64 9.ARM Cortex-MO+处理器中共有()个通用寄存器? A.15 B. 14 C. 13 D. 12 10.ARM Cortex-MO+处理器中,寄存器SP(R13)的最低( )位永远为0。 A. 1 B. 2 C.3 D.4 11.ARM Cortex-MO+处理器中,APSR用于反映ALU的运算结果的某些特 征,共有()个标志位。 A. 1 B. 2 C.3 D.4 12.KL25的UART模块不支持()位数据模式 A. 7 B. 8 C.9 D. 10 13.M CU各个模块作为中断源引起的中断称为(). A.内核中断 B.异常中断 C.可屏蔽中断 D.不可屏蔽中断 14.在CPU停机方式的DMA操作中,CPU与总线的关系是( ) A.只能控制数据总线 B.只能控制地址总线 C.处于隔离状态 D.能传送所有控制信号 15.CPU在中断响应过程中的何种措施是为了能正确地实现中断返回( ) 1目的 控制和提高相关方(客户、供应商、工程合同方、废物收购方)的环境行为,降低或消除相关方环境因素对本厂所造成的影响。 2范围 适用于本厂及其它重要相关方之间的环境影响的管理。 3定义 3.1相关方:关注组织的环境表现(行为)或受其环境表现(行为)影响的个人或团体。(注: 本文件所指的相关方包括有客户、供应商、工程合同方、废物收购方或收取方) 4职责 4.1营业部:对与其对口的供应商环境行为施加影响。 4.2管理部和对与其对口的废物收购或收取方环境行为施加影响。 4.3管理部负责对工程合同方的环境行为施加影响。 5环境信息沟通 5.1对客户环境信息的沟通管理 5.1.1营业部收到来自客户方面的环境信息,品保部按外来文件分发相关部门,需要回复时由 品保部回复客户。 5.1.2有关协议及相关改进措施经权责人员签核后由营业部传达至客户,并保留记录。 5.2对供应商的环境行为施加影响: 5.2.1营业部组织对供应商进行识别、登记和评价,将供应商分为:施加影响的单位和暂不施 加影响的单位,具体识别、登记和评价见《环境因素控制程序》。 5.2.2对施加影响的单位,由营业部负责与其签订《供应商环境协议》,对供应商的环境行为 做出要求。 5.2.3由营业部组织管理部、品保部对施加影响的供应商进行不定期的环境检查,对不符合要 求的施加影响的供应商,提出整改要求,对整改不符合或拒绝整改,可能造成严重污染或已经造成重大环境污染事故的供应商,有权向其提出:限期整改、减少订货和撤消供货点。 5.2.4在与供应商进行技术或质量方面的交流时,安排进行环境方面的交流,并由管理部(采 购)向供应商提出有关环境要求。 5.3对工程合同方的环境行为施加影响: 5.3.1工程项目的负责部门在与施工单位签订合同时,应同时签订《工程合同方环境协议》。 5.3.2工程项目的负责部门应组织对施工单位施工情况的检查与跟踪,对不符合要求的,按《工 程合同方环境协议》有关条款执行。 5.4对废物收购或收取方的环境行为施加影响: 1-3、ARM开发步步深入之MMU初窥 实验目的:启用MMU,映射SDRAM的地址空间,操作虚拟地址实现“点灯大法”,借此掌握MMU的使用。 实验环境及说明:恒颐S3C2410开发板H2410。H2410核心板扩展有64MB的K4S561632 SDRAM(4M*16bit*4BANK),地址范围是0x30000000~0x33FFFFFF。GPIO端口的地址范围是 0x56000000~0X560000B0。 实验思路:开发板上电启动后,自动将NandFlash开始的4K数据复制到SRAM中,然后跳转到0地址开始执行,然后初始化存储控制器SDRAM,把2K后的代码从SRAM中复制到SDRAM中(存放在0x30004000,前16KB用来存放页表)、设置页表、启动MMU 实现虚拟地址映射GPIO寄存器和SDRAM,最后跳转到SDRAM中(地址0xB0004000)运行。重新设置栈指针,跳到点灯代码的入口点实现点灯操作。 知识掌握:MMU地址转换、内存访问权限检查、TLB及Cache的使用 一、MMU地址转换: 1.首先弄清除为什么要使用MMU纳?MMU即内存管理单元,直白一点的讲,就像食堂的餐具,所有的学生一起吃饭时不够用,但食堂又不想再出资购买新的餐具(原因很明显:一方面要成本,另一方面 又占地方。这就像增加内存一样),那么有没有解决办法?根据以往经验得知不可能全学校的学习一起都到食堂吃饭,于是食堂就找几个人负责餐具的管理(相当于MMU),他们一方面发放餐具,保证来的同学有餐具可用,另一方面又回收用完的餐具(这就相当于虚拟地址到物理地址之间建立了一个映射一样,内存还是那么多,但从任意单个程序角度都好像用不完一样)。当然如果有同学一个人拿好几套餐具肯定不允许的(这就相当于内存的权限检查)。MMU在地址转换过程中涉及到三种地址:(VA---Virtual Address,虚拟地址)---这个就相当于餐具存放的地方(大家都可以领到餐具)。CPU核心看到和用到的只是虚拟地址VA,至于VA如果去对应物理地址PA,CPU 核心不理会,大家也不会去关心总共有多少餐具吧; (MVA---Modified Virtual Address,变换后的虚拟地址)---这个相当于放假的时候,人很少,只发餐具好了,用过的就不先回收了,节省人员了。Caches和MMU看不到VA,他们利用MVA转换得到PA,放假了回收餐具的人也不需要一直寻找用完的餐具; (PA---Physical Address,物理地址)---实际的餐具量,就那些。实际设备看不到VA、MVA,读写它们使用的是物理地址PA,同学们就餐一般会领到餐具。 2.虚拟地址到物理地址的转换过程。ARM使用页表来进行转换, S3C2410最多会用到两级页表,以段(Section,1M)的方式进行转换时只用到一级页表,以页(Page)的方式进行转换时用到两级页表。页的大小有3种:大页(64KB)、小页(4KB)和极小页(1KB)。本文 微处理器和嵌入式系统 1.简述Bootloader的作用,列举三种主流的Bootloader的名称和特点。 作用:引导装载程序,初始化内粗配置器,初始化串行端口,对后续内核加载引导执行主流:U-Boot,Redboot,vivi 特点:适用于不同的架构平台 2.什么是交叉编译环境?为什么要采用交叉编译环境? 一台pc机上建立一套编译环境,此环境是为了编译另一种架构的代码; 原因:目标的硬件平台与当前的不一样的CPU架构,指令集不兼容 3.Mount命令有哪些作用?举例说明。 1)挂载网络文件系统 2)挂载本地大容量存储设备(原生作用),硬盘/软盘/U盘分区 4.列举Linux根文件系统的目录树结构。写出三个目录的作用。 5.什么是Frame buffer设备?Frame buffer有哪些参数?如何在Frame buffer设备上显示 一个红色的像素点? 定义:帧缓冲设备,将设备映射到内存空间,将内存映射的操作映射到用户空间 参数:分辨率,色深,显示器色位 画红点: 6.NFS服务在嵌入式开发中的作用。 局域网里实验网络文件/目录的共享 7.Tftp服务在嵌入式开发中的作用。 轻量级的文件传输服务,内核文件系统下载 主机端:建立tftp端软件,配置下载目录 开发板、目标板端:利用bootloader,tftp命令下载主机端内核文件系统 8.Minicon 软件在嵌入式开发中的作用。 实现主机与开发板的串口通信, 9.Linux内核配置编译的基本步骤。 10.回答嵌入式系统的定义,列举其特点。 定义:以应用为中心,以计算机技术为基础,软件硬件可裁剪,适应系统对功能、可靠性、成本、体积、功耗严格要求的计算机系统。 特点:系统内核小、专用性强、系统精简、高性能的实时操作系统软件、使用多任务的操作系统 11.嵌入式系统处理器分为哪几类?主流嵌入式微处理器内核有哪些? 分类:嵌入式微控制器、嵌入式DSP处理器、嵌入式微处理器、嵌入式片上系统 内核:ARM、MIPS、Power Pc、x86、68k 12.ARM处理器与X86处理器最大的区别是什么? 1)架构:ARM精简指令集(RISC),x86复杂指令集(CISC) 2)其他:ARM 功耗极低,主板安全性更高 13.嵌入式系统软件测试技术有哪些? 黑盒测试、白盒测试、目标环境测试、宿主环境测试 14.嵌入式系统可靠性参数如何计算? 1)MTBF=缺陷率×每秒执行的千行代码数目 2)MTTR=软件故障检测到之后的重新启动时间的平均值 3)有效性A=MTBF MTBF+MTTR 15.Linux内核有哪5大功能? 进程管理、内存管理、文件管理、设备控制、网络功能 16.设备驱动程序的基本作用。 主要作用在于提供机制而非策略,主要解决需要提供什么功能的问题,可以看做应用和实际设备的一个软件层。 相关方管理控制程序 1目的 对相关方施加影响,共同提高产品质量、改善环境和职业健康安全绩效。 2适用范围 适用于公司质量、环境和职业健康安全管理体系各有关相关方的管理。 3职责 3.1安全环保部负责组织确定重点施加影响的相关方。 3.2管理者代表负责批准重点施加影响的相关方。 3.3各部门负责职责范围内的相关方施加影响的具体业务管理工作。 4工作程序 4.1能够影响的相关方的识别 4.1.1公司能够施加影响的相关方是指提供本公司的货物、设备和服务的过程中可能对产品质量、环境或职业健康安全风险产生影响的相关方。 4.1.2公司能够施加影响的相关方主要有工程合同供方、设备供方、备品备件供方、原辅材料供方、劳保用品供方、运输服务供方、固体废物处理或收购方、食堂承包方、到厂实习或参观人员、生产厂区周边的居民和单位等。 4.2对相关方进行评估 4.2.1安全环保部组织供应部、生产技术部、工程部、研发中心、储运部、公司办、工会、营销部等相关部门对相关方进行评估。与公司的重要环境因素或具有中度以上风险危险源相关联的,或可能造成重大环境污染或重大安全事故的相关方,原则上定为重点施加影响的相关方,列入《重点施加影响相关方一览表》中,由安全环保部审核后交管理者代表批准,该表应明确负责施加影响相关方的责任部门,并由相关的责任部门各保存一份。 4.2.2其他未定为重点施加影响的相关方为一般施加影响的相关方。 4.3对相关方的质量、环境行为和职业健康安全管理施加影响的内容: 4.3.1工程合同供方 生产技术部、工程部和研发中心在施工合同中要求供方遵守有关法律法规及其他要求,明确工程合同供方的施工质量要求和在公司内施工管理的要求,管理要求应至少包括施工现场的卫生、建筑垃圾、建筑噪声、消防管理、安全管理要求等内容。 4.3.2设备、备品备件、原辅材料、特种防护用品、运输服务供方 4.3.2.1供应部、生产技术部、研发中心、营销部按《采购控制程序》规定对设备、备品内外部环境和相关方要求识别控制程序

cp15协处理器指令详解

数字电路与微处理器基础实验

微处理器系统与嵌入式系统1—7章最全答案合集

微机原理课后习题答案第二章微处理器和指令系统习题答案

相关方控制程序

协处理器控制位详解cp15.

微处理器系统结构与嵌入式系统设计(第2版) 第3章答案

ISO45001相关方管理控制程序

微控制器原理及应用答案

相关方管理控制程序

ARM_协处理器-CP15

微控制器原理期末复习题整理

相关方管理控制程序

MMU详解

南京大学微处理器和嵌入式系统复习

ISO45001相关方管理控制程序