一、设计要求 (1)

二、设计原理及框图 (1)

1、设计原理 (1)

2、结构框图 (1)

三、设计过程 (2)

1、模块化设计 (2)

2、顶层文件生成 (3)

四、仿真调试过程 (4)

1、各模块时序仿真图 (4)

2、仿真过程中遇到的问题 (5)

五、设计体会及收获 (5)

一、设计要求

1、稳定的显示时、分、秒。

2、当电路发生走时误差时,要求电路有校时功能。

3、电路有整点报时功能。报时声响为四低一高,最后一响高音正好为整点。

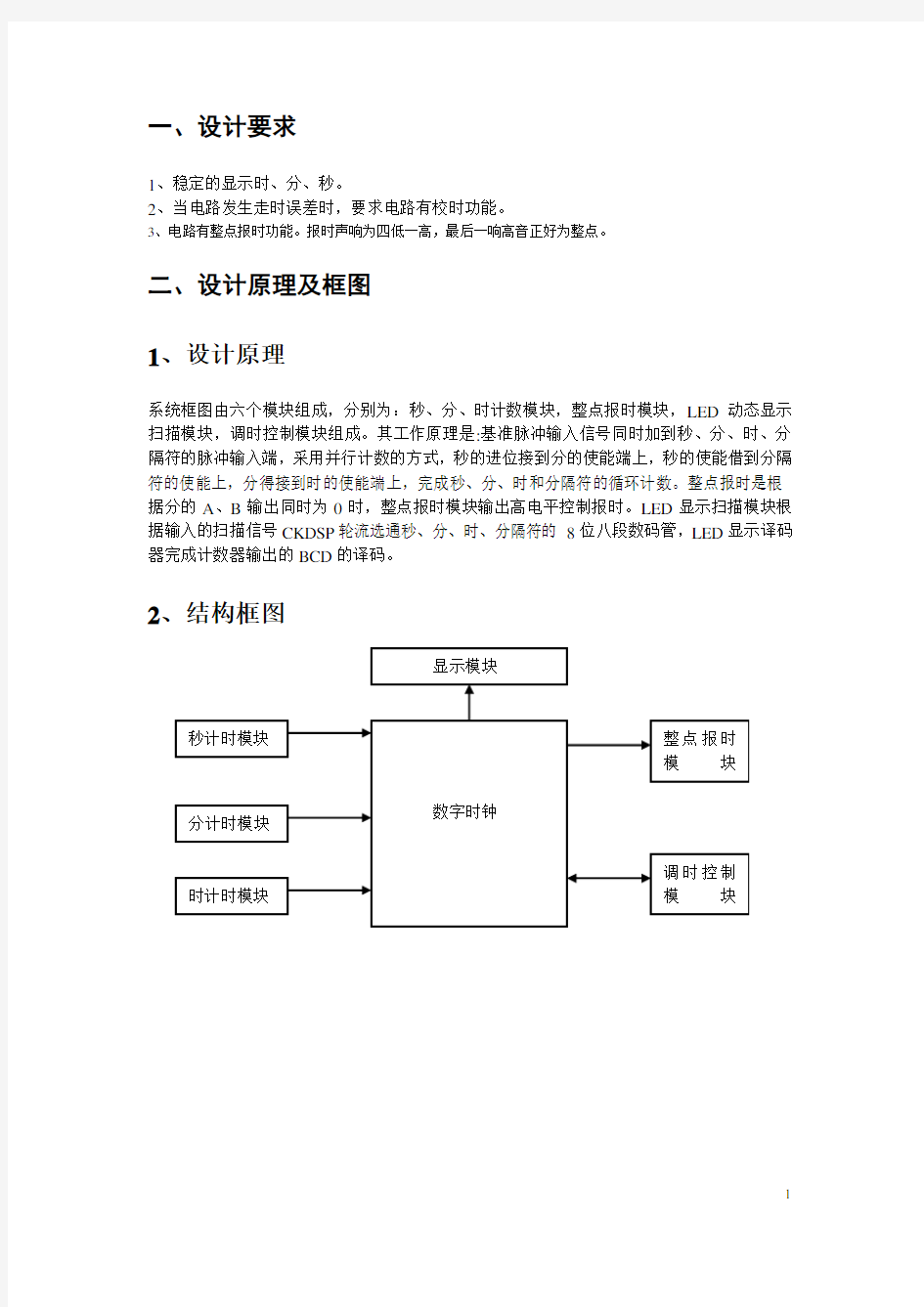

二、设计原理及框图 1、设计原理

系统框图由六个模块组成,分别为:秒、分、时计数模块,整点报时模块,LED 动态显示扫描模块,调时控制模块组成。其工作原理是:基准脉冲输入信号同时加到秒、分、时、分隔符的脉冲输入端,采用并行计数的方式,秒的进位接到分的使能端上,秒的使能借到分隔符的使能上,分得接到时的使能端上,完成秒、分、时和分隔符的循环计数。整点报时是根据分的A 、B 输出同时为0时,整点报时模块输出高电平控制报时。LED 显示扫描模块根据输入的扫描信号CKDSP 轮流选通秒、分、时、分隔符的8位八段数码管,LED 显示译码器完成计数器输出的BCD 的译码。

2、结构框图

显示模块

数字时钟

秒计时模块

分计时模块

时计时模块

整点报时模 块

调时控制模 块

三、设计过程

1、模块化设计

(1)秒计时模块

秒计时模块由一个60位计数器为主体构成,其输入输出端口组成为:

Clk:计时时钟信号

Reset:异步清零信号

Setmin:分钟设置信号

Enmin:使能输出信号

Daout[6:0]:BCD码输出

(2)分计时模块

分计时模块由一个60位计数器为主体构成,其输入输出端口组成为:

Clk、clk1:计时时钟信号

Reset:异步清零信号

Sethour:小时设置信号

Enmin:使能输出信号

Daout[6:0]:BCD码输出

(3)时计时模块

时计时模块由24位计数器为主体构成,其输入输出端口组成为:

Clk:计时时钟信号

Reset:异步清零信号

Daout[6:0]:BCD码输出

(4)显示模块

系统时间输出由六个七段数码管显示。

显示的数据是各计时模块给出的

BCD码。

(5)调时控制模块

该模块主要用于调节时、分显示,用于“对表”。

(6)整点报时模块

在时钟整点的时候产生扬声器驱动信号。由时钟计

时模块中分钟的进行信号进行控制。当contr_en 为

高电平时,将输入信号clk 送到输出端speak 用于

驱动扬声器,同时在clk 的控制下,输出端lamp[2..0]

进行循环移位。输出控制模块有扬声器控制器子模

块组成。

2、顶层文件生成

前面已经完成了电子时钟电路的各个组成部分的设计,下面把这些组成部分组装起来,形成完整的总体设计。该电子时钟的命名为clock,其外部端

口如右图所示。各个输入/ 输出端口的作用如下:

(1)clk 为外部时钟信号,其频率为1Hz,reset 为异

步清零信号.

(2)sethour 和setmin分别为调时调分脉冲输入信

号,当en_set为高电平时,

每来一个sethour 脉冲或setmin脉冲,时、分输出将分

别加1;

(3)second[6...0]为秒的个位和十位BCD 码输出,

min[6…0]为分钟的个位和十位BCD 码输出,hour[6...0]

为小时的个位和十位BCD 码输出,它们最终中用来驱

动七段数码管,lamp[2...0]为花样显示输出信号,speak

为整点报时扬声器驱动信号

四、仿真调试过程

1、各模块时序仿真图(1)秒计数器仿真图

(2)分计数器仿真图

(3)时计数器仿真图

(4)整点报时仿真图

(5)调时调分仿真图

(6)LED显示译码仿真图

2、仿真过程中遇到的问题

(1)由于距离学习EDA技术课程的时间较长,遗忘了部分课程内容,对仿真软件不熟悉造成多次仿真失败。就此问题我认真复习了所学的EDA相关课程,按照课本上介绍的步骤重新进行了仿真,问题得以解决。

(2)因为仿真过程中对各部分时序波形应采取什么样的激励波形不清楚,给仿真过程带来了较大的麻烦。通过查阅相关资料,阅读网上一些比较成熟的论文,确定了仿真过程中的相关参数。

五、设计体会及收获

本次课程设计我做出的数字时钟能够正确的进行整点报时,显示时间,但是对于调时调分功能不能正确显示。经过努力,简易电子时钟的设计基本上算是完成了,在整个设计中,我最大的体会就是:对学过的知识遗忘太多。在本次的课程设计中,我发现了很多问题,同时做起来也很难不顺手,看着简单的电路,要动手把它设计出来实非易事,主要原因对相关应用软件的不熟悉,这就要求我们在以后的学习中,应该注意复习的重要性,对学过的知识要时常复习,加深记忆,更重要的是我们要学会把从书本上学到的知识和实际电路联系起来,这不论对我们以后的学习还是就业,都会起到很大的促进和帮助。我相信,通过这次的课程设计,在下一阶段的学习中我们会更加努力,力争把这门课学好学精。同时通过本次课程设计,巩固了我们以前学过的专业知识,通过这次的程序设计,使我们对数字系统结构也有了更进一步的了解与认识,同时对数据库软件EDA技术,VHDL语言等系列知识都有了一定的了解与认识。使用EDA技术开发页面的能力也有了提高,也使我们把理论与实践从正真意义上结合了起来,考验了我们的动手能力和查阅相关资料的能力,还有组织材料的能力。通过此次实践,我们从中可以找出自己知识的不足与欠缺,以便我们在日后的学习中得以改进与提高。经过本次设计使我们对大学四年期间所学习到的知识得以进一步实践,这将对我们走出校园,走向社会,走向工作岗位奠定坚实的基础。

附录

1、秒计数单元代码

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY second IS

PORT(

clk,reset,setmin:IN STD_LOGIC;

enmin:OUT STD_LOGIC;

daout:out std_logic_vector(6 downto 0)); END entity second;

ARCHITECTURE fun OF second IS SIGNAL count:STD_LOGIC_VECTOR(6 downto 0);

SIGNAL enmin_1,enmin_2:STD_LOGIC; BEGIN

daout<=count;

enmin_2<=(setmin and clk);

enmin<=(enmin_1 or enmin_2);

process(clk,reset,setmin)

begin

if(reset='0') then count<="0000000";

elsif(clk'event and clk='1')then

if(count(3 downto 0)="1001")then

if(count<16#60#)then

if(count="1011001")then

enmin_1<='1';count<="0000000";

else

count<=count+7;

end if;

else

count<="0000000";

end if;

elsif(count<16#60#)then

count<=count+1;

enmin_1<='0' after 100 ns;

else

end if;

end if;

end process;

end fun ;

2、分计数单元代码LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY minute IS

PORT(

clk,clk1,reset,sethour:IN STD_LOGIC; enhour:OUT STD_LOGIC;

daout:out std_logic_vector(6 downto 0)); END entity minute;

ARCHITECTURE fun OF minute IS SIGNAL count:STD_LOGIC_VECTOR(6 downto 0);

SIGNAL enhour_1,enhour_2:STD_LOGIC; BEGIN

daout<=count;

enhour_2<=(sethour and clk1);

enhour<=(enhour_1 or enhour_2);

process(clk,reset,sethour)

begin

if(reset='0')then

count<="0000000";

elsif(clk'event and clk='1')then

if(count(3 downto 0)="1001")then

if(count<16#60#)then

if(count="1011001")then

enhour_1<='1';

count<="0000000";

ELSE

count<=count+7;

end if;

else

count<="0000000";

end if;

elsif(count<16#60#)then

count<=count+1;

enhour_1<='0'after 100 ns;

else

count<="0000000";

end if;

end if;

end process;

END fun;

3、时计数单元代码

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY hour IS

PORT(

clk,reset:IN STD_LOGIC;

daout:out std_logic_vector(5 downto 0)); END entity hour;

ARCHITECTURE fun OF hour IS

SIGNAL count:STD_LOGIC_VECTOR(5 downto 0);

BEGIN

daout<=count;

process(clk,reset)

begin

if(reset='0')then

count<="000000";

elsif(clk'event and clk='1')then

if (count(3 downto 0)="1001")then

if(count<=16#23#)then

count<=count+7;

else

count<="000000";

end if;

elsif(count<16#23#)then

count<=count+1;

else

count<="000000";

end if;

end if;

end process;

END fun;

4、显示单元代码

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY deled IS

PORT(num:IN std_logic_vector(3 downto 0); led:OUT std_logic_vector(6 downto 0));

end deled;

ARCHITECTURE fun OF deled IS

BEGIN led<="1111110"when num="0000"else "0110000"when num="0001"else "1101101"when num="0010"else "1111001"when num="0011"else "0110011"when num="0100"else "1011011"when num="0101"else "1011111"when num="0110"else "1110000"when num="0111"else "1111111"when num="1000"else "1111011"when num="1001"else "1110111"when num="1010"else "0011111"when num="1011"else "1001110"when num="1100"else "0111101"when num="1101"else "1001111"when num="1110"else "1000111"when num="1111";

END fun;

5、调时控制单元代码

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

ENTITY seltime IS

PORT(

clk1,reset:IN STD_LOGIC;

sec,min:IN STD_LOGIC_VECTOR(6 downto 0);

hour:in std_logic_vector(5 downto 0); daout:OUT STD_LOGIC_vector(3 downto 0); dp:OUT std_LOGIC;

sel:out std_logic_vector(2 downto 0));

END seltime;

ARCHITECTURE fun OF seltime IS SIGNAL count:STD_LOGIC_vector(2 downto 0);

BEGIN

sel<=count;

process(clk1,reset)

begin

if(reset='0')then

count<="000";

elsif(clk1'event and clk1='1')then

if(count>="101")then

count<="000";

else

count<=count+1;

end if;

end if;

case count is

when"000"=>daout<=sec(3 downto 0);dp<='0';

when"001"=>daout(3)<='0';daout(2 downto 0)<=sec(6 downto 4);dp<='0'; when"010"=>daout<=min(3 downto 0);dp<='1';

when"011"=>daout(3)<='0';daout(2 downto 0)<=min(6 downto 4);dp<='0'; when"100"=>daout<=hour(3 downto 0);dp<='1';

when others=>daout(3 downto 2)<="00"; daout(1 downto 0)<=hour(5 downto 4);dp<='0';

end case;

end process;

end fun;

6、整点报时单元代码

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY alert IS

PORT(

clk:IN STD_LOGIC;

dain:IN STD_LOGIC_VECTOR (6 DOWNTO 0);

speak:OUT STD_LOGIC;

lamp:OUT STD_LOGIC_VECTOR (2 DOWNTO 0));

END alert;

ARCHITECTURE fun OF alert IS

signal coun:std_logic_vector (1 downto 0); signal count1:std_logic_vector (1 downto 0); BEGIN

speaker:process(clk)

begin

speak<=count1(1);

if(clk'event and clk='1')then

if(dain="0000000")then

if(count1>="10")then count1<="00";

else

count1<=count1+1;

end if;

end if;

end if;

end process speaker;

lamper:process(clk)

begin

if(rising_edge(clk))then

if(coun<="10")then

if(coun="00")then

lamp<="001";

elsif(coun="01")then

lamp<="010";

elsif(coun="10")then

lamp<="100";

end if;

coun<=coun+1;

else

coun<="00";

end if;

end if;

end process lamper;

END fun;

7、顶层代码

library ieee;

use ieee.std_logic_1164.all;

entity clock_top is

port(clk,reset,setmin,sethour,clkdsp:in std_logic;

speaker:out std_logic;

lamp:out std_logic_vector(2 downto 0); sel:out std_logic_vector(2 downto 0); a,b,c,d,e,f,g,dpout:out std_logic);

end clock_top;

architecture a of clock_top is COMPONENT second

PORT(

clk,reset,setmin:IN STD_LOGIC; daout:out std_logic_vector(6 downto 0); enmin:OUT STD_LOGIC);

END COMPONENT; COMPONENT minute

PORT(

clk,clk1,reset,sethour:IN STD_LOGIC; enhour:OUT STD_LOGIC;

daout:out std_logic_vector(6 downto 0)); END COMPONENT;

COMPONENT hour

PORT(

clk,reset:IN STD_LOGIC;

daout:out std_logic_vector(5 downto 0)); END COMPONENT;

COMPONENT alert

PORT(

clk:IN STD_LOGIC;

dain:in std_logic_vector(6 downto 0); lamp:out std_logic_vector(2 downto 0); speak:OUT STD_LOGIC);

END COMPONENT;

COMPONENT seltime

PORT(

clk1,reset:IN STD_LOGIC;

sec,min:in std_logic_vector(6 downto 0); hour:in std_logic_vector(5 downto 0);

dp:out std_logic;

daout:out std_logic_vector(3 downto 0); sel:OUT STD_LOGIC_vector(2 downto 0)); END COMPONENT;

COMPONENT deled

PORT(

num:IN STD_LOGIC_vector(3 downto 0); led:out std_logic_vector(6 downto 0));

END COMPONENT;

signal enmin_re,enhour_re:std_logic;

signal

second_daout,minute_daout:std_logic_vector( 6 downto 0);

signal hour_daout:std_logic_vector(5 downto 0); signal seltime_daout:std_logic_vector(3 downto 0);

signal ledout:std_logic_vector(6 downto 0); begin

a<=ledout(6);b<=ledout(5);c<=ledout(4);d<=l edout(3);

e<=ledout(2);f<=ledout(1);g<=ledout(0);

u1: second port map(reset=>reset,

clk=>clk,

setmin=>setmin,

enmin=>enmin_re,

daout=>second_daout);

u2:minute port map(clk=>enmin_re,

clk1=>clk,

reset=>reset,

sethour=>sethour,

enhour=>enhour_re,

daout=>minute_daout);

u3:hour port map(clk=>enhour_re,

reset=>reset,

daout=>hour_daout);

u4:alert port map(clk=>clk,

dain=>minute_daout,

speak=>speaker,

lamp=>lamp);

u5:seltime port map(clk1=>clkdsp,

reset=>reset,

sec=>second_daout,

min=>minute_daout,

hour=>hour_daout,

daout=>seltime_daout,

dp=>dpout,

sel=>sel);

u6:deled port map(num =>seltime_daout,

led=>ledout);

end a;

数字钟的设计 一、系统功能概述 (一)、系统实现的功能: 1、具有“时”、“分”、“秒”的十进制数字显示(小时从00 ~ 23)。 2、具有手动校时、校分、校秒的功能。 3、有定时和闹钟功能,能够在设定的时间发出闹铃声。 4、能进行整点报时。从59分50秒起,每隔2秒发一次低音“嘟”的信号,连续5次, 最后一次为高音“嘀”的信号。 (二)、各项设计指标: 1、显示部分采用的6个LED显示器,从高位至低位分别显示时、分、秒。 2、有一个设置调闹钟定时时间、正常时间的按钮,选择调的对象。 3、有三个按钮分别调时、分、秒的时间。 4、有一个按钮用作开启/关闭闹铃。 5、另外需要两个时钟信号来给系统提供脉冲信号,使时钟和闹钟正常工作,分别为1Hz、 1kHz的脉冲。 二、系统组成以及系统各部分的设计 1、系统结构描述//要求:系统(或顶层文件)结构描述,各个模块(或子程序)的功能描述;(一)系统的顶层文件: 1、顶层文件图:(见下页) 2、各模块的解释: (1)、7个输入量clk_1khz、clk_1hz、key_slt、key_alarm、sec_set、min_set、hour_set:其中clk_1khz为闹铃模块提供时钟,处理后能产生“嘟”、“嘀”和变化的闹铃声音;clk_1hz为计时模块提供时钟信号,每秒计数一次;key_slt选择设置对象:定时或正常时间;key_alarm能够开启和关闭闹铃;sec_set、min_set、hour_set用于设置时间或定时,与key_slt相关联。各按键输出为脉冲信号。 (2)、CNT60_A_SEC模块: 这个模块式将clk_1hz这个时钟信号进行60进制计数,并产生一个分钟的触发信号。该模块能将当前计数值实时按BCD码的格式输出。将该输出接到两位LED数码后能时时显示秒的状态。通过alarm_clk可以选择设置对象为时间还是定时值。在设置时间模式上,key上的一个输入脉冲可以将clk的输入信号加一。在设置定时模式上,key 上的脉冲只修改定时值,不影响时间脉冲clk的状态。 同时该模块具有两个输出口out_do、out_di来触发整点报时的“嘟”、“嘀”声音。 (3)、CNT60_A_MIN模块: 这个模块式将CNT60_A_SEC的输出信号进行60进制计数,并产生一个时位的触发信号。该模块能将当前计数值实时按BCD码的格式输出。将该输出接到两位LED数码后能时时显示分的状态。通过alarm_clk可以选择设置对象为时间还是定时值。在设置时间模式上,key上的一个输入脉冲可以将clk的输入信号加一。在设置定时模式上,key上的脉冲只修改定时值,不影响时间脉冲clk的状态。 同时该模块具有三个输出口out_do、out_di、out_alarm来触发整点报时的“嘟”、“嘀”、闹铃声音。

数字时钟设计 一、题目分析 1、功能介绍 1)具有时、分、秒计数显示功能,以24小时循环计时。 2)时钟计数显示时有LED灯的花样显示。 3)具有调节小时、分钟及清零的功能。 4)具有整点报时功能。 2、总体方框图 3、性能指标及功能设计 1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。 2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来

一个脉冲,即计数一次。 3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。可以根据我们自己任意时间的复位。 4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。产生“滴答.滴答”的报警声音。 5)LED灯在时钟显示时有花样显示信号产生。即根据进位情况,LED不停的闪烁,从而产生“花样”信号。 二、选择方案 1、方案选择 方案一:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。显示:小时采用24进制,而分钟均是采用6进制和10进制的组合。 方案二:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。显示:小时采用24进制,而分钟和秒均60进制。 终上所述,考虑到试验时的简单性,故我选择了方案二。 三、细化框图 根据自顶向下的方法以及各功能模块的的功能实现上述设计方案应系统细化框图:

VHDL数字钟设计报告 一. 数字钟总体设计方案: 1.1设计目的 ①正确显示时、分、秒; ②可手动校时,能分别进行时、分的校正; ③整点报时功能; 1.2设计思路 数字钟的设计模块包括:分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路、 整点报时和译码显示电路。 每一个功能模块作为一个实体单独进行设计,最后再用VHDL的例化语句将各个模块进行整合,生成 顶层实体top。 该数字钟可以实现3个功能:计时功能、设置时间功能和报时功能。 二.数字钟模块细节 2.1 分频器(fenpin) 本系统共需3种频率时钟信号(1024Hz、512Hz、1Hz)。为减少输入引脚,本系统采用分频模块,只需由外部提供1024Hz基准时钟信号,其余三种频率时钟信号由分频模块得到。 分频原理:为以1024Hz基准时钟经1024分频得到512Hz,1Hz频率时钟信号。 分频器管脚 代码:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity fenpin is port(clk1024:in std_logic; clk1,clk512:out std_logic ); end fenpin ; architecture cml of fenpin is begin process (clk1024) variable count1: integer range 0 to 512; variable q1: std_logic; begin if clk1024' event and clk1024='1' then if count1=512 then q1:=not q1; count1:=0; else count1:=count1+1; end if; end if; clk1<=q1; end process; process(clk1024) variable count512: integer range 0 to 1; variable q512: std_logic; begin if clk1024' event and clk1024='1' then if count512=1 then q512:=not q512; count512:=0; else count512:=count512+1; end if; end if; clk512<=q512; end process; end cml; 2.2 校时电路(jiaoshi)

基于VHDL语言 数 字 钟 设 计 学院:信息工程学院 专业: 姓名: 学号: 2010年6月15日

一、设计要求 1、具有以二十四小时制计时、显示、整点报时、时间设置和闹钟的功能。 2、设计精度要求为1秒。 二、设计目的 1.掌握各类计数器以及计数器的级联方式; 2.掌握数码管动态显示的原理与方法; 3.掌握用FPGA技术的层次化设计方法; 4.理解数字逻辑硬件和软件的设计思想; 三、设计环境:Quartus II CPLD-5型试验箱 四、系统功能描述 1、系统输入:系统状态及较时、定时转换的控制信号为enset、k、set; 时钟信号clk采用50MHz;校时复位信号为reset,输入信号均由按键信号产生。 2、系统输出:LED显示输出;蜂鸣器声音信号输出。 3、多功能数字电子钟系统功能的具体描述如下: (一)计时:正常工作状态下,每日按24h计时制计时并显示,蜂鸣器无声,逢整点报时。 (二)校时:在计时显示状态下,按下“enset”键,接着按下“k”键,进入“小时”待校准状态,若此时按下“set”键,小时开始校准;之后按上“k”键则进入“分”待校准状态;继续按下“k”键则进入“秒”待复零状态;再次按上“k”键数码管显示闹钟时间,并进入闹钟“小时”待校准状态;再次按下“k”键则进入闹钟“分”待校准状态;若再按上“k”键恢复到正常计时显示状态。若校时过程中按下“reset”键,则系统恢复到正常计数状态。 (1)“小时”校准状态:在“小时”校准状态下,显示“小时”的数码管以2Hz 闪烁,并以2Hz的频率递增计数。 (2)“分”校准状态:在“分”校准状态下,显示“分”的数码管以2Hz闪烁,并以2Hz的频率递增计数。 (3)“秒”校准状态:在“秒复零”状态下,显示“秒”的数码管以2Hz闪烁,并以1Hz的频率递增计数。 (4)闹钟“小时”校准状态:在闹钟“小时”校准状态下,显示“小时”的数码管以2Hz闪烁,并以2Hz的频率递增计数。 (5)闹钟“分”校准状态:在闹钟“分”校准状态下,显示“分”的数码管以2Hz闪烁,并以2Hz的频率递增计数。 (三)整点报时:蜂鸣器在“59”分钟的第“51”、“53”、“55”、“57”秒发频率为500Hz的低音,在“59”分钟的第“59”秒发频率为1000Hz的高音,结束时为整点。 (四)显示:要求采用扫描显示方式驱动6个LED数码管显示小时、分、秒。(五)闹钟:闹钟定时时间到,蜂鸣器发出频率为1000Hz的高音,持续时间为60秒。

FPGA课程设计实验报告 题目:VHDL编写的数字钟设计 学院:电子信息学院 专业:电子与通讯工程 姓名:朱振军

基于FPGA的VHDL数字钟设计 一、功能介绍 1.在七段数码管上具有时--分--秒的依次显示。 2.时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数。 3.整点报时,当计数到整点时扬声器发出响声。 4.时间设置:可以通过按键手动调节秒和分的数值。此功能中可通过按键实现整体清零和暂停的功能。 5.LED灯循环显示:在时钟正常计数下,LED灯被依次循环点亮。 待增加功能: 1.实现手动调节闹铃时间,在制定时间使扬声器发声。 2.实现微妙的快速计数功能,可实现暂停、保存当前时间、继续计数的功能。 二、设计方案 本文数字钟的设计采用了自顶向下分模块的设计。底层是实现各功能的模块,各模块由vhdl语言编程实现:顶层采用原理图形式调用。其中底层模块包括秒、分、时三个计数器模块、按键去抖动模块、按键控制模块、时钟分频模块、数码管显示模块共7个模块。 设计框图如下: 图一数字钟系统设计框图 由图1可以清晰的看到数字钟系统设计中各功能模块间连接关系。系统时钟50MHZ经过分频后产生1秒的时钟信号,1秒的时钟信号作为秒计数模块的输入信号,秒计数模块产生的进位信号作为分计数模块的输入信号,分计数模块的进位信号作为时计数模块的输入信号。秒计数模块、分计数模块、时计数模块的计数输出分别送到显示模块。由于设计中要使用按键进行调节时间,而按键的动作过程中存在产生得脉冲的不稳定问题,所以就牵扯到按键去抖动的问题,对此系统中设置了按键去抖动模块,按键去抖动模块产生稳定的脉冲信号送入按键控制模块,按键控制模块根据按键的动作对秒、分、时进行调节。

课程:CPLD与FPGA设计及应用 实验:基于VHDL语言的数字时钟设计 学号:092030030 姓名:朱峰 专业:信号与信息处理 学院:电子与信息学院 2011年12月

基于VHDL语言的数字时钟设计一:主要功能 1:具有时、分、秒计数显示功能,以24小时循环计时。 2:具有日期和星期显示功能。 3:具有秒表功能 4:具有调节日期,星期,小时,分钟,清零的功能。 5:具有定时和闹铃的功能。 二:结构框图 三:RTL图