本节将使用综合工具(Design Compiler)对一个8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble)生成一个全加器的版图。

首先输入8位全加器verilog代码:

module adder8(Cout,S,A,Cin);

output Cout;

output[7:0]S;

input[7:0]A;

input[7:0]B;

input Cin;

reg[8:0]SUM;

reg[7:0]S;

reg Cout;

wire[7:0]A,B;

always@(A or B or Cin)

begin

SUM[8:0]=A+B+Cin;

S=SUM[7:0];

Cout=SUM[8];

end

endmodule

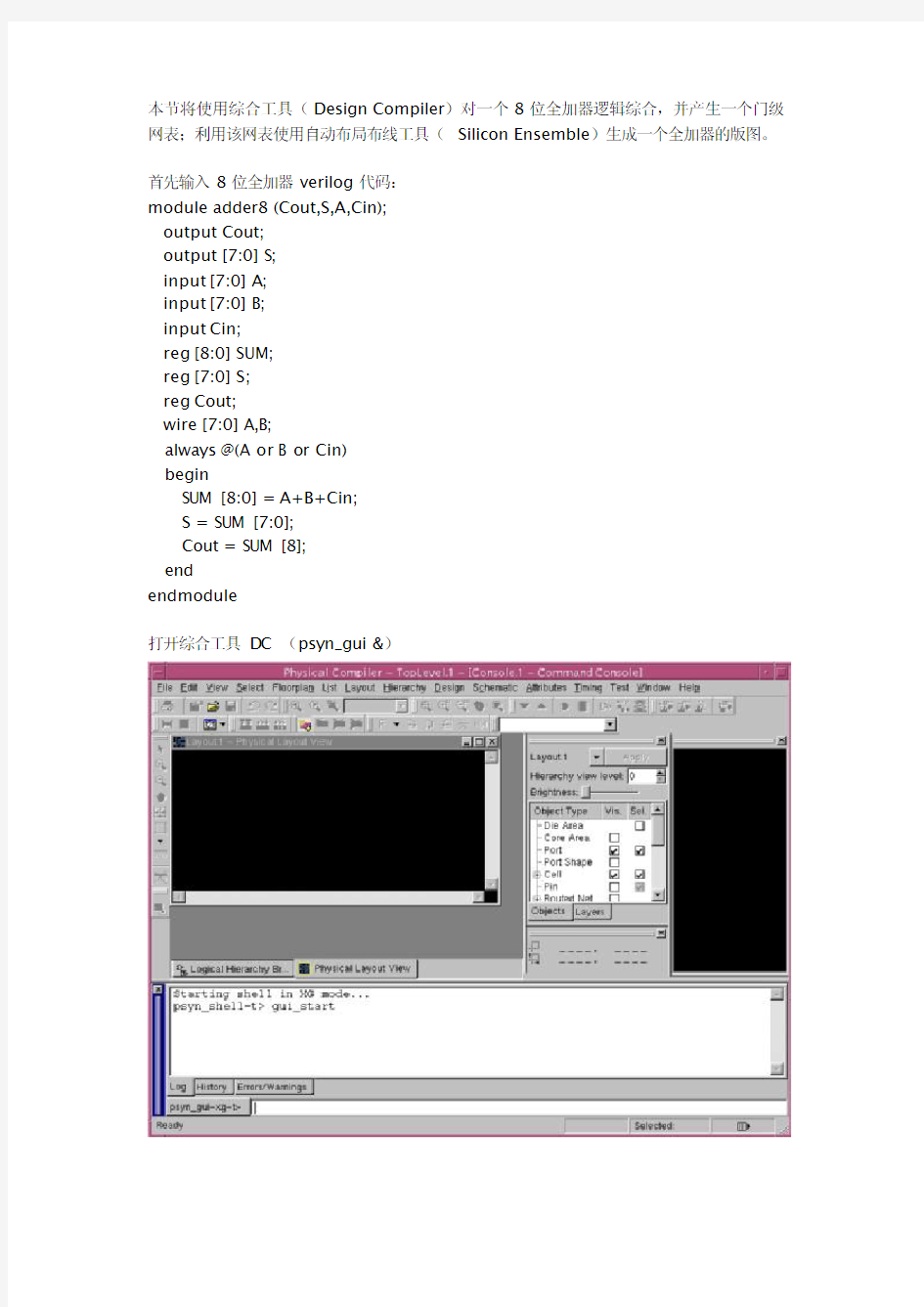

打开综合工具DC(psyn_gui&)

File->Read..读入代码

File->Setup..设置3个相关工艺库

将带红色*号的3个库设置如下图

Design->Compile Design..编译

Schematic->New Design Schematic View..可以看到综合后的顶层结构

通过双击C1模块还可以看到全加器的门级结构

为了后面自动布局布线的需要,这里我们要将这个综合结果保存为adder8_nl.v门级网表。在psyn_gui-xg-t>后输入如下命令

下面进行自动布局布线(一下有路径出现的地方要特别注意)打开Silicon Ensemble(sedsm&)

File->Import->LEF…导入库的转换格式

注意此文件的路径!

File->Import->Verilog…导入工艺库(此库为verilog描述的标准单元,包含各种延时信息)

这里去掉后面的!

继续File->Import->Verilog…导入网表adder8_nl.v(此处要先删掉第一个工艺库)

这里要加上顶层模块名adder8

Floorplan->Initialize Floorplan…准备工作完成开始布局布线

点击Variables将里面的PLAN.LOWERLEFT.ORIGIN由FALSE改为TURE

Edit->Add->Row…Area的区域可以直接点击Area并在图上拖拽,并使其大小与芯片核一致

File->Save as…保存为fplan

Route->Plan Power…设置电源环

在Plan Power窗口中点击Add Rings…

Place->Ios…放置输入输出

Place->Cells…放置单元

Place->Filler Cells->Add Cells…

Route->Route Power->Follow Pins…添加管脚(金属线宽设为1.8)

Route->Wroute…布线

View->Display Options…检查管脚名设置Pin为ON

File->Export->DEF…命名为adder8_wrouted.def

PCB电路板布局、布线基本原则 一、元件布局基本规则 1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开; 2. 定位孔、标准孔等非安装孔周围 1.27mm 内不得贴装元、器件,螺钉等安装孔周围 3.5mm (对于M2.5)、4mm(对于M3内不得贴装元器件; 3. 卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路; 4. 元器件的外侧距板边的距离为5mm; 5. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm; 6. 金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm定位孔、紧固件安装孔、椭圆孔及板中其它方孔外侧距板边的尺寸大于 3mm; 7. 发热元件不能紧邻导线和热敏元件;高热器件要均衡分布; 8. 电源插座要尽量布置在印制板的四周,电源插座与其相连的汇流条接线端应布置在同侧。特别应注意不要把电源插座及其它焊接连接器布置在连接器之间,以利于这些插座、连接器的焊接及电源线缆设计和扎线。电源插座及焊接连接器的布置间距应考虑方便电源插头的插 拔; 9. 其它元器件的布置: 所有 IC 元件单边对齐,有极性元件极性标示明确,同一印制板上极性标示不得多于两个方向,出现两个方向时,两个方向互相垂直; 10. 板面布线应疏密得当,当疏密差别太大时应以网状铜箔填充,网格大于 8mil(或 0.2mm); 11. 贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。重要信号线不准从插座脚间穿过; 12. 贴片单边对齐,字符方向一致,封装方向一致; 13. 有极性的器件在以同一板上的极性标示方向尽量保持一致。 二、元件布线规则 1画定布线区域距 PCB板边w 1mm的区域内,以及安装孔周围1mm内,禁止布线; 2、电源线尽可能的宽,不应低于18mil ;信号线宽不应低于12mil ;cpu 入出线不应低于10mil (或8mil );线间距不低于 10mil ; 3、正常过孔不低于 30mil ; 4、双列直插:焊盘 60mil ,孔径 40mil ; 1/4W电阻:51*55mil ( 0805表贴);直插时焊盘 62mil,孔径42mil ; 无极电容: 51*55mil (0805表贴);直插时焊盘 50mil ,孔径 28mil; 5、注意电源线与地线应尽可能呈放射状,以及信号线不能出现回环走线 PCB板布线技巧 在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB 中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、 双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。 自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布经线,快速地把短线连通,然后 进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。并试着重新再布线,以改进总体效果。 对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,

AltiumDesigner PCB布局布线过程与技巧 首先是原理图设计。 原理图设计是前期准备工作,对简单的板子,如果熟练流程,不妨可以跳过。但是对于初学者一定要按流程来,这样一方面可以养成良好的习惯,另一方面对复杂的电路也只有这样才能避免出错。在画原理图时,层次设计时要注意各个文件最后要连接为一个整体,这同样对以后的工作有重要意义。由于,软件的差别有些软件会出现看似相连实际未连(电气性能上)的情况。如果不用相关检测工具检测,万一出了问题,等板子做好了才发现就晚了,这也显示出按顺序来做的重要性了 接下来重点讨论具体制板的过程与技巧 1.制作物理边框 place>line,然后画框并选取框,最后design>board shape>define from selected objects,完成! 主要是要注意精确,否则以后出现安装问题麻烦可就大了。还有就是拐角地方最好用圆弧,一方面可以避免被尖角划伤,同时又可以减轻应力作用。 2.元件和网络的引入 打开原理图,选择Design>Update PCB Document... 常见问题:元件的封装形式找不到,元件网络问题,有未使用的元件或管脚,对照提示这些问题可以很快搞定的。 3.元件的布局 元件的布局与走线对产品的寿命、稳定性、电磁兼容都有很大的影响,是应该特别注意的地方。一般来说应该有以下一些原则:

(1)放置顺序 先放置与结构有关的固定位置的元器件,如电源插座、指示灯、开关、连接件之类,这些器件放置好后用软件的LOCK功能将其锁定,使之以后不会被误移动。再放置线路上的特殊元件和大的元器件,如发热元件、变压器、IC等。最后放置小器件。 (2)注意散热 元件布局还要特别注意散热问题。对于大功率电路,应该将那些发热元件如功率管、变压器等尽量靠边分散布局放置,便于热量散发,不要集中在一个地方,也不要高电容太近以免使电解液过早老化。 4.布线 通行的布线原则。 ◆高频数字电路走线细一些、短一些好 ◆大电流信号、高电压信号与小信号之间应该注意隔离(隔离距离与要承受的耐压有关,许多情况下为避免爬电,还在印制线路板上的高低压之间开槽。) ◆两面板布线时,两面的导线宜相互垂直、斜交、或弯曲走线,避免相互平行,以减小寄生耦合;作为电路的输人及输出用的印制导线应尽量避免相邻平行,以免发生回授,在这些导线之间最好加接地线。 ◆走线拐角尽量120度拐角 ◆同是地址线或者数据线,走线长度差异不要太大,否则短线部分要人为走弯线作补偿 ◆走线尽量走在焊接面,特别是通孔工艺的PCB ◆尽量少用过孔、跳线

计算机网页设计实习报告网页设计实习报告 计算机网页设计实习报告网页设计实习报告 计算机网页设计实习报告范文一实习目的:熟悉和掌握计算机网页设计的基本技巧及网页制作相关工具软件等内容。培养我们利用计算机进行商务网页设计的基本思路和应用开发能力,提高我们的计算机文化素质。 网页是世界上最有价值的不动产之一。人们在这个不足平米的空间内投资达数百万美元。网页对公司的影响比简单的电子商务增收方法大得多;网页也是公司对外的脸面。wEB 站点就像一栋房子,它的每一个窗口都可以看成一扇门,人们可以沿着搜索引擎其他wEB站点的链接,绕过主页而进入wEB的深层。 一.网站的整体规划 1.讨论网站主题:因为自己对普罗旺斯很感兴趣,于是就想到要是一下为心中的仙境设计一个旅游网站。 2.定位网站cI形象:旅游网站最重要的就是是浏览者产生想去亲身体验一下的共鸣。于是在网页设计上面,根据普罗旺斯梦幻般的意境,我采用的是清新隽永的cI形象。使浏览者有宾至如归的感受。 3.确定栏目和板块: 1]首先要考虑整个网页的长和宽,以及长度和宽度之间

的比例。 2]其次就应该考虑导航条的设置了。 3]正文的框架设置 在浏览了很多精美的旅游网站之后,再结合自己的想法,我先在草纸上画出了大体的栏目和板块。 4.网站的整体风格和创意:建立一个浪漫的旅行网站,走映像派路线,目的务必使浏览者留下映像。 二.网页制作的前期策划与准备 1.资料的搜集:由于个人的爱好,我很早以前就收集了许多普罗旺斯的美图,这次就方便多了。接着就搜集了一些有梦幻效果的网页背景,FIASH源代码、小图标和一些GIF 的动画等。 2.熟悉制作工具软件: 主页制作的基本条件有: 硬件: 一台电脑;可以拨号上网;如果你有条件的话,建议:配置扫描仪,这将大大方便图像和文字的输入;软件: HTmL编辑软件:常用的有Frontpage、Hotdog等,本文重点介绍Dreamweaver; 图像处理软件:常用的有Photoshop、flash、Fireworks 等; 文件上传软件:常用的有cuteftp、wSftp等。

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。 首先输入 8位全加器 verilog 代码: module adder8(Cout,S,A,Cin; output Cout; output [7:0]S; input [7:0]A; input [7:0]B; input Cin; reg [8:0]SUM; reg [7:0]S; reg Cout; wire [7:0]A,B; always @(Aor B or Cin begin SUM [8:0]=A+B+Cin; S =SUM [7:0]; Cout =SUM [8];

end endmodule 打开综合工具 DC (psyn_gui& File->Read..

读入代码

File->Setup..设置 3 个相关工艺库将带红色 *号的 3

个库设置如下图 Design->CompileDesign.. 编译 Schematic->NewDesign Schematic View.. 可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构 为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。 在 psyn_gui-xg-t> 后输入如下命令 下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm & File->Import->LEF… 导入库的转换格式 注意此文件的路径! File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息

计算机操作系统综合设计 实验一 实验名称:进程创建模拟实现 实验类型:验证型 实验环境: win7 vc++6.0 指导老师: 专业班级: 姓名: 学号: 联系电话: 实验地点:东六E507 实验日期:2017 年 10 月 10 日 实验报告日期:2017 年 10 月 10 日 实验成绩:

一、实验目的 1)理解进程创建相关理论; 2)掌握进程创建方法; 3)掌握进程相关数据结构。 二、实验内容 windows 7 Visual C++ 6.0 三、实验步骤 1、实验内容 1)输入给定代码; 2)进行功能测试并得出正确结果。 2、实验步骤 1)输入代码 A、打开 Visual C++ 6.0 ; B、新建 c++ 文件,创建basic.h 头文件,并且创建 main.cpp 2)进行功能测试并得出正确结果 A 、编译、运行main.cpp B、输入测试数据 创建10个进程;创建进程树中4层以上的数型结构 结构如图所示:。

createpc 创建进程命令。 参数: 1 pid(进程id)、 2 ppid(父进程id)、3 prio(优先级)。 示例:createpc(2,1,2) 。创建一个进程,其进程号为2,父进程号为1,优先级为2 3)输入创建进程代码及运行截图 4)显示创建的进程

3、画出createpc函数程序流程图 分析createpc函数的代码,画出如下流程图:

四、实验总结 1、实验思考 (1)进程创建的核心内容是什么? 答: 1)申请空白PCB 2)为新进程分配资源 3)初始化进程控制块 4)将新进程插入到就绪队列 (2)该设计和实际的操作系统进程创建相比,缺少了哪些步骤? 答:只是模拟的创建,并没有分配资源 2、个人总结 通过这次课程设计,加深了对操作系统的认识,了解了操作系统中进程创建的过程,对进程创建有了深入的了解,并能够用高 级语言进行模拟演示。一分耕耘,一分收获,这次的课程设计让 我受益匪浅。虽然自己所做的很少也不够完善,但毕竟也是努 力的结果。另外,使我体会最深的是:任何一门知识的掌握, 仅靠学习理论知识是远远不够的,要与实际动手操作相结合才能 达到功效。

教师学科教案[ 20 – 20 学年度第__学期] 任教学科:_____________ 任教年级:_____________ 任教老师:_____________ xx市实验学校

Photoshop CS3网页设计与制作教学计划 2011级计算机应用班授课教师:艾珉 一、教学目标 本教材以2011级计算机应用班的学生为教学对象,通过对本门课程的教学帮助学生认识photoshop软件,能够熟练的对给定素材进行处理和再加工,最后能够熟练的使用photoshop软件设计和制作网页。为以后从事网站设计与制作及网站的后期维护奠定良好的基础。同时,通过本门课程的讲解,让学生学会一种学习方法,学会一种认识事物的态度。让学生能够很快的适应工作环境。在教学过程中,结合上机操作,理论联系实际进一步加深对所学知识的掌握。在教学的过程中要及时了解学生的掌握程度,及时调整教学的难度,使每一位同学都能够学有所得,学有所获。 二、教材分析 本书以模块教学为主,全书共分为8个模块,第一模块主要讲解photoshop 在网页设计中的应用,第二模块主要讲解网页的版面设计;第三模块主要讲解网页的色彩搭配;第四模块主要讲解导航栏的设计与制作;第五模块主要讲解按钮的设计与制作;第六模块主要讲解特殊文字的设计和制作;第七模块主要讲解网页的设计和制作;第八模块主要讲解切割网页图像。本书通过案例有侧重点的由浅入深,循序渐进帮助学生全面掌握photoshop版面设计、色彩搭配、网页元素设计等综合技能。本书通过任务让学生能够运用所学的知识解决现实问题,积累经验,从而提高动手能力和解决问题的能力,每个模块在模拟制作完成任务后还设有独立实践任务,以强化学生技能应用能力和自学能力。 三、教学重点与难点 本教材采用模块教学。以“学一个案例就掌握一种工作技巧”为原则,有侧重点的实例由浅入深,循序渐进帮助学生掌握网页设计的基本技能。 本教材的重点是网页版面设计、网页的色彩搭配、导航栏的设计与制作、按钮的设计与制作、特殊文字的设计与制作、网页的设计与制作和切割网页图像。其中网页的色彩搭配、网页的设计与制作学生掌握起来有一定的难度,需要在讲

布局: 1、顾客指定器件位置是否摆放正确 2、BGA与其它元器件间距是否≥5mm 3、PLCC、QFP、SOP各自之间和相互之间间距是否≥2.5 mm 4、PLCC、QFP、SOP与Chip 、SOT之间间距是否≥1.5 mm 5、Chip、SOT各自之间和相互之间的间距是否≥0.3mm 6、PLCC表面贴转接插座与其它元器件的间距是否≥3 mm 7、压接插座周围5mm范围内是否有其他器件 8、Bottom层元器件高度是否≤3mm 9、模块相同的器件是否摆放一致 10、元器件是否100%调用 11、是否按照原理图信号的流向进行布局,调试插座是否放置在板边 12、数字、模拟、高速、低速部分是否分区布局,并考虑数字地、模拟地划分 13、电源的布局是否合理、核电压电源是否靠近芯片放置 14、电源的布局是否考虑电源层的分割、滤波电容的组合放置等因素 15、锁相环电源、REF电源、模拟电源的放置和滤波电容的放置是否合理 16、元器件的电源脚是否有0.01uF~0.1uF的电容进行去耦 17、晶振、时钟分配器、VCXO\TCXO周边器件、时钟端接电阻等的布局是否合理 18、数字部分的布局是否考虑到拓扑结构、总线要求等因素 19、数字部分源端、末端匹配电阻的布局是否合理 20、模拟部分、敏感元器件的布局是否合理 21、环路滤波器电路、VCO电路、AD、DA等布局是否合理 22、UART\USB\Ethernet\T1\E1等接口及保护、隔离电路布局是否合理 23、射频部分布局是否遵循“就近接地”原则、输入输出阻抗匹配要求等 24、模拟、数字、射频分区部分跨接的回流电阻、电容、磁珠放置是否合理 外形制作: 1、外形尺寸是否正确? 2、外形尺寸标注是否正确? 3、板边是否倒圆角≥1.0mm 4、定位孔位置与大小是否正确 5、禁止区域是否正确 6、Routkeep in距板边是否≥0.5mm 7、非金属定位孔禁止布线是否0.3mm以上 8、顾客指定的结构是否制作正确 规则设置: 1、叠层设置是否正确? 2、是否进行class设置 3、所有线宽是否满足阻抗要求? 4、最小线宽是否≧5mil 5、线、小过孔、焊盘之间间距是否≥6mil,线到大过孔是否≥10mil

PCB设计布局布线技巧分享 工程师往往更关注电路的设计、最新的元器件以及代码,认为这些才是一个电子产品项目中的重要部分,却忽略了PCB布局、布线这个关键的环节。如果PCB布局、布线不当,往往会导致电路工作不正常、不可靠。本文就列出实际PCB布局布线中要注意的一些要点,以帮助你的PCB项目做得更准确、可靠。 走线的尺寸PCB板上的铜线是有阻抗的,也就意味着在电路图上的一根连线在实际的板子上会有电压降、功耗,电流流过的时候也会有温升。阻抗由以下公式定义: PCB设计工程师通常使用走线的长度、厚度和宽度来控制其阻抗。电阻是用于制作PCB 走线的金属铜的物理特性,既然我们无法改变铜的物理特性,就来控制走线的尺寸吧。PCB走线的厚度以多少盎司的铜来计量。如果我们在1平方英尺的区域内均匀涂抹1盎司铜,这个厚度也就是一盎司的铜,这个厚度大致为1.4千分之一英寸。许多PCB设计师使用1盎司或2盎司的铜,但许多PCB制造商可提供6盎司的厚度。但请注意,许多要求精细的场合,比如靠得很近的管脚就很难铺设很厚的铜。在设计的阶段最好咨询PCB 制造商,先了解清楚他们的生产能力。 你可以借助“PCB走线宽度计算器”来确定你的走线厚度和宽度,在计算的时候可以设定升高的温度为5°C。当然如果你的板子空间足够,布线很轻松,不妨使用较宽的走线,因为在不增加成本的情况下可以获得较低的阻抗。 如果你的板子是多层的,外层上的走线肯定会比内层的走线温度更低,因为内层的热量必须通过内部走线、过孔、材料层等较长的路径才能将热散发掉。 环路一定要尽可能小 环路,尤其是高频环路,应尽可能小。较小的环路具有较低的电感和电阻。将环路放置在地平面上面也会进一步降低电感。通过小环路可减少由以下公式引起的高频电压尖峰:小的环路也会降低通过一些节点上的电感感应到的外部干扰,或者从节点广播出去的信号

一、元件布局基本规则 1.按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开; 2.定位孔、标准孔等非安装孔周围 1."27mm内不得贴装元、器件,螺钉等安装孔周围 3."5mm(对于M 2."5)、4mm(对于M3)内不得贴装元器件; 3.卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路; 4.元器件的外侧距板边的距离为5mm; 5.贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm; 6.金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm。定位孔、紧固件安装孔、椭圆孔及板中其它方孔外侧距板边的尺寸大于3mm; 7.发热元件不能紧邻导线和热敏元件;高热器件要均衡分布; 8.电源插座要尽量布置在印制板的四周,电源插座与其相连的汇流条接线端应布置在同侧。 特别应注意不要把电源插座及其它焊接连接器布置在连接器之间,以利于这些插座、连接器的焊接及电源线缆设计和扎线。电源插座及焊接连接器的布置间距应考虑方便电源插头的插拔; 9.其它元器件的布置: 所有IC元件单边对齐,有极性元件极性标示明确,同一印制板上极性标示不得多于两个方向,出现两个方向时,两个方向互相垂直;

10、"板面布线应疏密得当,当疏密差别太大时应以网状铜箔填充,网格大于8mil(或 0."2mm); 11、"贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。重要信号线不准从插座脚间穿过; 12、"贴片单边对齐,字符方向一致,封装方向一致; 13、"有极性的器件在以同一板上的极性标示方向尽量保持一致。 二、元件布线规则 1、画定布线区域距PCB板边≤1mm的区域内,以及安装孔周围1mm内,禁止布线; 2、"电源线尽可能的宽,不应低于18mil;信号线宽不应低于12mil;cpu入出线不应低于10mil(或8mil);线间距不低于10mil; 3、正常过孔不低于30mil; 4、双列直插: 焊盘60mil,孔径40mil; 1/4W电阻:51*55mil(0805表贴);直插时焊盘62mil,孔径42mil; 无极电容:51*55mil(0805表贴);直插时焊盘50mil,孔径28mil; 5、注意电源线与地线应尽可能呈放射状,以及信号线不能出现回环走线。 如何提高抗干扰能力和电磁兼容性 在研制带处理器的电子产品时,如何提高抗干扰能力和电磁兼容性? 1、下面的一些系统要特别注意抗电磁干扰: (1)微控制器时钟频率特别高,总线周期特别快的系统。

物联网传输综合课程设计实验报告 人体红外数据通信实验 一、实验目的 1. 了解基于Z-Stack 协议栈的SappWsn 应用程序框架的工作机制 2. 掌握在ZigBee 协议栈中添加人体红外传感器驱动的方法。 二、实验设备 1. 装有IAR 开发工具的PC 机一台 2. 下载器一个 3. 物联网多网技术开发设计平台一套 三、实验原理 在Z-Stack APP中的HAL\Target\CC2530EB\Includes组中,提供了一个hal_io.h的文件,如图所示。 其中,提供了名为HalIOSetInput 的函数,可以将燃气传感器端口(P1.0)设置为输入,然后通过调用HalIOGetLevel 函数来获取传感器状态。 四、实验步骤 1、将单片机zigbee协调器拆卸下来,取出烧写器。通过Mini USB接口将zigbee 协调器与下载器和PC机相连。

2、将实验箱控制方式切换开关拨至“手动”一侧,转动实验箱“旋钮节点选择”旋钮,使得协调器旁边的LED灯被点亮 3、打开配套代码中的ZStack-CC2530\Projects\SappWsn\SappWsn.eww工程文件,在“Tools”组中,找到“f8wConfig.cfg”文件,双击打开,并找到大概第59 行的“-DZAPP_CONFIG_PAN_ID=0xFFFF”,将其中的“0xFFFF”修改为其他值,例如0x0010

4、在工程目录结构树上方的下拉列表中,选择“CoordinatorEB”,点击工具栏中的“Make”按钮,编译工程,等待工程编译完成,如看到警告,可以忽略。在工程目录结构树中的工程名称上点击鼠标右键,选择“Options”,并在弹出的对话框中选择左侧的“Debugger”,并在右侧的“Driver”列表中选择“Texas Instruments”,点击“Download and Debug”按钮。待程序下载完毕后,点击“Go”按钮,使程序开始运行。点击工具栏中的“Stop Debugging”,退出调试模式, 5、转动实验箱“旋钮节点选择”旋钮,使得热释红外传感器节点旁边的LED灯被点亮,在工程目录结构树上方的下拉列表中,选择“EndDeviceEB”,在“SAPP_Device.h”文件中,取消“HAS_IRPERS”的注释,并保证其他的功能均被注释,如图所示

布局布线流程介绍 布局布线.....................................................................................................................................- 1 - 1. 布局布线工程师应该具备的能力.........................................................................................- 1 - 2. 布局布线实现使用的EDA工具............................................................................................- 3 - 3. 布局布线实现流程................................................................................................................- 4 - 3.1 数据导入.......................................................................................................................- 4 - 3.2布局规划(Floorplan)...............................................................................................- 7 - 3.3单元放置(Placement)............................................................................................- 13 - 3.4时钟树综合(Clock Tree Synthesis)......................................................................- 15 - 3.5全局与细节布线(NanoRoute)..............................................................................- 17 - 3.6电压衰减分析(IR-drop)........................................................................................- 20 - 3.7 GDSII及网表(netlist)导出并做物理验证............................................................- 20 - 3.8最终功能与时序验证..................................................................................................- 20 - 当一个设计完成了前端逻辑综合并生成了门级网表后,接下来的任务就是门级网表的物理实现,即把门级网表转换成版图(layout)。在半定制设计流程中,所谓的数字后端就是指布局布线物理实现。在半定制设计中所需要的大部分后端数据都是由流片厂家或者相关公司提供,这些数据对于设计者都是透明的,所以设计者只需要做后端布局布线工作。 实际上,布局布线只是后端设计的一个部分。在工程实践中,数字后端设计应该包括标准单元库的设计,宏单元的定制设计以及布局布线实现。 1. 布局布线工程师应该具备的能力 在超深亚微米集成电路设计中,我认为一个好的布局布线工程师应该具备以下几个基本能力: z要深入了解相关布局布线工具的各方面特性及参数。这样才能正确操作布局布线工具。 z要良好把握后端物理实现中标准单元和宏单元的性能指标及物理参数。 这样才能在芯片布局布线初期对预布局有合理地规划,并且可以对芯片 预估的性能有很好把握,最终减少布局布线实现的迭代次数,提高执行 效率。

《实验报告总结》 实验报告总结(一): 一个长学期的电路原理,让我学到了很多东西,从最开始的什么都不懂,到此刻的略懂一二。 在学习知识上面,开始的时候完全是老师讲什么就做什么,感觉速度还是比较快的,跟理论也没什么差距。但是之后就觉得越来越麻烦了。从最开始的误差分析,实验报告写了很多,但是真正掌握的确不多,到最后的回转器,负阻,感觉都是理论没有很好的跟上实践,很多状况下是在实验出现象以后在去想理论。在实验这门课中给我最大的感受就是,必须要先弄清楚原理,在做实验,这样又快又好。 在养成习惯方面,最开始的时候我做实验都是没有什么条理,想到哪里就做到哪里。比如说测量三相电,有很多种状况,有中线,无中线,三角形接线法还是Y形接线法,在这个实验中,如果选取恰当的顺序就能够减少很多接线,做实验就应要有良好的习惯,就应在做实验之前想好这个实验要求什么,有几个步骤,就应怎样安排才最合理,其实这也映射到做事情,不管做什么事情,就应都要想想目的和过程,这样才能高效的完成。电原实验开始的几周上课时间不是很固定,实验报告也累计了很多,第一次感觉有那么多实验报告要写,在交实验报告的前一天很多同学都通宵了的,这说明我们都没有合理的安排好自己的时间,我就应从这件事情中吸取教训,合理安排自己的时间,完成就应完成的学习任务。这学期做的一些实验都需要严谨的态度。在负阻的实验中,我和同组的同学连了两三次才把负阻链接好,又浪费时间,又没有效果,在这个实验中,有很多线,很容易插错,所以要个性仔细。 在最后的综合实验中,我更是受益匪浅。完整的做出了一个红外测量角度的仪器,虽然不是个性准确。我和我组员分工合作,各自完成自己的模块。我负责的是单片机,和数码显示电路。这两块都是比较简单的,但是数码显示个性需要细致,由于我自己是一个粗心的人,所以数码管我检查了很多遍,做了很多无用功。 总结:电路原理实验最后给我留下的是:严谨的学习态度。做什么事情都要认真,争取一次性做好,人生没有太多时间去浪费。 实验报告总结(二): 在分子生物学实验室为期两个月的实习使我受益匪浅,我不仅仅学习到了专业知识,更重要的是收获了经验与体会,这些使我一生受用不尽,记下来与大家共勉:

PCB布局、布线基本原则 亚洲电子研发中心 AIDONG 提供 一、元件布局基本规则 1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就 近集中原则,同时数字电路和模拟电路分开; 2.定位孔、标准孔等非安装孔周围1.27mm 内不得贴装元、器件,螺钉等安装孔周围 3.5mm(对 于M2.5)、4mm(对于M3)内不得贴装元器件; 3. 卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳 体短路; 4. 元器件的外侧距板边的距离为5mm; 5. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm; 6. 金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其 间距应大于2mm。定位孔、紧固件安装孔、椭圆孔及板中其它方孔外侧距板边的尺寸大于3mm; 7. 发热元件不能紧邻导线和热敏元件;高热器件要均衡分布; 8. 电源插座要尽量布置在印制板的四周,电源插座与其相连的汇流条接线端应布置在同侧。特 别应注意不要把电源插座及其它焊接连接器布置在连接器之间,以利于这些插座、连接器的焊接及电源线缆设计和扎线。电源插座及焊接连接器的布置间距应考虑方便电源插头的插拔; 9. 其它元器件的布置: 所有IC元件单边对齐,有极性元件极性标示明确,同一印制板上极性标示不得多于两个方向,出现两个方向时,两个方向互相垂直; 10、板面布线应疏密得当,当疏密差别太大时应以网状铜箔填充,网格大于8mil(或0.2mm); 11、贴片焊盘上不能有通孔,以免焊膏流失造成元件虚焊。重要信号线不准从插座脚间穿过; 12、贴片单边对齐,字符方向一致,封装方向一致; 13、有极性的器件在以同一板上的极性标示方向尽量保持一致。 二、元件布线规则 1、画定布线区域距PCB板边≤1mm的区域内,以及安装孔周围1mm内,禁止布线; 2、电源线尽可能的宽,不应低于18mil;信号线宽不应低于12mil;cpu入出线不应低于10mil

PCB布局方法技巧:布线、焊盘及敷铜的设计 2018-03-09 PCB布线焊盘敷铜设计 随着电子技术的进步, PCB (印制电路板)的复杂程度、适用范围有了飞速的发展。从事高频PCB的设计者必须具有相应的基础理论知识,同时还应具有丰富的高频PCB的制作经验。也就是说,无论是原理图的绘制,还是PCB 的设计,都应当从其所在的高频工作环境去考虑,才能够设计出较为理想的PCB。本文主要从高频PCB 的手动布局、布线两个方面,基于ProtelSE对在高频PCB 设计中的一些问题进行研究。 1 布局的设计 Protel 虽然具有自动布局的功能,但并不能完全满足高频电路的工作需要,往往要凭借设计者的经验,根据具体情况,先采用手工布局的方法优化调整部分元器件的位置,再结合自动布局完成PCB的整体设计。布局的合理与否直接影响到产品的寿命、稳定性、EMC (电磁兼容)等,必须从电路板的整体布局、布线的可通性和PCB的可制造性、机械结构、散热、EMI(电磁干扰) 、可靠性、信号的完整性等方面综合考虑。 一般先放置与机械尺寸有关的固定位置的元器件,再放置特殊的和较大的元器件,最后放置小元器件。同时,要兼顾布线方面的要求,高频元器件的放置要尽量紧凑,信号线的布线才能尽可能短,从而降低信号线的交叉干扰等。 1.1 与机械尺寸有关的定位插件的放置 电源插座、开关、PCB之间的接口、指示灯等都是与机械尺寸有关的定位插件。通常,电源与PCB之间的接口放到PCB的边缘处,并与PCB 边缘要有3 mm~5 mm的间距;指示发光二极管应根据需要准确地放置;开关和一些微调元器件,如可调电感、可调电阻等应放置在靠近PCB 边缘的位置,以便于调整和连接;需要经常更换的元器件必须放置在器件比较少的位置,以易于更换。 1.2 特殊元器件的放置 大功率管、变压器、整流管等发热器件,在高频状态下工作时产生的热量较多,所以在布局时应充分考虑通风和散热,将这类元器件放置在PCB上空气容易流通的地方。大功率整流管和调整管等应装有散热器,并要远离变压器。电解电容器之类怕热的元件也应远离发热器件,否则电解液会被烤干,造成其电阻增大,性能变差,影响电路的稳定性。 易发生故障的元器件,如调整管、电解电容器、继电器等,在放置时还要考虑到维修方便。对经常需要测量的测试点,在布置元器件时应注意保证测试棒能够方便地接触。 由于电源设备内部会产生50 Hz泄漏磁场,当它与低频放大器的某些部分交连时,会对低频放大器产生干扰。因此,必须将它们隔离开或者进行屏蔽处理。放大器各级最好能按原理图排成直线形式,如此排法的优点是各级的接地电流就在本级闭合流动,不影响其他电路的工作。输入级与输出级应当尽可能地远离,减小它们之间的寄生耦合干扰。

1 布局的设计 Protel 虽然具有自动布局的功能,但并不能完全满足高频电路的工作需要,往往要凭借设计者的经验,根据具体情况,先采用手工布局的方法优化调整部分元器件的位置,再结合自动布局完成PCB的整体设计。布局的合理与否直接影响到产品的寿命、稳定性、EMC (电磁兼容)等,必须从电路板的整体布局、布线的可通性和PCB的可制造性、机械结构、散热、EMI(电磁干扰) 、可靠性、信号的完整性等方面综合考虑。 一般先放置与机械尺寸有关的固定位置的元器件,再放置特殊的和较大的元器件,最后放置小元器件。同时,要兼顾布线方面的要求,高频元器件的放置要尽量紧凑,信号线的布线才能尽可能短,从而降低信号线的交叉干扰等。 1.1 与机械尺寸有关的定位插件的放置 电源插座、开关、PCB之间的接口、指示灯等都是与机械尺寸有关的定位插件。通常,电源与PCB之间的接口放到PCB的边缘处,并与PCB 边缘要有3 mm~5 mm的间距;指示发光二极管应根据需要准确地放置;开关和一些微调元器件,如可调电感、可调电阻等应放置在靠近PCB 边缘的位置,以便于调整和连接;需要经常更换的元器件必须放置在器件比较少的位置,以易于更换。 1.2 特殊元器件的放置 大功率管、变压器、整流管等发热器件,在高频状态下工作时产生的热量较多,所以在布局时应充分考虑通风和散热,将这类元器件放置在PCB上空气容易流通的地方。大功率整流管和调整管等应装有散热器,并要远离变压器。电解电容器之类怕热的元件也应远离发热器件,否则电解液会被烤干,造成其电阻增大,性能变差,影响电路的稳定性。 易发生故障的元器件,如调整管、电解电容器、继电器等,在放置时还要考虑到维修方便。对经常需要测量的测试点,在布置元器件时应注意保证测试棒能够方便地接触。 由于电源设备内部会产生50 Hz泄漏磁场,当它与低频放大器的某些部分交连时,会对低频放大器产生干扰。因此,必须将它们隔离开或者进行屏蔽处理。放大器各级最好能按原理图排成直线形式,如此排法的优点是各级的接地电流就在本级闭合流动,不影响其他电路的工作。输入级与输出级应当尽可能地远离,减小它们之间的寄生耦合干扰。 考虑各个单元功能电路之间的信号传递关系,还应将低频电路和高频电路分开,模拟电路和数字电路分开。集成电路应放置在PCB的中央,这样方便各引脚与其他器件的布线连接。 电感器、变压器等器件具有磁耦合,彼此之间应采用正交放置,以减小磁耦合。另外,它们都有较强的磁场,在其周围应有适当大的空间或进行磁屏蔽,以减小对其他电路的影响。 在PCB的关键部位要配置适当的高频退耦电容,如在PCB电源的输入端应接一个10μF~100 μF的电解电容,在集成电路的电源引脚附近都应接一个0.01 pF左右的瓷片电容。有些电路还要配置适当的高频或低频扼流圈,以减小高低频电路之间的影响。这一点在原理图设

EDA综合课程设计实验报告 题目:设计一个全双工UART电路院系:XXXX学院 学号:XXXXX 姓名:严XX 教师:林XX 时间:2012.06.02

1 课程设计的摘要原理 (2) 2 设计一个全双工UART电路,具体要求如下: (6) 3.UART设计 (7) 3.1 UART结构 (7) 3.2 UART的帧格式 (8) 4 UART的Verilog HDL语言设计 (9) 4.1 UART分频器 (9) 4.2UART发送模块 (10) 4.3 UART的接收模块 (14) 4.4 UART的硬件测试 (18) 5 课程设计总结 (19)

1摘要 UART协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议,在实际工业生产中有时并不使用UART的全部功能。只需将其核心功能集成即可。波特率发生器、接收器和发送器是UART的三个核心功能模块,利用Vefilog-HDL语言对这三个功能模块进行描述并加以整合UART(即Universal AsynchronousReceiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL或Veriolog -HDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。 实际应用上,有时我们不需要使用完整的UART的功能和这些辅助功能。使用Verilog-HDL将所需要的UART的核心功能集成到FPGA/CPLD内部,就可以实现紧凑、稳定且可靠的UART数据传输。这样,既可以满足实际的应用,实现所要求的简单的通信和控制,又能够去除更多不需要的繁杂复杂的功能实现。 一、UART的原理 串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。数据在一根数据线上一位一位传输,每一位数据都占据一个固定的时间长度。与并行通信方式相比,串行通信方式的传输速度较慢,但这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,因此得到了广泛的应用。 基本的UART只需要发送和接收两条数据线就可以完成数据的全双工通信,其基本功能是在发送端将控制器通过总线传过来的并行数据,以设定的格式,设定的频率串行地传输出去,并同时在接收端将串行接收到的数据,转换成相应的并行数据发送出去。UART的基本帧格式如图1所示。其中,起始位总是逻辑O状态,停止位总是逻辑l状态,其持续时间可选为1位、1.5位或2位,其数据位可为5、6、7、8位,校验位可根据需要选择奇校验位,偶校验位或无校验位。

教 案 《网页设计与制作》教案 序号:5 本次课程备课笔记 网 页 链 接 超链接是WWW 的魅力所在。为了把Internet 上众多分散的网站和网页联系起来,构成一个有机的整体,就要在网页上加入链接。通过简单地点击网页上的链接,用户就可以在信息海洋中尽情遨游。 超链接的分类,如图2.26所示。 下面将通过一些小例子讲述锚记链接、站点链接、图形热点链接等内容,同时结合 【文件】面板,介绍一些创建链接的高级技巧。 内部链接:在同一网站文档之间的链接 外部链接:不同网站文档之间的链接 锚记链接:同一网页或不同网页的指定位置的链接 E-mail 链接:电子邮件的链接 超链接 图2.26 超链接的种类 一、相对路径和绝对路径 先看最传统的链接创建方法。如果要给文字或图像创建链接,应先将文字或图像选中,直接在如图2.27所示的【链接】下拉列表框中输入要链接的网页文件路径和名字即可。 图2.27 链接下拉列表 单击【属性】面板中链接框旁的【浏览文件】图标,打开【选择文件】对话框,从中选择要链接的网页也可创建链接。【选择文件】对话框下面有【相对于】下拉列表框,里面有【文档】和【站点根目录】两项,如图2.28所示。 【文档】表示以文档相对路径方式链接;【站点根目录】表示以根绝对路径方式链接。相对路径与绝对路径是非常重要的概念,一定要掌握它们之间的区别。

1. 绝对路径 绝对路径是包括服务器协议(在本例中为HTTP协议)的完全路径,比如“网虫乐园——软件大观园”,绝对路径为“https://www.doczj.com/doc/f31698468.html,/web/softroom”,如果所要链接当前站点以外的文档,就必须使用绝对路径。 图2.28 【选择文件】对话框 2. 相对路径 相对路径又可分为与根目录相对的路径和与文档相对的路径两种。 在本地磁盘上编辑网页时,需要选定一个文件夹来定义本地站点,模拟服务器上的根文件夹,系统就根据这个文件夹来确定所有链接的本地文件位置,而根相对路径中的根就是指这个文件夹。 提示:根相对路径(也称相对根目录)的路径以“/”开头,路径是从当前站点的根目录开始计算。例如D盘myweb目录就是名为“myweb”的站点,这时“/index.htm” 路径就表示文件位置为D:\myweb\index.htm。根相对路径适用于链接内容需频繁更换的文件,这样即使站点中的文件被移动了,其链接仍可以生效。 如果目录结构过深,在引用根目录下的文件时,用根相对路径会更好些。例如某一个网页文件中引用根目录下img目录中的一个图,在当前网页中用文档相对路径表示为:“../../../../../img/a.gif”,而用根相对路径只要表示为“/img/a.gif”即可,其关系如图2.29所示。 绝对路径:如https://www.doczj.com/doc/f31698468.html,/web/softroom 根相对路径:如/img/a.gif、/pc/oa/index.htm 文档路径 相对路径: 文档相对路径:如img/a.gif、a.gif、../a.gif 图2.29 相对路径与绝对路径 注意:在预览文件时,用根相对路径链接的内容在本地浏览器中不会显示出来。这是因为浏览器不承认站点的根文件夹为服务器。